Philips TEA1200TS User Manual

查询TEA1200TS供应商查询TEA1200TS供应商

INTEGRATED CIRCUITS

DATA SH EET

TEA1200TS

0.95 V starting DC-to-DC converter

with low battery indicator

Product specification 2002 May 14

Philips Semiconductors Product specification

0.95 V starting DC-to-DC converter

with low battery indicator

FEATURES

• Complete DC-to-DC converter circuit and battery low

detector

• Configurablefor1, 2 or 3-cellNickel-Cadmium(NiCd)or

Nickel Metal Hydride (NiMH) batteriesand 1 LithiumIon

(Li-Ion) battery

• Guaranteed DC-to-DC converter start-up from 1-cell

NiCd or NiMH battery, even with a load current

• Upconversion or downconversion

• Internal power MOSFETs featuring a low R

approximately 0.1 Ω

• Synchronous rectification for high efficiency

• Soft start

• PWM-only operating option

• Stand-alone low battery detector requires no additional

supply voltage

• Low battery detection level at 0.90 V, externally

adjustable to a higher level

• Adjustable output voltages

• Shut-down function

• Small outline package

• 0.6 µm BICMOS process.

APPLICATIONS

• Cellular phones

• Cordless phones

• Personal Digital Assistants (PDAs)

• Portable audio players

• Pagers

• Mobile equipment.

DSon

of

TEA1200TS

GENERAL DESCRIPTION

The TEA1200TS is a fully integrated battery power unit

including a high-efficiency DC-to-DC converterwhich runs

from a 1-cell NiCd or NiMH battery and a low battery

detector. The circuit can be arranged in several ways to

optimize the application circuit of a power supply system.

Therefore, the DC-to-DC converter can be arranged for

upconversion or downconversion and the low battery

detector can be configured for several types of batteries.

Accurate low battery detection is possible while all other

blocks are switched off.

The DC-to-DC converter features efficient, compact and

dynamic power conversion using a digital control concept

comparable with Pulse Width Modulation (PWM) and

Pulse Frequency Modulation (PFM), integrated CMOS

power switches with a very low R

synchronous rectification.

The device operates at a switching frequency of 600 kHz

which enables the use of external components with

minimum size. The switching frequency can be

synchronized to an external high frequency clock signal.

Optionally, the device can be kept in PWM control mode

only. Deadlock is prevented by an on-chip undervoltage

lockout circuit.

Active current limiting enables efficient conversion in

pulsed-load systems such as Global System for Mobile

communication (GSM) and Digital Enhanced Cordless

Telecommunications (DECT).

The low battery detector has a built-in detection level

which is optimum for a 1-cell NiCd or NiMH battery.

DSon

and fully

ORDERING INFORMATION

TYPE

NUMBER

TEA1200TS SSOP16 plastic shrink small outline package; 16 leads; body width 4.4 mm SOT369-1

2002 May 14 2

NAME DESCRIPTION VERSION

PACKAGE

Philips Semiconductors Product specification

0.95 V starting DC-to-DC converter

TEA1200TS

with low battery indicator

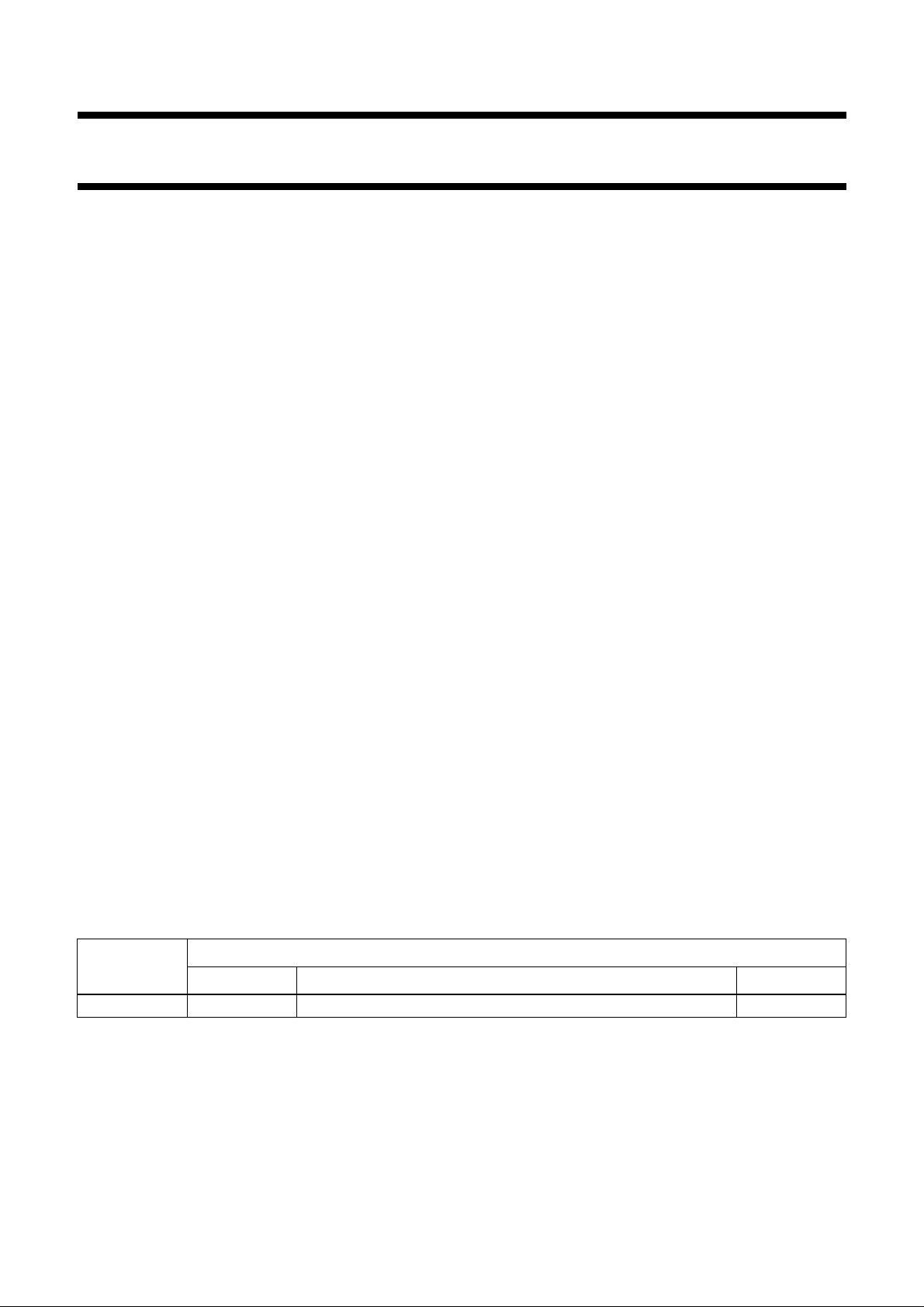

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

DC-to-DC converter

UPCONVERSION

V

i(up)

V

o(up)

V

i(start)

V

o(uvlo)

DOWNCONVERSION

V

i(dwn)

V

o(dwn)

CURRENT LEVELS

I

q(DC/DC)

I

shdwn

I

LX(max)

∆I

lim

POWER MOSFETS

R

DSon(N)

R

DSon(P)

EFFICIENCY

η efficiency upconversion see Fig.8; Voup to 3.3 V

TIMING

f

sw

f

i(sync)

t

start

General characteristics

V

ref

input voltage V

output voltage V

− 5.50 V

i(start)

− 5.50 V

o(uvlo)

start-up input voltage IL< 10 mA 0.93 0.96 1.00 V

undervoltage lockout voltage note 1 2.0 2.2 2.4 V

input voltage V

− 5.50 V

o(uvlo)

output voltage 1.30 − 5.50 V

quiescent current at pin

− 110 −µA

UPOUT/DNIN

current in shut-down mode V

maximum continuous current at

LBI1=VI(up)

T

=80°C −−1.0 A

amb

= 1.2 V − 65 −µA

pins LX1 and LX2

current limit deviation I

set to 1.0 A

lim

upconversion −12 − +12 %

downconversion −12 − +12 %

drain-to-sourceon-state resistance

Tj=27°C; IDS= 100 mA − 110 200 mΩ

NFET

drain-to-sourceon-state resistance

Tj=27°C; IDS= 100 mA − 125 250 mΩ

PFET

V

= 1.2 V; IL= 100 mA − 84 − %

i

V

= 2.4 V; IL=10mA − 92 − %

i

switching frequency PWM mode 480 600 720 kHz

synchronization clock input

6 1320MHz

frequency

start-up time − 10 − ms

reference voltage 1.165 1.190 1.215 V

Note

1. The undervoltage lockoutlevel showswide specification limits since it decreases withincreasing temperature.When

the temperature increases, the minimum supply voltage of the digital control part of the IC decreases and therefore

thecorrect operation of this functionis guaranteed overthe whole temperaturerange. The undervoltagelockout level

is measured at pin UPOUT/DNIN.

2002 May 14 3

Philips Semiconductors Product specification

0.95 V starting DC-to-DC converter

with low battery indicator

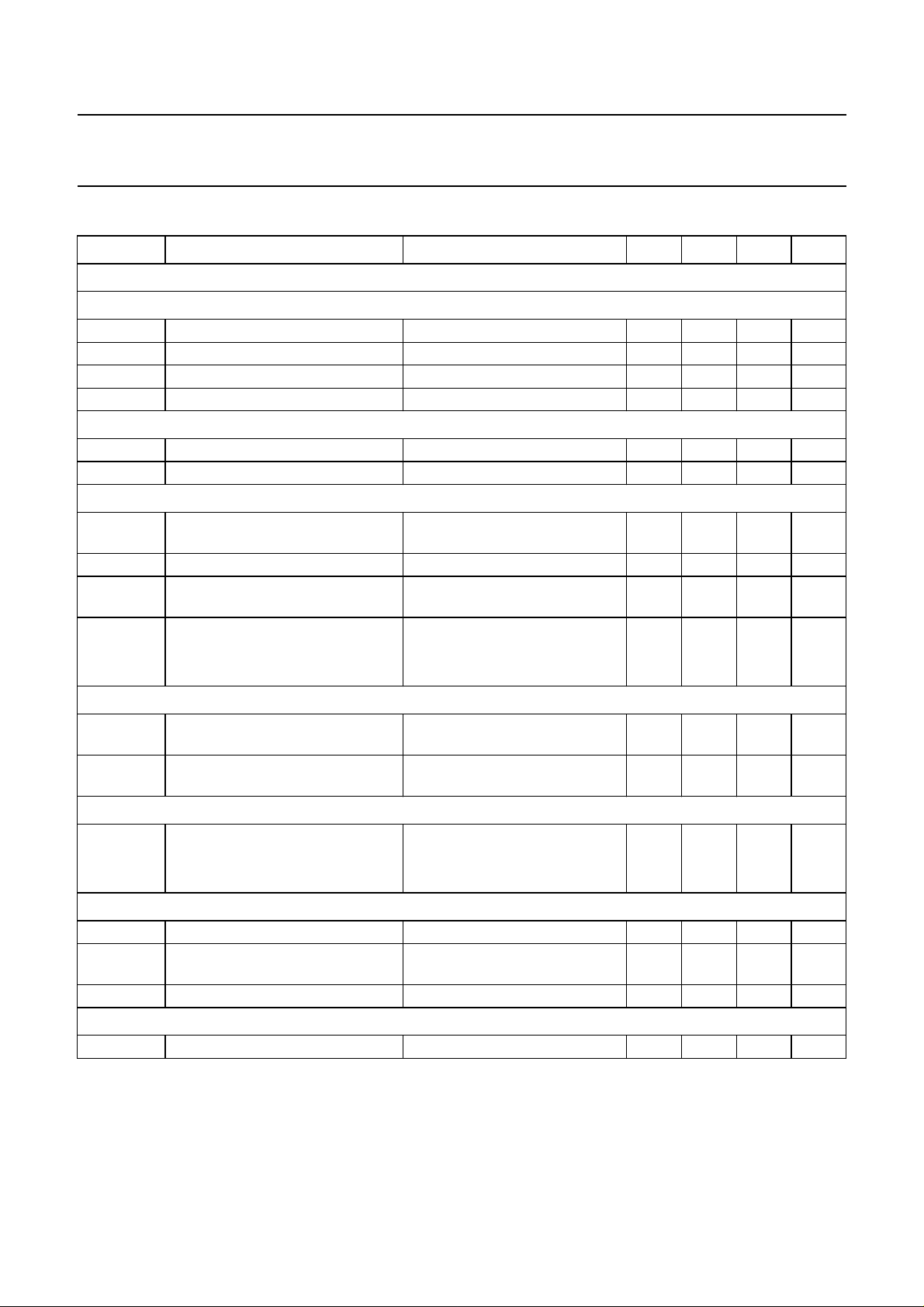

BLOCK DIAGRAM

UPOUT/DNIN

n.c.

3

6

UPOUT/DNIN

4

INTERNAL

SUPPLY

8

GND

TEA1200TS

FB0

12

ref

V

ref

V

11

VOLT AGE

REFERENCE

ref

V

7

MBL409

TEA1200TS

9

TIME

COUNTER

AND

CIRCUIT

START-UP

sense FET

P-type POWER FET

DETECTOR

LOW BATTERY

1

10

5

16

MODE GEARBOX

CONTROL LOGIC

COMPARATOR

CURRENT LIMIT

ref

V

TEMPERATURE

N-type

POWER

PROTECTION

FET

FET

sense

DIGITAL CONTROLLER

GATE

SYNC

13 MHz

OSCILLATOR

SHDWN0

1413 2 15

SYNC/PWM U/D

GND0

Fig.1 Block diagram.

handbook, full pagewidth

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

2002 May 14 4

LBI1

LBO

LX1

LX2

ILIM

Philips Semiconductors Product specification

0.95 V starting DC-to-DC converter

with low battery indicator

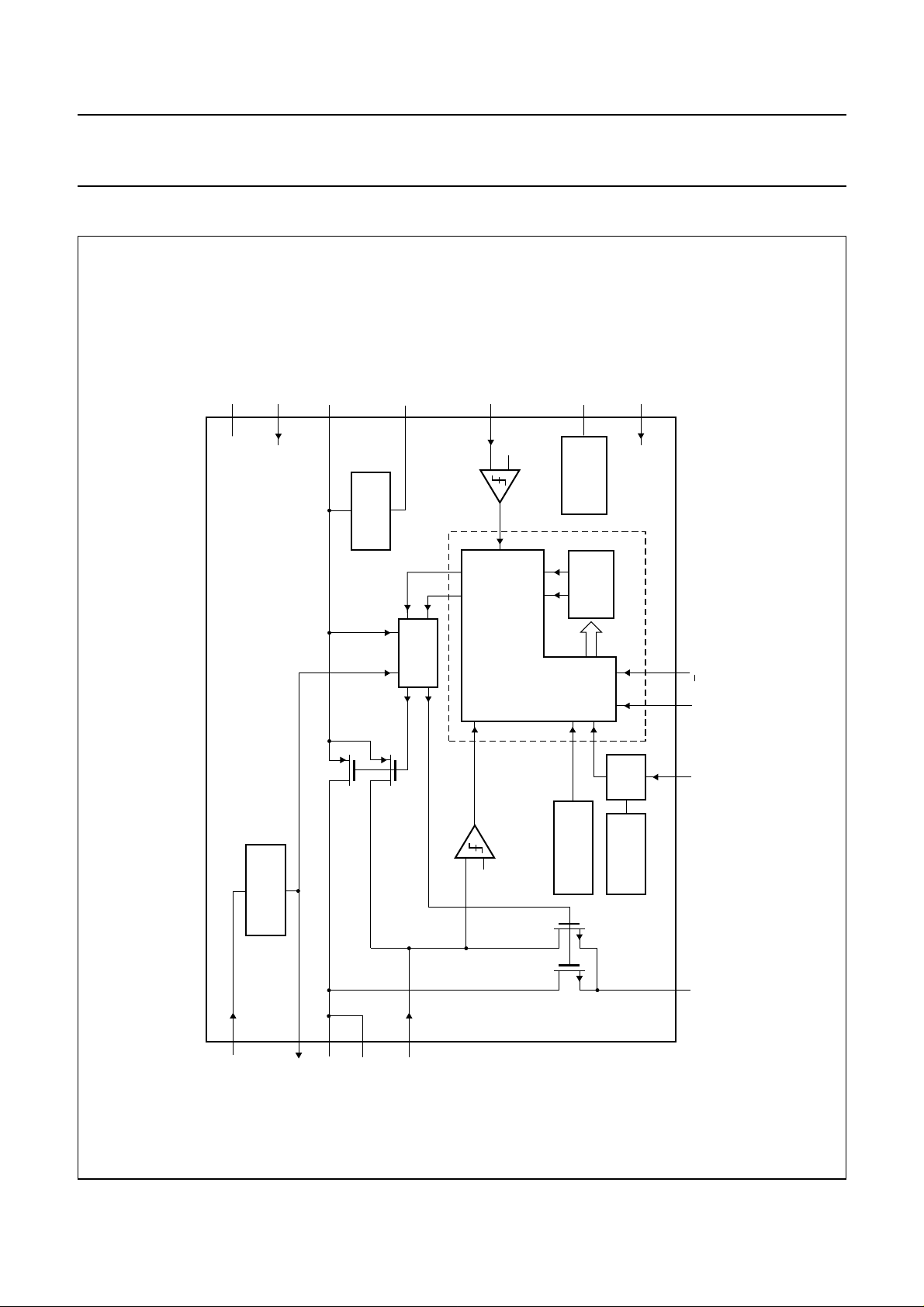

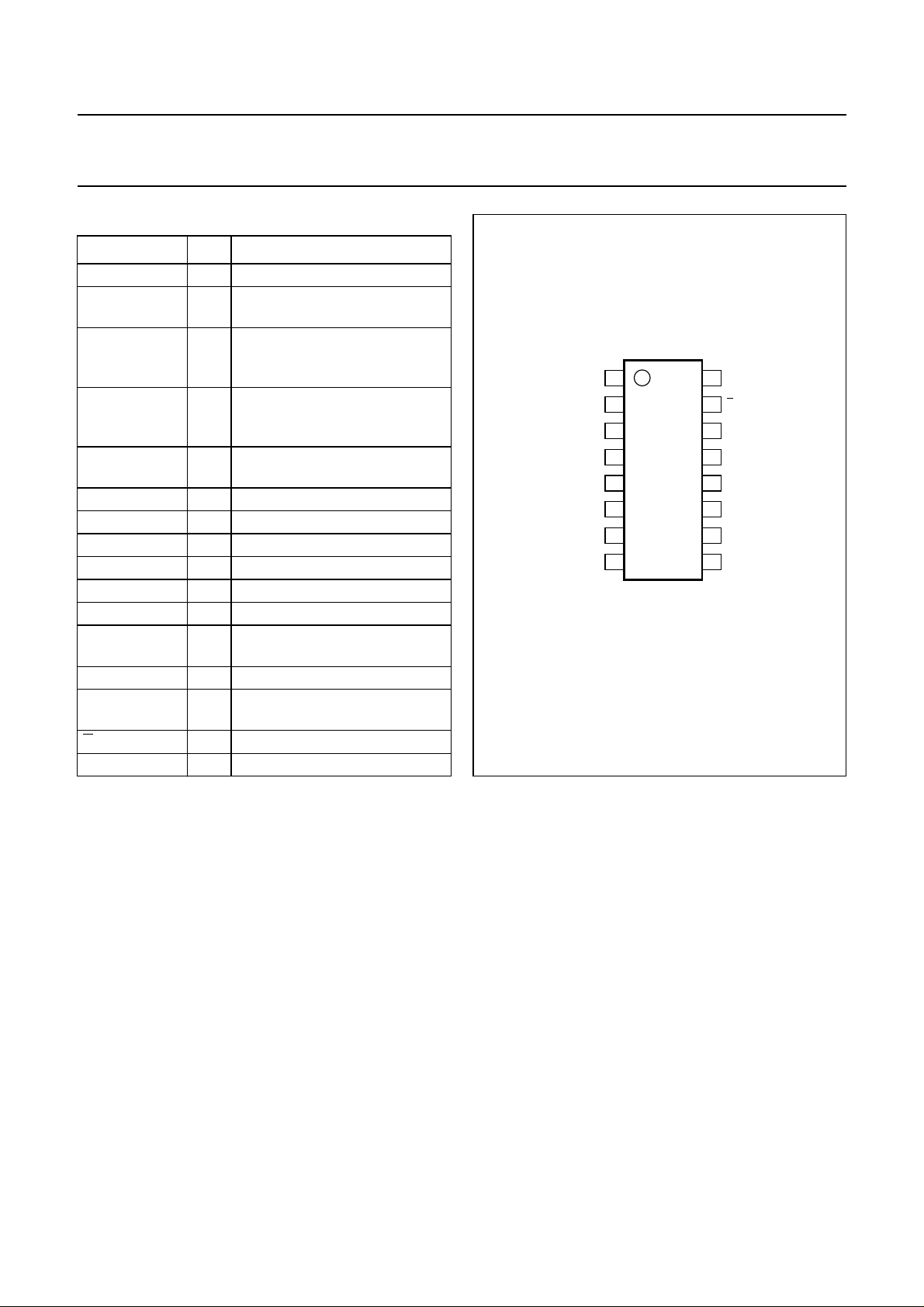

PINNING

SYMBOL PIN DESCRIPTION

LX1 1 inductor connection 1

SHDWN0 2 DC-to-DC converter shut-down

input

UPOUT/DNIN 3 up mode: DC-to-DC converter

output; down mode DC-to-DC

converter input

UPOUT/DNIN 4 up mode: DC-to-DC converter

output; down mode DC-to-DC

converter input

ILIM 5 current limiting resistor

connection

n.c. 6 not connected

V

ref

GND 8 internal supply ground

LBI1 9 low battery detector input 1

LBO 10 low battery detector output

V

ref

FB0 12 DC-to-DC converter feedback

GND0 13 DC-to-DC converter ground

SYNC/PWM 14 synchronization clock input or

U/D 15 conversion mode selection input

LX2 16 inductor connection 2

7 reference voltage input

11 reference voltage input

input

PWM-only selection input

handbook, halfpage

UPOUT/DNIN

UPOUT/DNIN

LX1

1

SHDWN0

ILIM

n.c.

V

ref

GND

2

3

4

TEA1200TS

5

6

7

8

Fig.2 Pin configuration.

TEA1200TS

LX2

16

U/D

15

14

SYNC/PWM

13

GND0

12

FB0

11

V

ref

10

LBO

9

LBI1

MBL419

FUNCTIONAL DESCRIPTION

Control mechanism

The TEA1200TS DC-to-DC converter is able to operate in

the PFM (discontinuous conduction) or PWM (continuous

conduction) operating mode. All switching actions are

completely determined by a digital control circuit which

usesthe output voltage levelasits control input. Thisnovel

digital approach enables the use of a new pulse width and

frequency modulation scheme, which ensures optimum

power efficiency over the complete range of operation of

the converter.

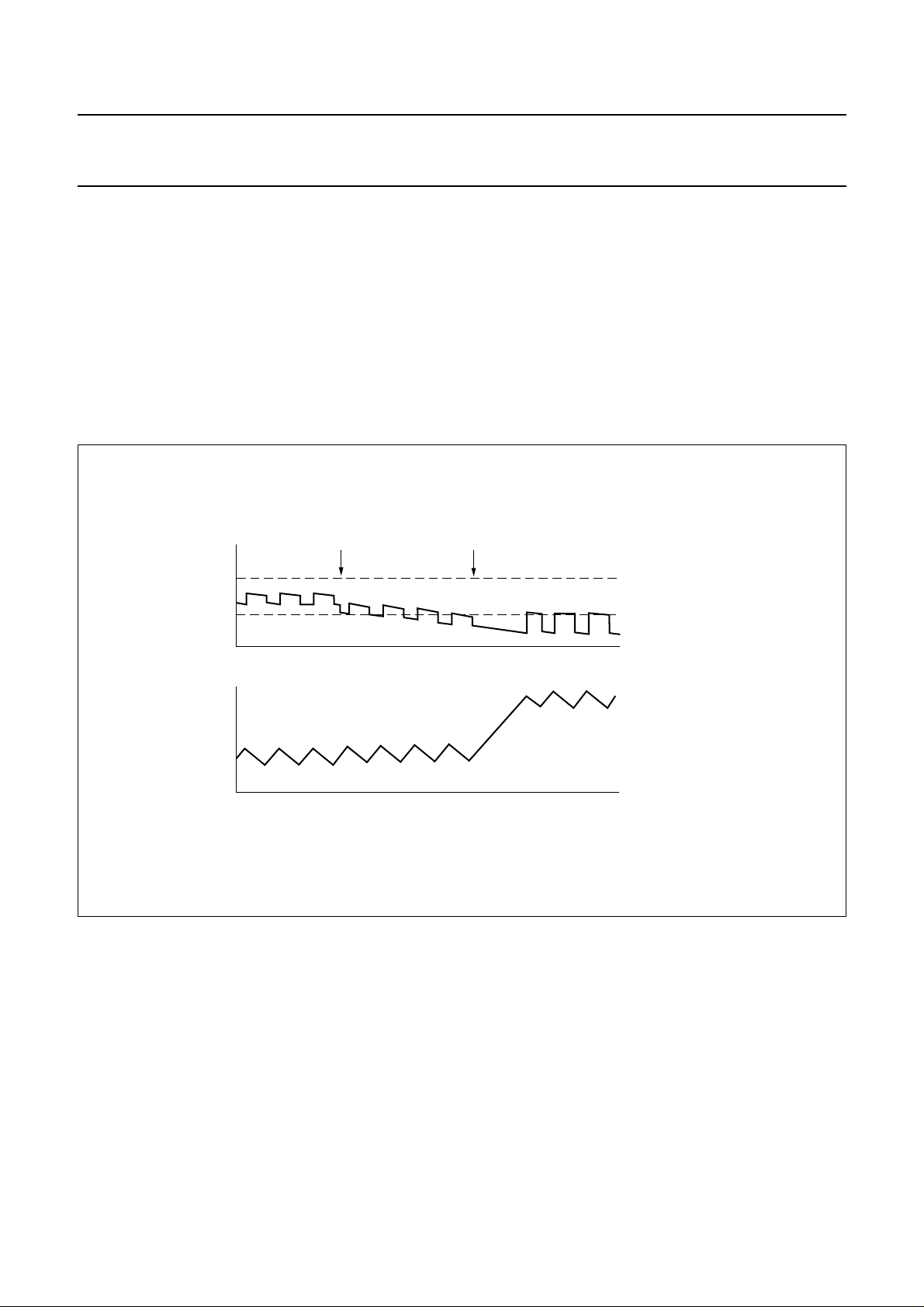

When high output power is requested, the device will

operate in the PWM operating mode. This results in

minimumAC currents in the circuitcomponentsandhence

optimum efficiency, minimum costs and low EMC. In this

operating mode, the output voltage is allowed to vary

between two predefined voltage levels. As long as the

output voltage stays within this so-called window,

switching continues in a fixed pattern.

2002 May 14 5

When the output voltage reaches one of the window

borders, the digital controller immediately reacts by

adjusting the pulse width and inserting a current step in

such a waythat the output voltage stayswithin the window

with higher or lower current capability. This approach

enables very fast reaction to load variations. Figure 3

shows the response of the converter to a sudden load

increase. The upper trace shows the output voltage.

The ripple on top of the DC level is a result of the current

in the output capacitor, which changes in sign twice per

cycle, times the internal Equivalent Series Resistance

(ESR) of the capacitor. After each ramp-down of the

inductor current, i.e. when the ESR effect increases the

output voltage, the converter determines what to do in the

next cycle. As soon as more load current istaken from the

output the output voltage starts to decay.

Philips Semiconductors Product specification

0.95 V starting DC-to-DC converter

with low battery indicator

When the output voltage becomes lower than the low limit

of the window, a corrective actionis taken by a ramp-up of

theinductor current duringa much longertime. As aresult,

the DC current level is increasedand normalPWM control

can continue. The output voltage (including ESR effect) is

again within the predefined window.

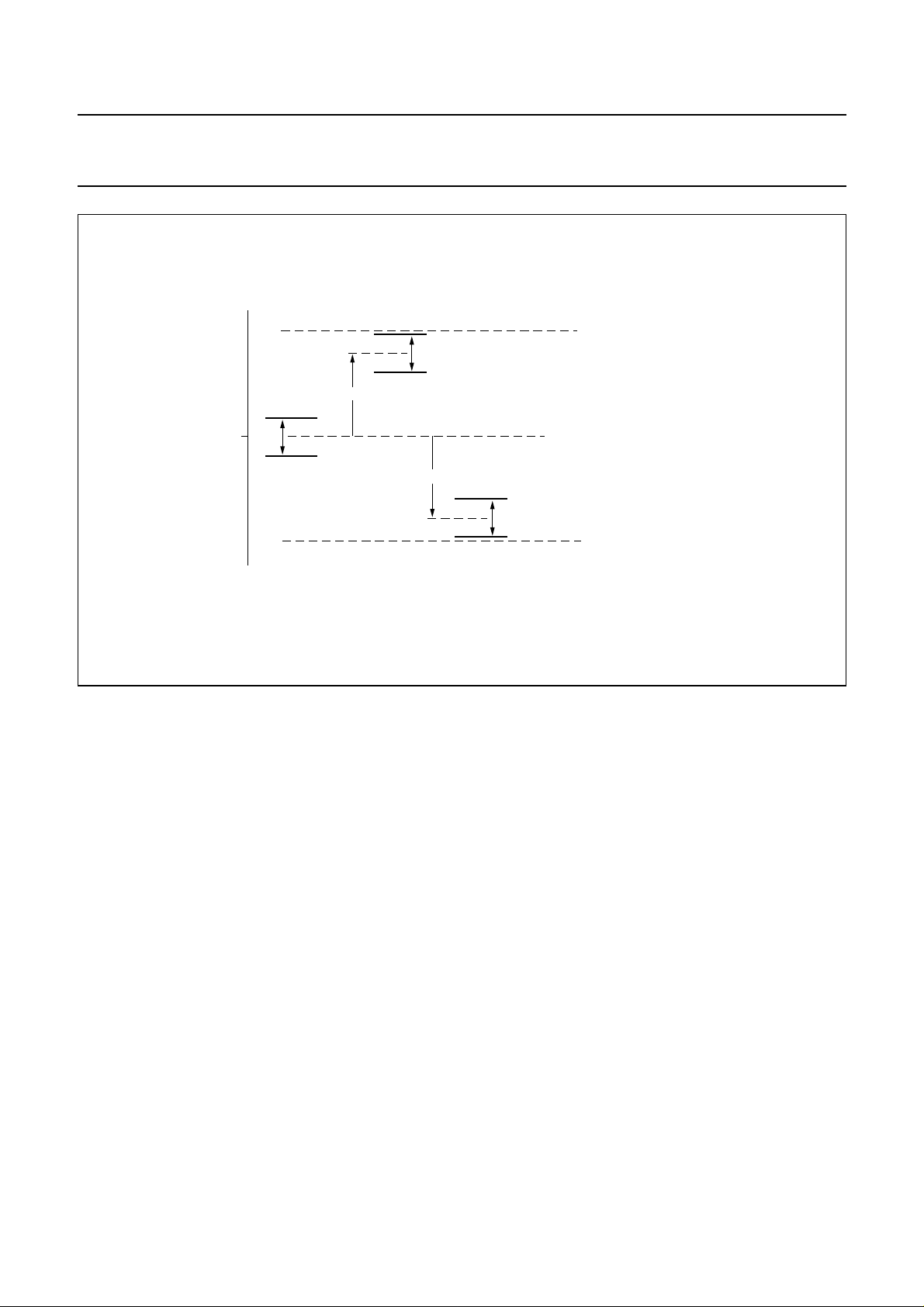

Figure 4 shows the spread of the output voltage window.

The absolute value is mostly dependent on spread, while

the actual window size [V

wdw(high)

affected. For one specific device, the output voltage will

not vary more than 2% (typical value).

handbook, full pagewidth

V

o

− V

wdw(low)

load increase

] is not

start corrective action

TEA1200TS

In low output power situations, the TEA1200TS will switch

over to PFM operating mode. In this mode, regulation

information from an earlier PWM operating mode is used.

This results in optimum inductor peak current levels in the

PFM mode, which are slightly larger than the inductor

ripple current in the PWM mode. As a result, the transition

between PFM and PWM mode is optimum under all

circumstances. In the PFM mode the TEA1200TS

regulates the output voltage to the high window limit as

shown in Fig.3.

high window limit

low window limit

time

I

L

time

MGK925

Fig.3 Response to load increase.

2002 May 14 6

Philips Semiconductors Product specification

0.95 V starting DC-to-DC converter

with low battery indicator

handbook, full pagewidth

V

O (typ)

V

wdw(high)

2%

V

wdw(low)

typical situation

maximum positive spread of V

+2%

V

wdw(high)

V

wdw(low)

maximum negative spread of V

2%

−2%

O

V

wdw(high)

V

wdw(low)

2%

upper specification limit

lower specification limit

O

TEA1200TS

MGU269

Fig.4 Output voltage window spread.

Synchronous rectification

For optimum efficiency over the whole load range,

synchronous rectifiers within the TEA1200TS ensure that

during the whole second switching phase, all inductor

current will flow through the low-ohmic power MOSFETs.

Special circuitry is included which detects when the

inductorcurrentreaches zero. Followingthisdetection,the

digital controller switches off the power MOSFET and

proceeds with regulation.

Start-up

Start-up from low input voltage in the boost mode is

realized by anindependent start-up oscillator,which starts

switching the N-type power MOSFET as soon as the

low-battery detector detects a sufficiently high voltage.

The inductor current is limited internally to ensure

soft-starting. The switch actions of the start-up oscillator

will increase the output voltage. As soon as the output

voltage is high enough for normal regulation, the digital

control system will take control over the power MOSFETs.

Undervoltage lockout

As a result of too high a load or disconnection of the input

power source, the output voltage can drop so low that

normal regulation cannot beguaranteed. In this event, the

device switches back to start-up mode. If the output

voltage drops even further, switching is stopped

completely.

Shut-down

When the shut-down input is set HIGH, the DC-to-DC

converter disables both switches and power consumption

is reduced to a few microamperes.

Power switches

The power switches in the IC are one N-type and one

P-type power MOSFET, both having a typical

drain-to-source resistance of 100 mΩ. The maximum

continuous current in the power switches is 1.0 A at

T

=80°C.

amb

2002 May 14 7

Philips Semiconductors Product specification

0.95 V starting DC-to-DC converter

with low battery indicator

Temperature protection

When the DC-to-DC converter operates in the PWM

mode, and thedie temperaturegets toohigh (typical value

is 190 °C), the converter will stop operating. It resumes

operation when the die temperature falls below 90 °C

again. As a result, low frequency cycling between the on

and off state willoccur. It should be noted that in the event

of device temperatures at the cut-off limit, the application

differs strongly from maximum specifications.

Current limiters

If the current in one of the power switches exceeds the

programmed limit in the PWM mode, the current ramp is

stopped immediately and the next switching phase is

entered. Current limiting is required to keep power

conversion efficient during temporary high loads.

Furthermore, current limiting protects the IC against

overload conditions, inductor saturation, etc.

The current limiting level is set by an external resistor

whichmust be connected betweenpin ILIMand ground for

downconversion, or betweenpins ILIM and UPOUT/DNIN

for upconversion.

External synchronization and PWM-only mode

If an external high-frequency clock or a HIGH level is

applied to pin SYNC/PWM, the TEA1200TSwill usePWM

regulation independent of the load applied.

In the event that a high-frequency clock is applied, the

switching frequency in the PWM mode will be exactly that

frequency divided by 22. In the PWM mode the quiescent

current of the device increases.

In the event that no external synchronization or PWM

mode selection is necessary, pin SYNC/PWM must be

connected to ground.

TEA1200TS

Behaviour when the input voltage exceeds the

specified range

In general, an inputvoltage exceeding the specified range

isnot recommended sinceinstability may occur.There are

two exceptions:

1. Upconversion: at an input voltage higher than the

targetoutput voltage, butupto 5.5 V, theconverter will

stop switching and the external Schottky diode will

take over. The output voltage will equal the input

voltageminus thediode voltage drop.Since all current

flows through the external diode in this situation, the

current limiting function is not active.

In the PWM mode, the P-type power MOSFET is

always on when the input voltage exceeds the target

output voltage. The internal synchronous rectifier

ensures that the inductor current does not fall below

zero. As a result, the achieved efficiency is higher in

this situation than standard PWM-controlled

converters achieve.

2. Downconversion: when the input voltage islower than

the target output voltage, but higher than 2.2 V, the

P-type power MOSFET will stay conducting resulting

in the output voltage being equal to the input voltage

minussomeresistive voltage drop. Thecurrentlimiting

function remains active.

Low battery detector

The low battery detector is an autonomous circuit which

can work at an input voltage down to 0.90 V. It is always

on, even when all other blocks are in the shut-down mode.

The low battery input (pin LBI1) is adjusted to accept a

1-cell NiCd or NiMH battery voltage directly. Hysteresis is

included for proper operating.

The output of the low battery detector (pin LBO) is an

open-collector output. The output is high (i.e. no current is

sunk by the collector) when the input voltage of the

detector is below the lower detection level.

2002 May 14 8

Loading...

Loading...