Philips TDA9855WP, TDA9855 Datasheet

INTEGRATED CIRCUITS

DATA SH EET

TDA9855

2

I

C-bus controlled BTSC stereo /

SAP decoder and audio processor

Preliminary specification

File under Integrated Circuits, IC02

July 1994

Philips Semiconductors Preliminary specification

I2C-bus controlled BTSC stereo / SAP

decoder and audio processor

FEATURES

• Quasi alignment-free BTSC stereo decoder due to auto

adjustment of channel separation via I2C-bus

• High integration level with automatically tuned

integrated filters

• Input level adjustment I2C-bus controlled

• Alignment-free SAP processing

• dbx noise reduction circuit

• Audio processor

– Selector for internal and external signals (line in)

– Automatic volume level control

– Subwoofer or surround output with separate volume

control

– Volume control

– Special loudness characteristic automatically

controlled in combination with volume setting

TDA9855

– Bass and treble control

– Audio signal zero crossing detection between any

volume step switching

• Mute control at audio signal zero crossing

2

• I

C-bus transceiver.

GENERAL DESCRIPTION

The TDA9855 is a bipolar-integrated BTSC stereo / SAP

decoder with hi-fi audio processor (I

application in TV sets.

2

C-bus controlled) for

ORDERING INFORMATION

P ACKAGE

EXTENDED TYPE NUMBER

PINS

TDA9855 52 SHDIL plastic SOT247AH

TDA9855WP 68 PLCC plastic SOT188CG

Note

1. SOT247-1; 1996 December 5.

2. SOT188-2; 1996 December 5.

A license is required for this product. For further information, please contact:

THAT Corporation

Licensing Operations

734 Forest St.

Marlborough, MA 01752

USA

Tel. (508) 229-2500

Fax: (508) 229-2590

THAT Corporation

Tokyo Office

405 Palm House, 1-20-2 Honmachi

Shibuya-ku, Tokyo 151

Japan

Tel: (03) 3378-0915

Fax: (03) 3374-5191

PIN

POSITION

MA TERIAL CODE

(1)

(2)

July 1994 2

Philips Semiconductors Preliminary specification

I2C-bus controlled BTSC stereo / SAP

decoder and audio processor

TDA9855

July 1994 3

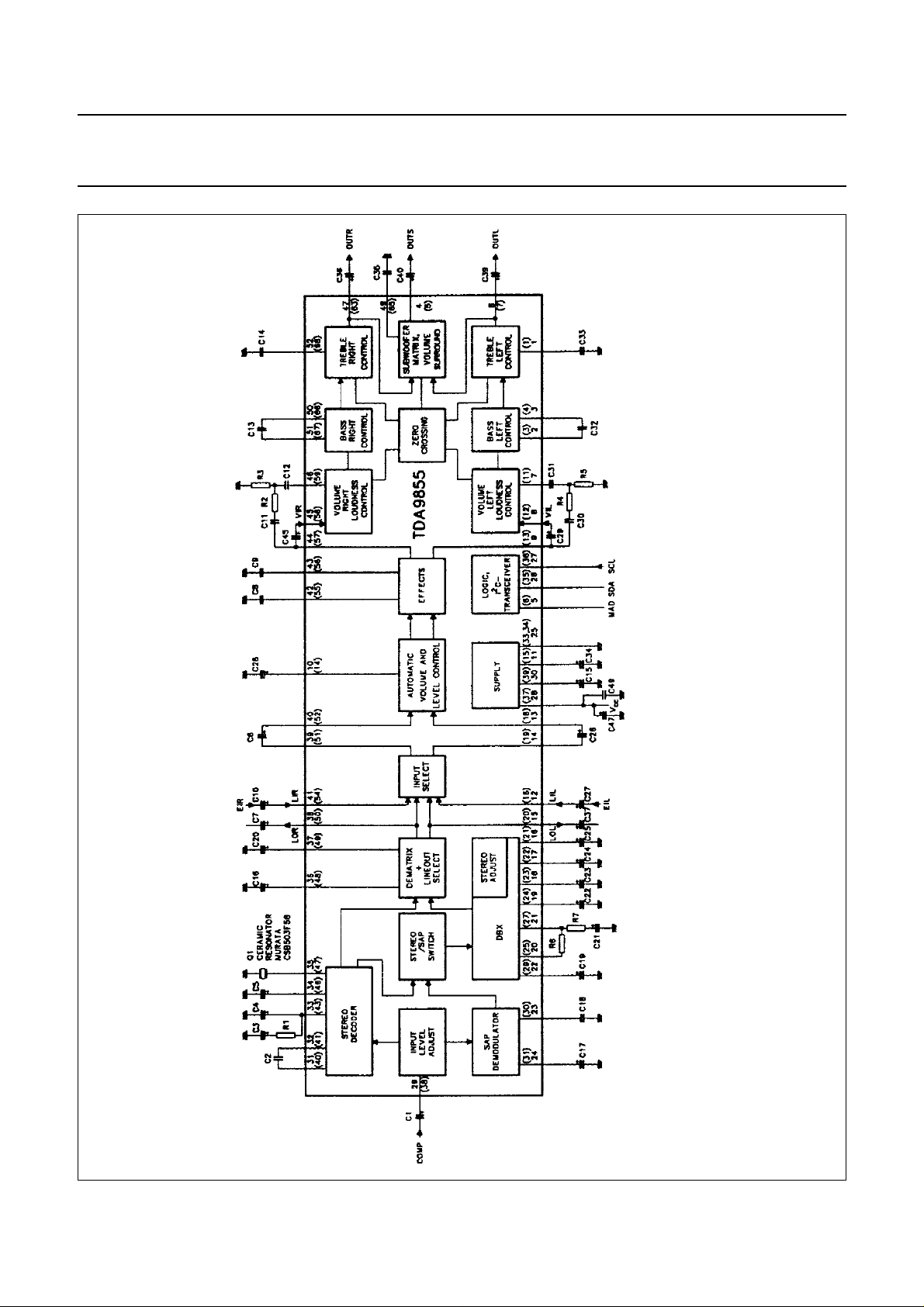

Fig.1 Block, application and test diagram (PLCC pinning in parenthesis).

Philips Semiconductors Preliminary specification

I2C-bus controlled BTSC stereo / SAP

decoder and audio processor

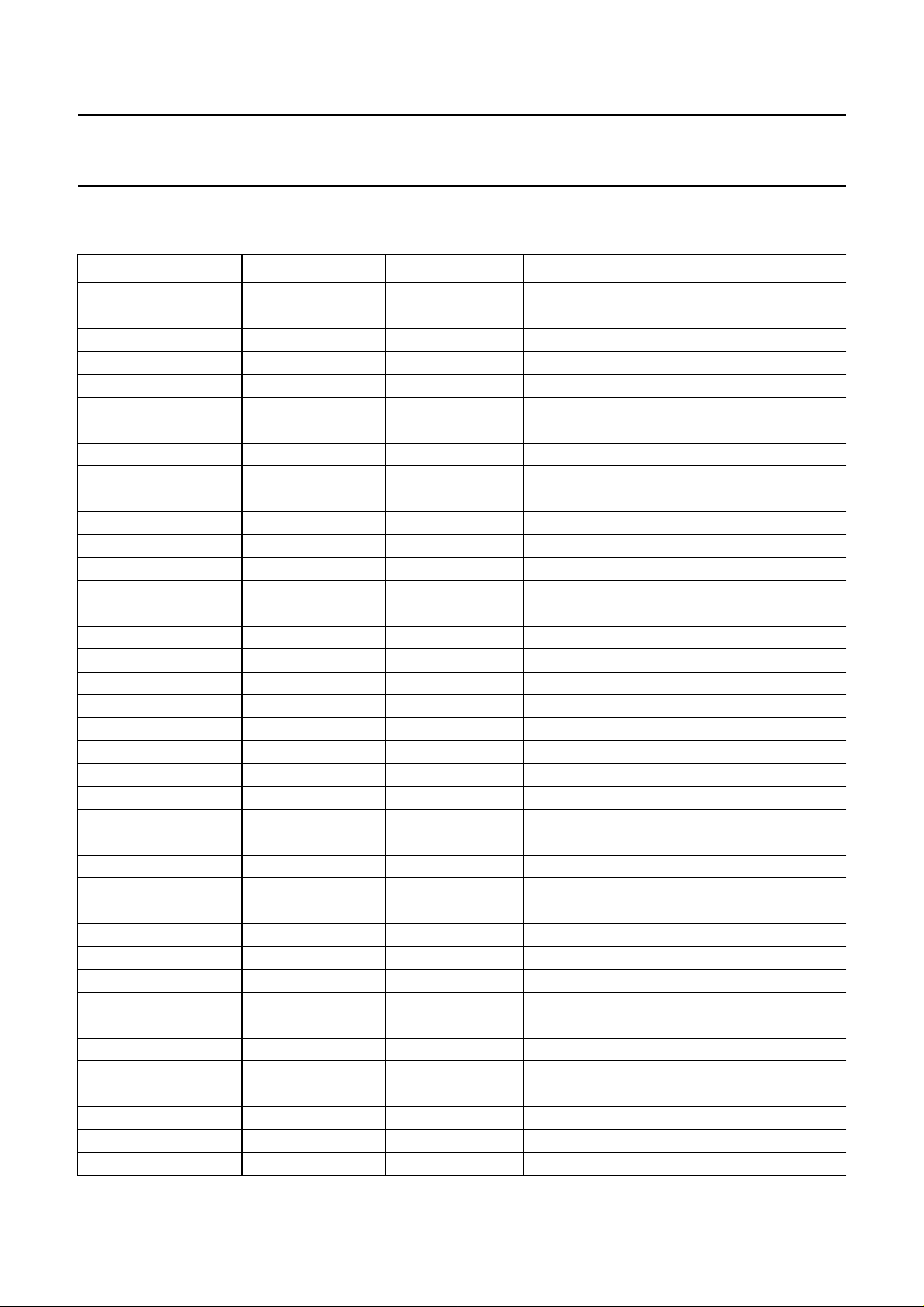

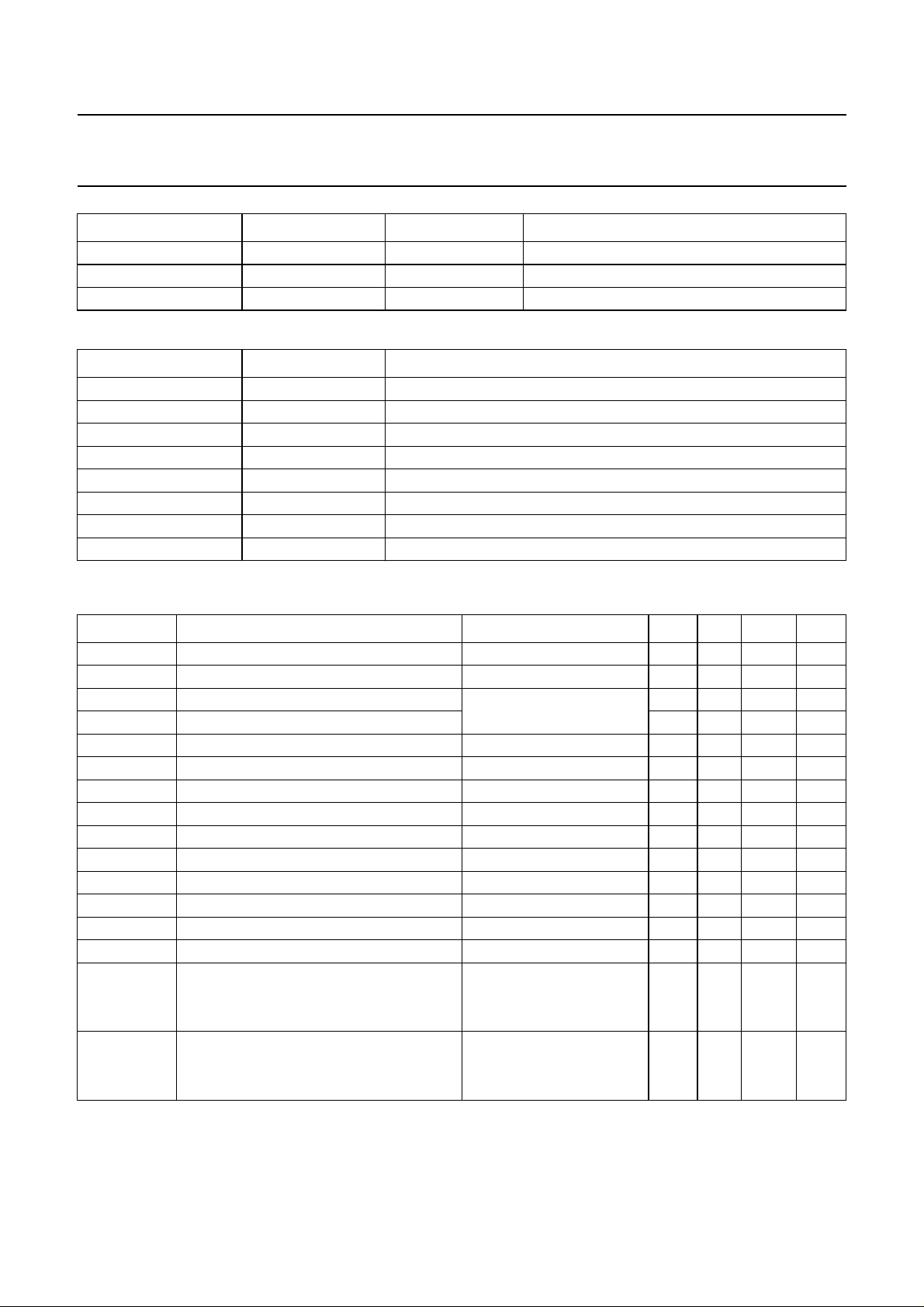

COMPONENT LIST

elco ±20%; foil or ceramic ± 10%; resistors ±5% unless otherwise specified.

COMPONENT VALUE TYPE REMARK

C1 10 µF elco 63 V

C2 470 nF foil

C3 4.7 µF elco 63 V

C4 220 nF foil

C5 10 µF elco 63 V; l

C6 2.2 µF elco 16 V

C7 4.7 µF elco 16 V

C8 15 nF foil ±5%

C9 15 nF foil ±5%

C10 2.2 µF elco 63 V

C11 8.2 nF foil or ceramic ±5% SMD 2220/1206

C12 150 nF foil ±5%

C13 33 nF foil ±5%

C14 5.6 nF foil or ceramic ±5% SMD 2220/1206

C15 100 µF elco 16 V

C16 4.7 µF elco 63 V

C17 4.7 µF elco 63 V

C18 100 nF foil

C19 10 µF elco 63 V

C20 4.7 µF elco 63 V

C21 47 nF foil ±5%

C22 1 µF elco 63 V

C23 1 µF elco 63 V

C24 10 µF elco 63 V ± 10%

C25 10 µF elco 63 V ± 10%

C26 2.2 µF elco 16 V

C27 2.2 µF elco 63 V

C28 4.7 µF elco 63 V ± 10%

C29 2.2 µF elco 16 V

C30 8.2 nF foil or ceramic ±5% SMD 2220/1206

C31 150 nF foil ±5%

C32 33 nF foil ±5%

C33 5.6 nF foil or ceramic ±5% SMD 2220/1206

C34 100 µF elco 16 V

C35 150 nF foil ±5%

C36 4.7 µF elco 16 V

C37 4.7 µF elco 16 V

C39 4.7 µF elco 16 V

C40 4.7 µF elco 16 V

leak

< 1.5 µA

TDA9855

July 1994 4

Philips Semiconductors Preliminary specification

I2C-bus controlled BTSC stereo / SAP

decoder and audio processor

COMPONENT VALUE TYPE REMARK

C45 2.2 µF elco 16 V

C47 220 µF elco 25 V

C49 100 nF foil or ceramic SMD 1206

COMPONENT VALUE REMARK

R1 2.2 KΩ

R2 20 KΩ

R3 2.2 KΩ

R4 20 KΩ

R5 2.2 KΩ

R6 8.2 KΩ±2%

R7 160 KΩ±2%

Q1 503.5 kHz MURATA CSB503F58

TDA9855

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

CC

I

CC

V

comp

V

LOR

G

LA

α

st

THD

V

I, O

, V

L, R

LOL

supply voltage 8.0 8.5 9.0 V

supply current 50 75 95 mA

input signal (RMS value) 100% modulation L + R;

output signal (RMS value) − 500 − mV

f = 300 Hz

− 250 − mV

input level adjustment control range −3.5 −+4.0 dB

stereo channel separation fL= 300 Hz; fR= 3 kHz 25 35 − dB

total harmonic distortion f = 1 kHz − 0.2 − %

signal handling (RMS value) THD < 0.5% 2 −− V

AVL control range −15 −+6dB

G

c

L

B

G

b

G

t

G

v

volume control range −71 −+16 dB

maximum loudness boost f = 40 Hz − 17 − dB

bass control range f = 40 Hz −12 −+16.5 dB

treble control range f = 15 kHz −12 −+12 dB

subwoofer control range f = 40 Hz −14 −+14 dB

S/N signal-to-noise ratio line out (mono);

= 0.5 V (RMS)

V

CCIR noise weighting filter (peak value) − 60 − dB

O

DIN noise weighting filter (RMS value) − 73 − dBA

S/N signal-to-noise ratio audio section;

V

= 2 V (RMS);

CCIR noise weighting filter (peak value) − 94 − dB

DIN noise weighting filter (RMS value) − 107 − dBA

O

gain = 0 dB

July 1994 5

Philips Semiconductors Preliminary specification

I2C-bus controlled BTSC stereo / SAP

decoder and audio processor

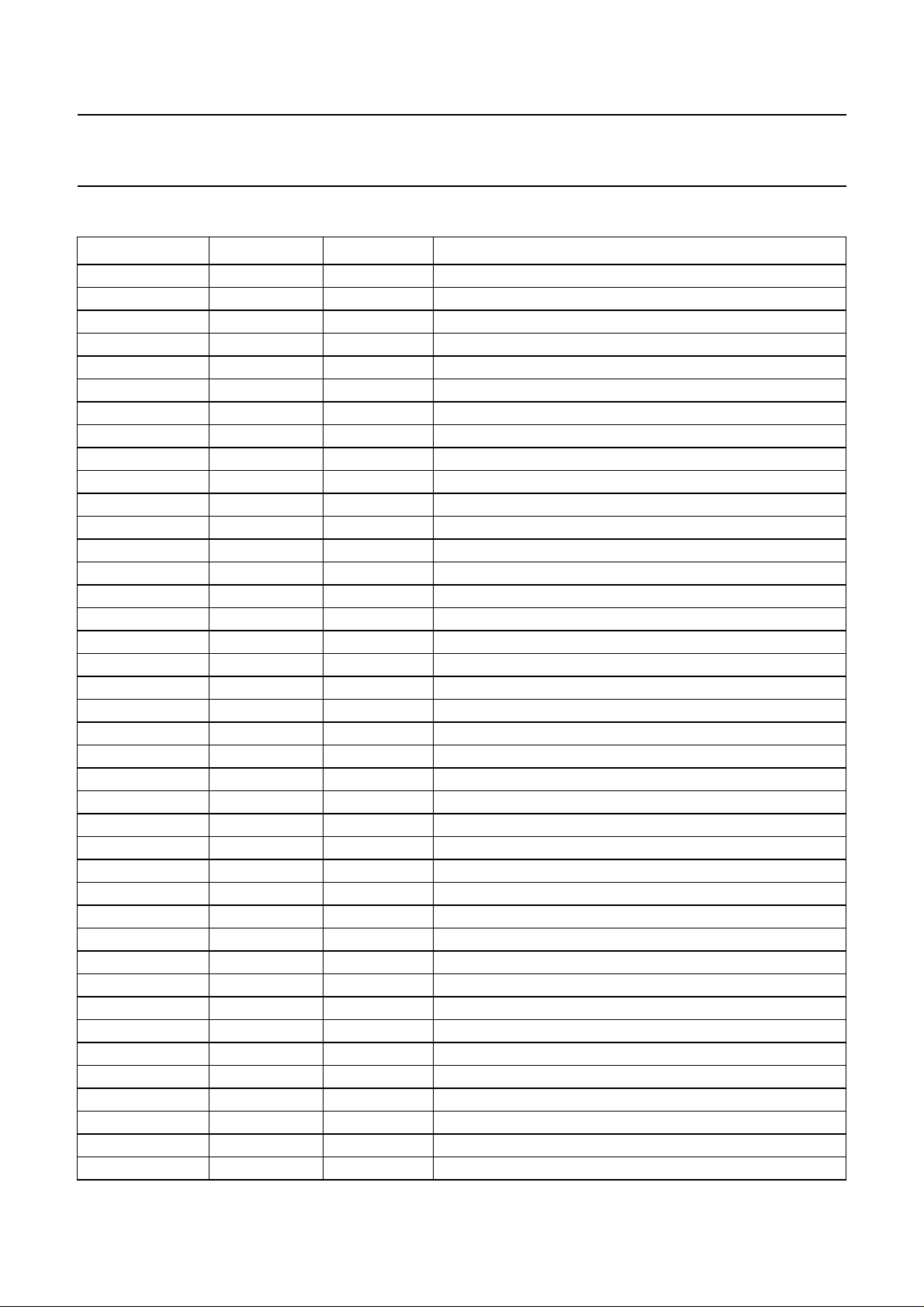

PINNING

SYMBOL SOT188 SOT247 DESCRIPTION

TL 1 1 treble control capacitor, left channel

n.c. 2 − not connected

B1L 3 2 bass control capacitor, left channel

B2L 4 3 bass control capacitor, left channel

OUTS 5 4 output subwoofer or output surround sound

MAD 6 5 programmable address bit (module address)

OUTL 7 6 output, left channel

n.c. 8 to 10 − not connected

LDL 11 7 input loudness, left channel

VIL 12 8 input volume control, left channel

EOL 13 9 output effects, left channel

CAV 14 10 automatic volume control capacitor

V

REF

LIL 16 12 line input, left channel

n.c. 17 − not connected

AVL 18 13 input automatic volume control, left channel

SOL 19 14 output selector, left channel

LOL 20 15 line output, left channel

TW 21 16 capacitor timing wideband for dbx

TS 22 17 capacitor timing spectral for dbx

CW 23 18 capacitor wideband for dbx

CS 24 19 capacitor spectral for dbx

VEO 25 20 variable emphasis out for dbx

n.c. 26 − not connected

VEI 27 21 variable emphasis in for dbx

n.c. 28 − not connected

CNR 29 22 capacitor noise reduction for dbx

CM 30 23 capacitor mute for SAP

CD 31 24 capacitor DC decoupling for SAP

n.c. 32 − not connected

GND 33 − analog ground

GND 34 − digital ground

GND − 25 common ground

SDA 35 26 serial data input/output

SCL 36 27 serial clock input

V

CC

COMP 38 29 input composite signal

VCAP 39 30 capacitor for electronic filtering of supply

CP1 40 31 capacitor for pilot detector

CP2 41 32 capacitor for pilot detector

15 11 reference voltage 0.5V

37 28 supply voltage

CC

TDA9855

July 1994 6

Philips Semiconductors Preliminary specification

I2C-bus controlled BTSC stereo / SAP

decoder and audio processor

SYMBOL SOT188 SOT247 DESCRIPTION

n.c. 42 − not connected

CPH 43 33 capacitor for phase detector

n.c. 44, 45 − not connected

CA 46 34 capacitor for filter adjust

CER 47 35 ceramic resonator

CMO 48 36 capacitor DC decoupling mono

CSS 49 37 capacitor DC decoupling stereo/SAP

LOR 50 38 line output, right channel

SOR 51 39 output selector, right channel

AVR 52 40 input automatic volume control, right channel

n.c. 53 − not connected

LIR 54 41 line input, right channel

PS2 55 42 capacitor 2 pseudo function

PS1 56 43 capacitor 1 pseudo function

EOR 57 44 output effects, right channel

VIR 58 45 input volume control, right channel

LDR 59 46 input loudness, right channel

n.c. 60 to 62 − not connected

OUTR 63 47 output, right channel

n.c. 64 48 not connected

SW 65 49 filter capacitor for subwoofer

B2R 66 50 bass control capacitor, right channel

B1R 67 51 bass control capacitor, right channel

TR 68 52 treble control capacitor

TDA9855

July 1994 7

Philips Semiconductors Preliminary specification

I2C-bus controlled BTSC stereo / SAP

decoder and audio processor

TDA9855

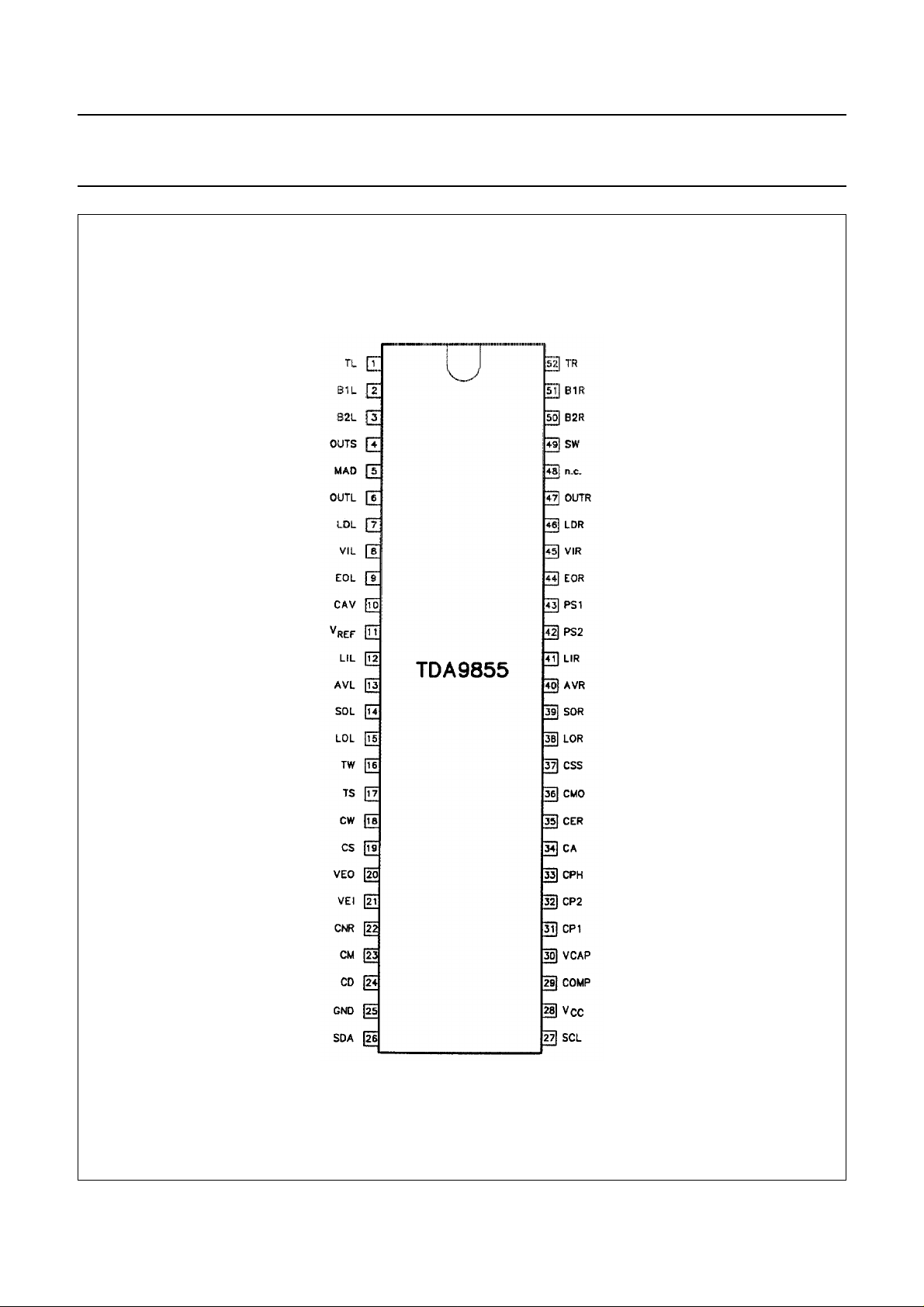

Fig.2 Pin configuration for SHRDIL-version.

July 1994 8

Philips Semiconductors Preliminary specification

I2C-bus controlled BTSC stereo / SAP

decoder and audio processor

TDA9855

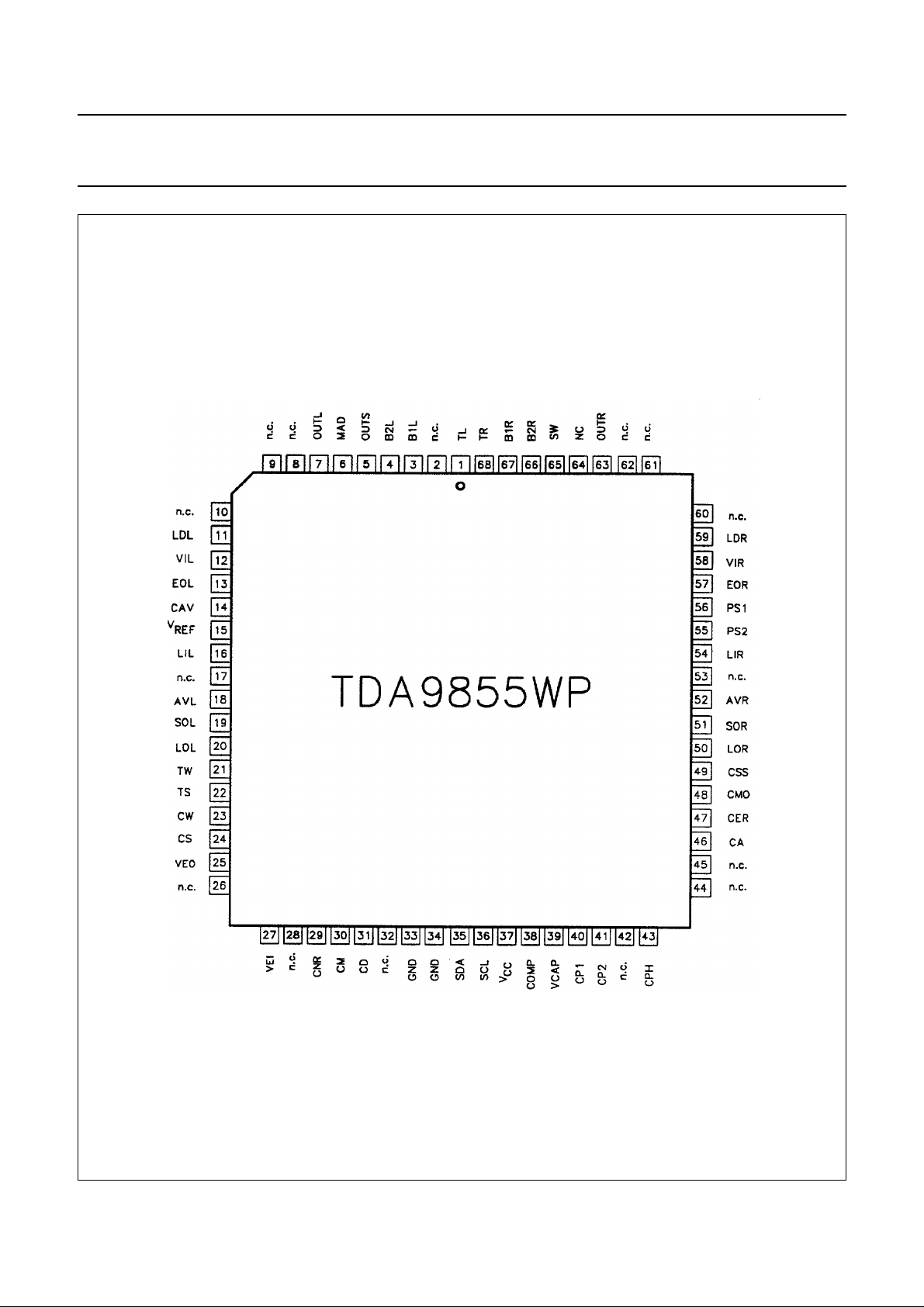

Fig.3 Pin configuration for PLCC-version.

July 1994 9

Philips Semiconductors Preliminary specification

I2C-bus controlled BTSC stereo / SAP

decoder and audio processor

FUNCTIONAL DESCRIPTION

Decoder

Input level adjustment

The composite input signal is fed to the input level

adjustment stage. In order to compensate tolerances of

the FM demodulator which supplied the composite input

signal, the TDA9855 provides an input level adjustment

stage. The control range is between −3.5 dB and +4.0 dB

in steps of 0.5 dB. The subaddress control 3 of Tables 2

and 3 and the level adjust setting of Table 16 allows an

optimal signal adjustment during the set alignment in the

production line. This value has to be stored in a none

volatile memory. The maximum input signal voltage is 2 V

(RMS).

Stereo decoder

The output signal of the level adjustment stage is coupled

to a low-pass filter which suppresses the baseband noise

above 125 kHz. The composite signal is then fed into a

pilot detector/pilot cancellation circuit and into the MPX

demodulator. The main L + R signal passes a 75 µs fixed

de-emphasis filter and is fed into the dematrix circuit. The

decoded subsignal L − R is sent to the stereo/SAP switch.

To generate the pilot signal the stereo demodulator uses a

PLL circuit including a ceramic resonator. The stereo

channel separation can be adjusted by an automatic

procedure or manually. A detailed description of this

alignment is provided in the ADJUSTMENT

PROCEDURE. The stereo identification can be read by

2

the I

C-bus (see Table 1). Two different pilot thresholds

can be selected via I2C-bus (see Table 18).

SAP demodulator

The composite signal is fed from the output of the input

level adjustment stage to the SAP demodulator circuit

through a 5f

automatically controlled. The SAP demodulator includes

internal noise and field strength detectors that mute the

SAP output in case of insufficient signal conditions. The

SAP identification signal can be read by the I2C-bus (see

Table 1).

Switch

The stereo/SAP switch feeds either the L − R signal or the

SAP demodulator output signal via the internal dbx noise

reduction circuit to the dematrix/line out select circuit.

Table 15 shows the different switch modes provided at the

output pins LOR and LOL.

band-pass filter. The demodulator level is

H

TDA9855

dbx decoder

The dbx circuit includes all blocks required for the noise

reduction system according to the BTSC system

specification. The output signal is fed through a 73 µs fixed

de-emphasis circuit to the dematrix block.

Integrated filters

The filter functions necessary for stereo and SAP

demodulation and part of the dbx filter circuits are provided

on chip using transconductor circuits. The required filter

accuracy is attained by an automatic filter alignment

circuit.

Audio processor

Selector

The selector allows selecting either the internal line out

signals LOR or LOL (dematrix out) or the external line in

signals LIR and LIL and combines the left and right signals

in several modes (see Table 8). The input signal capability

of the line inputs (LIR/LIL) is 2 V (RMS). The output of the

selector is AC coupled to the automatic volume level

control circuit via pins SOR/SOL and AVR/AVL to avoid

offset voltages.

Automatic volume level control

The automatic volume level stage controls its output

voltage to a constant level of typically 200 mV (RMS) from

an input voltage range between 0.1 and 1.1 V (RMS). The

circuit adjusts variations in modulation during broadcasting

and due to changes in the programme material. The

function can be switched off. To avoid audible ‘plops’

during the permanent operation of the AVL circuit a soft

blending scheme has been applied between the different

gain stages. A capacitor at pin CAV determines the attack

and decay time constants. In addition the ratio of attack

and decay time can be changed via I

and 4 of the CHARACTERISTICS).

Effects

The audio processor section offers the following mode

selections: linear stereo, pseudo stereo, spatial stereo and

forced mono. The spatial mode provides an antiphase

crosstalk of 30% or 52% (switchable via I

Table 13).

Volume/loudness

The volume control range is between +16 dB and −71 dB

in steps of 1 dB and ends with a mute step (see Table 4).

Balance control is achieved by the independent volume

2

C-bus (see notes 3

2

C-bus; see

July 1994 10

Philips Semiconductors Preliminary specification

I2C-bus controlled BTSC stereo / SAP

decoder and audio processor

control of each channel. The volume control blocks

operate in combination with the loudness control. The filter

is linear when maximum gain for volume control is

selected. The filter characteristic changes automatically

over a range of 28 dB down to a setting of −12 dB. At

−12 dB volume control the maximum loudness boost is

obtained. The filter characteristic is determined by external

components.

The proposed application provides a maximum boost of

17 dB for bass and 4.5 dB for treble. The loudness may be

switched on or off via the I2C-bus control (see Table 10).

The left and right volume control stages include two

independent zero crossing detectors. In the zero cross

mode a change in volume is automatically activated but

not executed. The execution is enabled at the next zero

crossing of the signal. If a new volume step is activated

before the previous one has been processed, the previous

value will be executed first, and then the new value will be

activated. If no zero crossing occurs the next volume

transmission will enforce the last activated volume setting.

The zero crossing mode is realized between adjoining

steps and between any steps, but not from any step to

mute. In this case the GMU bit is needed to use. In case of

need to mute only one channel, two steps are necessary.

The first step is a transmission from any steps to −71 dB

and the second is −71 dB step to mute. The step of −71 dB

to mute has no zero crossing but it is not relevant. This

procedure has to be provided by software.

Bass control

A single external 33 nF capacitor for each channel in

combination with a linear operational amplifier and internal

resistors provides a bass control range of +16.5 dB to

−12 dB in steps of 1.5 dB at low frequencies (40 Hz).

Internally the basic step width is 3 dB, with intermediate

steps are obtained by a toggle function that provides

additional an 1.5 dB boost or attenuation (see Table 5).

Please note that both loudness and bass control together

result in a maximum bass boost of 34.5 dB for low volume

steps.

Treble control

The adjustable range of the treble control stage is

between −12 dB and +12 B in steps of 3 dB. The filter

characteristic is determined by an external 5.6 nF

capacitor for each channel. The logic circuitry is arranged

in a way that the same data words (HEX 06 to 16) can be

used for both tone controls if a bass control range from

−12 dB to +12 dB and a treble control range from −12 dB

to +12 dB with 3 dB steps are used (see Tables 5 and 6).

TDA9855

Subwoofer;

surround sound control

The subwoofer or the surround mode can be activated with

the control bit SUR (see Table 3). A low bit provides an

output signal (L + R)/2 in subwoofer mode, a high bit

selects surround mode and provides an output signal

(L − R)/2. The signal is fed through a volume control stage

with a range between +14 dB and −14 dB in 2 dB steps on

top of the main channel control to the output pin OUTS.

The last setting is the mute position (see Table 7). The

capacitor C35 at pin SW provides a 230 Hz low-pass filter

in subwoofer mode. In surround mode this capacitor

should be disconnected. If balance is not in mid position

the selected left and right output levels will be combined.

Mute

The mute function can be activated independently with the

last step of volume or subwoofer/surround control at the

left, right or centre output. By setting the general mute bit

GMU via the I

channels include an independent zero cross detector. The

zero crossing mute feature can be selected via bit

TZCM:

TZCM 0:

forced mute with direct execution,

TZCM = 1:

execution in time with signal zero crossing.

In the zero cross mode a change of the GMU bit is

activated but not executed. The execution is enabled at

the next zero crossing of the signal. To avoid a large delay

of mute switching, when very low frequencies are

processed, or the output signal amplitude is lower than the

DC offset voltage, the following I2C-bus transmissions are

needed:

• a first transmission for mute execution

• a second transmission about 100 ms later, which must

switch the zero crossing mode to forced mute

(TZCM = 0)

• a third transmission to reactivate the zero crossing

mode (TZCM = 1). This transmission can take place

immediately, but must follow before the next mute

execution.

2

C-bus all audio part outputs are muted. All

July 1994 11

Philips Semiconductors Preliminary specification

I2C-bus controlled BTSC stereo / SAP

TDA9855

decoder and audio processor

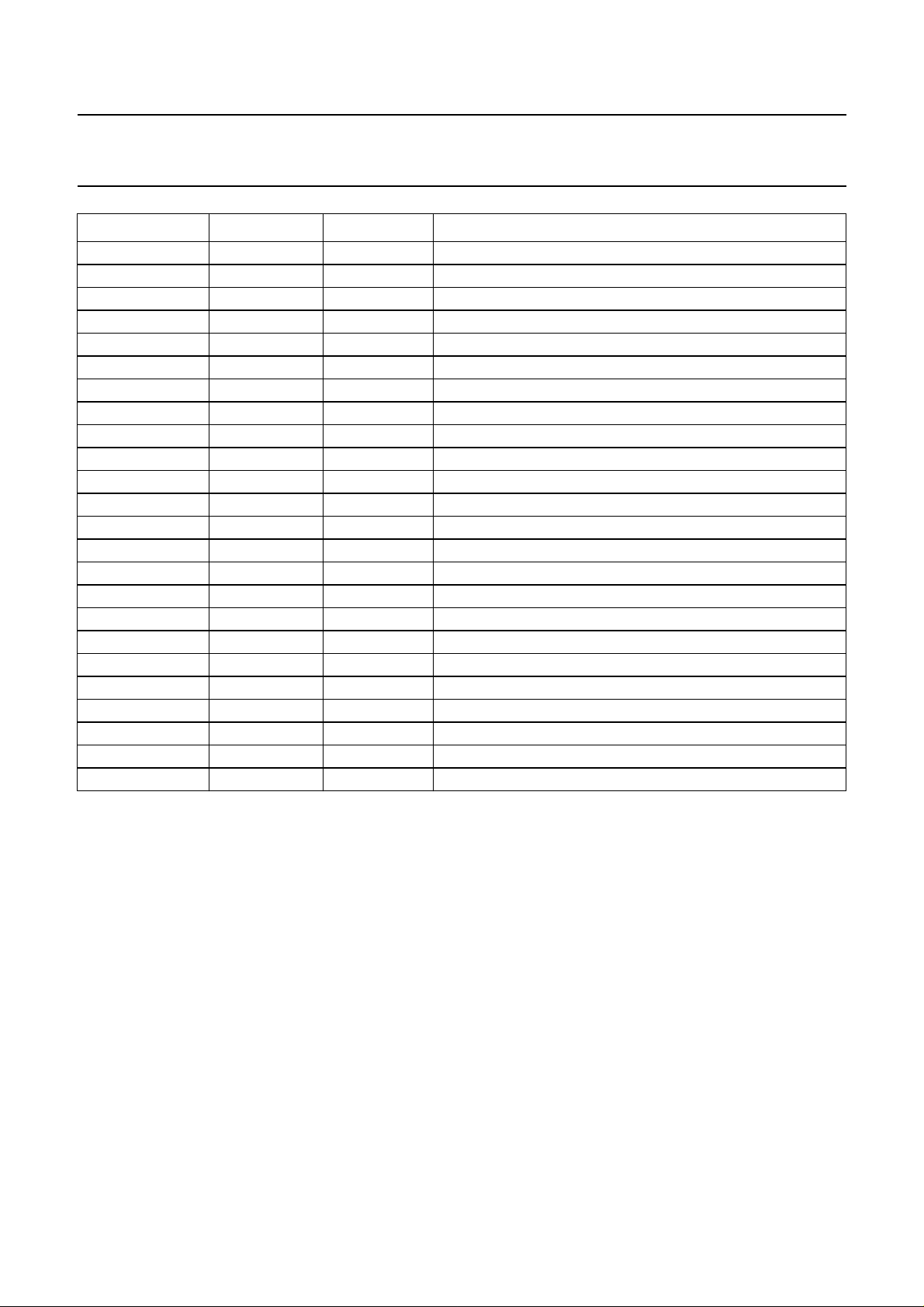

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

CC

T

amb

T

stg

V

es

V

n

Note to the limiting values

1. Human body model: C = 100 pF; R = 1.5 kΩ; V = 2 kV; charge device model: C = 200 pF; R = 0 Ω; V = 300 V.

THERMAL RESISTANCE

SYMBOL PARAMETER THERMAL RESISTANCE

R

th j-a

supply voltage 0 9.5 V

operating ambient temperature −20 +70 °C

storage temperature −65 +150 °C

electrostatic handling note 1

voltage at all other pins to pin GND 0 V

CC

V

from junction to ambient in free air

SOT247AH 43 K/W

SOT188CG 38 K/W

July 1994 12

Philips Semiconductors Preliminary specification

I2C-bus controlled BTSC stereo / SAP

TDA9855

decoder and audio processor

Requirements for the composite input signal to ensure proper system performance.

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

COMP

composite input level for 100%

L+R

modulation L + R (25 kHz

deviation), RMS, f = 300 Hz

∆COMP composite input level spreading

under operating conditions

Z

O

f

−2 dB

output impedance note 1 − low-ohmic 5 kΩ

roll-off frequencies (25 kHz

deviation L + R)

THD total harmonic distortion L + R;

f = 1 kHz

S/N signal-to-noise ratio

L + R/noise

α

SB

side band suppression mono into

unmodulated SAP carrier;

SAP carrier/side band

α

SP

spectral spurious attenuation

L + R/spurious

measured at COMP 162 250 363 mV

T

= −20 to +70 °C; aging;

amb

−0.5 −+0.5 dB

power supply influence

low frequency (−2 dB) −− 5Hz

high frequency (−2 dB) 100 −−kHz

25 kHz deviation −− 0.5 %

125 kHz deviation; note 2 −− 1.5 %

CCIR 468-2 weighted quasi peak; L + R; 25 kHz deviation;

f = 1 kHz; 75 µs de-emphasis

critical picture modulation 44 −−dB

with sync only 54 −−dB

mono signal: 25 kHz

46 −−dB

deviation,

f = 1 kHz; side band: SAP

carrier frequency ±1 kHz

50 Hz to 100 kHz; mainly

40 −−dB

n x fH; no de-emphasis; L + R:

25 kHz deviation, f = 1 kHz

Notes to the requirements

1. Low-ohmic preferred, otherwise the signal loss and spreading at COMP, caused by ZO and the composite input

impedance (see input level adjustment control) must be taken into account.

2. In order to prevent clipping at overmodulation (maximum deviation in the BTSC system for 100% modulation is

73 kHz).

July 1994 13

Philips Semiconductors Preliminary specification

I2C-bus controlled BTSC stereo / SAP

TDA9855

decoder and audio processor

CHARACTERISTICS

All voltages are measured relative to GND; V

AC coupled; f = 1 kHz; T

= +25 °C; volume gain control Gc= 0 dB; bass linear; treble linear; loudness off; AVL off;

amb

effects linear; composite input signal according to BTSC standard; see block diagram unless otherwise specified.

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

CC

I

CC

V

DC

supply voltage 8.0 8.5 9.0 V

supply current 50 75 95 mA

DC voltage at signal

handling pins

DECODER SECTION

Input level adjustment control

G

LA

input level adjustment

control

G

step

V

i(RMS)

Z

i

step resolution − 0.5 − dB

maximum input level 2 −−V

input impedance 29.5 35 40.5 kΩ

Stereo decoder

MPX

L + R

input level for 100%

modulation L + R (25 kHz

deviation) (RMS value)

MPX

L − R

input level for 100%

modulation L − R

(50 kHz deviation)

(peak value)

MPX

MPX

max

pilot

headroom for L + R, L, R f

nominal stereo pilot level

(RMS value)

ST

ON

pilot threshold STEREO

ON (RMS value)

ST

OFF

pilot threshold STEREO

OFF (RMS value)

Hyst hysteresis − 2.5 − dB

Out

L+R

output level for 100%

modulation L + R at LINE

OUT

α

ST

stereo channel

separation L/R at LINE

OUT

= 8.5 V, source resistance≤600Ω, output load RL≥ 10 kΩ, CL≤ 2.5 nf,

CC

− VCC/2 − V

maximum gain − 4.0 − dB

maximum attenuation −−3.5 − dB

input level adjusted via I2C-bus

− 250 − mV

(L + R; f = 300 Hz); monitoring

LINE OUT

− 707 − mV

< 15 kHz; THD < 15% for

mod

9 −−dB

75 µs equivalent input modulation

− 50 − mV

data STS = 1 −− 35 mV

data STS = 0 −− 30 mV

data STS = 1 15 −−mV

data STS = 0 10 −−mV

input level adjusted via I2C-bus

480 500 520 mV

(L + R; f = 300 Hz); monitoring

LINE OUT

aligned with dual tone 14%

modulation; alignment at

fL= 300 Hz; fR= 3.1 kHz

= 300 Hz; fR= 3 kHz 25 35 − dB

f

L

f

= 300 Hz; fR= 8 kHz 20 30 − dB

L

= 300 Hz; fR= 10 kHz 15 25 − dB

f

L

July 1994 14

Philips Semiconductors Preliminary specification

I2C-bus controlled BTSC stereo / SAP

TDA9855

decoder and audio processor

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

L, R

(f)

THD

L,R

S/N S/N CCIR 468-2

Stereo decoder, oscillator (VCXO)

f

o

f

of

Remark: The oscillator is designed to work together with MURATA resonator CSB503F58 for TDA9855. Change of

the resonator supplier is possible, but the resonator specification must be close to CSB503F58 for TDA9855.

∆f

H

L, R frequency response 14% modulation;

f

reference

= 300 Hz L or R

50 Hz to 11 kHz −3 −−dB

12 kHz −−3 −dB

total harmonic distortion

L, R at

modulation L or R 1% to

100%; f = 1 kHz

LINE OUT

LINE OUT in position MONO 50 60 − dB

weighted; quasi peak;

V

= 500 mV (RMS)

O

nominal VCXO frequency

(32fH)

with nominal ceramic

resonator

spread of free running

frequency

capture range (nominal

pilot)

− 0.2 1.0 %

− 503.5 − kHz

500.0 − 507.0 kHz

±190 ±265 − Hz

SAP demodulator

Remark: The internal SAP carrier level is determined by the composite input level and the level adjust gain.

SAP

IN

nominal SAP carrier input

level

15 kHz frequency deviation

of intercarrier

− 150 − mV

(RMS value)

SAP

ON

pilot threshold SAP ON

−− 85 mV

(RMS value)

SAP

OFF

pilot threshold SAP OFF

35 −−mV

(RMS value)

SAP

SAP

HYS

LEV

hysteresis − 2 − dB

SAP output level at LINE

OUT

(RMS value)

LINE OUT (LOL, LOR) in

position SAP / SAP;

f

= 300 Hz;

mod

− 500 − mV

100% modulation

F

res

frequency response 14% modulation; 50 Hz to

8 kHz; f

reference

= 300 Hz

−3 −−dB

THD total harmonic distortion 1 kHz − 0.5 2.0 %

LINE OUT (at pins LOL, LOR)

V

o

nominal output voltage

100% modulation − 500 − mV

(RMS value)

Headr output headroom 9 −−dB

Z

o

Out

R

L

DC

output impedance − 80 120 Ω

DC output voltage 0.45VCC0.5V

output load resistance

5 −−kΩ

CC

0.55VCCV

(AC)

July 1994 15

Loading...

Loading...