Philips TDA9811 Datasheet

INTEGRATED CIRCUITS

DATA SH EET

TDA9811

Multistandard VIF-PLL

with QSS-IF and AM demodulator

Preliminary specification

File under Integrated Circuits, IC02

1995 Oct 03

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL

with QSS-IF and AM demodulator

FEATURES

• 5 V supply voltage

• Two switched VIF inputs, gain controlled wide band

VIF-amplifier (AC-coupled)

• True synchronous demodulation with active carrier

regeneration (very linear demodulation, good

intermodulation figures, reduced harmonics, excellent

pulse response)

• Gated phase detector for L/L accent standard

• VCO frequency switchable between L and L accent

(alignment external) picture carrier frequency

• Separate video amplifier for sound trap buffering with

high video bandwidth

• VIF AGC detector for gain control, operating as peak

sync detector for B/G (optional external AGC) and peak

white detector for L; signal controlled reaction time for L

• Tuner AGC with adjustable takeover point (TOP)

• AFC detector without extra reference circuit

• SIF input for single reference QSS mode (PLL

controlled); SIF AGC detector for gain controlled SIF

amplifier; single reference QSS mixer able to operate in

high performance single reference QSS mode

• AM demodulator without extra reference circuit

• AM mute (especially for NICAM)

• Stabilizer circuit for ripple rejection and to achieve

constant output signals.

TDA9811

GENERAL DESCRIPTION

The TDA9811 is an integrated circuit for multistandard

vision IF signal processing and sound AM demodulation,

with single reference QSS-IF in TV and VCR sets.

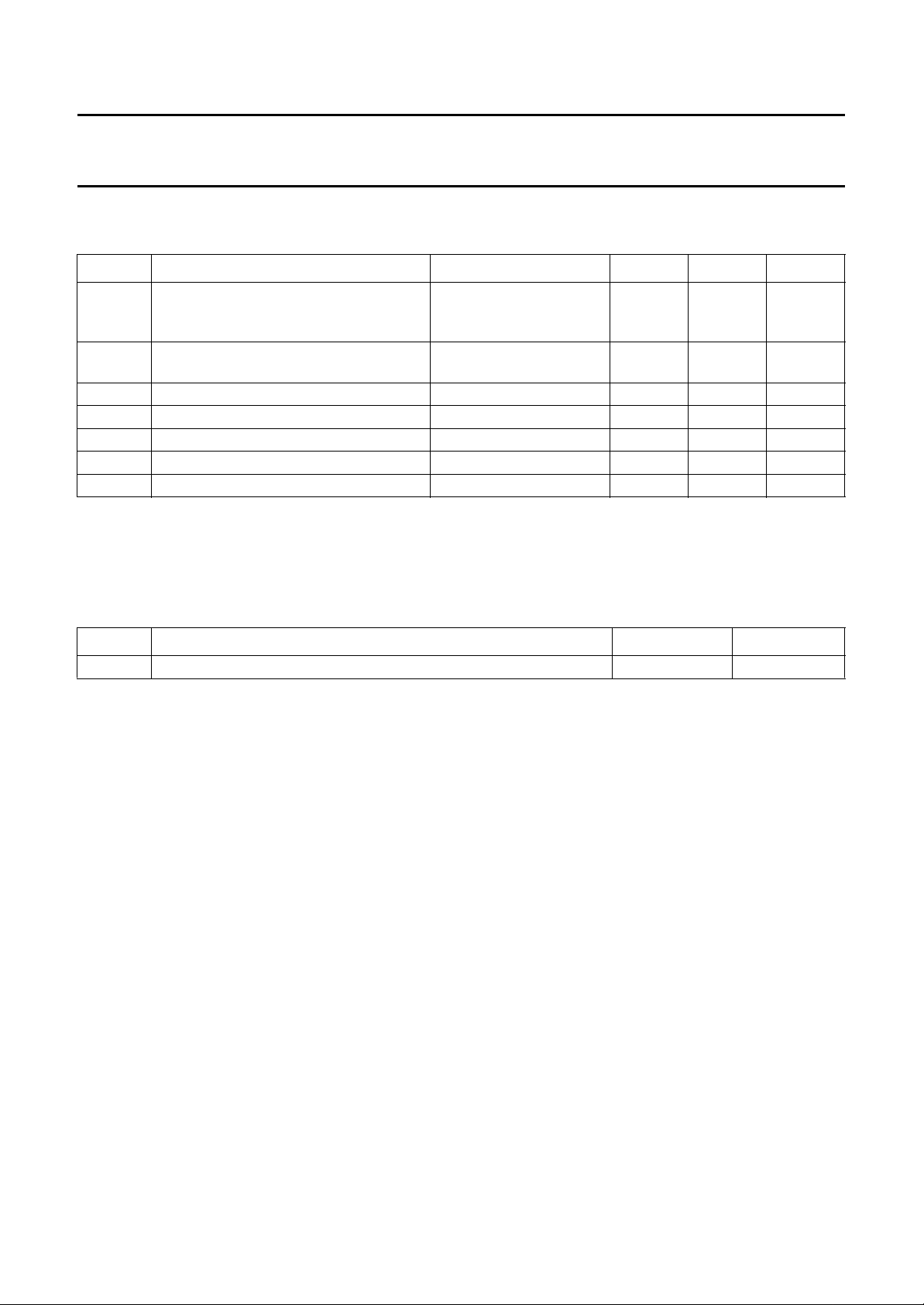

ORDERING INFORMATION

TYPE NUMBER

NAME DESCRIPTION VERSION

TDA9811 SDIP32 plastic shrink dual in-line package; 32 leads (400 mil) SOT232-1

1995 Oct 03 2

PACKAGE

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL

TDA9811

with QSS-IF and AM demodulator

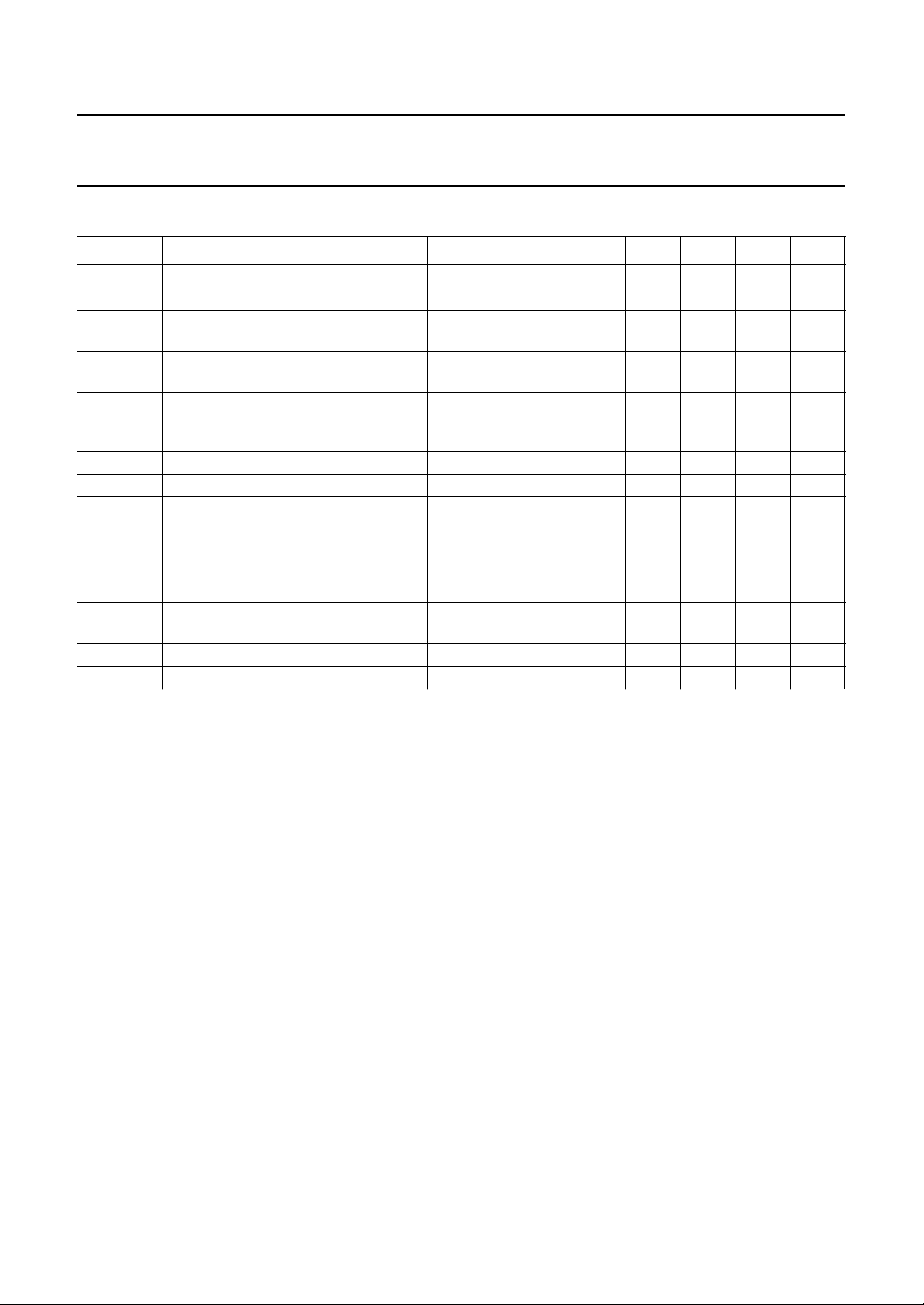

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

P

I

P

V

i VIF(rms)

V

o CVBS(p-p)

B

−3

S/N (W) weighted signal-to-noise ratio for video 56 60 − dB

IM

α1.1

IM

α3.3

α

H(sup)

V

i SIF(rms)

V

o(rms)

THD total harmonic distortion 54% modulation − 0.5 1.0 %

S/N (W) weighted signal-to-noise ratio 54% modulation 47 53 − dB

supply voltage 4.5 5 5.5 V

supply current 93 109 125 mA

vision IF input signal voltage sensitivity

−1 dB video at output − 60 100 µV

(RMS value)

CVBS output signal voltage

1.7 2.0 2.3 V

(peak-to-peak value)

−3 dB video bandwidth on pin CVBS B/G and L standard;

< 20 pF; RL> 1kΩ;

C

L

78−MHz

AC load

intermodulation attenuation at ‘blue’ f = 1.1 MHz 58 64 − dB

intermodulation attenuation at ‘blue’ f = 3.3 MHz 58 64 − dB

suppression of harmonics in video

35 40 − dB

signal

sound IF input signal voltage sensitivity

−3 dB at intercarrier output − 30 70 µV

(RMS value)

audio output signal voltage

L standard; 54% modulation − 0.5 − V

(RMS value)

1995 Oct 03 3

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL

with QSS-IF and AM demodulator

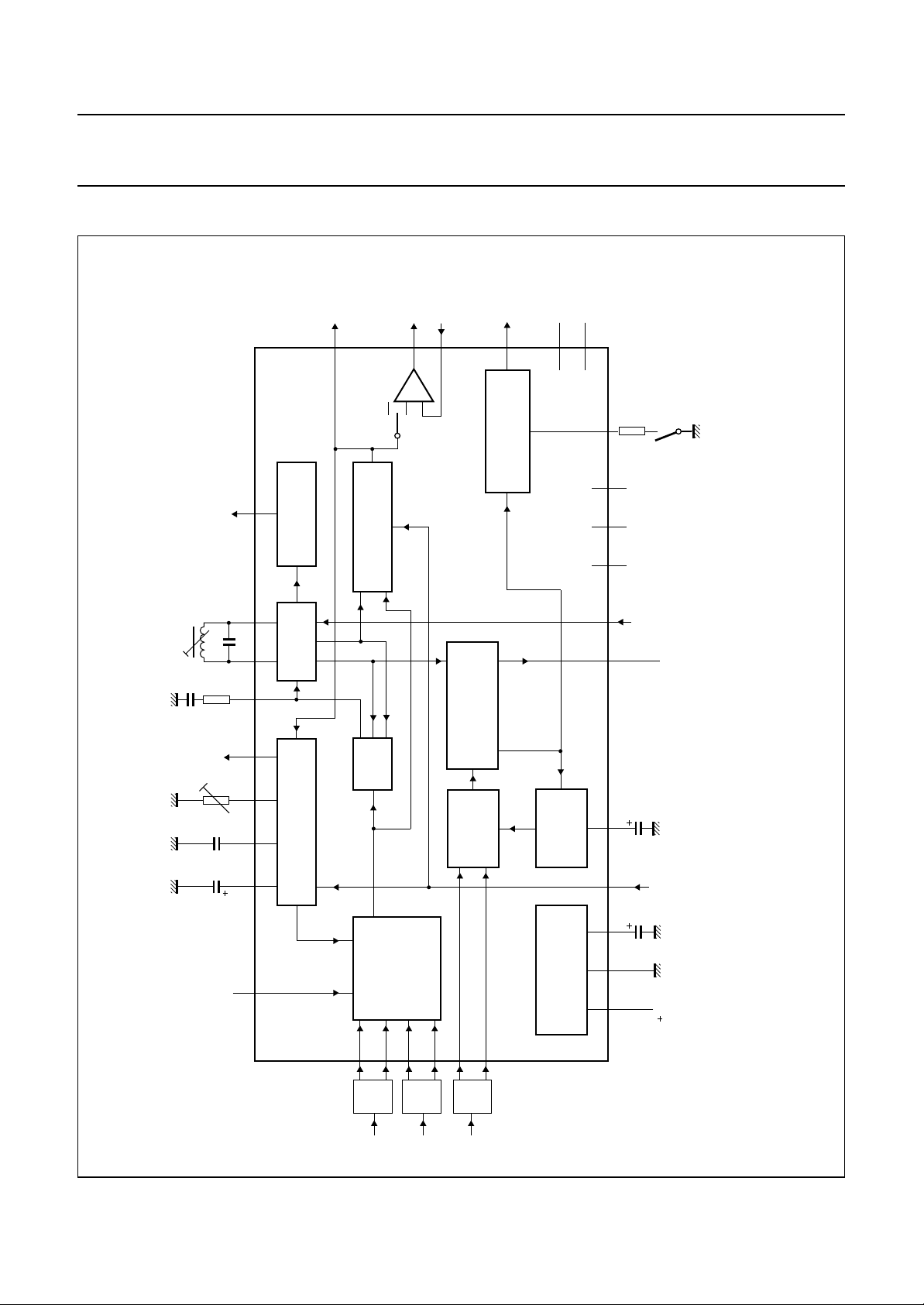

BLOCK DIAGRAM

video

1 V (p-p)

2324257192830 63

AFC

AFC DETECTOR

VIDEO DEMODULATOR

i(vid)

CVBS

V

2 V (p-p)

102122

VIDEO

BUFFER

AND AMPLIFIER

TDA9811

AF/AM

12

AF AMPLIFIER

13

AND SWITCH

n.c.

TDA9811

n.c.

14

MHA046

17

15

16

1811

mute switch, AM

n.c.

n.c.

n.c.

book, full pagewidth

PC

2 x f

tuner

TOP

C

C

filter

loop

AGC

BL

AGC

VIF input switch

VCO TWD

FPLL

TUNER AND VIF-AGC

VIF AMPLIFIER

5

4

AND

INPUT SWITCH

2

1

MIXER AND

AM DEMODULATOR

SINGLE REFERENCE

SIF

AMPLIFIER

32

31

L′/L

20

AGC

C

SIF-AGC

P

V

1/2

STABILIZER

29 27 26 9 8

INTERNAL VOLTAGE

switch

(2nd SIF)

switch

standard

5 V

o QSS

V

Fig.1 Block diagram.

VIFB

VIFA

1995 Oct 03 4

SIF

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL

with QSS-IF and AM demodulator

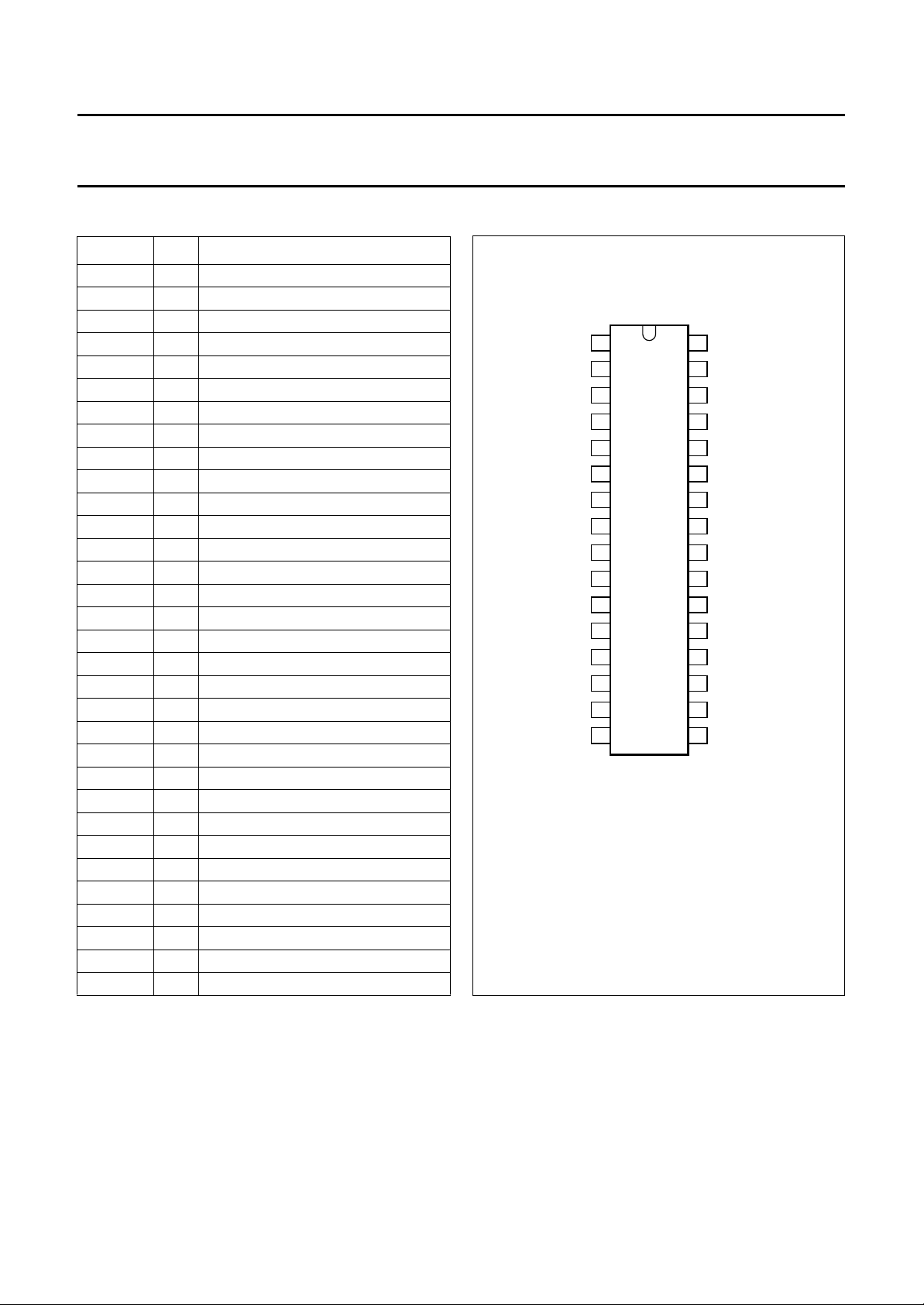

PINNING

SYMBOL PIN DESCRIPTION

V

i VIF1

V

i VIF2

C

BL

V

i VIF3

V

i VIF4

TADJ 6 tuner AGC takeover adjust (TOP)

T

PLL

C

SAGC

STD 9 standard switch

V

o CVBS

LSWI 11 L/L accent switch

V

oAF

n.c. 13 not connected

n.c. 14 not connected

n.c. 15 not connected

n.c. 16 not connected

MUTE 17 AM mute

n.c. 18 not connected

TAGC 19 tuner AGC output

V

o QSS

V

o(vid)

V

i(vid)

AFC 23 AFC output

VCO1 24 VCO1 reference circuit for 2f

VCO2 25 VCO2 reference circuit for 2f

C

ref

GND 27 ground

C

VAGC

V

P

INSWI 30 VIF input switch

V

i SIF1

V

i SIF2

1 VIF differential input signal voltage 1

2 VIF differential input signal voltage 2

3 black level detector

4 VIF differential input signal voltage 3

5 VIF differential input signal voltage 4

7 PLL loop filter

8 SIF AGC capacitor

10 CVBS output signal voltage

12 AM audio voltage frequency output

20 single reference QSS output voltage

21 composite video output voltage

22 video buffer input voltage

PC

PC

261⁄2VP reference capacitor

28 VIF AGC capacitor

29 supply voltage

31 SIF differential input signal voltage 1

32 SIF differential input signal voltage 2

ndbook, halfpage

V

V

V

V

C

V

o CVBS

i VIF1

i VIF2

C

BL

i VIF3

i VIF4

TADJ

T

PLL

SAGC

STD

LSWI

V

o AF

n.c.

n.c.

n.c.

n.c.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

TDA9811

Fig.2 Pin configuration.

MHA047

V

32

i SIF2

V

31

i SIF1

30

INSWI

V

29

P

C

28

VAGC

GND

27

C

26

ref

VCO2

25

VCO1

24

AFC

23

V

22

i(vid)

V

21

o(vid)

V

20

o QSS

TAGC

19

18

n.c.

17

MUTE

TDA9811

1995 Oct 03 5

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL

with QSS-IF and AM demodulator

FUNCTIONAL DESCRIPTION

Vision IF amplifier and input switch

The vision IF amplifier consists of three AC-coupled

differential amplifier stages. Each differential stage

comprises a feedback network controlled by emitter

degeneration. The first differential stage is extended by

two pairs of emitter followers to provide two IF input

channels. The VIF input can be selected by pin 30.

Tuner and VIF AGC

The AGC capacitor voltage is transferred to an internal IF

control signal, and is fed to the tuner AGC to generate the

tuner AGC output current (open-collector output).

The tuner AGC takeover point can be adjusted. This allows

the tuner and the SWIF filter to be matched to achieve the

optimum IF input level.

The AGC detector charges/discharges the AGC capacitor

to the required voltage for setting of VIF and tuner gain in

order to keep the video signal at a constant level.

Therefore for negative video modulation the sync level and

for positive video modulation the peak white level of the

video signal is detected. In order to reduce the reaction

time for positive modulation, where a very large time

constant is needed, an additional level detector increases

the discharging current of the AGC capacitor (fast mode)

in the event of a decreasing VIF amplitude step. The

additional level information is given by the black-level

detector voltage.

TDA9811

VCO, Travelling Wave Divider (TWD) and AFC

The VCO operates with a resonance circuit (with L and C

in parallel) at double the PC frequency. The VCO is

controlled by two integrated variable capacitors.

The control voltage required to tune the VCO from its

free-running frequency to actually double the PC

frequency is generated by the frequency-phase detector

and fed via the loop filter to the first variable capacitor

(FPLL). This control voltage is amplified and additionally

converted into a current which represents the AFC output

signal. The VCO centre frequency can be decreased

(required for L accent standard) by activating an additional

internal capacitor. This is achieved by using the L accent

switch. In this event the second variable capacitor can be

controlled by a variable resistor at the L accent switch for

setting the VCO centre frequency to the required L accent

value. At centre frequency the AFC output current is equal

to zero.

The oscillator signal is divided-by-two with a TWD which

generates two differential output signals with a 90 degree

phase difference independent of the frequency.

Video demodulator and amplifier

The video demodulator is realized by a multiplier which is

designed for low distortion and large bandwidth. The vision

IF input signal is multiplied with the ‘in phase’ signal of the

travelling wave divider output. In the demodulator stage

the video signal polarity can be switched in accordance

with the TV standard.

Frequency Phase Locked Loop detector (FPLL)

The VIF-amplifier output signal is fed into a frequency

detector and into a phase detector via a limiting amplifier.

During acquisition the frequency detector produces a DC

current proportional to the frequency difference between

the input and the VCO signal. After frequency lock-in the

phase detector produces a DC current proportional to the

phase difference between the VCO and the input signal.

The DC current of either frequency detector or phase

detector is converted into a DC voltage via the loop filter,

which controls the VCO frequency. In the event of positive

modulated signals the phase detector is gated by

composite sync in order to avoid signal distortion for

overmodulated VIF signals.

1995 Oct 03 6

The demodulator output signal is fed via an integrated

low-pass filter for attenuation of the carrier harmonics to

the video amplifier. The video amplifier is realized by an

operational amplifier with internal feedback and high

bandwidth. A low-pass filter is integrated to achieve an

attenuation of the carrier harmonics for B/G and

L standard. The standard dependent level shift in this

stage delivers the same sync level for positive and

negative modulation. The video output signal is 1 V (p-p)

for nominal vision IF modulation.

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL

with QSS-IF and AM demodulator

Video buffer

For an easy adaption of the sound traps an operational

amplifier with internal feedback is used in the event of B/G

and L standard. This amplifier is featured with a high

bandwidth and 7 dB gain. The input impedance is adapted

for operating in combination with ceramic sound traps. The

output stage delivers a nominal 2 V (p-p) positive video

signal. Noise clipping is provided.

SIF amplifier and AGC

The sound IF amplifier consists of two AC-coupled

differential amplifier stages. Each differential stage

comprises a controlled feedback network provided by

emitter degeneration.

The SIF AGC detector is related to the SIF input signals

(average level of AM or FM carriers) and controls the SIF

amplifier to provide a constant SIF signal to the AM

demodulator and single reference QSS mixer. The SIF

AGC reaction time is set to ‘slow’ for nominal video

conditions. But with a decreasing VIF amplitude step the

SIF AGC is set to ‘fast’ mode controlled by the VIF AGC

detector. In FM mode this reaction time is also set to ‘fast’

controlled by the standard switch.

TDA9811

AM demodulator

The AM demodulator is realized by a multiplier. The

modulated SIF amplifier output signal is multiplied in

phase with the limited (AM is removed) SIF amplifier

output signal. The demodulator output signal is fed via an

integrated low-pass filter for attenuation of the carrier

harmonics to the AF amplifier.

1

Internal voltage stabilizer and

The bandgap circuit internally generates a voltage of

approximately 1.25 V, independent of supply voltage and

temperature. A voltage regulator circuit, connected to this

voltage, produces a constant voltage of 3.6 V which is

used as an internal reference voltage.

For all audio output signals the constant reference voltage

cannot be used because large output signals are required.

Therefore these signals refer to half the supply voltage to

achieve a symmetrical headroom, especially for the

rail-to-rail output stage. For ripple and noise attenuation

1

the

⁄2VP voltage has to be filtered via a low-pass filter by

using an external capacitor together with an integrated

resistor (fg= 5 Hz). For a fast setting to 1⁄2VP an internal

start-up circuit is added.

⁄2VP-reference

Single reference QSS mixer

The single reference QSS mixer is realized by a multiplier.

The SIF amplifier output signal is fed to the single

reference QSS mixer and converted to intercarrier

frequency by the regenerated picture carrier (VCO).

The mixer output signal is fed via a high-pass for

attenuation of the video signal components to the output

pin 20. With this system a high performance hi-fi stereo

sound processing can be achieved.

1995 Oct 03 7

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL

TDA9811

with QSS-IF and AM demodulator

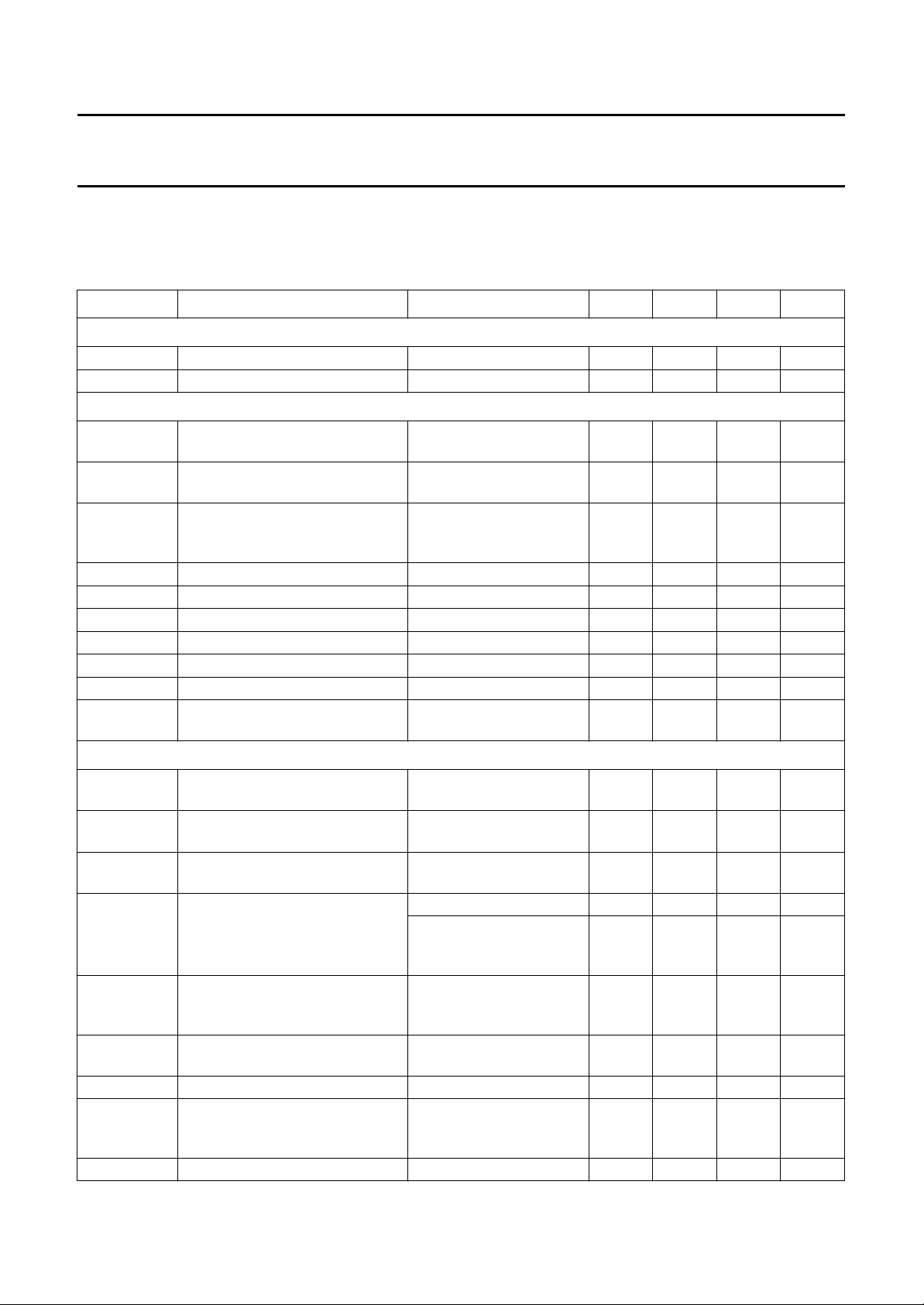

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

P

V

i

t

s(max)

V

19

T

stg

T

amb

V

es

Notes

1. I

P

2. Machine model class B.

supply voltage (pin 29) maximum chip

0 7.0 V

temperature of 125 °C;

note 1

voltage at pins 1 to 9, 11, 12, 19, 22, 23

0V

and 26 to 32

maximum short-circuit time − 10 s

tuner AGC output voltage 0 13.2 V

storage temperature −25 +150 °C

operating ambient temperature −20 +70 °C

electrostatic handling voltage note 2 −300 +300 V

= 125 mA; T

=70°C; R

amb

th j-a

= 60 K/W.

P

V

THERMAL CHARACTERISTICS

SYMBOL PARAMETER VALUE UNIT

R

th j-a

thermal resistance from junction to ambient in free air 60 K/W

1995 Oct 03 8

Philips Semiconductors Preliminary specification

Multistandard VIF-PLL

TDA9811

with QSS-IF and AM demodulator

CHARACTERISTICS

VP=5V; T

(sync-level for B/G, peak white level for L); video modulation DSB; residual carrier B/G: 10%; L = 3%; video signal in

accordance with

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Supply (pin 29)

V

P

I

P

Vision IF amplifier (pins 1, 2, 4 and 5)

V

i VIF(rms)

V

i max(rms)

∆V

o(int)

G

IFcr

R

i(diff)

C

i(diff)

V

1, 2,4, 5

R

i

V

1, 2, 4, 5

α

ct IF

=25°C; see Table 1 for input frequencies and level; input level V

amb

“CCIR, line 17”

; measurements taken in Fig.13; unless otherwise specified.

iIF1,2,3,4

= 10 mV RMS value

supply voltage note 1 4.5 5 5.5 V

supply current 93 109 125 mA

input signal voltage sensitivity

(RMS value)

maximum input signal voltage

(RMS value)

internal IF amplitude difference

between picture and

sound carrier

B/G standard;

−1 dB video at output

B/G standard;

+1 dB video at output

within AGC range;

B/G standard;

∆f = 5.5 MHz

− 60 100 µV

120 200 − mV

− 0.7 1 dB

IF gain control range see Fig.3 65 70 − dB

differential input resistance note 2; activated input 1.7 2.2 2.7 kΩ

differential input capacitance note 2; activated input 1.2 1.7 2.5 pF

DC input voltage note 2; activated input − 3.4 − V

input resistance to ground note 2; not activated input − 1.1 − kΩ

DC input voltage note 2; not activated input − 0.2 − V

crosstalk attenuation of IF input

notes 2 and 3 55 60 − dB

switch at pins 1, 2, 4 and 5

True synchronous video demodulator; note 4

f

VCO(max)

maximum oscillator frequency for

carrier regeneration

/∆T oscillator drift as a function of

∆f

osc

temperature

V

0 ref(rms)

oscillator voltage swing at pins 24

and 25 (RMS value)

f

PC CR

Qf

PC(fr)

picture carrier capture range B/G and L standard ±1.5 ±2.0 − MHz

picture carrier frequency

(free-running) accuracy

f

PC(alg)CR

L accent alignment frequency

range

t

acq

V

i VIF(rms)

acquisition time BL = 180 kHz; note 6 −−30 ms

VIF input signal voltage sensitivity

for PLL to be locked (RMS value;

pins 1, 2, 4 and 5)

I

FPLL(offset)

FPLL offset current at pin 7 note 8 −−±4.5 µA

f=2f

PC

oscillator is free-running;

I

= 0; note 5

AFC

125 130 − MHz

−−±20 ppm/K

70 100 130 mV

L accent standard;

= 33.9 MHz;

f

PC

±1.0 ±1.3 − MHz

R11= 5.6 kΩ

L accent standard;

−±200 ±400 kHz

fPC= 33.9 MHz;

R11= 5.6 kΩ

I

=0 ±400 ±600 − kHz

AFC

maximum IF gain; note 7 − 30 70 µV

1995 Oct 03 9

Loading...

Loading...