Philips TDA5149G Datasheet

INTEGRATED CIRCUITS

DATA SH EET

TDA5149G

12 V Voice Coil Motor (VCM) driver

and spindle motor pre-driver

combination chip

Product specification

File under Integrated Circuits, IC11

1996 May 06

Philips Semiconductors Product specification

12 V Voice Coil Motor (VCM) driver and

spindle motor pre-driver combination chip

FEATURES

General features

• Single-chip voice coil motor driver and spindle motor

pre-driver

• Internal voltage reference generator

• Programming of timing parameters via the serial bus

• Control of sleep, brake and disable modes for both the

VCM and spindle via the serial bus

• Temperature monitor circuit

• General purpose uncommitted operational amplifier.

Voice coil motor driver

• On-board full-bridge power DMOS driver with low R

• Class AB linear amplifier with no dead zone

• Adjustable gain and bandwidth

• Retract circuit operating at power-down.

Spindle motor pre-driver

• Designed to drive external N-channel power MOSFETs

for brushless, sensorless DC motors

• Internal or external commutation control

• Digital commutation timing

• Average motor supply current control with Pulse Width

Modulation (PWM)

• Soft switching under PWM control

• Spindle brake after park at power-down.

DSon

APPLICATIONS

• 12 V high-performance hard disk drives.

GENERAL DESCRIPTION

The TDA5149G is a combination of a voice coil motor

driver and a spindle motor pre-driver, capable of operating

12 V high-performance hard disk drives.

The device integrates a spindle pre-driver that drives three

external N-channel power MOSFETs in order to drive a

three-phase brushless, sensorless DC motor in full wave

mode. In the normal mode, commutations are generated

from the internal Back EMF (BEMF) sensing circuitry.

Commutations, however, can also be generated from an

external source, thereby providing the possibility of driving

the motor in the stepper-motor mode.

The VCM driver is a linear transconductance amplifier

capable of handling currents up to 1.65 A. It allows

external adjustment of the gain and compensation.

The TDA5149G also contains two drivers for a latch that

secures the heads in the event of power-down.

To control functions such as park, brake, sleep or disable

and to program the different timing parameters, the

TDA5149G is provided with a three-wire serial port. A high

precision voltage monitor is also included, for both

5 and 12 V power supplies. Finally, the IC contains a

temperature monitor circuit and an uncommitted

operational amplifier connected to VDD, which can be used

freely within the application. The device is contained in a

LQFP64 package with 4 pins connected to the lead frame

for improved heat dissipation.

TDA5149G

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

DD

V

DDD

V

DDA1

I

oVCM

R

DSon

ORDERING INFORMATION

TYPE

NUMBER

TDA5149G LQFP64 plastic low profile quad flat package; 64 leads; body 10 × 10 × 1.4 mm SOT314-2

1996 May 06 2

general supply voltage (pin 54) 10.8 12.0 13.2 V

digital supply voltage (pin 55) 4.5 5.0 5.5 V

analog supply voltage (pin 27) 4.5 5.0 5.5 V

voice coil motor output current − − 1.65 A

VCM power DMOS total on-resistance

(including leads and bond wires)

NAME DESCRIPTION VERSION

Tj= 25 °C − − 0.65 Ω

Tj= 125 °C − − 1.1 Ω

PACKAGE

Philips Semiconductors Product specification

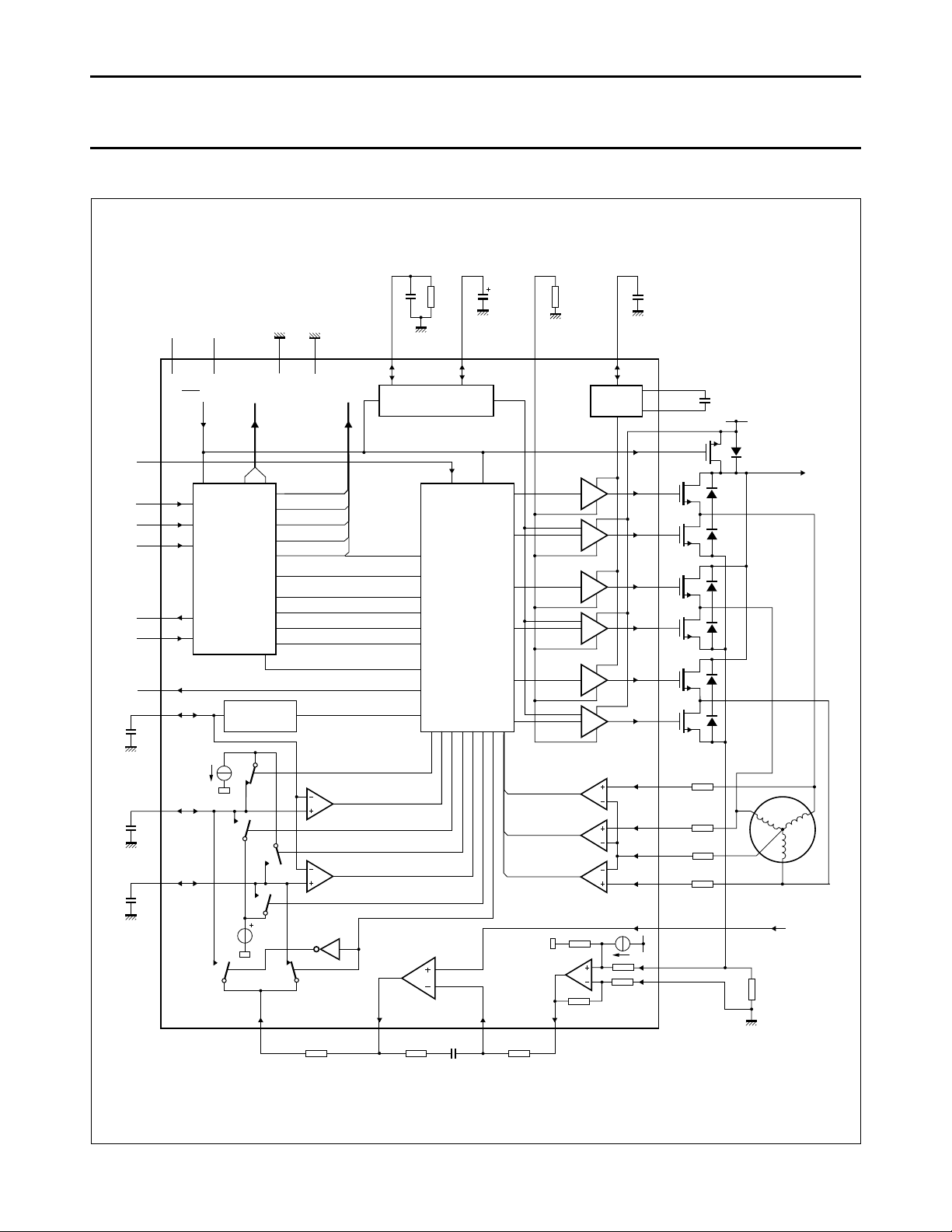

Fig.1 Block diagram of the spindle part.

handbook, full pagewidth

MGE657

SAWTOOTH

OSCILLATOR

SERIAL

PORT

VPARK

VCM_CONT1

VCM_CONT2

VGAINSEL

SLEEP

COMMUT. DELAYS

SBRAKE

SDISABLE

SPINMODE

COMMCLOCK

INIT

TRIGGER

CSS2 dis

SPWM comp 1

SPWM comp 2

CSS2 short

CSS1 dis

CSS1 short

LOOP1 select

CHARGE

PUMP

BRAKE

DELAY

22

CSS1

CSS2

23

STOSC

24

FG

57

SCANTEST

56

SCANOUT

25

SENABLE

61

SDATA

59

SCLOCK

60

CLOCK

58

54

V

DD

45

H0

3

H1

5

L1

6

H2

8

L2

9

H3

11

L3

4

MOT1

7 MOT2

2

MOT0

10

MOT3

19

ISPIN

13

14

SPINSENSEH

SPINSENSEL

63

62

CAPX2

CAPX1

12 V

CLAMP

to the

VCM

MOT1

MOT2

MOT3

3 kΩ

3 kΩ

1 kΩ

3 kΩ

from the

PWM DAC

R

sense

1

CAPY

IDRIVE

12

BRAKEPOWER

BRAKEDELAY

AGND

DGND

64

16

51

47

V

DDA1

V

DDD

55

27

from the

POR circuit

to the

LATCH

to the

VCM

DIGITAL

CONTROL

21

RPOS

20

SICOMP

18

SINTIN

15

SISENS

5×

INTG

COMP

COMP

BEMF comp 1

BEMF comp 2

BEMF comp 3

DRIVER

DRIVER

DRIVER

DRIVER

DRIVER

DRIVER

COMP

COMP

COMP

0.4 V

LACTIVE

LHOLD

TDA5149G

1

2

3

1

2

3

4

5

BLOCK DIAGRAMS

12 V Voice Coil Motor (VCM) driver and

spindle motor pre-driver combination chip

TDA5149G

1996 May 06 3

Philips Semiconductors Product specification

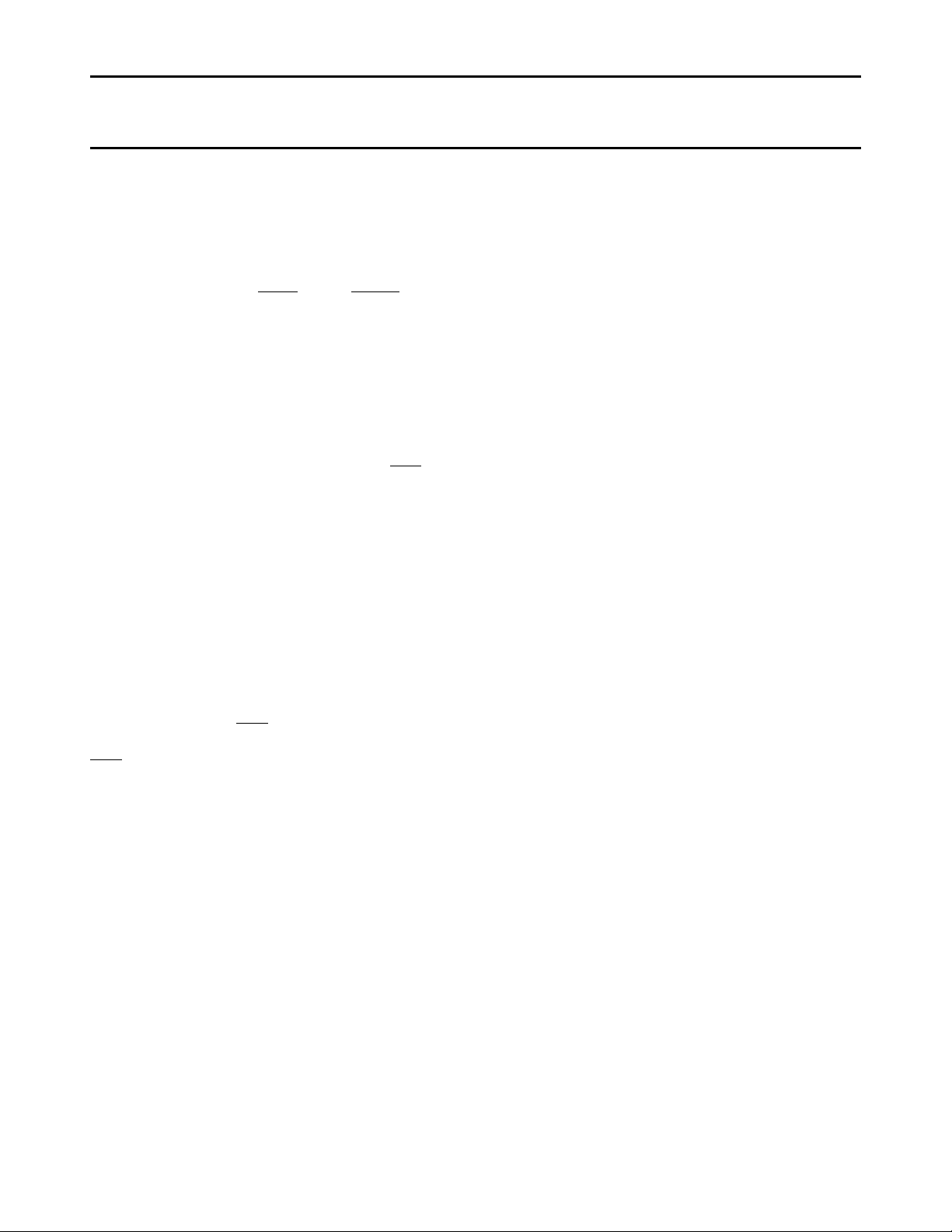

Fig.2 Block diagram of the VCM and RESET circuits.

handbook, full pagewidth

MGE656

M

FOLLOWER

FOLLOWER

PREAMP

PREAMP

PARK

CIRCUITRY

SENSE

BUFFER

REFERENCE

CURRENT

GENERATOR

REFERENCE

VOLTAGE

GENERATOR

LATCH

CIRCUITRY

LACTIVE LHOLD

from the

serial port

TEMPERATURE

SENSOR

POWER-

ON RESET

GENERATOR

OPAMP

to the

PARK

circuit

COMP

COMP

+5 V

+12 V

+12 v

from the

serial port

from the

POR circuit

C

comp

R

comp

V

CMIN2

V

CMIN1

R

fb

V

CMSENSOUT

VCM

ref

V

ref(o)

I

ref

POR12

ADJ

POR5

ADJ

VCM_CONT1

VCM_CONT2

AMPIN−

AMPIN+

AMPOUT

CLAMP

PGND1

V

DDV

V

CM+

V

CM−

PGND2

V

CMSENSEL

V

CMSENSEH

latch

LATCHACTIV

LATCHHOLD

TEMPMON

RESETPRESETA

POR

DELAY

26 35 34

37

52

53

42

48

43

44

39

36

32

38

33

31

30

40

41

50

46

49

17

29

28

100 nF

R

8

from the

spindel

27 Ω

100 nF

27 Ω

R

in2

R

in1

VCM

input

VCM

reference

input

TDA5149G

disable

park

brake

V

GAINSEL

V

CMref

R

R

*

20 kΩ

23 kΩ

50 kΩ

10 kΩ

10 kΩ

50 kΩ

−

+

−

+

−

+

+

−

−

+

−

+

+5 V

+12 V

12 V Voice Coil Motor (VCM) driver and

spindle motor pre-driver combination chip

TDA5149G

1996 May 06 4

Philips Semiconductors Product specification

12 V Voice Coil Motor (VCM) driver and

spindle motor pre-driver combination chip

PINNING

SYMBOL PIN I/O DESCRIPTION

CAPY 1 I/O charge pump capacitor

MOT0 2 I motor centre tap input

H1 3 O driver output to gate of upper power FET 1

MOT1 4 I back EMF comparator input 1

L1 5 O driver output to gate of lower power FET 1

H2 6 O driver output to gate of upper power FET 2

MOT2 7 I back EMF comparator input 2

L2 8 O driver output to gate of lower power FET 2

H3 9 O driver output to gate of upper power FET 3

MOT3 10 I back EMF comparator input 3

L3 11 O driver output to gate of lower power FET 3

IDRIVE 12 I adjustment for output stage drive current

SPINSENSEH 13 I positive spindle sense amplifier input

SPINSENSEL 14 I negative spindle sense amplifier input

SISENS 15 O spindle sense amplifier output

AGND 16 − general analog ground; note 1

I

ref

SINTIN 18 I negative integrator input

ISPIN 19 I positive integrator input, average current adjustment

SICOMP 20 O integrator output

RPOS 21 I duty cycle modulator input

CSS1 22 I/O soft switching capacitor 1

CSS2 23 I/O soft switching capacitor 2

STOSC 24 I/O sawtooth oscillator capacitor

SCANOUT 25 O test output

POR

DELAY

V

DDA1

POR5

ADJ

POR12

ADJ

AMPIN− 30 I negative input of the uncommitted operational amplifier

AMPIN+ 31 I positive input of the uncommitted operational amplifier

PGND1 32 − power ground 1 for VCM DMOS; note 1

AMPOUT 33 O uncommitted operational amplifier output

RESETP 34 O power-on reset digital output with passive pull-up resistor

RESETA 35 O power-on reset digital output with active pull-up resistor

V

CM−

TEMPMON 37 O temperature monitor output

CLAMP 38 I/O clamp capacitor used for head retraction

V

DDV

V

CMIN2

17 O reference current generator output

26 I/O power-on reset delay capacitor (active LOW)

27 − analog supply voltage 1 (+5 V)

28 O adjustment of POR threshold (for +5 V)

29 O adjustment of POR threshold (for +12 V)

36 O negative output voltage of the VCM power stage

39 − power supply for VCM DMOS driver (+12 V)

40 I switchable VCM control input voltage

TDA5149G

1996 May 06 5

Philips Semiconductors Product specification

12 V Voice Coil Motor (VCM) driver and

spindle motor pre-driver combination chip

SYMBOL PIN I/O DESCRIPTION

V

CMIN1

V

CMSENSEH

V

CMSENSEL

V

CM+

H0 45 O gate control of the isolating power FET

VCM

ref

BRAKEPOWER 47 I/O reservoir capacitor for the brake/park circuitry

PGND2 48 − power ground 2 for VCM DMOS; note 1

V

ref(o)

V

CMSENSOUT

BRAKEDELAY 51 I/O powerless brake delay adjustment

LATCHHOLD 52 O latch hold output

LATCHACTIV 53 O latch activate output

V

DD

V

DDD

SCANTEST 56 I test mode input

FG 57 O commutation frequency generator output

CLOCK 58 I clock for digital timing input

SDATA 59 I serial port data input

SCLOCK 60 I serial port clock input

SENABLE 61 I serial port enable input

CAPX2 62 I/O charge pump capacitor input/output

CAPX1 63 I/O charge pump capacitor input/output

DGND 64 − digital ground; note 1

41 I VCM control input voltage

42 I positive VCM sense amplifier input voltage

43 I negative VCM sense amplifier input voltage

44 O positive output voltage of the VCM power stage

46 I reference voltage input for the VCM

49 O reference voltage generator output

50 O VCM sense amplifier output voltage

54 − general supply voltage (+12 V)

55 − digital supply voltage (+5 V)

TDA5149G

Note

1. The 4 ground pins are tied to the lead frame for better heat dissipation.

1996 May 06 6

Philips Semiconductors Product specification

Fig.3 Pin configuration.

handbook, full pagewidth

TDA5149G

MGE654

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

PGND2

BRAKEPOWER

VCM

ref

H0

V

CM+

V

CMSENSEL

V

CMSENSEH

V

CMIN1

V

CMIN2

V

DDV

CLAMP

TEMPMON

V

CM−

RESETA

RESETP

AMPOUT

CAPY

MOT0

H1

MOT1

L1

H2

MOT2

L2

H3

MOT3

L3

IDRIVE

SPINSENSEH

SPINSENSEL

SISENS

AGDN

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

DGND

CAPX1

CAPX2

SENABLE

SCLOCK

SDATA

CLOCK

FG

SCANTEST

V

DDD

V

DD

LATCHACTIV

LATCHHOLD

BRAKEDELAY

V

CMSENSOUT

V

ref(o)

I

ref

SINTIN

ISPIN

SICOMP

RPOS

CSS1

CSS2

STOSC

SCANOUT

POR

DELAY

V

DDA1

POR5

ADJ

POR12

ADJ

AMPIN−

AMPIN+

PGND1

12 V Voice Coil Motor (VCM) driver and

spindle motor pre-driver combination chip

TDA5149G

1996 May 06 7

Philips Semiconductors Product specification

12 V Voice Coil Motor (VCM) driver and

spindle motor pre-driver combination chip

FUNCTIONAL DESCRIPTION

Spindle

The spindle section contains both the low and high side

pre-drivers for a three phase DC brushless motor.

The digital commutation control, using the timing

information provided via the serial port, is responsible for

the proper switch-on and switch-off of the external power

FETs. It is also responsible for selecting the correct BEMF

comparator.

For optimum power efficiency, a continuous PWM method

is used to control the average current from the power

supply to the motor coils. This PWM mode, by controlling

the average power supply current, produces a lower

torque ripple and thus lower audible noise. In order to

reduce further acoustic noise the TDA5149G is provided

with a soft switching circuit to turn-on and turn-off linearly

the switching current under PWM control. The switching

transition time is controlled by the digital commutation

circuit and is fixed to 50% of the time between two

zero-crossings, i.e. 30° of the electrical revolution.

Soft switching is achieved by activating, during

commutation, a free-running duty-cycle modulator

controlled by a linearly decreasing voltage across a

capacitor. This will reduce the current smoothly in the

off-going leg to zero. In conjunction with this additional

PWM open loop, the average current control regulates the

sum of the current in the off-going and on-going leg.

This method requires two PWM control loops; one to

control the average current (main loop) and one to control

the current in the off-going leg. The swapping of the two

loops is realized with a pair of analog switches that are

sequentially switched by the digital commutation circuitry.

The PWM control also causes PWM pulses on the back

EMF. These pulses disturb correct sensing of the back

EMF for the zero-crossing detection. Consequently,

edge-triggered latches are inserted behind the back EMF

comparators, thus ensuring reliable back EMF sensing.

In the SPINMODE, programmable via the serial bus, the

user can feed their own commutation pulses to the

pre-drivers and control the motor in the stepper-motor

mode. The commutation pulses are applied to the

TDA5149G via the serial bus by setting the COMMCLK bit

successively to logic 1 and logic 0.

TDA5149G

The different control modes of the TDA5149G can be

commanded via the serial bus. These modes are as

follows:

• Sleep mode: all analog circuits, except the power supply

monitor, are switched off to reduce the power

consumption of both the 12 and 5 V supplies.

• Disable mode: the output voltage of all pre-drivers is

LOW thus the external power MOSFETs are not

conducting.

• Brake mode: all low side pre-drivers are turned on

(output voltage HIGH) thus switching on the low-side

power MOSFETs. In this way the back EMF voltage of

the motor is short-circuited to ground.

Voice coil motor

The VCM is a linear, symmetrical, class AB, H-bridge type

power amplifier with all power devices on-chip. The driver

is a transconductance amplifier that controls the output

currents up to 1.65 A. The driver is constructed in a

master-slave configuration with the zero current level

internally adjusted in such a way that it corresponds to the

middle of the output swing. Moreover, the gain of the slave

has been made greater than 1 in order to ensure full

saturation of the driver output VCM+.

The gain of the closed loop is programmable, using the

V

GAINSEL

bus. A sense resistor (Rs) allows the measurement of the

VCM current. The voltage across this resistor is connected

to an accurate sense amplifier with a typical gain of 5.

The output of the sense amplifier (V

to the input of the VCM amplifier. Because of the symmetry

of the circuit, the compensation network can be connected

between the VCM1 input and the VCM− output.

Control modes such as VCM-BRAKE, VCM-DISABLE and

VCM-PARK can be controlled via the serial bus.

Latch drivers

The TDA5149G provides the possibility of driving an

external latch to secure the VCM heads. There are two

modes; the activate mode (LACTIVE) and the hold mode

(LHOLD). The hold mode is used to preserve power.

Both modes are controlled via the serial bus. The drivers

are switched off during the SLEEP mode or in the event of

a power-down.

bit. This bit can be programmed via the serial

CMSENSOUT

) is fed back

1996 May 06 8

Philips Semiconductors Product specification

12 V Voice Coil Motor (VCM) driver and

spindle motor pre-driver combination chip

Power-on/power-off reset

The power-on reset circuitry monitors the analog, digital

and general supplies. The voltage thresholds have been

set internally for both supplies, i.e. 4.4 V for V

V

, and 10.5 V for VDD. External adjustment and

DDD

filtering, to suppress supply spikes, has been made

possible through the pins POR5

and POR12

ADJ

When either of the supplies falls below their threshold

levels, the reset circuit provides two active LOW output

signals. The RESETA signal is a full CMOS output and the

RESETP signal has an active pull-down MOS transistor

with a passive pull-up resistance of 10 kΩ. The latter can

be used for emulation purposes. Both signals remain LOW

until the supply voltages are again above the threshold

level, delayed by a time constant period that is determined

by the value of the capacitor connected to pin POR

A park sequence is initiated on a reset fault. This includes

disabling the actuator latch drivers and starting a delayed

spindle brake operation by switching on the low side

pre-drivers simultaneously. This brake delay is determined

by an external RC combination connected to

BRAKEDELAY. Actuator PARK and spindle BRAKE can

also be controlled via the serial port.

At power-up, the two reset output signals (RESETA and

RESETP) will remain LOW as long as either supply

voltage is below the specified threshold plus the hysteresis

voltage. Once the supply voltages are above their specific

trip levels, the two reset signals become HIGH after the

power-on reset delay (POR

). This delay time is

DELAY

determined by the value of the capacitor connected to the

POR

DELAY

pin.

DDA

ADJ

and

.

DELAY

.

TDA5149G

To ensure that the stored energy in the clamp capacitor is

only used for the park operation, the CLAMP input must be

isolated from the power supply. This can be achieved by

using a Schottky diode or a reverse connected N-channel

power FET (see Fig.1). The TDA5149G provides an

output H0 to control this power FET.

At power-down the brake delay circuit is also enabled.

The brake delay circuit is supplied by the energy stored in

the capacitor (charged during normal operation from VDD)

that is connected to the BRAKEPOWER pin. Both the

BRAKEDELAY and BRAKEPOWER pins are then isolated

from the 12 V supply voltage. When the voltage on the

BRAKEDELAY pin reaches a value of 1.6 V (typ.), the

low-side external power FETs are turned on to brake the

spindle motor. The BRAKEPOWER capacitor then

supplies the current to keep the power FETs conducting.

This means that the voltage on this capacitor decreases

with time.

Serial port

The serial port is used to modify the various operational

modes of the TDA5149G and to adjust the timing

parameters to ensure the proper commutation sequence

of the spindle motor. It is a synchronous, slave only,

three-wire communication port with data (SDATA), clock

(SCLOCK) and enable (SENABLE) inputs.

The serial port requires the data to be sent in bytes, the

LSB (data 0) to be sent first and the MSB (address 2) last.

The three most significant bits (MSBs) determine the

register address, the remaining five bits represent the

data, which means up to 8 registers can be independently

addressed.

Powerless park/brake

As with the normal retract procedure, an actuator park

sequence is initiated whenever a power-down situation

occurs. The power-on/power-off reset circuit generates the

two active LOW reset signals and also activates the VCM

park circuit. The VCM park circuit provides a voltage,

retrieved from the rectified back EMF voltage of the

running-out spindle, of 1.2 V (typ.) to the VCM pin.

The voltage at pin VCM+ is 0 V. This voltage is supplied by

the capacitor C

that is connected to the CLAMP pin.

CLAMP

This capacitor smooths the rectified back EMF and stores

the electrical energy generated by the motor.

1996 May 06 9

When SENABLE is LOW, the serial port is disabled and

the IC is not affected by any change both on SDATA and

SCLOCK. When SENABLE is HIGH the data is written

serially to the shift register on the rising edge of SCLOCK.

When SENABLE goes LOW the shifting sequence is

stopped and the last 8 bits that are clocked in are latched

into the appropriate control register. Therefore, the

transmission of two consecutive bytes requires that

SENABLE is LOW for at least a duration of ‘t’

(see Chapter “Characteristics”).

Loading...

Loading...