Page 1

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte

FIFOs and Motorola µP interface

Rev. 03 — 29 November 2005 Product data sheet

1. General description

The SC68C752B is a dual Universal Asynchronous Receiver/Transmitter (UART) with

64-byte FIFOs, automatic hardware/software flow control, and data rates up to 5 Mbit/s.

The SC68C752B offers enhanced features. It has a Transmission Control Register (TCR)

that stores receiver FIFO threshold levels to start/stop transmission during hardware and

software flow control. With the FIFO Rdy register, the software gets the status of

TXRDY/RXRDY for all four ports in one access. On-chip status registers provide the user

with error indications, operational status, and modem interface control. System interrupts

may be tailored to meet user requirements. An internal loopback capability allows

on-board diagnostics.

The UART transmits data, sent to it over the peripheral 8-bit bus, on the TX signal and

receives characters on the RX signal. Characters can be programmed to be 5 bits, 6 bits,

7 bits, or 8 bits. The UART has a 64-byte receive FIFO and transmit FIFO and can be

programmed to interrupt at different trigger levels. The UART generates its own desired

baud rate based upon a programmable divisor and its input clock. It can transmit even,

odd, or no parity and 1, 1.5, or 2 stop bits. The receiver can detect break, idle, or framing

errors, FIFO overflow, and parity errors. The transmitter can detect FIFO underflow. The

UART also contains a software interface for modem control operations, and has software

flow control and hardware flow control capabilities.

2. Features

The SC68C752B is available in LQFP48 and HVQFN32 packages.

■ Dual channel with Motorola µP interface

■ Up to 5 Mbit/s data rate

■ 64-byte transmit FIFO

■ 64-byte receive FIFO with error flags

■ Programmable and selectable transmit and receive FIFO trigger levels for DMA and

interrupt generation

■ Software/hardware flow control

◆ Programmable Xon/Xoff characters

◆ Programmable Auto-RTS and Auto-CTS

■ Optional data flow resume by Xon any character

■ DMA signalling capability for both received and transmitted data

■ Supports 5 V, 3.3 V and 2.5 V operation

■ 5 V tolerant inputs

■ Software selectable baud rate generator

Page 2

Philips Semiconductors

■ Prescaler provides additional divide-by-4 function

■ Industrial temperature range (−40 °C to +85 °C)

■ Fast data bus access time

■ Programmable Sleep mode

■ Programmable serial interface characteristics

◆ 5-bit, 6-bit, 7-bit, or 8-bit characters

◆ Even, odd, or no parity bit generation and detection

◆ 1, 1.5, or 2 stop bit generation

■ False start bit detection

■ Complete status reporting capabilities in both normal and Sleep mode

■ Line break generation and detection

■ Internal test and loopback capabilities

■ Fully prioritized interrupt system controls

■ Modem control functions (CTS, RTS, DSR, DTR, RI, and CD)

3. Ordering information

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

Table 1: Ordering information

Type number Package

Name Description Version

SC68C752BIB48 LQFP48 plastic low profile quad flat package; 48 leads;

body 7 × 7 × 1.4 mm

SC68C752BIBS HVQFN32 plastic thermal enhanced very thin quad flat package;

no leads; 32 terminals; body 5 × 5 × 0.85 mm

SOT313-2

SOT617-1

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 2 of 49

Page 3

Philips Semiconductors

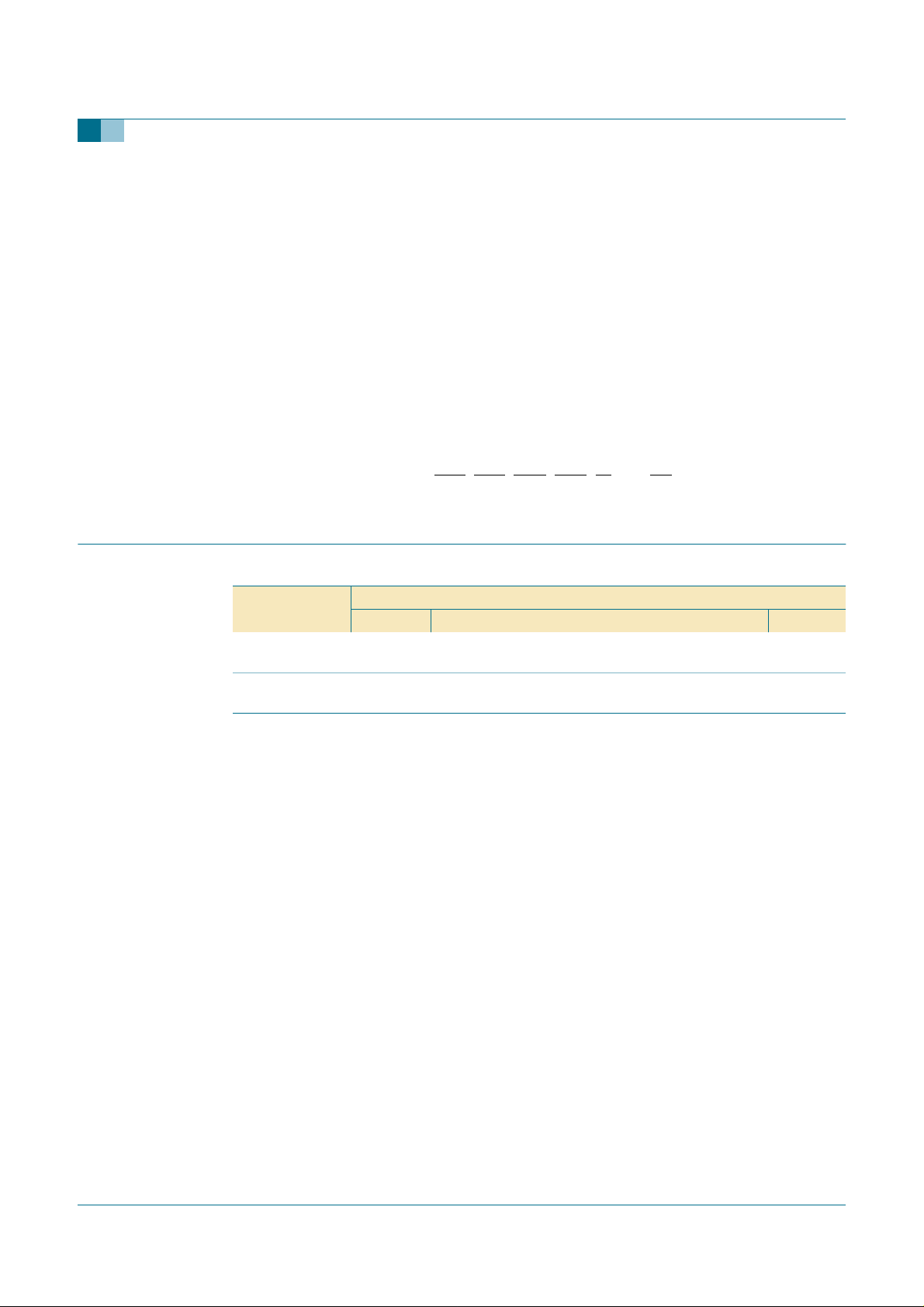

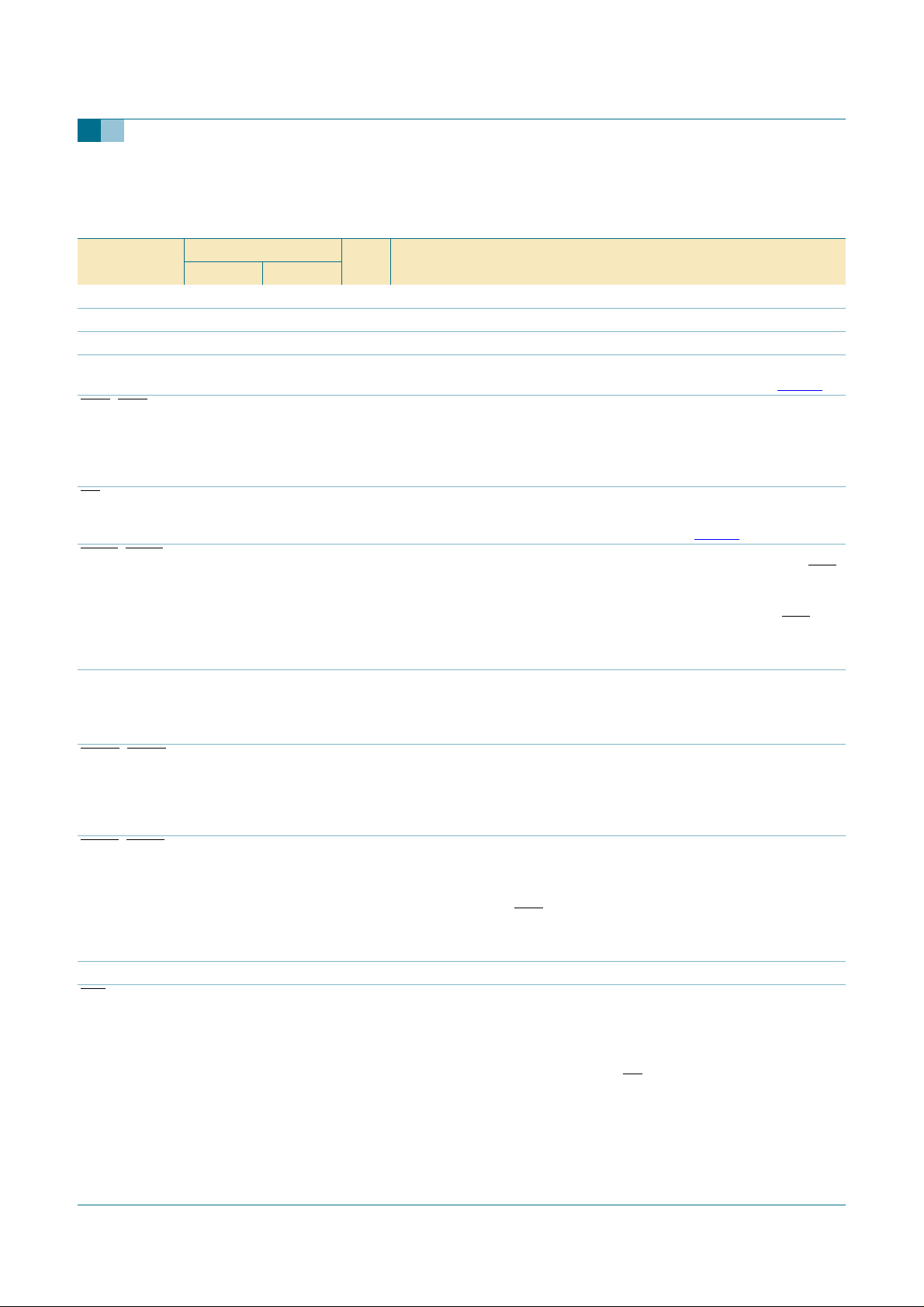

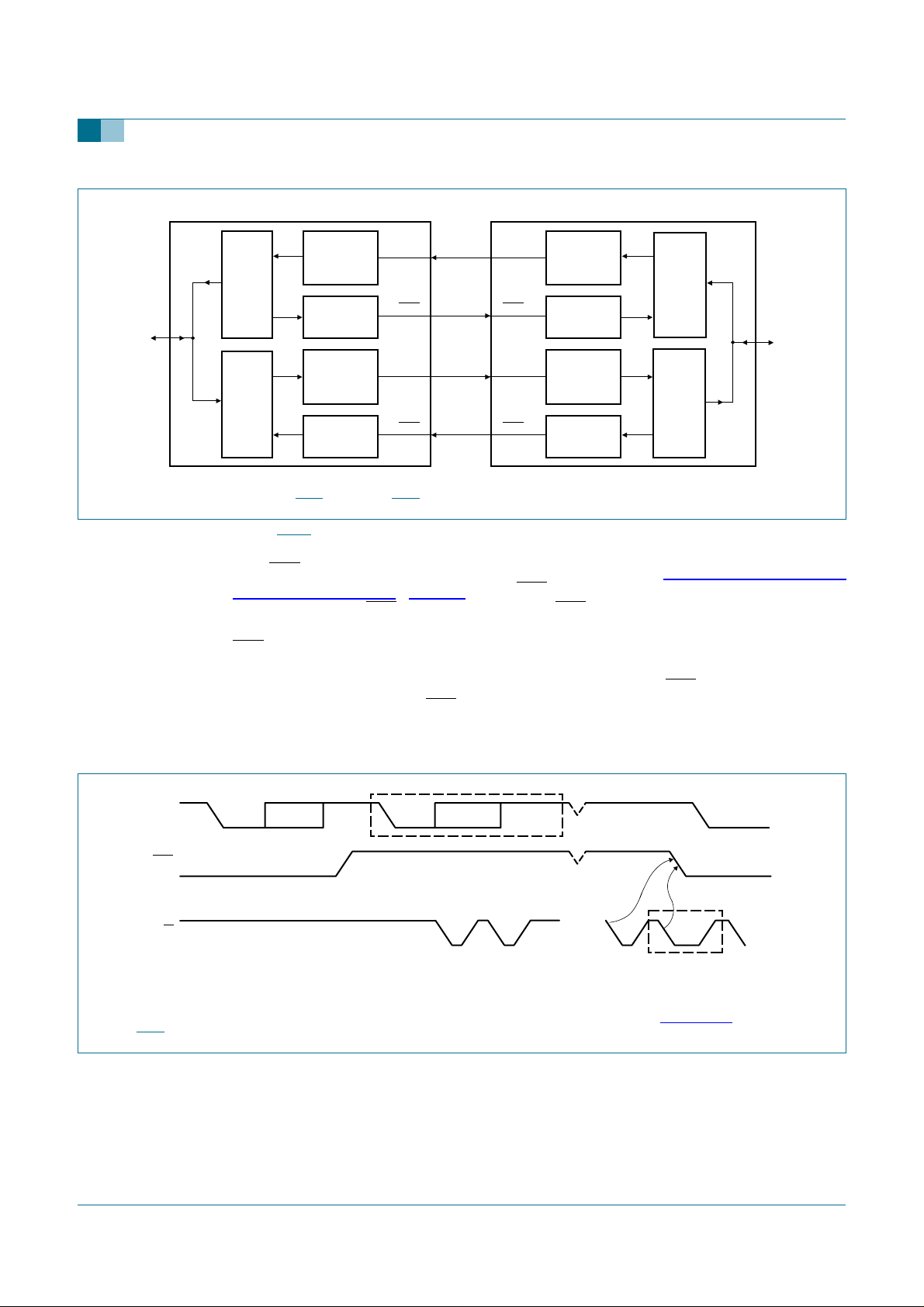

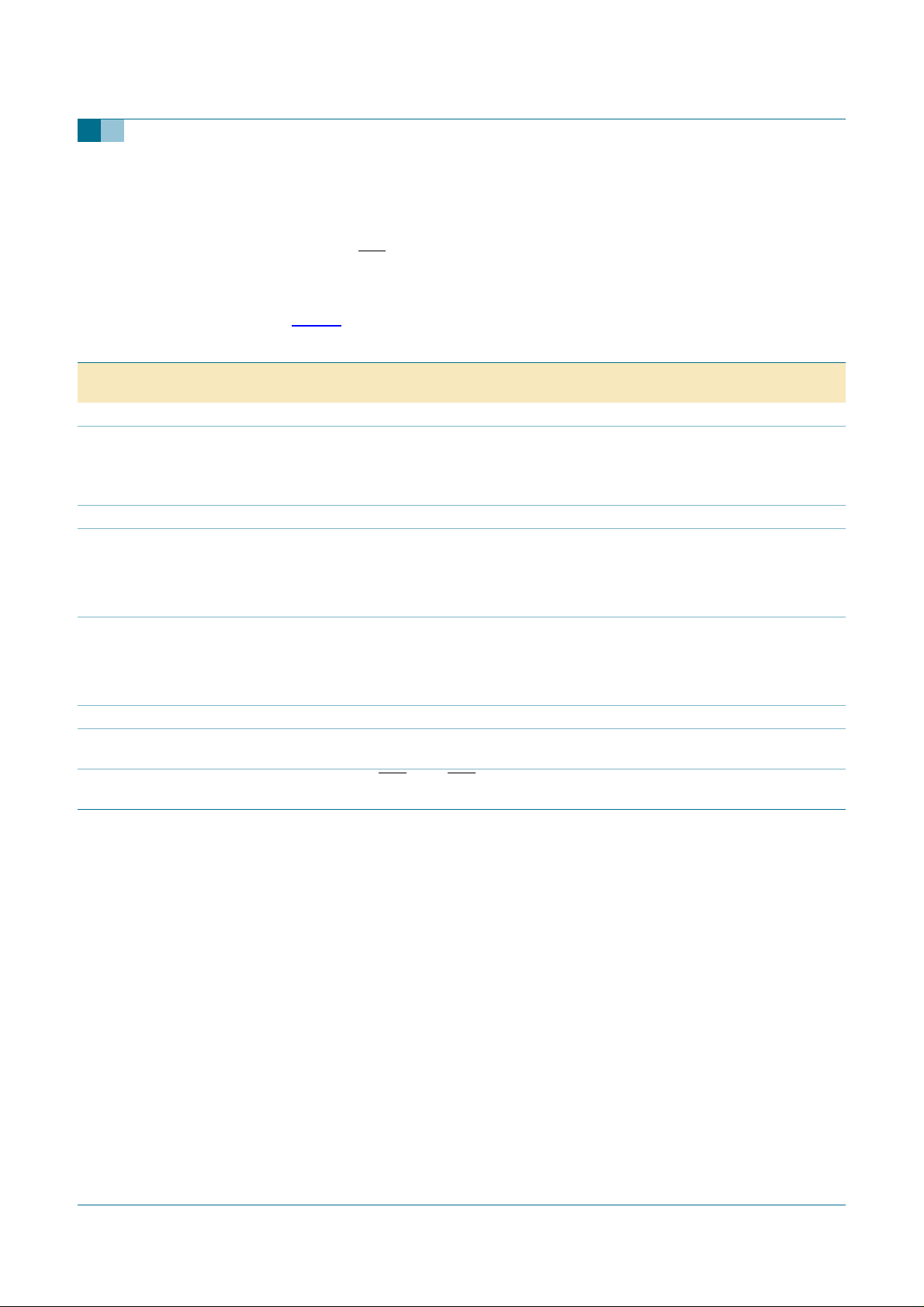

4. Block diagram

SC68C752B

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

D0 to D7

R/W

RESET

A0 to A3

CS

DATA BUS

AND

CONTROL

LOGIC

REGISTER

SELECT

LOGIC

AND

CONTROL SIGNALS

INTERCONNECT BUS LINES

TRANSMIT

FIFO

REGISTER

FLOW

CONTROL

LOGIC

RECEIVE

FIFO

REGISTER

FLOW

CONTROL

LOGIC

TRANSMIT

SHIFT

REGISTER

RECEIVE

SHIFT

REGISTER

TXA, TXB

RXA, RXB

DTRS, DTRB

RTSA, RTSB

OPA, OPB

MODEM

TXRDYA, TXRDYB

IRQ

RXRDYA, RXRDYB

INTERRUPT

CONTROL

LOGIC

CLOCK AND

BAUD RATE

GENERATOR

XTAL2XTAL1

CONTROL

LOGIC

002aab017

CTSA, CTSB

RIA, RIB

CDA, CDB

DSRA, DSRB

Fig 1. Block diagram of SC68C752B

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 3 of 49

Page 4

Philips Semiconductors

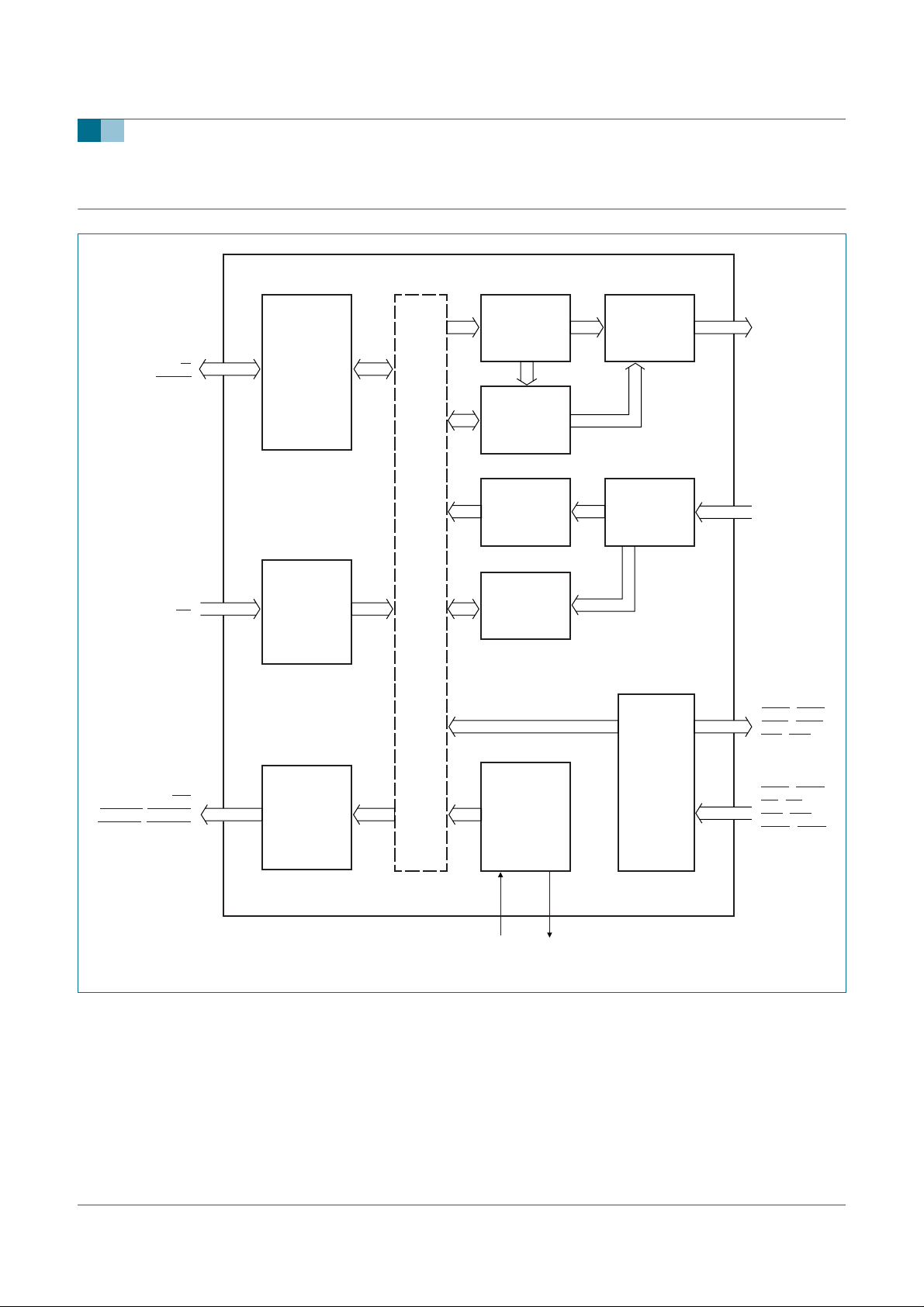

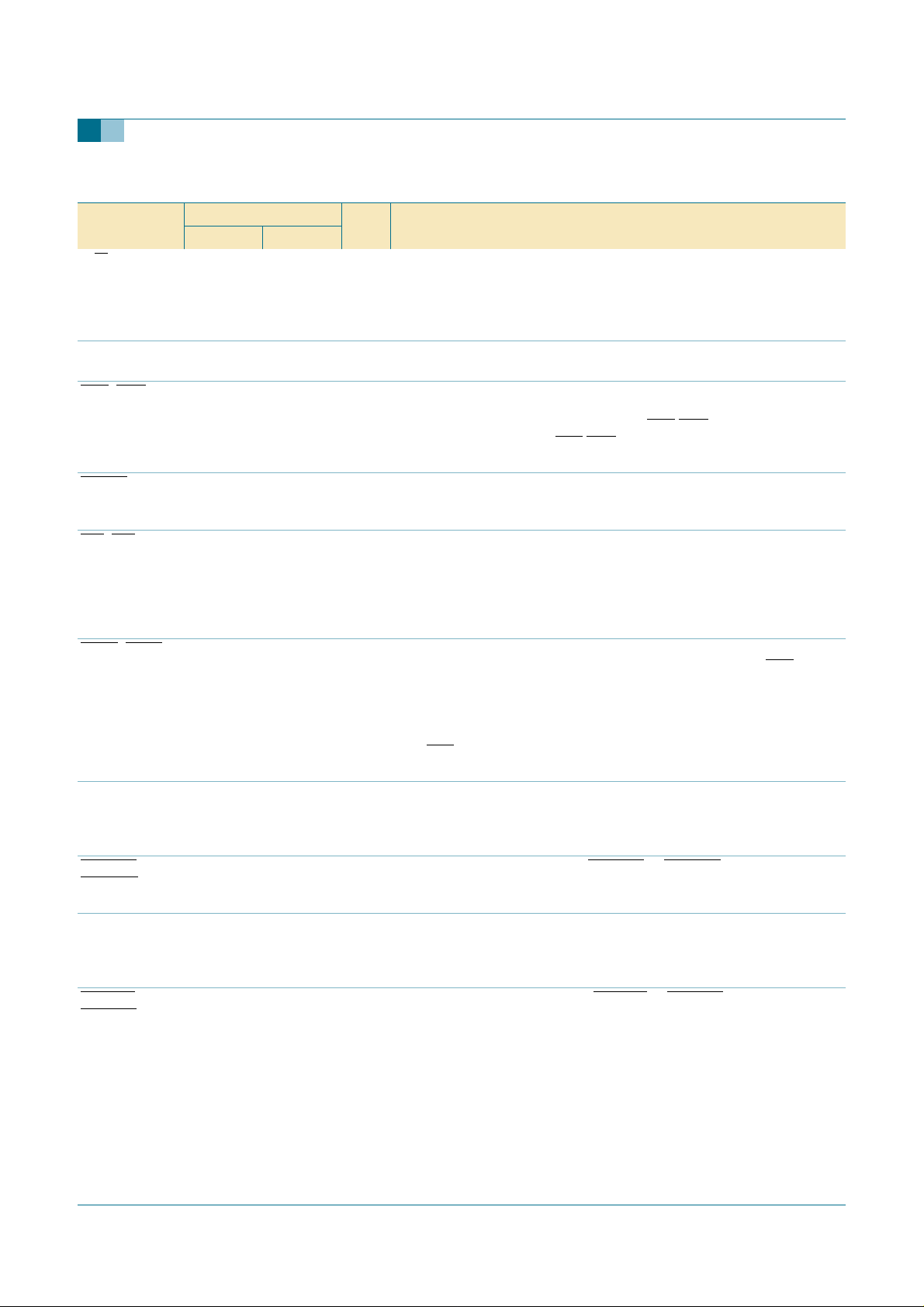

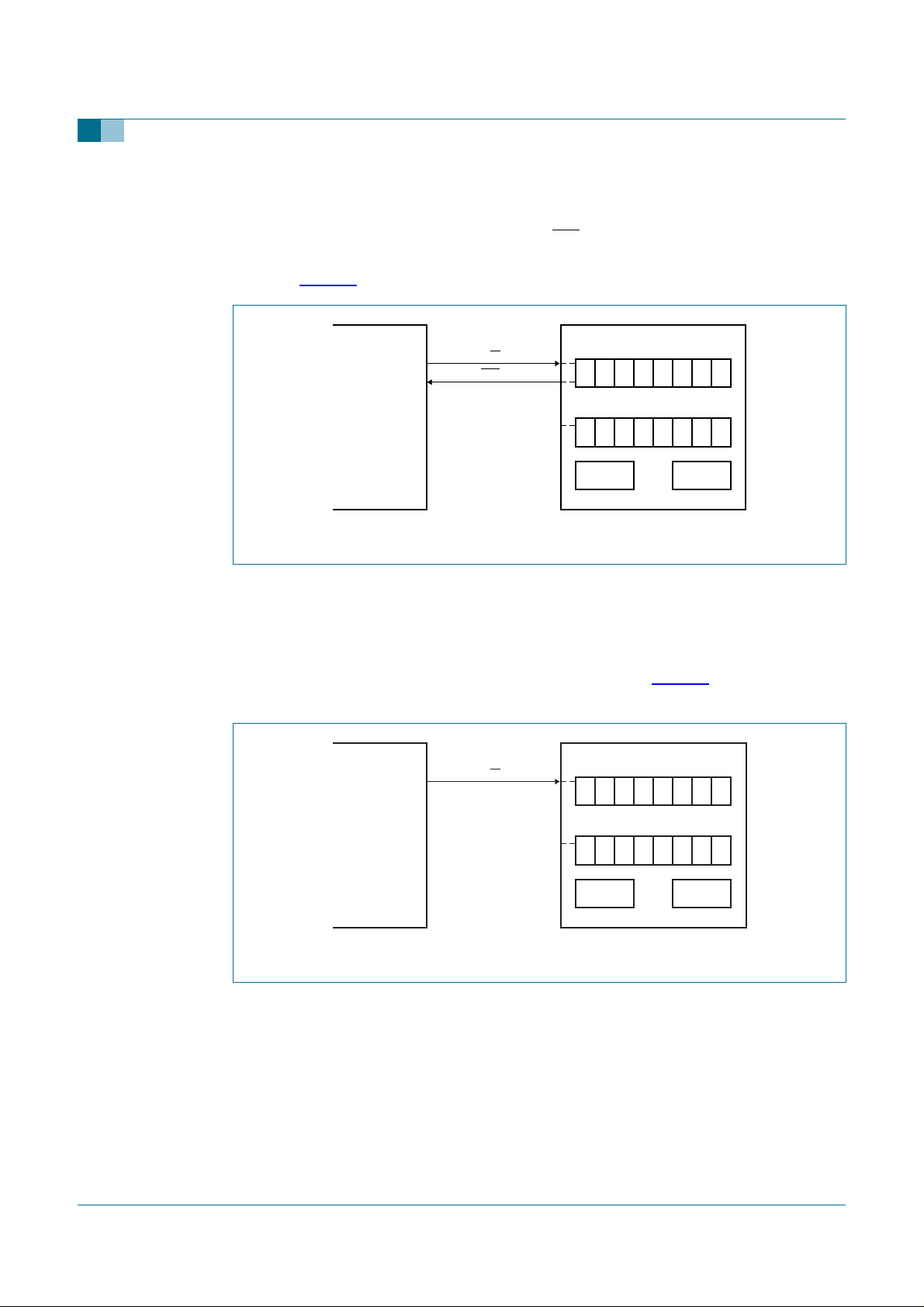

5. Pinning information

5.1 Pinning

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

CC

V

RIA

DSRA

CTSA

n.c.

4847464544434241403938

37

1

D5 RESET

2

D6 DTRB

3

D7 DTRA

4

RXB RTSA

5

RXA OPA

TXRDYB RXRDYA

6

7

TXA IRQ

8

TXB n.c.

9

OPB A0

10

CS A1

11

A3 A2

12

n.c. n.c.

1314151617181920212223

XTAL1 D4

XTAL2 D3

Fig 2. Pin configuration for LQFP48

terminal 1

index area

1 24

D6 RESET

2 23

D7 RTSA

3 22

RXB OPA

4 21

RXA IRQ

5 20

TXA n.c.

6 19

TXB A0

7 18

OPB

8 17

CS

SC68C752BIB48

CC

GND D0

V

RXRDYB TXRDYA

DSRB

R/W D2

CDB D1

D5D4D3D2D1D0V

32313029282726

SC68C752BIBS

9

10111213141516

A3

XTAL1

XTAL2

Transparent top view

R/W

GND

n.c.

RIB CDA

RTSB

RTSB

CC

CTSB

CTSA

25

CTSB

36

35

34

33

32

31

30

29

28

27

26

25

24

002aab018

GND

A1

A2

002aac014

Fig 3. Pin configuration for HVQFN32

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 4 of 49

Page 5

Philips Semiconductors

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

5.2 Pin description

Table 2: Pin description

Symbol Pin Type Description

LQFP48 HVQFN32

A0 28 19 I Address 0 select bit. Internal registers address selection.

A1 27 18 I Address 1 select bit. Internal registers address selection.

A2 26 17 I Address 2 select bit. Internal registers address selection.

A3 11 9 I Address 3. A3 is used to select Channel A or Channel B. A logic LOW

selects Channel A, and a logic HIGH selects Channel B. (See

CDA, CDB 40, 16 - I Carrier Detect (active LOW). These inputs are associated with

individual UART ChannelA and Channel B. A logic LOW on these pins

indicates that a carrier has been detected by the modem for that

channel. The state of these inputs is reflected in the Modem Status

Register (MSR).

CS 10 8 I Chip Select (active LOW). This pin enables data transfers between the

user CPU and the SC68C752B for the channel(s) addressed. Individual

UART sections (A, B) are addressed by A3. See

CTSA, CTSB 38, 23 25, 15 I Clear to Send (active LOW). These inputs are associated with

individual UART Channel A and Channel B. A logic 0 (LOW) on the

pins indicates the modem or data set is ready to accept transmit data

from the SC68C752B. Status can be tested by reading MSR[4]. These

pins only affect the transmit and receive operations when Autofunction is enabled via the Enhanced Feature Register EFR[7] for

hardware flow control operation.

D0 to D7 44, 45, 46,

47, 48, 1,

2, 3

DSRA, DSRB 39, 20 - I Data Set Ready (active LOW). These inputs are associated with

DTRA, DTRB 34, 35 - O Data Terminal Ready (active LOW). These outputs are associated with

GND 17, 24 13 I Signal and power ground.

IRQ 30 21 O Interrupt Request. Interrupts from UART Channel A and Channel B are

27, 28, 29,

30, 31, 32,

1, 2

I/O Data bus (bidirectional). These pins are the 8-bit, 3-state data bus for

transferring information to or from the controlling CPU. D0 is the least

significant bit and the first data bit in a transmit or receive serial data

stream.

individual UART ChannelA and Channel B. A logic 0 (LOW) on these

pins indicates the modem or data set is powered-on and is ready for data

exchange with the UART. The state of these inputs is reflected in the

Modem Status Register (MSR).

individual UART ChannelA and Channel B. A logic 0 (LOW) on these

pins indicates that the SC68C752B is powered-on and ready.Thesepins

can be controlled via the Modem Control Register. Writing a logic 1 to

MCR[0] will set the

The output of these pins will be a logic 1 after writing a logic 0 to MCR[0],

or after a reset.

wire-ORed internally to function as a single IRQ interrupt. This pin

transitions to a logic 0 (if enabled by the Interrupt Enable Register)

whenever a UART channel(s) requires service. Individual channel

interrupt status can be determined by addressing each channel through

its associated internal register, using

resistor must be connected between this pin and V

DTR output to logic 0 (LOW), enabling the modem.

CS and A3. An external pull-up

Table 3.

.

CC

Table 3.)

CTS

CTS

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 5 of 49

Page 6

Philips Semiconductors

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

Table 2: Pin description

Symbol Pin Type Description

LQFP48 HVQFN32

R/W 15 12 I A logic LOW on this pin will transfer the contents of the data bus (D[0:7])

n.c. 12, 25, 29,3714, 20 - not connected

OPA, OPB 32, 9 22, 7 O User defined outputs. This function is associated with individual

RESET 36 24 I Reset (active LOW). This pin will reset the internal registers and all the

RIA, RIB 41, 21 - I Ring Indicator (active LOW). These inputs are associated with

RTSA, RTSB 33, 22 23, 16 O Request to Send (active LOW). These outputs are associated with

RXA, RXB 5, 4 4, 3 I Receive data input. These inputs are associated with individual serial

RXRDYA,

RXRDYB

TXA, TXB 7, 8 5, 6 O Transmit data A, B. These outputs are associated with individual serial

TXRDYA,

TXRDYB

31, 18 - O Receive Ready (active LOW).

43, 6 - O Transmit Ready (active LOW).

…continued

from an external CPU to an internal register that is defined by address

bits A[0:2]. A logic HIGH on this pin will load the contents of an internal

register defined by address bits A[0:2] on the SC68C752B data bus

(D[0:7]) for access by an external CPU.

Channel A and Channel B. The state of these pins is defined by the user

through the software settings of MCR[3].

MCR[3] is set to a logic 1.

logic 0. The output of these two pins is HIGH after reset.

outputs. The UART transmitter output and the receiver input will be

disabled during reset time. RESET is an active LOW input.

individual UART ChannelA and Channel B. A logic 0 on these pins

indicates the modem has received a ringing signal from the telephone

line. A LOW-to-HIGH transition on these input pins generates a modem

status interrupt, if enabled. The state of these inputs is reflected in the

Modem Status Register (MSR).

individual UART ChannelA and Channel B. A logic 0 on the

indicates the transmitter has data ready and waiting to send. Writing a

logic 1 in the Modem Control Register MCR[1] will set this pin to a

logic 0, indicating data is available. After a reset these pins are set to a

logic 1. These pins only affect the transmit and receive operations when

Auto-

RTS function is enabled via the Enhanced Feature Register

(EFR[6]) for hardware flow control operation.

channel data to the SC68C752B. During the local Loopback mode,

these RX input pins are disabled and TX data is connected to the UART

RX input internally.

the trigger level has been reached or the FIFO has at least one

character. It goes HIGH when the RX FIFO is empty.

transmit channel data from the SC68C752B. During the local Loopback

mode, the TX output pin is disabled and TX data is internally connected

to the UART RX input.

there are at least a trigger level number of spaces available or when the

FIFO is empty. It goes HIGH when the FIFO is full or not empty.

OPA/OPB is a logic 1 when MCR[3] is set to a

RXRDYA or RXRDYB goes LOW when

TXRDYA or TXRDYB go LOW when

OPA/OPB is a logic 0 when

RTS pin

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 6 of 49

Page 7

Philips Semiconductors

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

Table 2: Pin description

Symbol Pin Type Description

LQFP48 HVQFN32

V

CC

XTAL1 13 10 I Crystal or external clock input. Functions as a crystal input or as an

XTAL2 14 11 O Output of the crystal oscillator or buffered clock. (See also XTAL1.)

19, 42 26 I Power supply input.

…continued

external clock input. A crystal can be connected between XTAL1 and

XTAL2 to form an internal oscillator circuit (see

an external clock can be connected to this pin to provide custom data

rates.

XTAL2 is used as a crystal oscillator output or a buffered clock output.

Table 3: Channel selection using CS pin

CS A3 UART channel

1 - none

0 0 Channel A

0 1 Channel B

Figure 13). Alternatively,

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 7 of 49

Page 8

Philips Semiconductors

6. Functional description

The UART will perform serial-to-parallel conversion on data characters received from

peripheral devices or modems, and parallel-to-parallel conversion on data characters

transmitted by the processor. The complete status of each channel of the SC68C752B

UART can be read at any time during functional operation by the processor.

The SC68C752B can be placed in an alternate mode (FIFO mode) relieving the processor

of excessive software overhead by buffering received/transmitted characters. Both the

receiver and transmitter FIFOs can store up to 64 bytes (including three additional bits of

error status per byte for the receiver FIFO) and have selectable or programmable trigger

levels. Primary outputs RXRDY and TXRDY allow signalling of DMA transfers.

The SC68C752B has selectable hardware flow control and software flow control.

Hardware flow control significantly reduces software overhead and increases system

efficiency by automatically controlling serial data flow using the RTS output and CTS input

signals. Software flow control automatically controls data flow by using programmable

Xon/Xoff characters.

The UART includes a programmable baud rate generator that can divide the timing

reference clock input by a divisor between 1 and (216− 1).

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

6.1 Trigger levels

The SC68C752B provides independent selectable and programmable trigger levels for

both receiver and transmitter DMA and interrupt generation. After reset, both transmitter

and receiver FIFOs are disabled and so, in effect, the trigger level is the default value of

one byte. The selectable trigger levels are available via the FCR. The programmable

trigger levels are available via the Trigger Level Register (TLR).

6.2 Hardware flow control

Hardware flow control is comprised of Auto-CTS and Auto-RTS. Auto-CTS and Auto-RTS

can be enabled/disabled independently by programming EFR[7:6].

With Auto-CTS, CTS must be active before the UART can transmit data.

Auto-RTSonly activates the RTSoutput when there is enough room in the FIFO to receive

data and de-activates the RTS output when the RX FIFO is sufficiently full. The halt and

resume trigger levels in the TCR determine the levels at which RTS is

activated/deactivated.

If both Auto-CTS and Auto-RTS are enabled, when RTS is connected to CTS, data

transmission does not occur unless the receiver FIFO has empty space. Thus, overrun

errors are eliminated during hardware flow control. If not enabled, overrun errors occur if

the transmit data rate exceeds the receive FIFO servicing latency.

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 8 of 49

Page 9

Philips Semiconductors

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

UART 1 UART 2

SERIAL TO

PARALLEL

RX

FIFO

FLOW

CONTROL

D7 to D0

PARALLEL

TO SERIAL

TX

FIFO

FLOW

CONTROL

RX TX

RTS CTS

TX RX

CTS RTS

Fig 4. Auto flow control (Auto-RTS and Auto-CTS) example

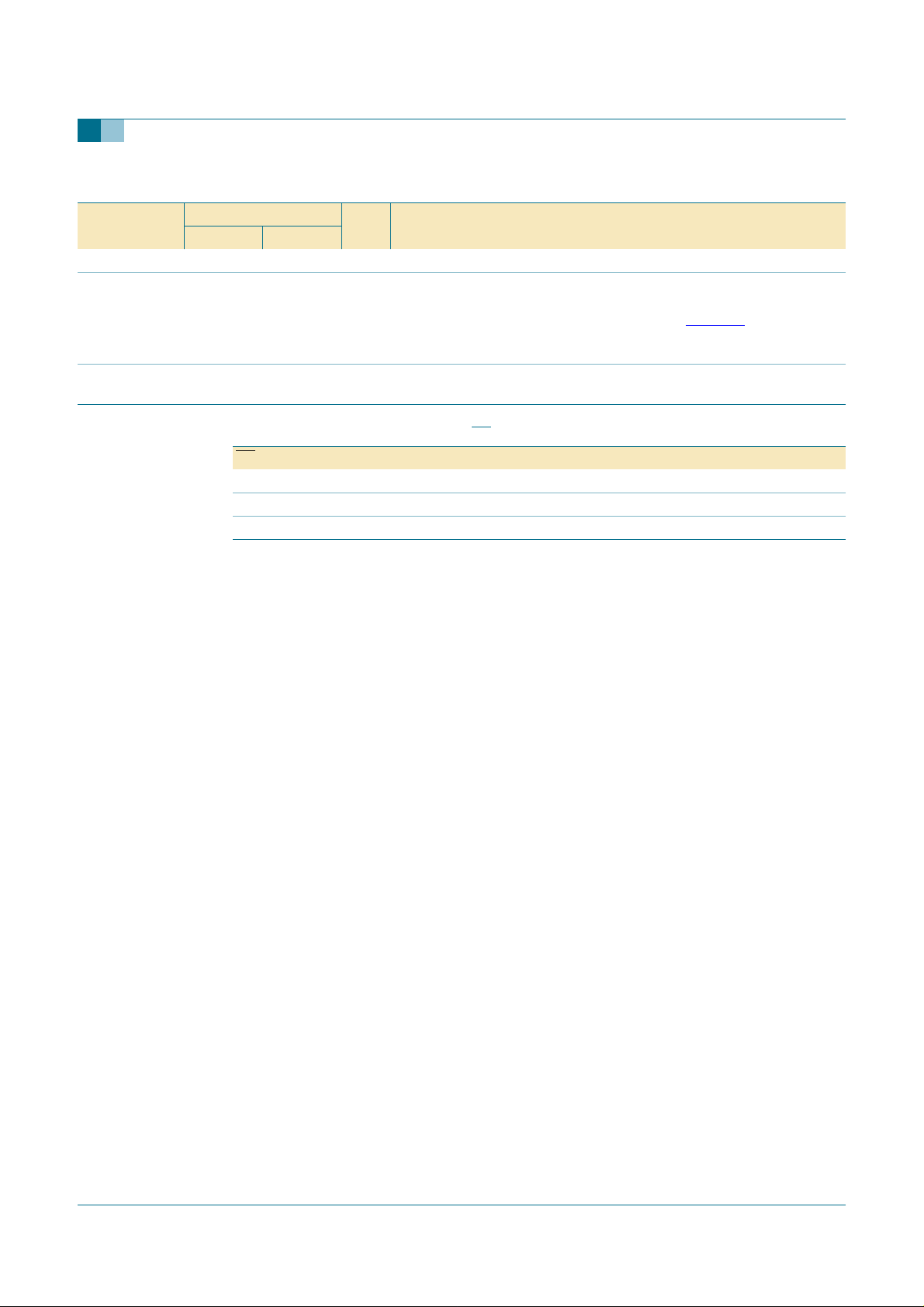

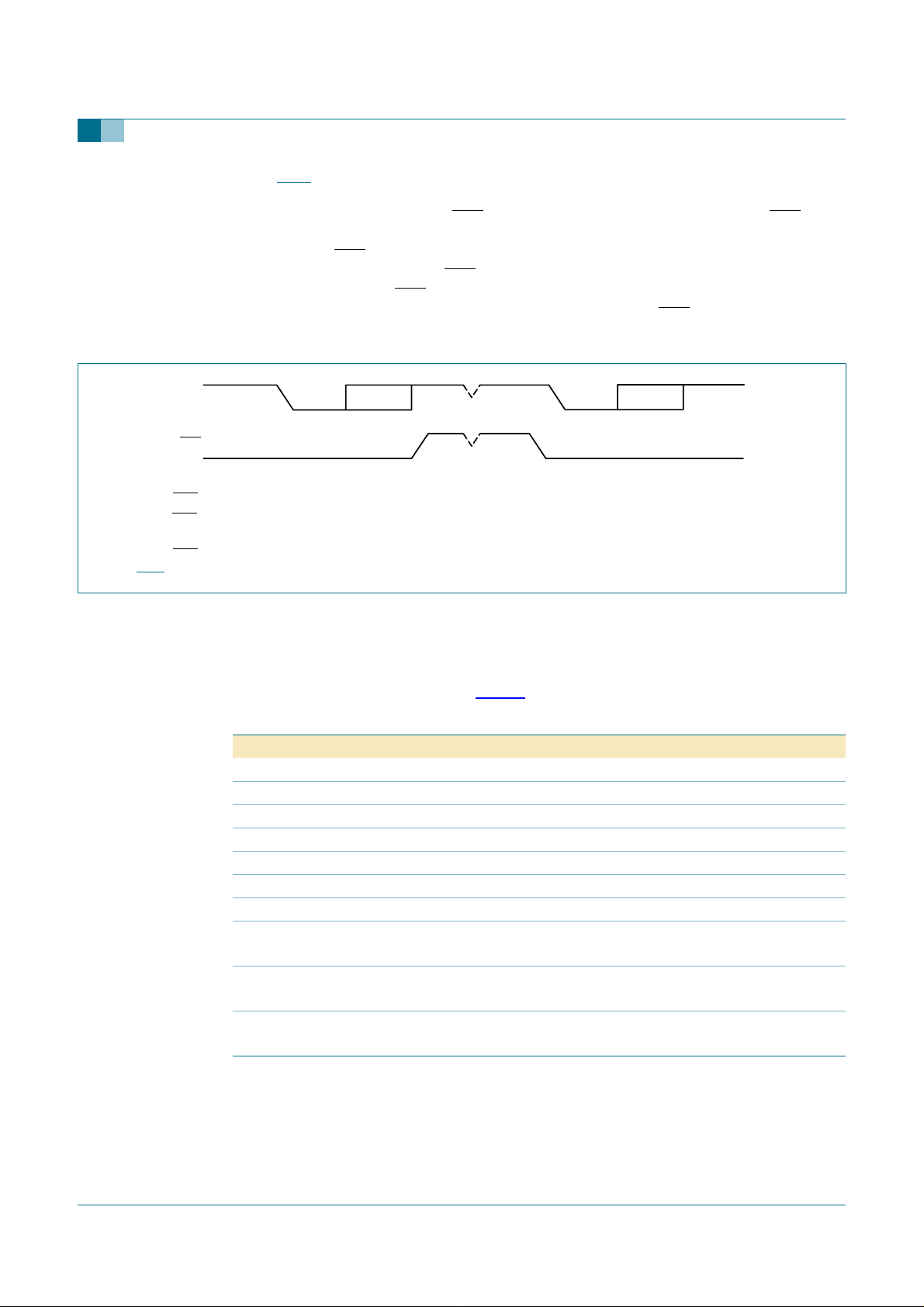

6.2.1 Auto-RTS

Auto-RTSdata flow control originates in the receiver block (see Figure 1 “Block diagram of

SC68C752B” on page 3). Figure 5 shows RTS functional timing. The receiver FIFO trigger

levelsused in Auto-RTS are stored in the TCR. RTS is active if the RX FIFO level is below

the halt trigger level in TCR[3:0]. When the receiver FIFO halt trigger level is reached,

RTS is de-asserted. The sending device (for example, another UART) may send an

additional byte after the trigger level is reached (assuming the sending UART has another

byte to send) because it may not recognize the de-assertion of RTS until it has begun

sending the additional byte. RTS is automatically reasserted once the receiver FIFO

reaches the resume trigger level programmed via TCR[7:4]. This re-assertion allows the

sending device to resume transmission.

PARALLEL

TO SERIAL

TX

FIFO

FLOW

CONTROL

D7 to D0

SERIAL TO

PARALLEL

RX

FIFO

FLOW

CONTROL

002aaa228

Start byte N Start byte N + 1 StartStop StopRX

RTS

R/W

(1) N = receiver FIFO trigger level.

(2) The two blocks in dashed lines cover the case where an additional byte is sent, as described in Section 6.2.1.

NN + 112

002aab086

Fig 5. RTS functional timing

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 9 of 49

Page 10

Philips Semiconductors

6.2.2 Auto-CTS

The transmitter circuitry checks CTS before sending the next data byte. When CTS is

active, the transmitter sends the next byte. To stop the transmitter from sending the

following byte, CTS must be de-asserted before the middle of the last stop bit that is

currently being sent. The Auto-CTS function reduces interrupts to the host system. When

flow control is enabled, CTS level changes do not trigger host interrupts because the

device automatically controls its own transmitter. Without Auto-CTS, the transmitter sends

any data present in the transmit FIFO and a receiver overrun error may result.

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

Start byte 0 to 7 StopTX

CTS

(1) When CTS is LOW, the transmitter keeps sending serial data out.

(2) When CTS goes HIGH before the middle of the last stop bit of the current byte, the transmitter finishes sending the current

byte, but is does not send the next byte.

(3) When CTS goes from HIGH to LOW, the transmitter begins sending data again.

Fig 6. CTS functional timing

Start byte 0 to 7 Stop

002aaa227

6.3 Software flow control

Software flow control is enabled through the Enhanced Feature Register and the Modem

Control Register. Different combinations of software flow control can be enabled by setting

different combinations of EFR[3:0]. Table 4 shows software flow control options.

Table 4: Software flow control options (EFR[0:3])

EFR[3] EFR[2] EFR[1] EFR[0] TX, RX software flow controls

0 0 X X no transmit flow control

1 0 X X transmit Xon1, Xoff1

0 1 X X transmit Xon2, Xoff2

1 1 X X transmit Xon1, Xon2, Xoff1, Xoff2

X X 0 0 no receive flow control

X X 1 0 receiver compared Xon1, Xoff1

X X 0 1 receiver compares Xon2, Xoff2

1011transmit Xon1, Xoff1

receiver compares Xon1 and Xon2, Xoff1 and Xoff2

0111transmit Xon2, Xoff2

receiver compares Xon1 and Xon2, Xoff1 and Xoff2

1111transmit Xon1, Xon2, Xoff1, Xoff2

receiver compares Xon1 and Xon2, Xoff1 and Xoff2

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 10 of 49

Page 11

Philips Semiconductors

There are two other enhanced features relating to software flow control:

• Xon Any function (MCR[5]): Operation will resume after receiving any character

after recognizing the Xoff character. It is possible that an Xon1 character is

recognized as an Xon Any character, which could cause an Xon2 character to be

written to the RX FIFO.

• Special character (EFR[5]): Incoming data is compared to Xoff2. Detection of the

special character sets the Xoff interrupt (IIR[4]) but does not halt transmission. The

Xoff interrupt is cleared by a read of the IIR. The special character is transferredto the

RX FIFO.

6.3.1 Receive flow control

When software flow control operation is enabled, the SC68C752B will compare incoming

data with Xoff1/Xoff2 programmed characters (in certain cases, Xoff1 and Xoff2 must be

received sequentially). When the correct Xoff character are received, transmission is

halted after completing transmission of the current character. Xoff detection also sets

IIR[4] (if enabled via IER[5]) and causes IRQ to go HIGH.

To resume transmission, an Xon1/Xon2 character must be received (in certain cases

Xon1 and Xon2 must be received sequentially). When the correct Xon characters are

received, IIR[4] is cleared, and the Xoff interrupt disappears.

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

6.3.2 Transmit flow control

Xoff1/Xoff2 character is transmitted when the RX FIFO has passed the HALTtrigger level

programmed in TCR[3:0].

Xon1/Xon2 character is transmitted when the RX FIFO reaches the RESUME trigger level

programmed in TCR[7:4].

The transmission of Xoff/Xon(s) follows the exact same protocol as transmission of an

ordinary byte from the FIFO. This means that even if the word length is set to be 5, 6, or 7

characters, then the 5, 6, or 7 least significant bits of Xoff1/Xoff2, Xon1/Xon2 will be

transmitted. (Note that the transmission of 5, 6, or 7 bits of a character is seldom done, but

this functionality is included to maintain compatibility with earlier designs.)

It is assumed that software flow control and hardware flow control will never be enabled

simultaneously. Figure 7 shows an example of software flow control.

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 11 of 49

Page 12

Philips Semiconductors

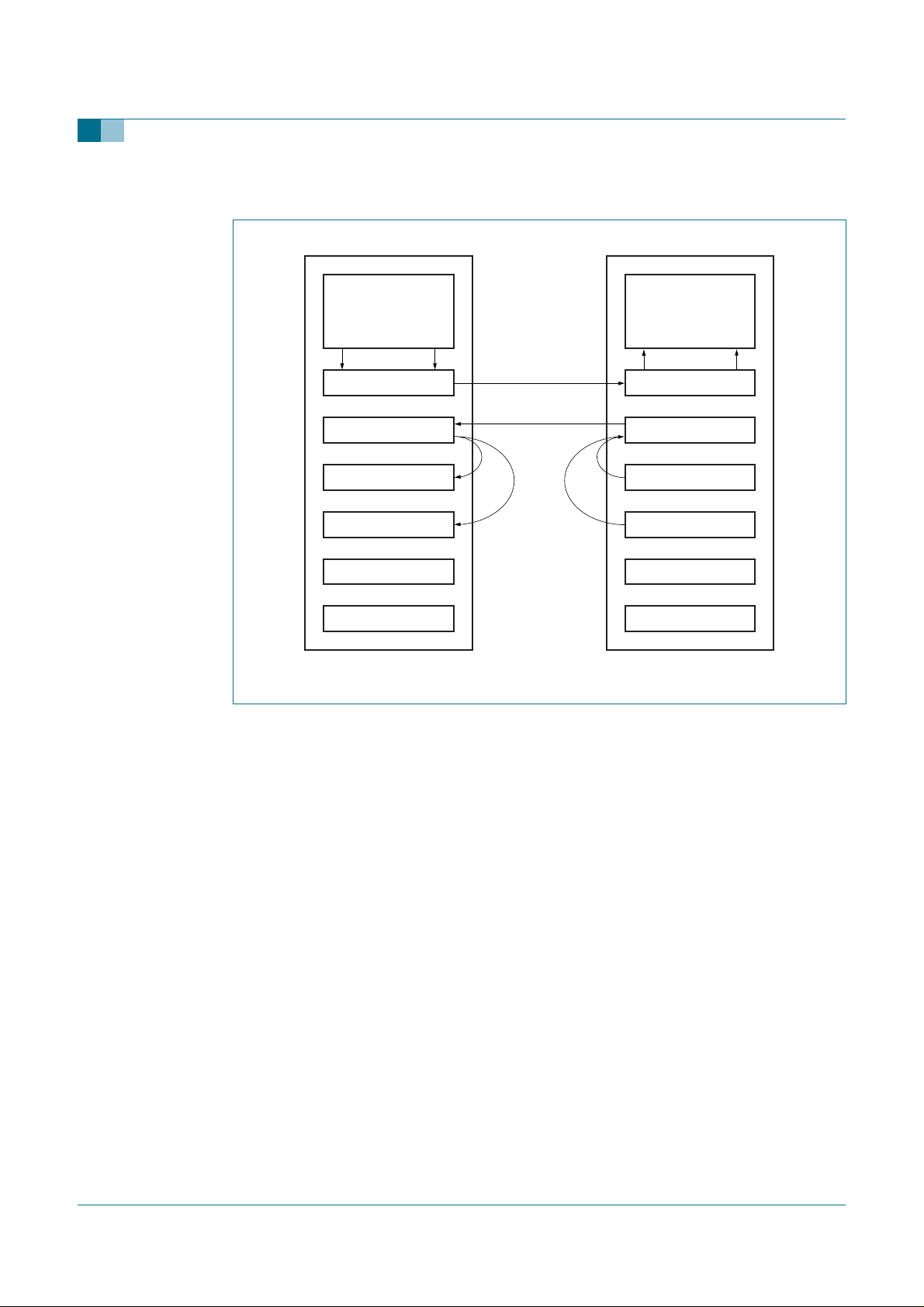

6.3.3 Software flow control example

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

UART2UART1

Fig 7. Software flow control example

6.3.3.1 Assumptions

UART1 is transmitting a large text file to UART2. Both UARTs are using software flow

control with single character Xoff (0F) and Xon (0D) tokens. Both have Xoff threshold

(TCR[3:0] = F) set to 60, and Xon threshold (TCR[7:4] = 8) set to 32. Both have the

interrupt receive threshold (TLR[7:4] = D) set to 52.

TRANSMIT FIFO

PARALLEL-TO-SERIAL

SERIAL-TO-PARALLEL

Xon1 WORD

Xon2 WORD

Xoff1 WORD

Xoff2 WORD

data

Xoff–Xon–Xoff

compare

programmed

Xon-Xoff

characters

RECEIVE FIFO

SERIAL-TO-PARALLEL

PARALLEL-TO-SERIAL

Xon1 WORD

Xon2 WORD

Xoff1 WORD

Xoff2 WORD

002aaa229

UART1 begins transmission and sends 52 characters, at which point UART2 will generate

an interrupt to its processor to service the RX FIFO, but assume the interrupt latency is

fairly long. UART1 will continue sending characters until a total of 60 characters have

been sent. At this time, UART2 will transmit a 0Fh to UART1, informing UART1 to halt

transmission. UART1 will likely send the 61st character while UART2 is sending the Xoff

character. Now UART2 is serviced and the processor reads enough data out of the RX

FIFO that the level drops to 32. UART2 will now send a 0Dh to UART1, informing UART1

to resume transmission.

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 12 of 49

Page 13

Philips Semiconductors

6.4 Reset

Table 5 summarizes the state of register after reset.

Table 5: Register reset functions

Register Reset control Reset state

Interrupt Enable Register

Interrupt Identification Register

FIFO Control Register

Line Control Register

Modem Control Register

Line Status Register

Modem Status Register

Enhanced Feature Register

Receiver Holding Register

Transmitter Holding Register

Transmission Control Register

Trigger Level Register

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

RESET all bits cleared

RESET bit 0 is set; all other bits cleared

RESET all bits cleared

RESET reset to 0001 1101 (1Dh)

RESET all bits cleared

RESET bits 5 and 6 set; all other bits cleared

RESET bits 0 to 3 cleared; bits 4 to 7 input signals

RESET all bits cleared

RESET pointer logic cleared

RESET pointer logic cleared

RESET all bits cleared

RESET all bits cleared

Remark: Registers DLL, DLH, SPR, XON1, XON2, XOFF1, XOFF2 are not reset by the

top-level reset signal RESET, that is, they hold their initialization values during reset.

Table 6 summarizes the state of registers after reset.

Table 6: Signal

Signal Reset control Reset state

TX

RTS RESET HIGH

DTR RESET HIGH

RXRDY RESET HIGH

TXRDY RESET LOW

RESET functions

RESET HIGH

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 13 of 49

Page 14

Philips Semiconductors

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

6.5 Interrupts

The SC68C752B has interrupt generation and prioritization (six prioritized levels of

interrupts) capability. The Interrupt Enable Register (IER) enables each of the six types of

interrupts and the IRQ signal in response to an interrupt generation. The IER can also

disable the interrupt system by clearing bits 0:3, 5:7. When an interrupt is generated, the

IIR indicates that an interrupt is pending and provides the type of interrupt through

IIR[5:0]. Table 7 summarizes the interrupt control functions.

Table 7: Interrupt control functions

IIR[5:0] Priority

level

000001 None none none none

000110 1 receiver line status OE, FE, PE, or BI errors occur in

001100 2 RX time-out stale data in RX FIFO read RHR

000100 2 RHR interrupt DRDY (data ready)

000010 3 THR interrupt TFE (THR empty)

000000 4 modem status MSR[3:0] = 0 read MSR

010000 5 Xoff interrupt receive Xoff character(s)/special

100000 6 CTS, RTS

Interrupt type Interrupt source Interrupt reset method

FE, PE, BI: all erroneous

characters in the RX FIFO

(FIFO disable)

RX FIFO above trigger level

(FIFO enable)

(FIFO disable)

TX FIFO passes above trigger level

(FIFO enable)

character

RTSpin or CTS pin change state from

active (LOW) to inactive (HIGH)

characters are read from the

RX FIFO.

OE: read LSR

read RHR

read IIR or a write to the THR

receive Xon character(s)/Read of

IIR

read IIR

SC68C752B

It is important to note that for the framing error, parity error, and break conditions, LSR[7]

generates the interrupt. LSR[7] is set when there is an error anywhere in the RX FIFO,

and is cleared only when there are no more errors remaining in the FIFO. LSR[4:2] always

represent the error status for the received character at the top of the RX FIFO. Reading

the RX FIFO updates LSR[4:2] to the appropriate status for the new character at the top of

the FIFO. If the RX FIFO is empty, then LSR[4:2] are all zeros.

For the Xoff interrupt, if an Xoff flow character detection caused the interrupt, the interrupt

is cleared by an Xon flow character detection. If a special character detection caused the

interrupt, the interrupt is cleared by a read of the IIR.

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 14 of 49

Page 15

Philips Semiconductors

6.5.1 Interrupt mode operation

In Interrupt mode (if any bit of IER[3:0] is 1) the processor is informed of the status of the

receiver and transmitter by an interrupt signal, IRQ. Therefore, it is not necessary to

continuously poll the Line Status Register (LSR) to see if any interrupt needs to be

serviced. Figure 8 shows Interrupt mode operation.

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

PROCESSOR

Fig 8. Interrupt mode operation

6.5.2 Polled mode operation

In Polled mode (IER[3:0] = 0000) the status of the receiver and transmitter can be

checkedby polling the Line Status Register (LSR). This mode is an alternative to the FIFO

Interrupt mode of operation where the status of the receiver and transmitter is

automatically known by means of interrupts sent to the CPU. Figure 9 shows FIFO

Polled mode operation.

R/W

IRQ

R/W

IIR

IER

1111

THR RHR

002aab096

IIR

PROCESSOR

IER

0000

THR RHR

002aab097

Fig 9. FIFO Polled mode operation

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 15 of 49

Page 16

Philips Semiconductors

6.6 DMA operation

There are two modes of DMA operation, DMA mode 0 or DMA mode 1, selected by

FCR[3].

In DMA mode 0 or FIFO disable (FCR[0] = 0) DMA occurs in single character transfers. In

DMA mode 1, multi-character (or block) DMA transfers are managed to relieve the

processor for longer periods of time.

6.6.1 Single DMA transfers (DMA mode 0/FIFO disable)

Figure 10 shows TXRDY and RXRDY in DMA mode 0/FIFO disable.

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

wrptr

wrptr

Fig 10. TXRDY and RXRDY in DMA mode 0/FIFO disable

6.6.1.1 Transmitter

When empty, the TXRDY signal becomes active.TXRDY will go inactive after one

character has been loaded into it.

6.6.1.2 Receiver

RXRDY is active when there is at least one character in the FIFO. It becomes inactive

when the receiver is empty.

TX

FIFO EMPTY

TXRDY

at least one

location filled

TXRDY

rdptr

rdptr

RX

RXRDY

at least one

location filled

RXRDY

FIFO EMPTY

002aaa232

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 16 of 49

Page 17

Philips Semiconductors

6.6.2 Block DMA transfers (DMA mode 1)

Figure 11 shows TXRDY and RXRDY in DMA mode 1.

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

wrptr

trigger

level

wrptr

Fig 11. TXRDY and RXRDY in DMA mode 1

6.6.2.1 Transmitter

TXRDY is active when there is a trigger level number of spaces available. It becomes

inactive when the FIFO is full.

6.6.2.2 Receiver

RXRDY becomes active when the trigger level has been reached, or when a time-out

interrupt occurs. It will go inactive when the FIFO is empty or an error in the RX FIFO is

flagged by LSR[7].

TX

TXRDY

FIFO full

TXRDY

trigger

level

rdptr

rdptr

RX

RXRDY

at least one

location filled

RXRDY

FIFO EMPTY

002aaa234

6.7 Sleep mode

Sleep mode is an enhanced feature of the SC68C752B UART. It is enabled when EFR[4],

the enhanced functions bit, is set and when IER[4] is set. Sleep mode is entered when:

• The serial data input line, RX, is idle (see Section 6.8 “Break and time-out

conditions”).

• The TX FIFO and TX shift register are empty.

• There are no interrupts pending except THR and time-out interrupts.

Remark: Sleep mode will not be entered if there is data in the RX FIFO.

In Sleep mode, the UARTclock and baud rate clock are stopped. Since most registers are

clocked using these clocks, the power consumption is greatly reduced. The UART will

wake up when any change is detected on the RX line, when there is any change in the

state of the modem input pins, or if data is written to the TX FIFO.

Remark: Writing to the divisor latches, DLL and DLH, to set the baud clock, must not be

done during Sleep mode. Therefore, it is advisable to disable Sleep mode using IER[4]

before writing to DLL or DLH.

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 17 of 49

Page 18

Philips Semiconductors

6.8 Break and time-out conditions

An RX idle condition is detected when the receiver line, RX, has been HIGH for

4 character time. The receiver line is sampled midway through each bit.

When a break condition occurs, the TX line is pulled LOW. A break condition is activated

by setting LCR[6].

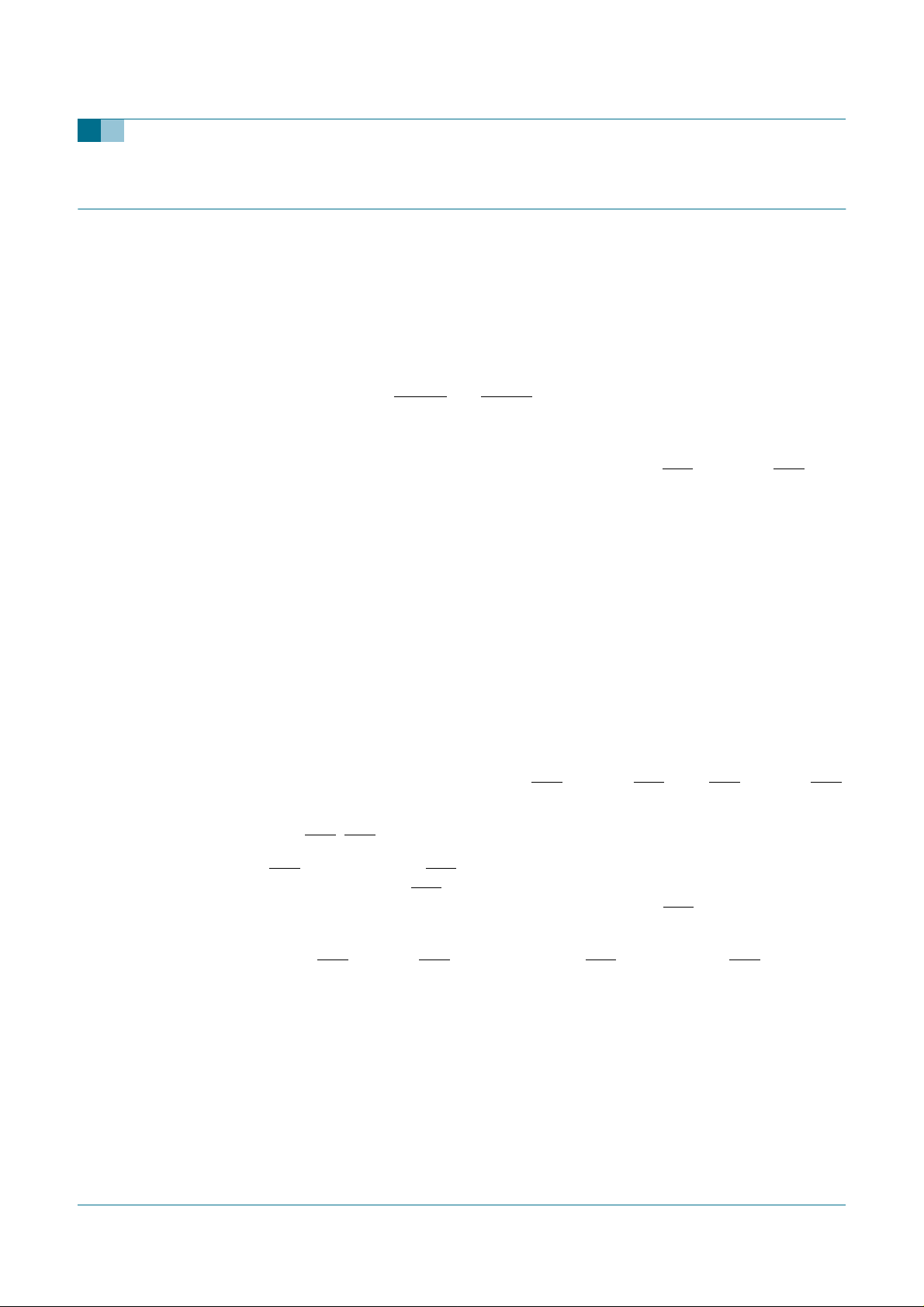

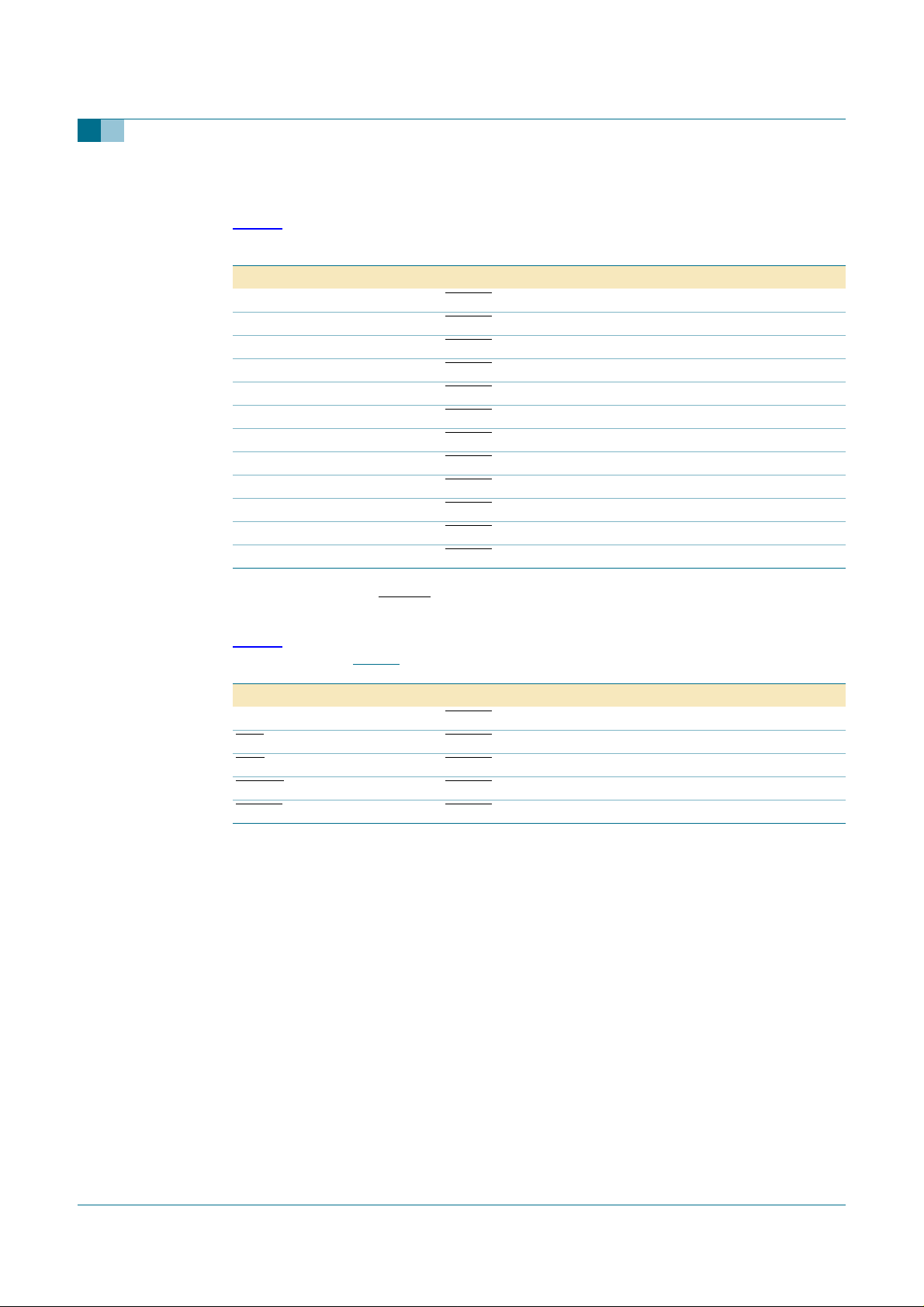

6.9 Programmable baud rate generator

The SC68C752B UART contains a programmable baud generator that takes any clock

input and divides it by a divisor in the range between 1 and (216− 1). An additional

divide-by-4 prescaler is also available and can be selected by MCR[7], as shown in

Figure 12. The output frequency of the baud rate generator is 16 × the baud rate. The

formula for the divisor is:

divisor

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

XTAL1 crystal input frequency

---------------------------------------------------------------------------

=

---------------------------------------------------------------------------------

prescaler

desired baud rate 16×()

SC68C752B

Where:

prescaler = 1, when MCR[7] is set to 0 after reset (divide-by-1 clock selected)

prescaler = 4, when MCR[7] is set to 1 after reset (divide-by-4 clock selected).

Remark: The default value of prescaler after reset is divide-by-1.

Figure 12 shows the internal prescaler and baud rate generator circuitry.

PRESCALER

LOGIC

(DIVIDE-BY-1)

XTAL1

XTAL2

INTERNAL

OSCILLATOR

LOGIC

input clock

PRESCALER

LOGIC

(DIVIDE-BY-4)

Fig 12. Prescaler and baud rate generator block diagram

MCR[7] = 0

reference

clock

MCR[7] = 1

BAUD RATE

GENERATOR

LOGIC

internal

baud rate

clock for

transmitter

and receiver

002aaa233

DLL and DLH must be written to in order to program the baud rate. DLL and DLH are the

least significant and most significant byte of the baud rate divisor.If DLL and DLH are both

zero, the UART is effectively disabled, as no baud clock will be generated.

Remark: The programmable baud rate generator is provided to select both the transmit

and receive clock rates.

Table 8 and Table 9 show the baud rate and divisor correlation for crystal with frequency

1.8432 MHz and 3.072 MHz, respectively.

Figure 13 shows the crystal clock circuit reference.

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 18 of 49

Page 19

Philips Semiconductors

Table 8: Baud rates using a 1.8432 MHz crystal

Desired baud rate Divisor used to generate

50 2304

75 1536

110 1047 0.026

134.5 857 0.058

150 768

300 384

600 192

1200 96

1800 64

2000 58 0.69

2400 48

3600 32

4800 24

7200 16

9600 12

19200 6

38400 3

56000 2 2.86

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

Percent error difference

16× clock

between desired and actual

Table 9: Baud rates using a 3.072 MHz crystal

Desired baud rate Divisor used to generate

16× clock

50 2304

75 2560

110 1745 0.026

134.5 1428 0.034

150 1280

300 640

600 320

1200 160

1800 107 0.312

2000 96

2400 80

3600 53 0.628

4800 40

7200 27 1.23

9600 20

19200 10

38400 5

Percent error difference

between desired and actual

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 19 of 49

Page 20

Philips Semiconductors

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

Fig 13. Crystal oscillator connections

7. Register descriptions

Each register is selected using address lines A0, A1, A2, and in some cases, bits from

other registers. The programming combinations for register selection are shown in

Table 10.

Table 10: Register map - read/write properties

A2 A1 A0 Read mode Write mode

0 0 0 Receive Holding Register (RHR) Transmit Holding Register (THR)

0 0 1 Interrupt Enable Register (IER) Interrupt Enable Register

0 1 0 Interrupt Identification Register (IIR) FIFO Control Register (FCR)

0 1 1 Line Control Register (LCR) Line Control Register

1 0 0 Modem Control Register (MCR)

1 0 1 Line Status Register (LSR)

1 1 0 Modem Status Register (MSR)

1 1 1 ScratchPad Register (SPR) ScratchPad Register

0 0 0 Divisor Latch LSB (DLL)

0 0 1 Divisor Latch MSB (DLH)

0 1 0 Enhanced Feature Register (EFR)

1 0 0 Xon1 word

1 0 1 Xon2 word

1 1 0 Xoff1 word

1 1 1 Xoff2 word

1 1 0 Transmission Control Register (TCR)

1 1 1 Trigger Level Register (TLR)

1 1 1 FIFO ready register

XTAL1 XTAL2

X1

1.8432 MHz

C1

22 pF

[2] [4]

[2] [4]

[2] [4]

[2] [4]

[2] [6]

C2

33 pF

[2] [3]

[2] [3]

[2] [5]

XTAL1 XTAL2

1.8432 MHz

C1

22 pF

[1]

[2] [4]

[2] [5]

1.5 kΩ

X1

C2

47 pF

002aaa870

Modem Control Register

divisor latch LSB

[2] [3]

divisor latch MSB

Enhanced Feature Register

Xon1 word

Xon2 word

Xoff1 word

Xoff2 word

[2] [4]

[2] [4]

[2] [4]

[2] [4]

[1]

[2] [3]

[2] [4]

Transmission Control Register

Trigger Level Register

[2] [5]

[2] [5]

[1] MCR[7] can only be modified when EFR[4] is set.

[2] Accessed by a combination of address pins and register bits.

[3] Accessible only when LCR[7] is logic 1.

[4] Accessible only when LCR is set to 1011 1111 (BFh).

[5] Accessible only when EFR[4] = 1 and MCR[6] = 1, that is, EFR[4] and MCR[6] are read/write enables.

[6] Accessible only when CS = 0, MCR[2] = 1, and loopback is disabled (MCR[4] = 0).

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 20 of 49

Page 21

Philips Semiconductors

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

Table 11 lists and describes the SC68C752B internal registers.

Table 11: SC68C752B internal registers

A2 A1 A0 Register Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

General register set

[1]

0 0 0 RHR bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 R

0 0 0 THR bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 W

001IER

CTS

interrupt

enable

0 1 0 FCR RX

trigger

level

(MSB)

[2]

RTS

interrupt

enable

RX

trigger

level

(LSB)

0 1 0 IIR FCR[0] FCR[0]

0 1 1 LCR DLAB break

control

bit

1 0 0 MCR 1× or

1×/4

clock

1 0 1 LSR error in

RX FIFO

[2]

TCR and

TLR

enable

THR and

TSR

[2]

[2]

[2]

Xoff

Sleep

mode

TXtrigger

level

(MSB)

CTS,

TX trigger

level

[2]

(LSB)

Xoff interrupt

RTS

set parity parity

type

select

Xon

Any

THR

empty

enable

[2]

loopback

break

interrupt

[2]

[2]

modem

status

interrupt

DMA

mode

select

priority

bit 2

parity

enable

OPA/

OPB

control

framing

error

receive

linestatus

interrupt

TX FIFO

reset

interrupt

priority

bit 1

numberof

stop bits

FIFO

ready

enable

parity

error

THR

empty

interrupt

RX FIFO

reset

interrupt

priority

RX data

available

interrupt

FIFO

enable

interrupt

status

bit 0

word

length

bit 1

word

length

bit 0

RTS DTR R/W

overrun

error

data in

receiver

empty

1 1 0 MSR CD RI DSR CTS ∆CD ∆RI ∆DSR ∆CTS R

1 1 1 SPR bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 R/W

1 1 0 TCR bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 R/W

1 1 1 TLR bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 R/W

1 1 1 FIFO Rdy 0 0 RX FIFO

B status

Special register set

[3]

RX FIFO

A status

0 0 TX FIFO

B status

TX FIFO

A status

0 0 0 DLL bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 R/W

0 0 1 DLH bit 15 bit 14 bit 13 bit 12 bit 11 bit 10 bit 9 bit 8 R/W

Enhanced register set

0 1 0 EFR Auto

[4]

CTS

Auto

RTS

special

character

detect

enable

enhanced

functions

[2]

software

flow

control

bit 3

software

flow

control

bit 2

software

flow

control

bit 1

software

flow

control

bit 0

1 0 0 XON1 bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 R/W

1 0 1 XON2 bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 R/W

1 1 0 XOFF1 bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 R/W

1 1 1 XOFF2 bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 R/W

Read/

Write

R/W

W

R

R/W

R

R

R/W

[1] These registers are accessible only when LCR[7] = 0.

[2] This bit can only be modified if register bit EFR[4] is enabled, that is, if enhanced functions are enabled.

[3] The Special register set is accessible only when LCR[7] is set to a logic 1.

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 21 of 49

Page 22

Philips Semiconductors

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

[4] Enhanced Feature Register; XON1/XON2 and XOFF1/XOFF2 are accessible only when LCR is set to ‘BFh’.

Remark: Refer to the notes under Table 10 for more register access information.

SC68C752B

7.1 Receiver Holding Register (RHR)

The receiver section consists of the Receiver Holding Register (RHR) and the Receiver

Shift Register (RSR). The RHR is actually a 64-byte FIFO. The RSR receives serial data

from the RX terminal. The data is converted to parallel data and moved to the RHR. The

receiver section is controlled by the line control register. If the FIFO is disabled, location

zero of the FIFO is used to store the characters.

Remark: In this case, characters are overwritten if overflow occurs.

If overflow occurs, characters are lost. The RHR also stores the error status bits

associated with each character.

7.2 Transmit Holding Register (THR)

The transmitter section consists of the Transmit Holding Register (THR) and the Transmit

Shift Register (TSR). The THR is actually a 64-byte FIFO. The THR receives data and

shifts it into the TSR, where it is converted to serial data and moved out on the TX

terminal. If the FIFO is disabled, the FIFO is still used to store the byte. Characters are

lost if overflow occurs.

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 22 of 49

Page 23

Philips Semiconductors

7.3 FIFO Control Register (FCR)

This is a write-only register that is used for enabling the FIFOs, clearing the FIFOs, setting

transmitter and receiver trigger levels, and selecting the type of DMA signalling. Table 12

shows FIFO Control Register bit settings.

Table 12: FIFO Control Register bits description

Bit Symbol Description

7:6 FCR[7](MSB),

5:4 FCR[5](MSB),

3 FCR[3] DMA mode select.

2 FCR[2] Reset TX FIFO.

1 FCR[1] Reset RX FIFO.

0 FCR[0] FIFO enable.

FCR[6] (LSB)

FCR[4] (LSB)

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

RX trigger. Sets the trigger level for the RX FIFO.

00 - 8 characters

01 - 16 characters

10 - 56 characters

11 - 60 characters

TX trigger. Sets the trigger level for the TX FIFO.

00 - 8 spaces

01 - 16 spaces

10 - 32 spaces

11 - 56 spaces

FCR[5:4] can only be modified and enabled when EFR[4] is set. This is

because the transmit trigger level is regarded as an enhanced function.

logic 0 = Set DMA mode ‘0’

logic 1 = Set DMA mode ‘1’

logic 0 = No FIFO transmit reset (normal default condition)

logic 1 = Clears the contents of the transmit FIFO and resets the FIFO

counter logic (the transmit shift register is not cleared or altered). This

bit will return to a logic 0 after clearing the FIFO.

logic 0 = no FIFO receive reset (normal default condition)

logic 1 = Clears the contents of the receive FIFO and resets the FIFO

counter logic (the receive shift register is not cleared or altered). This

bit will return to a logic 0 after clearing the FIFO.

logic 0 = disable the transmit and receive FIFO (normal default

condition)

logic 1 = enable the transmit and receive FIFO

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 23 of 49

Page 24

Philips Semiconductors

7.4 Line Control Register (LCR)

This register controls the data communication format. The word length, number of stop

bits, and parity type are selected by writing the appropriate bits to the LCR. Table 13

shows the Line Control Register bit settings.

Table 13: Line Control Register bits description

Bit Symbol Description

7 LCR[7] Divisor latch enable.

6 LCR[6] Break control bit. When enabled, the Break control bit causes a break

5 LCR[5] Set parity. LCR[5] selects the forced parity format (if LCR[3] = 1).

4 LCR[4] Parity type select.

3 LCR[3] Parity enable.

2 LCR[2] Number of stop bits. Specifies the number of stop bits.

1:0 LCR[1:0] Word length bits 1, 0. These two bits specify the word length to be

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

logic 0 = divisor latch disabled (normal default condition)

logic 1 = divisor latch enabled

condition to be transmitted (the TX output is forced to a logic 0 state). This

condition exists until disabled by setting LCR[6] to a logic0.

logic 0 = no TX break condition (normal default condition)

logic 1 = forces the transmitter output (TX) to a logic 0 to alert the

communication terminal to a line break condition

logic 0 = parity is not forced (normal default condition)

LCR[5] = logic 1 and LCR[4] = logic 0: parity bit is forced to a logical 1 for

the transmit and receive data.

LCR[5] = logic 1 and LCR[4] = logic 1: parity bit is forced to a logical 0 for

the transmit and receive data.

logic 0 = odd parity is generated (if LCR[3] = 1).

logic 1 = even parity is generated (if LCR[3] = 1).

logic 0 = no parity (normal default condition).

logic 1 = a parity bit is generated during transmission and the receiver

checks for received parity.

0 = 1 stop bit (word length = 5, 6, 7, 8)

1 = 1.5 stop bits (word length = 5)

1 = 2 stop bits (word length = 6, 7, 8)

transmitted or received.

00 = 5 bits

01 = 6 bits

10 = 7 bits

11 = 8 bits

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 24 of 49

Page 25

Philips Semiconductors

7.5 Line Status Register (LSR)

Table 14 shows the Line Status Register bit settings.

Table 14: Line Status Register bits description

Bit Symbol Description

7 LSR[7] FIFO data error.

6 LSR[6] THR and TSR empty. This bit is the Transmit Empty indicator.

5 LSR[5] THR empty. This bit is the Transmit Holding Register Empty indicator.

4 LSR[4] Break interrupt.

3 LSR[3] Framing error.

2 LSR[2] Parity error.

1 LSR[1] Overrun error.

0 LSR[0] Data in receiver.

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

logic 0 = No error (normal default condition)

logic 1 = At least one parity error, framing error, or break indication is in the

receiver FIFO. This bit is cleared when no more errors are present in the

FIFO.

logic 0 = transmitter hold and shift registers are not empty

logic 1 = transmitter hold and shift registers are empty

logic 0 = Transmit Hold Register is not empty

logic 1 = TransmitHold Register is empty. The processor can now load up to

64 bytes of data into the THR if the TX FIFO is enabled.

logic 0 = no break condition (normal default condition)

logic 1 = A break condition occurred and associated byte is 00, that is,

RX was LOW for one character time frame.

logic 0 = no framing error in data being read from RX FIFO (normal default

condition)

logic 1 = Framing error occurred in data being read from RX FIFO, that is,

received data did not have a valid stop bit.

logic 0 = no parity error (normal default condition)

logic 1 = parity error in data being read from RX FIFO

logic 0 = no overrun error (normal default condition)

logic 1 = overrun error has occurred

logic 0 = no data in receive FIFO (normal default condition)

logic 1 = at least one character in the RX FIFO

When the LSR is read, LSR[4:2] reflect the error bits (BI, FE, PE) of the character at the

top of the RX FIFO (next character to be read). The LSR[4:2] registers do not physically

exist, as the data read from the RX FIFO is output directly onto the output data bus,

D[4:2], when the LSR is read. Therefore, errors in a character are identified by reading the

LSR and then reading the RHR.

LSR[7] is set when there is an error anywhere in the RX FIFO, and is cleared only when

there are no more errors remaining in the FIFO.

Reading the LSR does not cause an increment of the RX FIFO read pointer. The RX FIFO

read pointer is incremented by reading the RHR.

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 25 of 49

Page 26

Philips Semiconductors

Remark: The three error bits (parity, framing, break) may not be updated correctly in the

first read of the LSR when the input clock (XTAL1) is running faster than 36 MHz.

However, the second read is always correct. It is strongly recommended that when using

this device with a clock faster than 36 MHz, that the LSR be read twice and only the

second read be used for decision making. All other bits in the LSR are correct on all

reads.

7.6 Modem Control Register (MCR)

The MCR controls the interface with the mode, data set, or peripheral device that is

emulating the modem. Table 15 shows Modem Control Register bit settings.

Table 15: Modem Control Register bits description

Bit Symbol Description

7 MCR[7]

6 MCR[6]

5 MCR[5]

4 MCR[4] Enable loopback.

3 MCR[3] OPA/OPB control.

2 MCR[2] FIFO Ready enable.

1 MCR[1]

0 MCR[0]

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

[1]

Clock select.

logic 0 = divide-by-1 clock input

logic 1 = divide-by-4 clock input

[1]

TCR and TLR enable.

logic 0 = no action.

logic 1 = enable access to the TCR and TLR registers

[1]

Xon Any.

logic 0 = disable Xon Any function

logic 1 = enable Xon Any function

logic 0 = normal operating mode

logic 1 = Enable local Loopback mode (internal). In this mode the

MCR[3:0] signals are looped back into MSR[7:4] and the TX output is

looped back to the RX input internally.

logic 0 = forces

logic 1 = forces

controls MSR[7].

logic 0 = Disable the FIFO Rdy register

logic 1 = Enable the FIFO Rdy register. In Loopback mode, controls

MSR[6].

RTS

logic 0 = force

logic 1 = force

MSR[4]. If Autohardware flow control.

DTR

logic 0 = force

logic 1 = force

MSR[5].

OPA/OPB output to HIGH state

OPA/OPB output to LOW state. In Loopback mode,

RTS output to inactive (HIGH)

RTS output to active (LOW). In Loopback mode, controls

RTS is enabled, the RTS output is controlled by

DTR output to inactive (HIGH)

DTR output to active (LOW). In Loopback mode, controls

[1] MCR[7:5] can only be modified when EFR[4] is set, that is, EFR[4] is a write enable.

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 26 of 49

Page 27

Philips Semiconductors

7.7 Modem Status Register (MSR)

This 8-bit register provides information about the current state of the control lines from the

mode, data set, or peripheral device to the processor. It also indicates when a control

input from the modem changes state. Table 16 shows Modem Status Register bit settings

per channel.

Table 16: Modem Status Register bits description

Bit Symbol Description

7 MSR[7]

6 MSR[6]

5 MSR[5]

4 MSR[4]

3 MSR[3] ∆CD. Indicates that

2 MSR[2] ∆RI.Indicates that

1 MSR[1] ∆DSR. Indicates that

0 MSR[0] ∆CTS. Indicates that CTS input (or MCR[1] in Loopback mode) has changed

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

[1]

CD (active HIGH, logical 1). This bit is the complement of the CD input during

normal mode. During internal Loopback mode, it is equivalent to MCR[3].

[1]

RI (active HIGH, logical 1). This bit is the complement of the RI input during

normal mode. During internal Loopback mode, it is equivalent to MCR[2].

[1]

DSR (active HIGH, logical 1). This bit is the complement of the DSR input

during normal mode. During internal Loopback mode, it is equivalent MCR[0].

[1]

CTS (active HIGH, logical 1). This bit is the complement of the CTS input

during normal mode. During internal Loopback mode, it is equivalent to

MCR[1].

CD input (or MCR[3] in Loopback mode) has changed

state. Cleared on a read.

RI input (or MCR[2] in Loopback mode) has changed state

from LOW to HIGH. Cleared on a read.

DSR input (or MCR[0] in Loopback mode) has changed

state. Cleared on a read.

state. Cleared on a read.

[1] The primary inputs RI, CD, CTS, DSR are all active LOW, but their registered equivalents in the MSR and

MCR (in Loopback mode) registers are active HIGH.

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 27 of 49

Page 28

Philips Semiconductors

7.8 Interrupt Enable Register (IER)

The Interrupt Enable Register (IER) enables each of the six types of interrupt, receiver

error,RHR interrupt, THR interrupt, Xoff received, or CTS/RTS change of state from LOW

to HIGH. The IRQ output signal is activated in response to interrupt generation. Table 17

shows Interrupt Enable Register bit settings.

Table 17: Interrupt Enable Register bits description

Bit Symbol Description

7 IER[7]

6 IER[6]

5 IER[5]

4 IER[4]

3 IER[3] Modem Status Interrupt.

2 IER[2] Receive Line Status interrupt.

1 IER[1] Transmit Holding Register interrupt.

0 IER[0] Receive Holding Register interrupt.

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

[1]

CTS interrupt enable.

logic 0 = disable the

logic 1 = enable the

[1]

RTS interrupt enable.

logic 0 = disable the

logic 1 = enable the

[1]

Xoff interrupt.

logic 0 = disable the Xoff interrupt (normal default condition)

logic 1 = enable the Xoff interrupt

[1]

Sleep mode.

logic 0 = disable Sleep mode (normal default condition)

logic 1 = enable Sleep mode. See

logic 0 = disable the Modem Status Register interrupt (normal default

condition)

logic 1 = enable the Modem Status Register interrupt

logic 0 = disable the receiver line status interrupt (normal default condition)

logic 1 = enable the receiver line status interrupt

logic 0 = disable the THR interrupt (normal default condition)

logic 1 = enable the THR interrupt

logic 0 = disable the RHR interrupt (normal default condition)

logic 1 = enable the RHR interrupt

CTS interrupt (normal default condition)

CTS interrupt

RTS interrupt (normal default condition)

RTS interrupt

Section 6.7 “Sleep mode” for details.

[1] IER[7:4] can only be modified if EFR[4] is set, that is, EFR[4] is a write enable. Re-enabling IER[1] will not

cause a new interrupt if the THR is below the threshold.

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 28 of 49

Page 29

Philips Semiconductors

7.9 Interrupt Identification Register (IIR)

The IIR is a read-only 8-bit register which provides the source of the interrupt in a

prioritized manner. Table 18 shows Interrupt Identification Register bit settings.

Table 18: Interrupt Identification Register bits description

Bit Symbol Description

7:6 IIR[7:6] Mirror the contents of FCR[0].

5 IIR[5]

4 IIR[4] 1 = Xoff/Special character has been detected

3:1 IIR[3:1] 3-bit encoded interrupt. See

0 IIR[0] Interrupt status.

The interrupt priority list is shown in Table 19.

Table 19: Interrupt priority list

Priority

level

1 000110receiver line status error

2 001100receiver time-out interrupt

2 000100RHR interrupt

3 000010THR interrupt

4 000000modem interrupt

5 010000received Xoff signal/ special

6 100000

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

RTS/CTS LOW-to-HIGH change of state

Table 19.

logic 0 = an interrupt is pending

logic 1 = no interrupt is pending

IIR[5] IIR[4] IIR[3] IIR[2] IIR[1] IIR[0] Source of the interrupt

character

CTS, RTS change of state from

active (LOW) to inactive (HIGH)

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 29 of 49

Page 30

Philips Semiconductors

7.10 Enhanced Feature Register (EFR)

This 8-bit register enables or disables the enhanced features of the UART. Table 20 shows

the Enhanced Feature Register bit settings.

Table 20: Enhanced Feature Register bits description

Bit Symbol Description

7 EFR[7]

6 EFR[6]

5 EFR[5] Special character detect.

4 EFR[4] Enhanced functions enable bit.

3:0 EFR[3:0] Combinations of software flow control can be selected by programming these

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

CTS flow control enable.

logic 0 =

logic 1 =

signal is detected on the

RTS flow control enable.

logic 0 =

logic 1 =

receiver FIFO halt trigger levelTCR[3:0] is reached, and goes LOW when the

receiver FIFO resume transmission trigger level TCR[7:4] is reached.

logic 0 = special character detect disabled (normal default condition)

logic 1 = special character detect enabled. Received data is compared with

Xoff2 data. If a match occurs, the received data is transferred to FIFO and

IIR[4] is set to a logical 1 to indicate a special character has been detected.

logic 0 = disables enhanced functions and writing to IER[7:4], FCR[5:4],

MCR[7:5]

logic 1 = enables the enhanced function IER[7:4], FCR[5:4], and MCR[7:5]

can be modified, that is, this bit is therefore a write enable

bits. See

CTS flow control is disabled (normal default condition)

CTS flow control is enabled. Transmission will stop when a HIGH

CTS pin.

RTS flow control is disabled (normal default condition)

RTS flow control is enabled. The RTS pin goes HIGH when the

Table 4 “Software flow control options (EFR[0:3])” on page 10.

7.11 Divisor latches (DLL, DLH)

These are two 8-bit registers which store the 16-bit divisor for generation of the baud clock

in the baud rate generator. DLH stores the most significant part of the divisor. DLL stores

the least significant part of the divisor.

Note that DLL and DLH can only be written to before Sleep mode is enabled, that is,

before IER[4] is set.

7.12 Transmission Control Register (TCR)

This 8-bit register is used to store the RX FIFO threshold levels to stop/start transmission

during hardware/software flow control. Table 21 shows transmission control register bit

settings.

Table 21: Transmission Control Register bits description

Bit Symbol Description

7:4 TCR[7:4] RX FIFO trigger level to resume transmission (0 bytes to 60 bytes).

3:0 TCR[3:0] RX FIFO trigger level to halt transmission (0 bytes to 60 bytes).

TCR trigger levels are available from 0 bytes to 60 bytes with a granularity of four.

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 30 of 49

Page 31

Philips Semiconductors

Remark: TCR can only be written to when EFR[4] = 1 and MCR[6] = 1. The programmer

must program the TCR such that TCR[3:0] > TCR[7:4]. There is no built-in hardware

check to make sure this condition is met. Also, the TCR must be programmed with this

condition before Auto-RTS or software flow control is enabled to avoid spurious operation

of the device.

7.13 Trigger Level Register (TLR)

This 8-bit register is pulsed to store the transmit and received FIFO trigger levels used for

DMA and interrupt generation. Trigger levels from 4 to 60 can be programmed with a

granularity of 4. Table 22 shows trigger level register bit settings.

Table 22: Trigger Level Register bits description

Bit Symbol Description

7:4 TLR[7:4] RX FIFO trigger levels (4 to 60), number of characters available.

3:0 TLR[3:0] TX FIFO trigger levels (4 to 60), number of spaces available.

Remark: TLR can only be written to when EFR[4] = 1 and MCR[6] = 1. If TLR[3:0] or

TLR[7:4] are logical 0, the selectable trigger levels via the FIFO control register (FCR) are

used for the transmit and receive FIFO trigger levels. Trigger levels from

4 bytes to 60 bytes are available with a granularity of four. The TLR should be

programmed forN⁄4, where N is the desired trigger level.

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

When the trigger levelsetting in TLR is zero,the SC68C752B uses the trigger level setting

defined in FCR. If TLR has non-zero trigger level value, the trigger leveldefined in FCR is

discarded. This applies to both transmit FIFO and receive FIFO trigger level setting.

When TLR is used for RX trigger level control, FCR[7:6] should be left at the default state,

that is, ‘00’.

7.14 FIFO ready register

The FIFO ready register provides real-time status of the transmit and receive FIFOs of

both channels.

Table 23: FIFO ready register bits description

Bit Symbol Description

7:6 FIFO Rdy[7:6] unused; always 0

5 FIFO Rdy[5] RX FIFO B status; related to DMA

4 FIFO Rdy[4] RX FIFO A status; related to DMA

3:2 FIFO Rdy[3:2] unused; always 0

1 FIFO Rdy[1] TX FIFO B status; related to DMA

0 FIFO Rdy[0] TX FIFO A status; related to DMA

The FIFO Rdy register is a read-only register that can be accessed when any of the two

UARTs is selected CS = 0, MCR[2] (FIFO Rdy Enable) is a logic 1, and loopback is

disabled. The address is 111.

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 31 of 49

Page 32

Philips Semiconductors

8. Programmer’s guide

The base set of registers that is used during high-speed data transfer have a

straightforward access method. The extended function registers require special access

bits to be decoded along with the address lines. The following guide will help with

programming these registers. Note that the descriptions below are for individual register

access. Some streamlining through interleaving can be obtained when programming all

the registers.

Table 24: Register programming guide

Command Actions

Set baud rate to VALUE1, VALUE2 read LCR (03h), save in temp

Set Xoff1, Xon1 to VALUE1, VALUE2 read LCR (03h), save in temp

Set Xoff2, Xon2 to VALUE1, VALUE2 read LCR (03h), save in temp

Set software flow control mode to VALUE read LCR (03h), save in temp

Set flow control threshold to VALUE read LCR (03h), save in temp1

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

set LCR (03h) to 80h

set DLL (00h) to VALUE1

set DLM (01h) to VALUE2

set LCR (03h) to temp

set LCR (03h) to BFh

set Xoff1 (06h) to VALUE1

set Xon1 (04h) to VALUE2

set LCR (03h) to temp

set LCR (03h) to BFh

set Xoff2 (07h) to VALUE1

set Xon2 (05h) to VALUE2

set LCR (03h) to temp

set LCR (03h) to BFh

set EFR (02h) to VALUE

set LCR (03h) to temp

set LCR (03h) to BFh

read EFR (02h), save in temp2

set EFR (02h) to 10h + temp2

set LCR (03h) to 00h

read MCR (04h), save in temp3

set MCR (04h) to 40h + temp3

set TCR (06h) to VALUE

set MCR (04h) to temp3

set LCR (03h) to BFh

set EFR (02h) to temp2

set LCR (03h) to temp1

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 32 of 49

Page 33

Philips Semiconductors

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

Table 24: Register programming guide

Command Actions

Set TX FIFO and RX FIFO thresholds

to VALUE

Read FIFO Rdy register read MCR (04h), save in temp1

Set prescaler value to divide-by-1 read LCR (03h), save in temp1

Set prescaler value to divide-by-4 read LCR (03h), save in temp1

…continued

read LCR (03h), save in temp1

set LCR (03h) to BFh

read EFR (02h), save in temp2

set EFR (02h) to 10h + temp2

set LCR (03h) to 00h

read MCR (04h), save in temp3

set MCR (04h) to 40h + temp3

set TLR (07h) to VALUE

set MCR (04h) to temp3

set LCR (03h) to BFh

set EFR (02h) to temp2

set LCR (03h) to temp1

set temp2 = temp1 × EFh

set MCR (04h) = 40h + temp2

read FFR (07h), save in temp2

pass temp2 back to host

set MCR (04h) to temp1

set LCR (03h) to BF

read EFR (02h), save in temp2

set EFR (02h) to 10h + temp2

set LCR (03h) to 00h

read MCR (04h), save in temp3

set MCR (04h) to temp3 × 7Fh

set LCR (03h) to BFh

set EFR (02h) to temp2

set LCR (03h) to temp1

set LCR (03h) to BFh

read EFR (02h), save in temp2

set EFR (02h) to 10h + temp2

set LCR (03h) to 00h

read MCR (04h), save in temp3

set MCR (04h) to temp3 + 80h

set LCR (03h) to BFh

set EFR (02h) to temp2

set LCR (03h) to temp1

[1]

[1]

[1] × sign here means bit-AND.

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 33 of 49

Page 34

Philips Semiconductors

9. Limiting values

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

Table 25: Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

[1]

Symbol Parameter Conditions Min Max Unit

V

CC

V

I

V

O

T

amb

T

stg

[1] Stresses beyond those listed under Table 25 “Limiting values” maycausepermanent damage to the device.

supply voltage - 7 V

input voltage −0.3 VCC+ 0.3 V

output voltage −0.3 VCC+ 0.3 V

ambient temperature operating in free-air −40 +85 °C

storage temperature −65 +150 °C

These are stress ratings only, and functional operation of the device at these or any other conditions

beyond those indicated under recommended operating conditions is not implied. Exposure to

absolute-maximum-rated conditions for extended periods may affect device reliability.

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 34 of 49

Page 35

Philips Semiconductors

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

10. Static characteristics

Table 26: Static characteristics

Tolerance of VCC=±10 %

Symbol Parameter Conditions VCC= 2.5 V VCC= 3.3 V and 5 V Unit

Min Typ Max Min Typ Max

V

CC

V

I

V

IH

supply voltage VCC− 10 % V

CCVCC

input voltage 0 - V

HIGH-levelinput

[1]

1.6 - V

voltage

V

IL

LOW-level input

[1]

- - 0.65 - - 0.8 V

voltage

V

O

V

OH

V

OL

C

i

output voltage

HIGH-level

output voltage

LOW-level

output voltage

input

IOH= −8mA

I

OH

I

OH

I

OH

IOL=8mA

[5]

I

OL

I

OL

I

OL

= −4mA

= −800 µA

= −400 µA

=4mA

=2mA

= 1.6 mA

[2]

0-VCC0-VCCV

[3]

- - - 2.0 - - V

[4]

- - - 2.0 - - V

[3]

1.85 - - - - - V

[4]

1.85 - - - - - V

[3]

- - - - - 0.4 V

[4]

- - - - - 0.4 V

[3]

--0.4---V

[4]

--0.4---V

- - 18 - - 18 pF

capacitance

T

amb

ambient

operating −40 +25 +85 −40 +25 +85 °C

temperature

T

j

junction

[6]

0 +25 +125 0 +25 +125 °C

temperature

f

XTAL1

frequencyonpin

[7]

- - 50 - - 80 MHz

XTAL1

δ clock duty cycle - 50 - - 50 - %

I

CC

I

CC(sleep)

supply current f = 5 MHz

sleep current - - 200 - - 200 µA

[8]

- - 3.5 - - 4.5 mA

+10% VCC− 10 % V

CC

CC

0-VCCV

2.0 - V

CCVCC

CC

+10% V

V

[1] Meets TTL levels, V

[2] Applies for external output buffers.

[3] These parameters apply for D[7:0].

[4] These parameters apply for DTRA, DTRB, RTSA, RTSB, RXRDYA, RXRDYB, TXRDYA, TXRDYB, TXA, TXB.

[5] Except XTAL2, VOL= 1 V typical.

[6] These junction temperatures reflect simulated conditions. Absolute maximum junction temperature is 150 °C. The customer is

responsible for verifying junction temperature.

[7] Applies to external clock; crystal oscillator max. 24 MHz.

[8] Measurement condition, normal operation other than Sleep mode:

VCC= 3.3 V; T

recommended operating conditions with divisor of 1.

SC68C752B_3 © Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet Rev. 03 — 29 November 2005 35 of 49

amb

= 2 V and V

IL(min)

=25°C. Full duplex serial activity on all two serial (UART) channels at the clock frequency specified in the

= 0.8 V on non-hysteresis inputs.

IH(max)

Page 36

Philips Semiconductors

SC68C752B

5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.), with 64-byte FIFOs

11. Dynamic characteristics

Table 27: Dynamic characteristics

T

=−40°C to +85°C; tolerance of VCC=±10 %, unless specified otherwise.

amb

Symbol Parameter Conditions VCC= 2.5 V VCC= 3.3 V and 5 V Unit

Min Max Min Max

t

d1

t

d2

t

d3

t

d4

t

d6

t

d7

t

d8

t

d9

t

d10

t

d11

t

d12

t

d13

t

d14

t

d15

t

d16

t

d17

t

d18

t

h2

t

h3

t

h4

, t

t

w1

f

XTAL1

t

(RESET)

t

su1

t

su2

t

w1

R/W to chip select 10 - 10 - ns

read cycle delay 25 pF load 20 - 20 - ns

delay from CS to data 25 pF load - 77 - 26 ns

data disable time 25 pF load - 15 - 15 ns

write cycle delay 25 - 25 - ns

delay from WRITE to output 25 pF load - 100 - 33 ns

delay to set interrupt from modem

25 pF load - 100 - 24 ns

input

delay to reset interrupt from READ 25 pF load - 100 - 24 ns

delay from stop to set interrupt - 1T

RCLK

[1]

-1T

delay from READ to reset interrupt 25 pF load - 100 - 29 ns

delay from start to set interrupt - 100 - 100 ns

delay from WRITE to transmit start 8T

RCLK

[1]

24T

RCLK

[1]

8T

RCLK

[1]

24T

delay from WRITE to reset interrupt - 100 - 70 ns

delay from stop to set RXRDY-1T

RCLK

[1]

-1T

delay from READ to reset RXRDY - 100 - 75 ns

delay from WRITE to set TXRDY - 100 - 70 ns

delay from start to reset TXRDY - 16T

RCLK