Philips SAA7130HL Datasheet

INTEGRATED CIRCUITS

DATA SH EET

SAA7130HL

PCI video broadcast decoder

Product specification 2002 Apr 23

Philips Semiconductors Product specification

PCI video broadcast decoder SAA7130HL

CONTENTS

1 FEATURES

1.1 PCI and DMA bus mastering

1.2 TV video decoder and video scaling

1.3 Peripheral interface

1.4 General

2 GENERAL DESCRIPTION

2.1 Introduction

2.2 Overview of TV decoders with PCI bridge

2.3 Related documents

3 QUICK REFERENCE DATA

4 ORDERING INFORMATION

5 BLOCK DIAGRAM

6 PINNING

6.1 Pins sorted by number

6.2 Pins grouped by function

6.3 Pin description

7 FUNCTIONAL DESCRIPTION

7.1 Overview of internal functions

7.2 Application examples

7.3 Software support

7.4 PCI interface

7.5 Analog TV standards

7.6 Video processing

7.7 Analog audio pass-through and loop back

cable

7.8 DTV/DVB channel decoding and TS capture

7.9 Control of peripheral devices

8 BOUNDARY SCAN TEST

8.1 Initialization of boundary scan circuit

8.2 Device identification codes

9 LIMITING VALUES

10 THERMAL CHARACTERISTICS

11 CHARACTERISTICS

12 PACKAGE OUTLINE

13 SOLDERING

13.1 Introduction to soldering surface mount

packages

13.2 Reflow soldering

13.3 Wave soldering

13.4 Manual soldering

13.5 Suitability of surface mount IC packages for

wave and reflow soldering methods

14 DATA SHEET STATUS

15 DEFINITIONS

16 DISCLAIMERS

17 PURCHASE OF PHILIPS I2C COMPONENTS

2002 Apr 23 2

Philips Semiconductors Product specification

PCI video broadcast decoder SAA7130HL

1 FEATURES

1.1 PCI and DMA bus mastering

• PCI 2.2 compliantincluding full Advanced Configuration

and Power Interface (ACPI)

• System vendor ID, etc. via EEPROM

• Hardware support for virtual addressing by MMU

• DMA bus master write for video, VBI and TS

• Configurable PCI FIFOs, graceful overflow

• Packed and planar video formats, overlay clipping.

1.2 TV video decoder and video scaling

• All-standards TV decoder: NTSC, PAL and SECAM

• Five analog video inputs: CVBS and S-video

• Video digitizing by two 9-bit ADCs at 27 MHz

• Sampling according ITU-R BT.601 with 720 pixels/line

• Adaptive comb filter for NTSC and PAL, also operating

for non-standard signals

• Automatic TV standard detection

• Three level Macrovision copy protection detection

according to Macrovision Detect specification

Revision 1

• Control of brightness, contrast, saturation and hue

• Versatile filter bandwidth selection

• Horizontal and vertical downscaling or zoom

• Adaptive anti-alias filtering

• Capture of raw VBI samples

• Two alternating settings for active video scaling

• Output in YUV and RGB

• Gamma compensation, black stretching.

1.5 General

• Package: LQFP128

• Power supply: 3.3 V only

• Power consumption of typical application: 1 W

• Power-down state (D3-hot): <20 mW

• All interface signals 5 V tolerant

• Reference designs available

• SDK for Windows (95, 98, NT, 2000and XP), Video for

Windows (VfW) and Windows Driver Model (WDM).

2 GENERAL DESCRIPTION

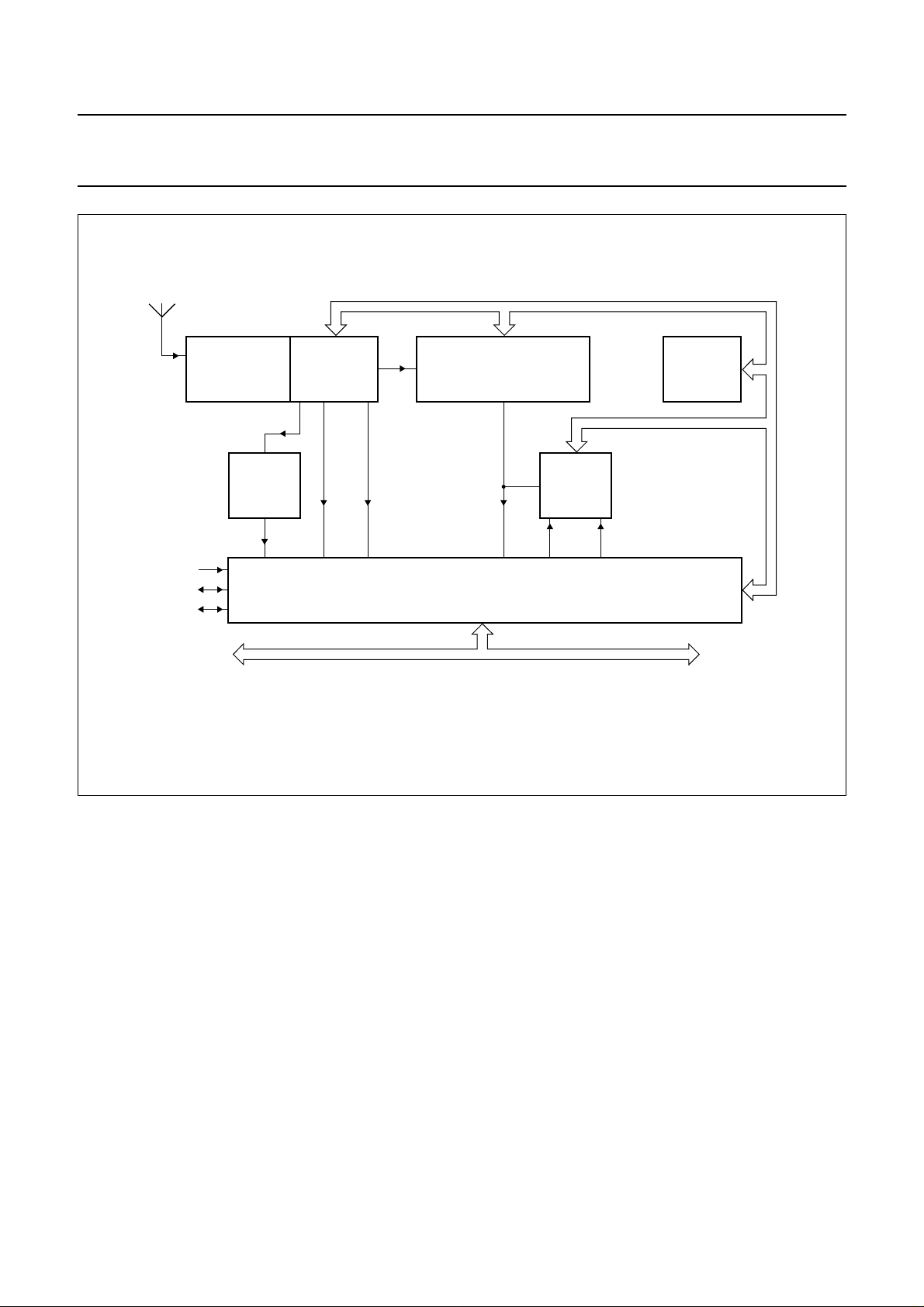

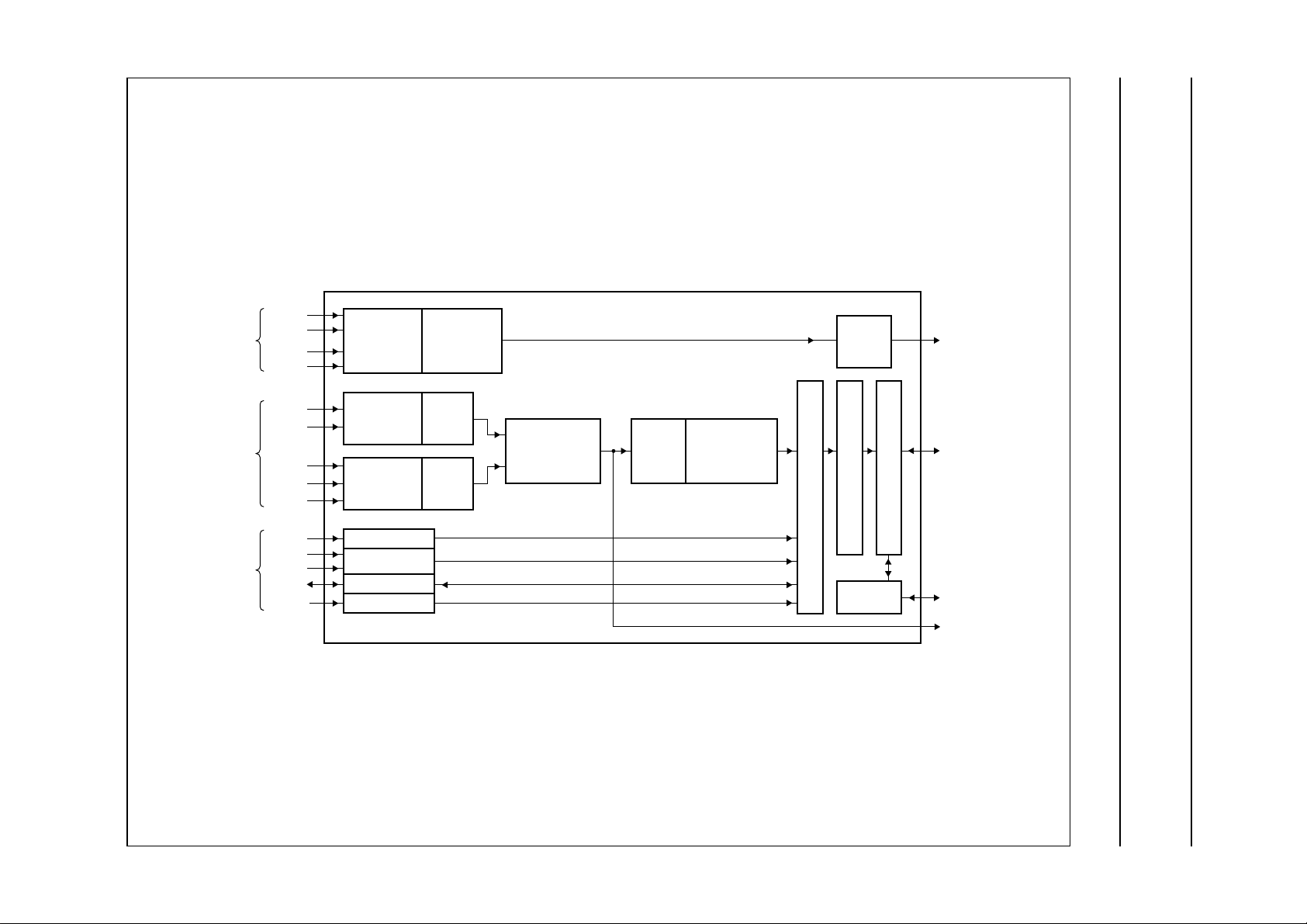

The SAA7130HL is a single chip solution to digitize and

decode video, and capture it through the PCI-bus.

Special means are incorporated to maintain the

synchronization of audio to video. The device offers

versatileperipheral interfaces(GPIO),that supportvarious

extended applications, e.g. analog audio pass-through for

loop back cable to the sound card, or capture of DTV and

DVB transport streams, such as Vestigial Side Band

(VSB), Orthogonal Frequency Division Multiplexing

(OFDM) and Quadrature Amplitude Modulation (QAM)

decoded digital television standards (see Fig.1).

1.3 TV audio I/O

• Integrated analog audio pass-through for analog audio

loop back cable to sound card.

1.4 Peripheral interface

• I2C-bus master interface: 3.3 and 5 V

• Digital video output: ITU and VIP formats

• TS input: serial or parallel

• General purpose I/O, e.g. for strapping and interrupt

• Propagate reset and ACPI state D3-hot.

2002 Apr 23 3

Philips Semiconductors Product specification

PCI video broadcast decoder SAA7130HL

handbook, full pagewidth

CVBS

S-video

audio I/O

line-in

line-out

TV TUNER:

• CABLE

• TERRESTRIAL

• SATELLITE

AUDIO

DECODER:

• BTSC

audio

L/R

IF-PLL:

• DVB

• ATV

SIF

AF

(mono)

DTV

DVB

CVBS

DECODER FOR TV VIDEO

WITH TS INTERFACE AND

DMA MASTER INTO PCI-BUS

DIGITAL CHANNEL DECODER:

• VSB

• QAM

• OFDM

TS

ENCODER:

• MPEG2

2

I

S-bus ITU656

PCI-bus

I2C-bus

SAA7130HL

2

I

C-BUS

EEPROM

MHC169

Fig.1 Application diagramfor capturing live TVvideo in the PC,with optional extensionsfor enhanced DTVand

DVB capture.

2.1 Introduction

The PCI video broadcastdecoder SAA7130HL is a highly

integrated, low cost and solid foundation forTV capture in

the PC, for analog TV and digital video broadcast. The

various multimedia data types are transported over the

PCI-bus by bus-master-write, to optimum exploit the

streaming capabilities of a modern host based system.

Legacy requirements are also taken care of.

The SAA7130HL meets the requirements of PC Design

Guides 98/99 and 2001 and is PCI 2.2 and Advanced

Configuration and Power Interface (ACPI) compliant.

The analogvideo is sampledby 9-bit ADCs,decoded by a

multi-line adaptive comb filter and scaled horizontally,

vertically and by field rate. Multiple video output formats

(YUV and RGB) are available, including packed and

planar, gamma-compensated or black-stretched.

2002 Apr 23 4

Audio is routed as an analog signal viathe loopback cable

to the sound card.

The SAA7130HL provides a versatile peripheral interface

to support system extensions, e.g. MPEG encoding for

time shift viewing, or DSP applications for audio

enhancements.

The channel decoderfor digital video broadcastreception

(ATSC or DVB) can re-use the integrated video ADCs.

The Transport Stream (TS) is collected by a tailored

interface and pumped through the PCI-bus to the system

memory in well-defined buffer structures. Various internal

events,or peripheralstatusinformation, canbeenabled as

an interrupt on the PCI-bus.

Philips Semiconductors Product specification

PCI video broadcast decoder SAA7130HL

2.2 Overview of TV decoders with PCI bridge

A TV decoder family with PCI interfacing has been created tosupport worldwide TV broadcasting. The pin compatibility

of these TV decoders offers the opportunity to support different TV broadcast standards with one PCB layout.

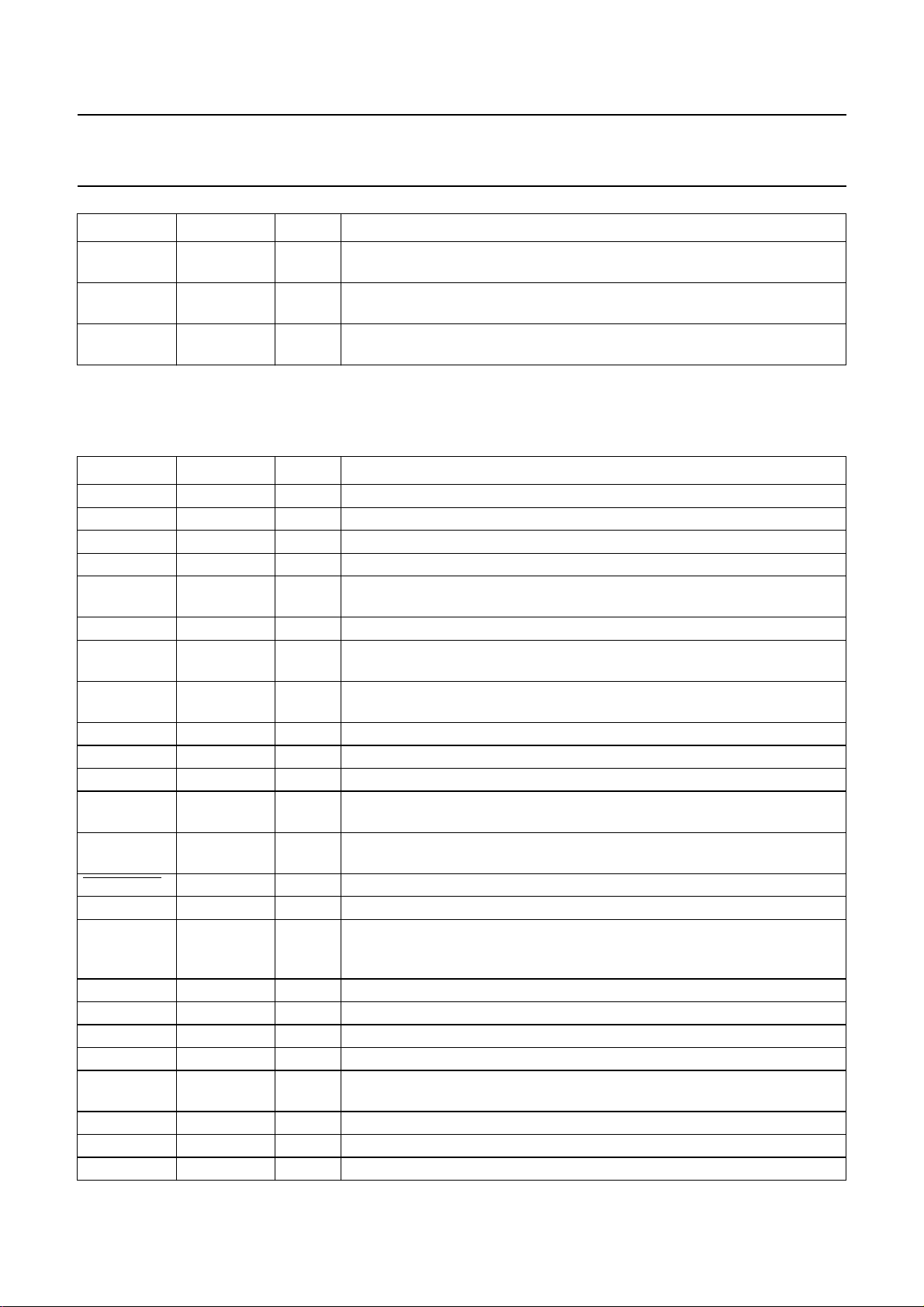

Table 1 TV decoder family with PCI interfacing

TV PARAMETER

TV DECODER TYPE

SAA7130HL SAA7133HL SAA7134HL SAA7135HL

PCI bridge version 2.2 2.2 2.2 2.2

DMA channel 7 7 7 7

TV video decoding PAL, NTSC and SECAM XXXX

Video scaling 2 dimension and 2 task scaler XXXX

Raw VBI 27 MHz sampling rate XXXX

TV sound decoding FM A2 and NICAM X X

BTSC (dBx) plus SAP; EIAJ X X

stereo sampling

2

(I

S-bus and DMA)

32 kHz 32 kHz,

Radio FM radio stereo X X

Audio left and right pass-through XXXX

stereo sampling

2

(I

S-bus and DMA)

32 kHz,

44.1 kHz,

48 kHz

video frame locked audio X X X

incredible surround X X X

Dolby® Prologic (note 2) X

virtual Dolby® surround X

volume, bass and treble

X volume only X

control

Transport stream serial and parallel TS XXXX

GPIO static I/O pins 27 27 27 27

interrupt input pins 4 4 4 4

2

I

C-bus multi-master or slave XXXX

video out XXXX

(1)

48 kHz

32 kHz,

44.1 kHz,

48 kHz

32 kHz,

48 kHz

32 kHz,

44.1 kHz,

48 kHz

Notes

1. X = function available.

2. Dolby is a registered trademark of Dolby Laboratories Licensing Corporation.

2002 Apr 23 5

Philips Semiconductors Product specification

PCI video broadcast decoder SAA7130HL

2.3 Related documents

This document describes the functionality and

characteristics of the SAA7130HL.

Other documents related to the SAA7130HL are:

• User manual SAA7130HL/34HL, describing the

programmability

• Application note SAA7130HL/34HL, pointing out

• Data sheets of other devices referred to in this

document, e.g:

– TDA8961: DTV channel decoder

– TD1316: ATV+DVB-T tuner

– TDA10045: DVB channel decoder

– TDA9886: Analog IF-PLL

– TDA9889: Digital IF-PLL.

recommendations for system implementation

• Demonstration and reference boards, including

description, schematics, etc.:

– Proteus-Pro: TV capture PCI card for analog TV

(standards: B/G, I, D/K and L/L’)

– Europa: hybrid DVB-T and analog TV capture PCI

card for European broadcasting.

3 QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

DD

P

tot

P

standby

T

amb

supply voltage 3.0 3.3 3.6 V

total power dissipation − 1.0 − W

standby power dissipation D3-hot of ACPI −−0.02 W

ambient temperature 0 25 70 °C

4 ORDERING INFORMATION

TYPE

NUMBER

NAME DESCRIPTION VERSION

PACKAGE

SAA7130HL LQFP128 plastic low profile quad flat package; 128 leads; body 14 × 20 × 1.4 mm SOT425-1

2002 Apr 23 6

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to forcelandscape pages to berotated correctly when browsing throughthe pdf in theAcrobat reader. white to forcelandscape pages to be...

2002 Apr 23 7

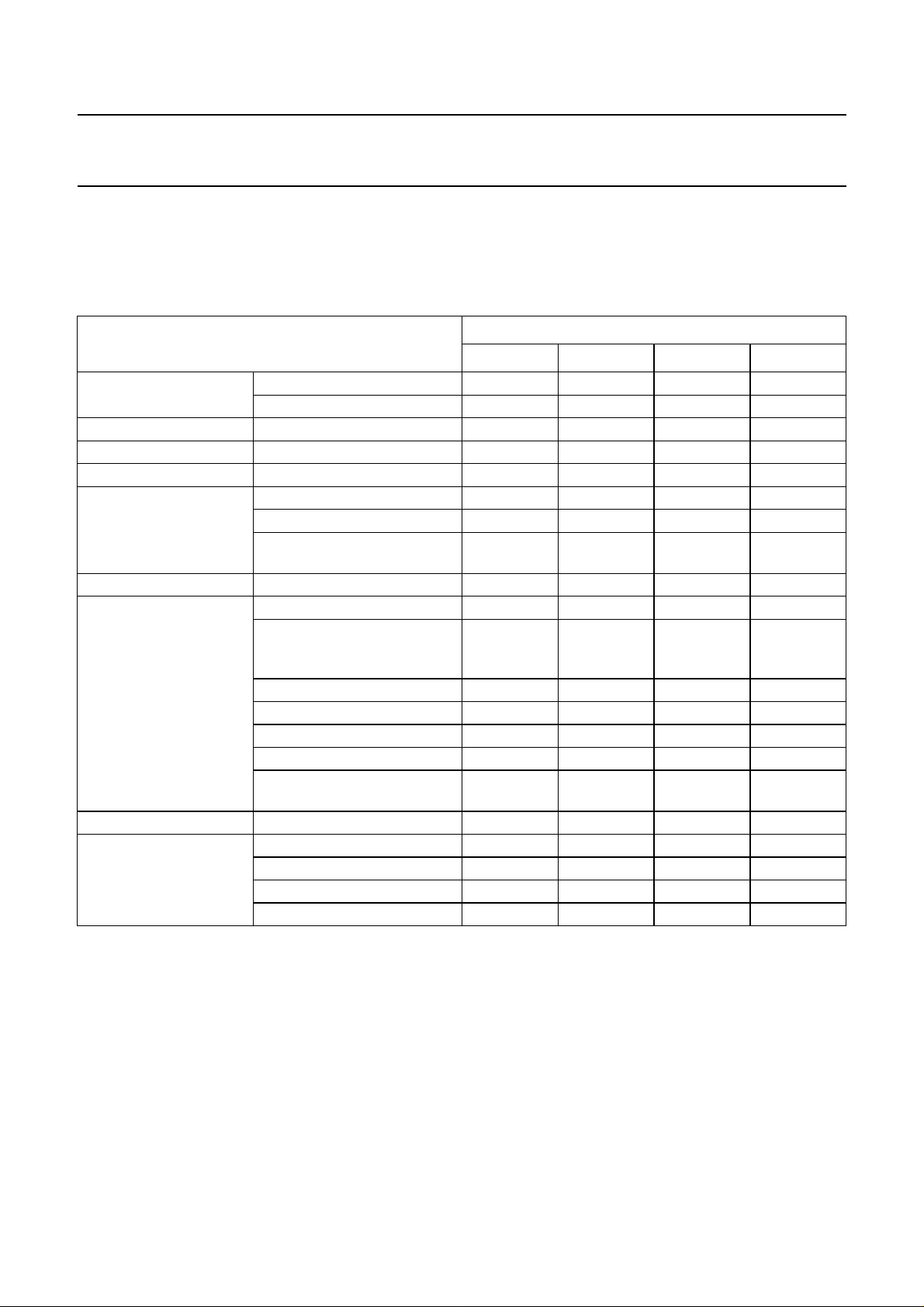

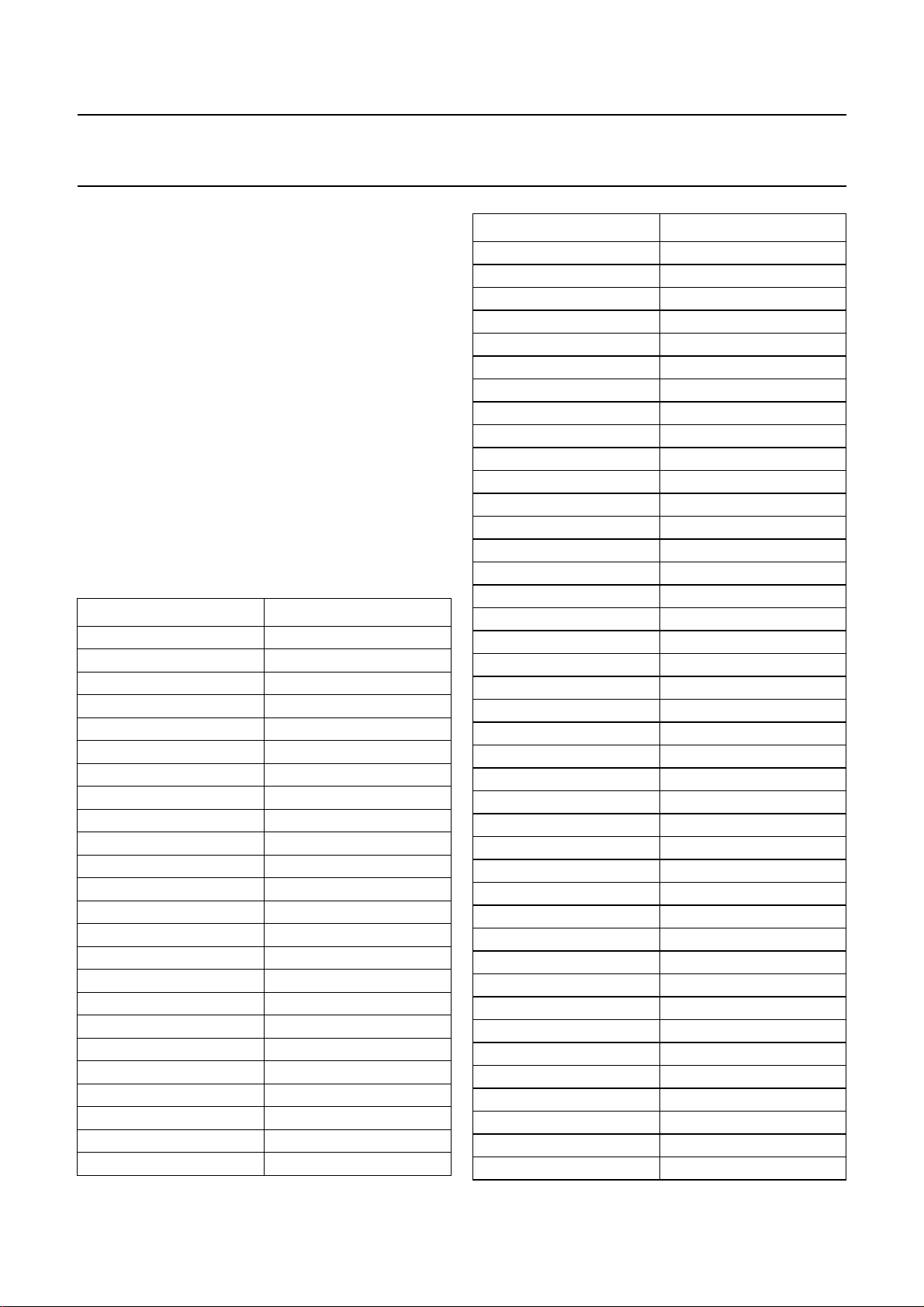

handbook, full pagewidth

5 BLOCK DIAGRAM

Philips Semiconductors Product specification

PCI video broadcast decoder SAA7130HL

base-

band

audio

inputs

CVBS

S-video

inputs

digital

data

inputs

left 1

right 1

left 2

right 2

CV0

CV1

CV2

CV3

CV4

TS data

TS data

2

I

GPIO

interrupt

ANALOG

NF/AUDIO

FRONT-END

STEREO

BUFFER

AUDIO

OUTPUT

audio

stereo

output

SAA7130HL

ANALOG

VIDEO

FRONT-END

ANALOG

VIDEO

FRONT-END

TS PARALLEL

S

TS SERIAL

STATIC I/O

IRQ

9-BIT

VIDEO

ADC

9-BIT

VIDEO

ADC

DIGITAL VIDEO

COMB FILTER

DECODER

VIDEO

SCALER

PIXEL ENGINE:

• MATRIX

• GAMMA

• FORMAT

FIFO

DMA

REGISTER

UNIT

PCI-bus

PCI INTERFACE

2

I

C-bus

ITU656

MHC170

Fig.2 Block diagram.

Philips Semiconductors Product specification

PCI video broadcast decoder SAA7130HL

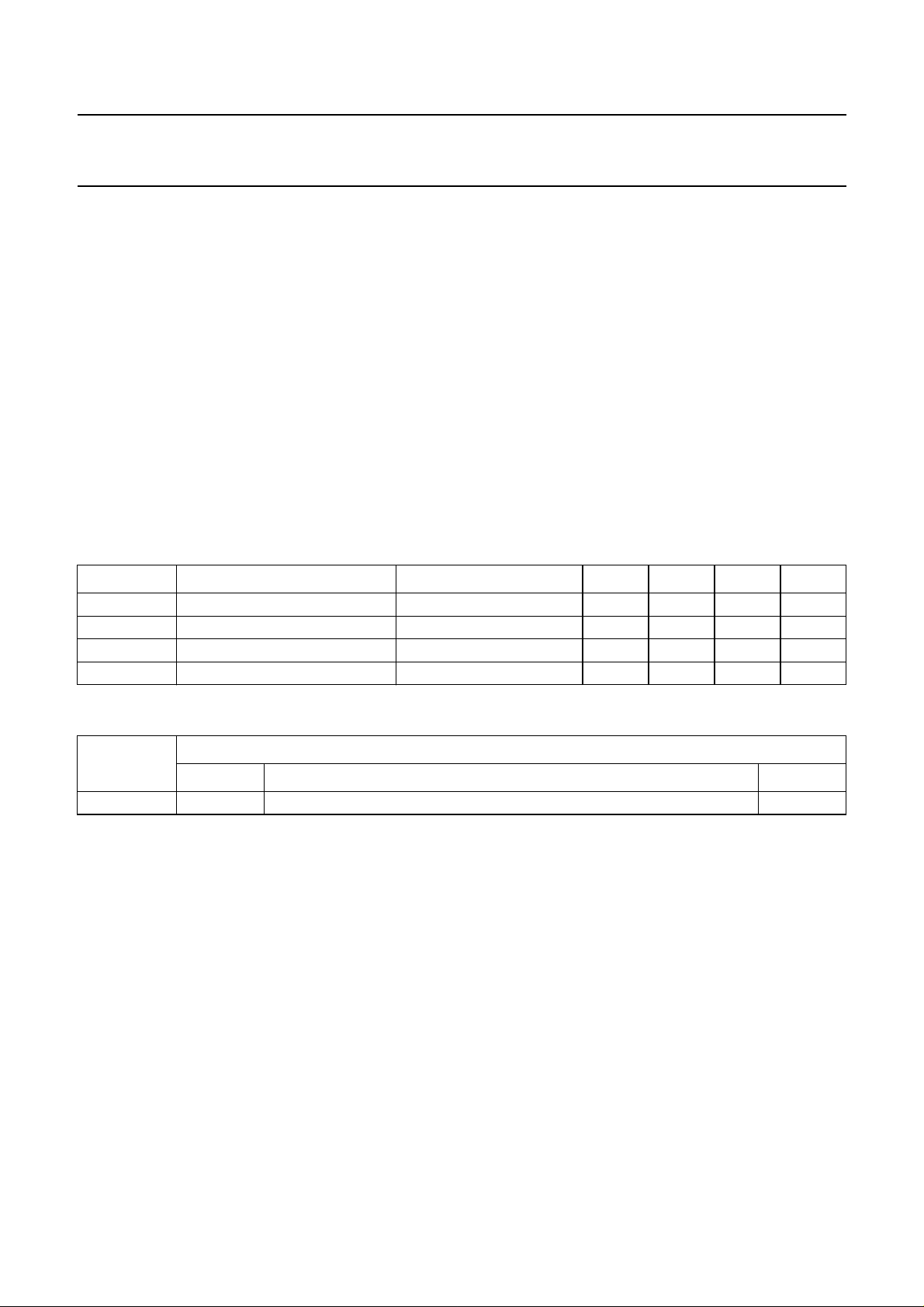

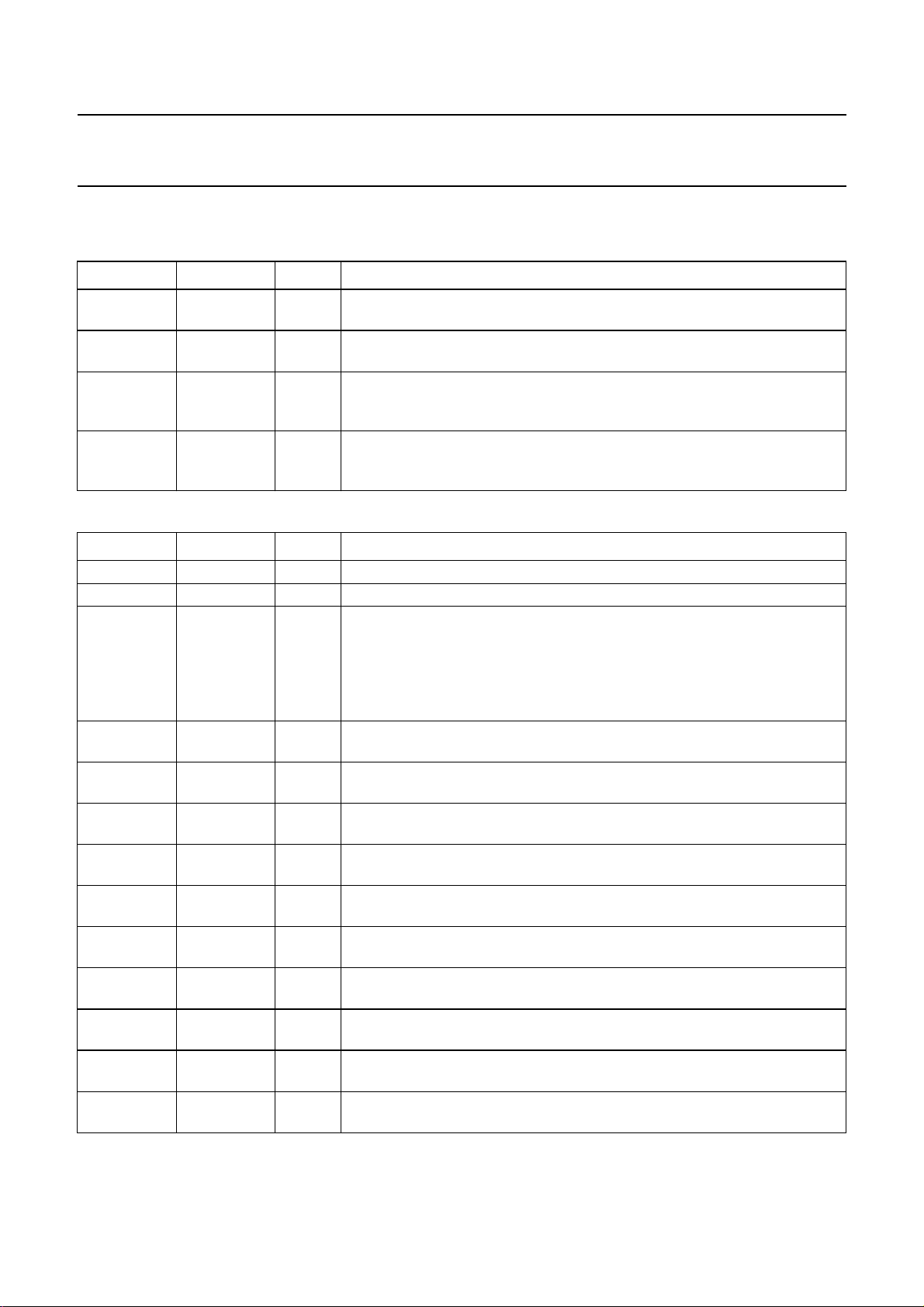

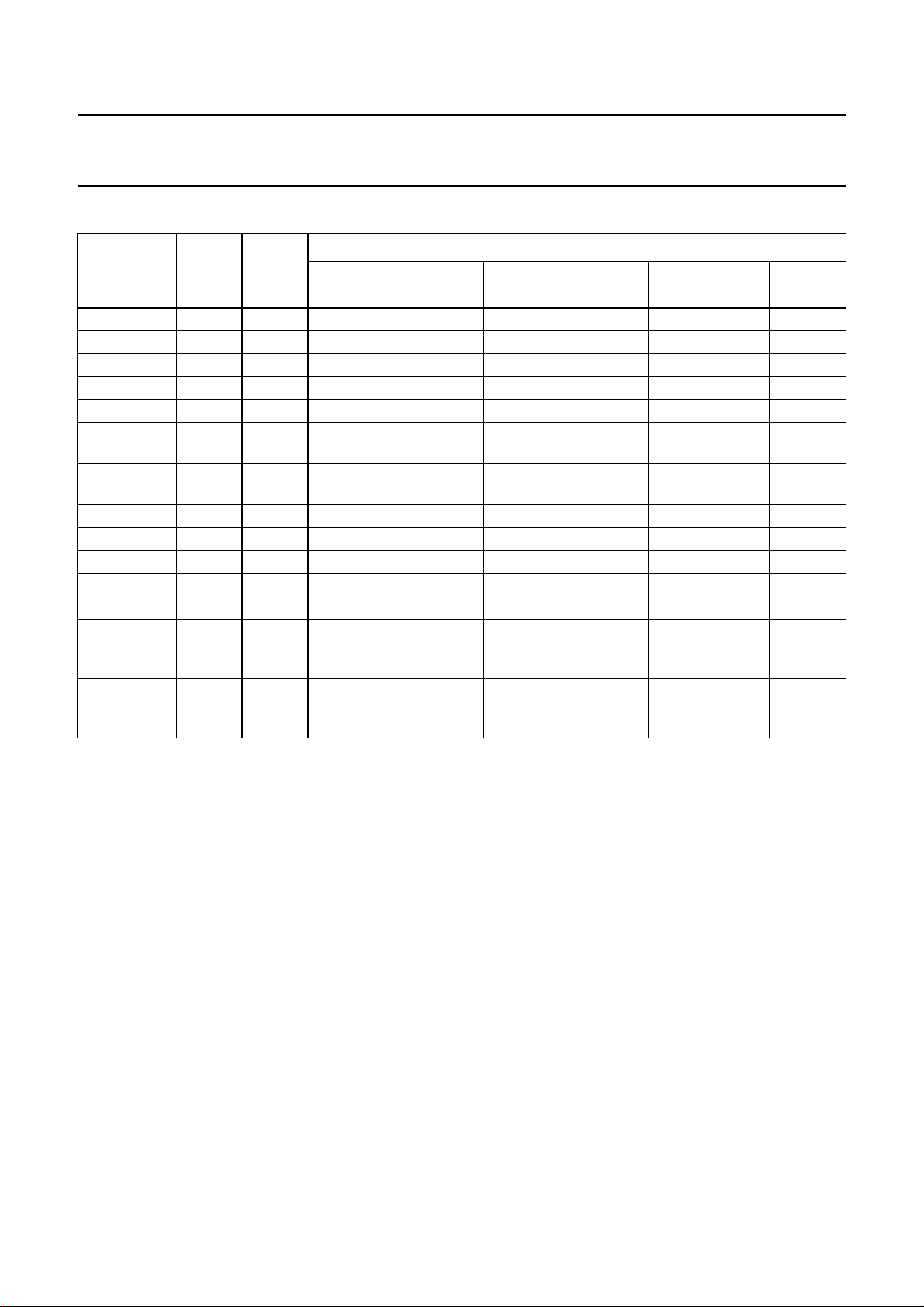

6 PINNING

The SAA7130HL is packaged in a rectangular LQFP (low

profile quad flat package) with 128 pins (see Fig.3).

In Section 6.1 all the pins are sorted by number.

The pin description for the functional groups is given in

Tables 2 to 7:

• Power supply pins

• PCI interface pins

• Analog interface pins

• Joint Test Action Group (JTAG) test interface pins for

boundary scan test

• I2C-bus multimaster interface

• General purpose interface (pins GPIO) and the main

functions.

The characteristicsof the pintypes are detailedin Table 8.

6.1 Pins sorted by number SYMBOL PIN

V

DDD

1

GNT# 2

REQ# 3

AD31 4

AD30 5

AD29 6

AD28 7

AD27 8

AD26 9

AD25 10

AD24 11

CBE#3 12

IDSEL 13

AD23 14

AD22 15

AD21 16

AD20 17

AD19 18

V

V

DDD

SSD

19

20

AD18 21

AD17 22

AD16 23

CBE#2 24

SYMBOL PIN

FRAME# 25

IRDY# 26

TRDY# 27

DEVSEL# 28

STOP# 29

PERR# 30

SERR# 31

PAR 32

CBE#1 33

AD15 34

AD14 35

AD13 36

AD12 37

V

V

DDD

SSD

38

39

PCI_CLK 40

AD11 41

AD10 42

AD9 43

AD8 44

CBE#0 45

AD7 46

AD6 47

AD5 48

AD4 49

AD3 50

AD2 51

AD1 52

AD0 53

V

V

DDD

SSD

54

55

GPIO23 56

GPIO22 57

GPIO21 58

GPIO20 59

GPIO19 60

GPIO18 61

XTALI 62

XTALO 63

V

V

SSD

DDD

64

65

2002 Apr 23 8

Philips Semiconductors Product specification

PCI video broadcast decoder SAA7130HL

SYMBOL PIN

V_CLK 66

GPIO17 67

GPIO16 68

GPIO15 69

GPIO14 70

GPIO13 71

GPIO12 72

V

V

DDD

SSD

73

74

GPIO11 75

GPIO10 76

GPIO9 77

GPIO8 78

GPIO7 79

GPIO6 80

GPIO5 81

GPIO4 82

GPIO3 83

GPIO2 84

GPIO1 85

GPIO0 86

GPIO27 87

GPIO26 88

GPIO25 89

SCL 90

SDA 91

V

V

DDD

SSD

92

93

LEFT2 94

V

DDA

95

LEFT1 96

V

SSA

97

RIGHT1 98

V

REF0

99

RIGHT2 100

V

V

REF1

REF2

101

102

OUT_RIGHT 103

OUT_LEFT 104

PROP_RST 105

SIF 106

SYMBOL PIN

V

V

REF3

SSA

107

108

CV2_C 109

V

V

DDA

REF4

110

111

DRCV_Y 112

V

SSA

113

CV0_Y 114

V

DDA

115

CV1_Y 116

DRCV_C 117

CV3_C 118

V

SSA

119

CV4 120

TRST 121

TCK 122

TMS 123

TDO 124

TDI 125

INT_A 126

PCI_RST# 127

V

SSD

128

2002 Apr 23 9

Philips Semiconductors Product specification

PCI video broadcast decoder SAA7130HL

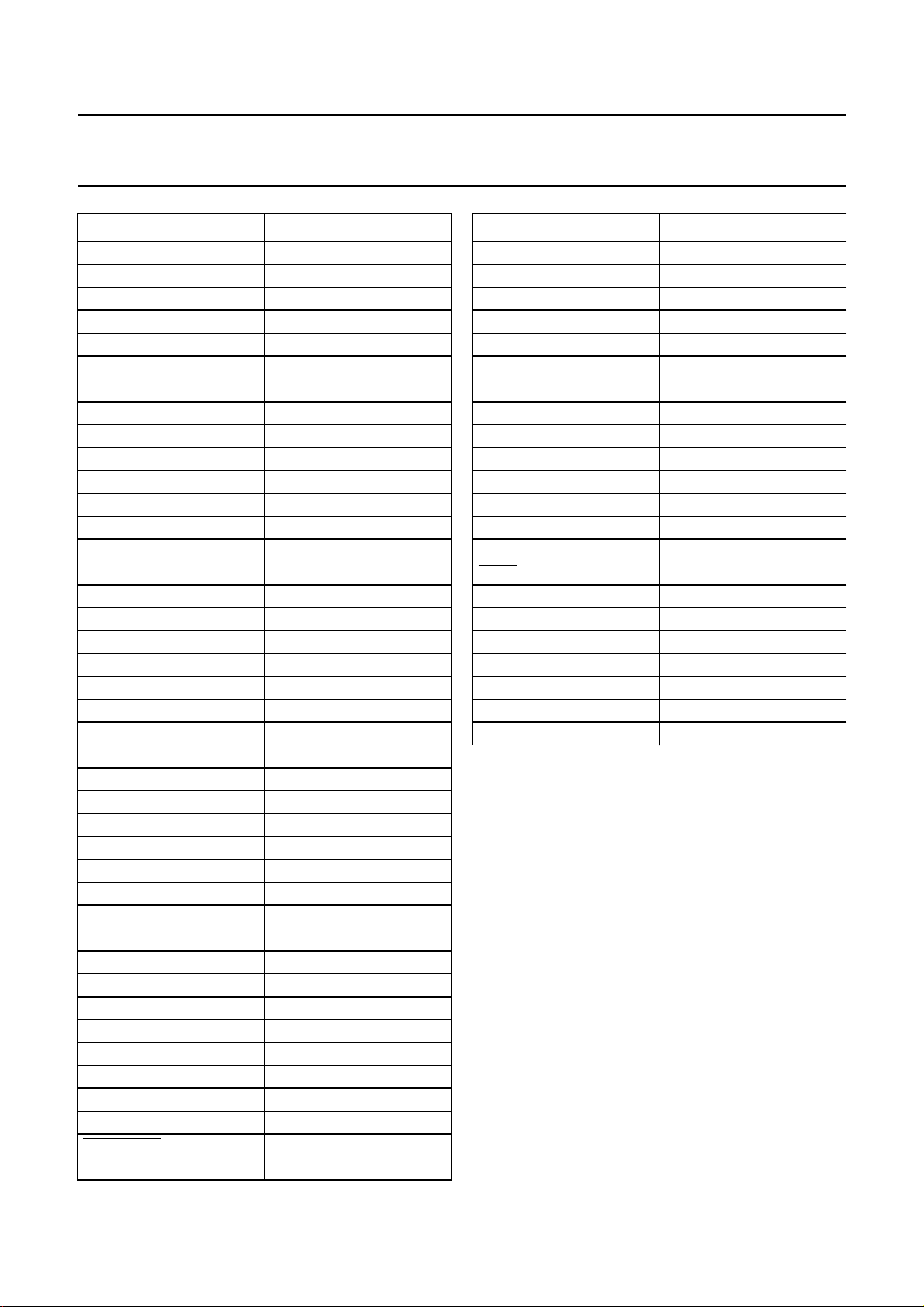

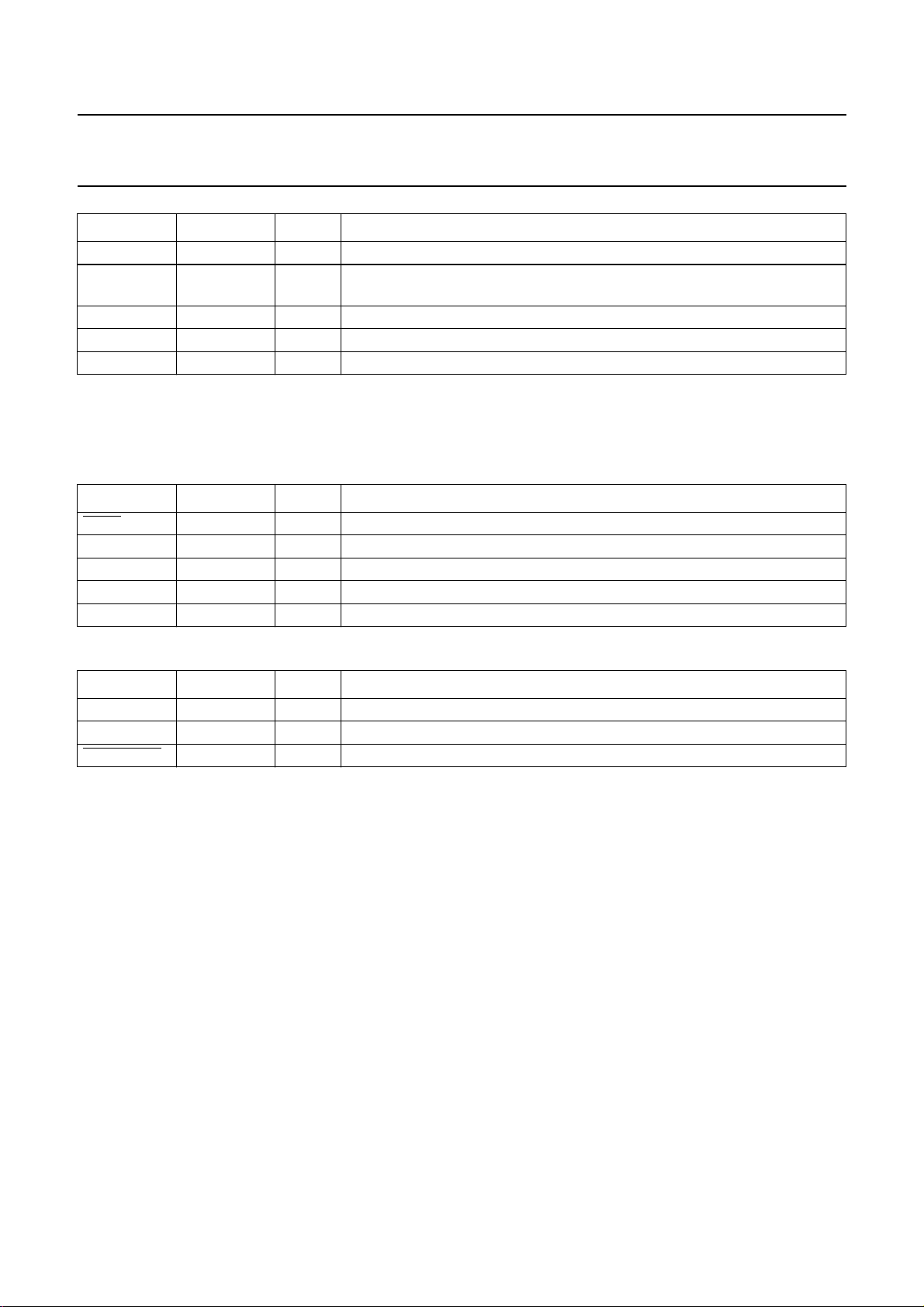

6.2 Pins grouped by function Table 2 Power supply pins

SYMBOL PIN TYPE DESCRIPTION

V

SSA

97, 108, 113

and 119

V

DDA

95, 110

and 115

V

SSD

20, 39, 55,

64, 74, 93

and 128

V

DDD

1, 19,38, 54,

65, 73

and 92

Table 3 PCI interface pins; note 1

SYMBOL PIN TYPE DESCRIPTION

PCI_CLK 40 PI PCI clock input: reference for all bus transactions, up to 33.33 MHz

PCI_RST# 127 PI PCI reset input: will 3-state all PCI pins (active LOW)

AD31 to AD0 4 to 11,

14 to 18,

21 to 23,

34 to 37,

41 to 44 and

46 to 53

CBE3# to

CBE0#

12, 24, 33

and 45

PAR 32 PIO and

FRAME# 25 PIO and

TRDY# 27 PIOand

IRDY# 26 PIOand

STOP# 29 PIOand

IDSEL 13 PI initialization device select input: this input is used to select the SAA7130HL

DEVSEL# 28 PIOand

REQ# 3 PO PCI request output: the SAA7130HL requests master access to PCI-bus

GNT# 2 PI PCI grant input: the SAA7130HL is granted to master access PCI-bus

AG analog ground for integrated analog signal processing

AS analog supply voltage for integrated analog signal processing

VG digital ground for digital circuit, core and I/Os

VS digital supply voltage for digital circuit, core and I/Os

PIOand

multiplexed address and data input or output: bi-directional, 3-state

T/S

PIOand

T/S

command code input or output: indicates type of requested transaction and

byte enable, for byte aligned transactions (active LOW)

parity input or output: driven by the data source, even parity over all pins AD

T/S

and CBE#

frame input or output: driven by the current bus master (owner), to indicate

S/T/S

the beginning and duration of a bus transaction (active LOW)

target ready input or output: driven by the addressed target, to indicate

S/T/S

readiness for requested transaction (active LOW)

initiator ready input or output: driven by the initiator, to indicate readiness to

S/T/S

continue transaction (active LOW)

stop input or output: target is requesting the master to stop the current

S/T/S

transaction (active LOW)

during configuration read and write transactions

device select input or output: driven by the target device, to acknowledge

S/T/S

address decoding (active LOW)

(active LOW)

(active LOW)

2002 Apr 23 10

Philips Semiconductors Product specification

PCI video broadcast decoder SAA7130HL

SYMBOL PIN TYPE DESCRIPTION

INT_A 126 PO and

O/D

PERR# 30 PIO and

S/T/S

SERR# 31 PO and

O/D

Note

1. PCI-bus pins are located on the long side of the package to simplify PCI board layout requirements.

Table 4 Analog interface pins; note 1

SYMBOL PIN TYPE DESCRIPTION

XTALI 62 CI quartz oscillator input: 32.11 or 24.576 MHz

XTALO 63 CO quartz oscillator output

LEFT2 94 AI analog audio stereo left 2 input or mono input

V

DDA

95 AS analog supply voltage (3.3 V)

LEFT1 96 AI analog audio stereo left 1 input or mono input; default analog pass-through

V

SSA

97 AG analog ground (for audio)

RIGHT1 98 AI analog audio stereo right 1 input or mono input; default analog pass-through

V

REF0

99 AR analog reference ground for audio Sigma Delta ADC; to be connected

RIGHT2 100 AI analog audio stereo right 2 input or mono input

n.c. 101 − not connected

n.c. 102 − not connected

OUT_RIGHT 103 AO analog audio stereo right channel output; 1 V (RMS) line-out, feeding the

OUT_LEFT 104 AO analog audio stereo left channel output; 1 V (RMS) line-out, feeding the

PROP_RST 105 AO analog output for test and debug purpose (active LOW)

n.c. 106 − not connected

V

V

REF3

SSA

107 AR analog reference voltage for audio FIR-DAC and SCART audio input buffer;

108 AG analog ground

CV2_C 109 AI composite video input (mode 2) or C input (modes 6 and 8)

V

DDA

110 AS analog power supply (3.3 V)

n.c. 111 − not connected

DRCV_Y 112 AR differential reference connection (for CV0 and CV1); to be supported with a

V

SSA

113 AG analog ground

CV0_Y 114 AI composite video input (mode 0) or Y input (modes 6 and 8)

V

DDA

115 AS analog supply voltage (3.3 V)

interrupt A output: this pin is an open-drain interrupt output, conditions

assigned by the interrupt register

parity error input or output: the receiving device detects data parity error

(active LOW)

system error output: reports address parity error (active LOW)

to pin OUT_LEFT after reset

to pin OUT_RIGHT after reset

directly to analog ground (V

SSA

)

audio loop back cable via a coupling capacitor of 2.2 µF

audio loop back cable via a coupling capacitor of 2.2 µF

to be supported with two parallel capacitors of 47 and 0.1 µF to analog

ground (V

capacitor of 47 nF to analog ground (V

SSA

)

)

SSA

2002 Apr 23 11

Philips Semiconductors Product specification

PCI video broadcast decoder SAA7130HL

SYMBOL PIN TYPE DESCRIPTION

CV1_Y 116 AI composite video input (mode 1) or Y input (modes 7 and 9)

DRCV_C 117 AR differential reference connection (for CV2, CV3 and CV4); to be supported

with a capacitor of 47 nF to analog ground (V

CV3_C 118 AI composite video input (mode 3) or C input (modes 7 and 9)

V

SSA

119 AG analog ground

CV4 120 AI composite video input (mode 4)

Note

1. TheSAA7130HL offers an interfacefor analog videoand audio signals. Therelated analog supply pinsare included

in this table.

Table 5 JTAG test interface pins

SYMBOL PIN TYPE DESCRIPTION

TRST 121 I test reset input: drive LOW for normal operating (active LOW)

TCK 122 I test clock input: drive LOW for normal operating

TMS 123 I test mode select input: tie HIGH or let float for normal operating

TDO 124 O test serial data output: 3-state

TDI 125 I test serial data input: tie HIGH or let float for normal operating

SSA

)

Table 6 I

2

C-bus multimaster interface

SYMBOL PIN TYPE DESCRIPTION

SCL 90 IO2 serial clock output; always available

SDA 91 IO2 serial data input and output; always available

PROP_RST 105 GO propagate reset and D3-hot output; to peripheral board circuitry

2002 Apr 23 12

Philips Semiconductors Product specification

PCI video broadcast decoder SAA7130HL

Table 7 GPIO pins and functions; note 1

FUNCTION

SYMBOL PIN TYPE

GPIO27 87 GIO −−−R/W

GPIO26 88 GIO −−−R/W

GPIO25 89 GIO −−−R/W

V_CLK 66 GO V_CLK (also gated) − ADC_CLK (out) −

GPIO23 56 GIO HSYNC − ADC_C[0] (LSB) R/W, INT

GPIO22 57 GIO VSYNC TS_LOCK (channel

GPIO21 58 GIO − TS_S_D

GPIO20 59 GIO − TS_CLK (<33 MHz) − R/W

GPIO19 60 GIO − TS_SOP (packet start) − R/W

GPIO18 61 GIO VAUX2 − X_CLK_IN R/W, INT

GPIO17 67 GIO VAUX1 (e.g. VACTIVE) − ADC_Y[0] (LSB) R/W

GPIO16 68 GIO − TS_VAL (valid flag) − R/W, INT

GPIO15 to

GIOPIO8

GPIO7 to

GPIO0

69 to 72

and

75 to 78

79 to 86 GIO VP extension for 16-bit

GIO VP[7:0] for formats:

AUDIO AND VIDEO

PORT OUTPUTS

ITU-R BT.656, VMI,

VIP (1.1, 2.0), etc.

formats: ZV, VIP-2,

DMSD, etc.

TS CAPTURE

INPUTS

decoder locked)

(bit-serial data)

− ADC_Y[8:1] R/W

TS_P_D[7:0]

(byte-parallel data)

RAW DTV/DVB

OUTPUTS

− R/W, INT

− R/W

ADC_C[8:1] R/W

GPIO

Note

1. The SAA7130HL offers a peripheral interface with General Purpose Input/Output (GPIO) pins. Dedicated functions

can be selected:

a) Digital Video Port (VP):output only;in 8-bitand 16-bitformats, suchas VMI, DMSD(ITU-R BT.601); zoom-video,

with discrete sync signals; ITU-R BT.656; VIP (1.1 and 2.0), with sync encoded in SAV and EAV codes.

b) Transport Stream (TS) capture input: from the peripheral DTV/DVB channel decoder; synchronized by Start Of

Packet (SOP); in byte-parallel or bit-serial protocol.

c) Digitized raw DTV/DVB samples stream output: from internal ADCs; to feed the peripheral DTV/DVB channel

decoder.

d) GPIO: as default (no other function selected); static (no clock); read and write from or to individually selectable

pins; latching ‘strap’ information at system reset time.

e) Peripheral interrupt (INT) input: enabled by interrupt enable register; routed to PCI interrupt (INT_A).

2002 Apr 23 13

Philips Semiconductors Product specification

PCI video broadcast decoder SAA7130HL

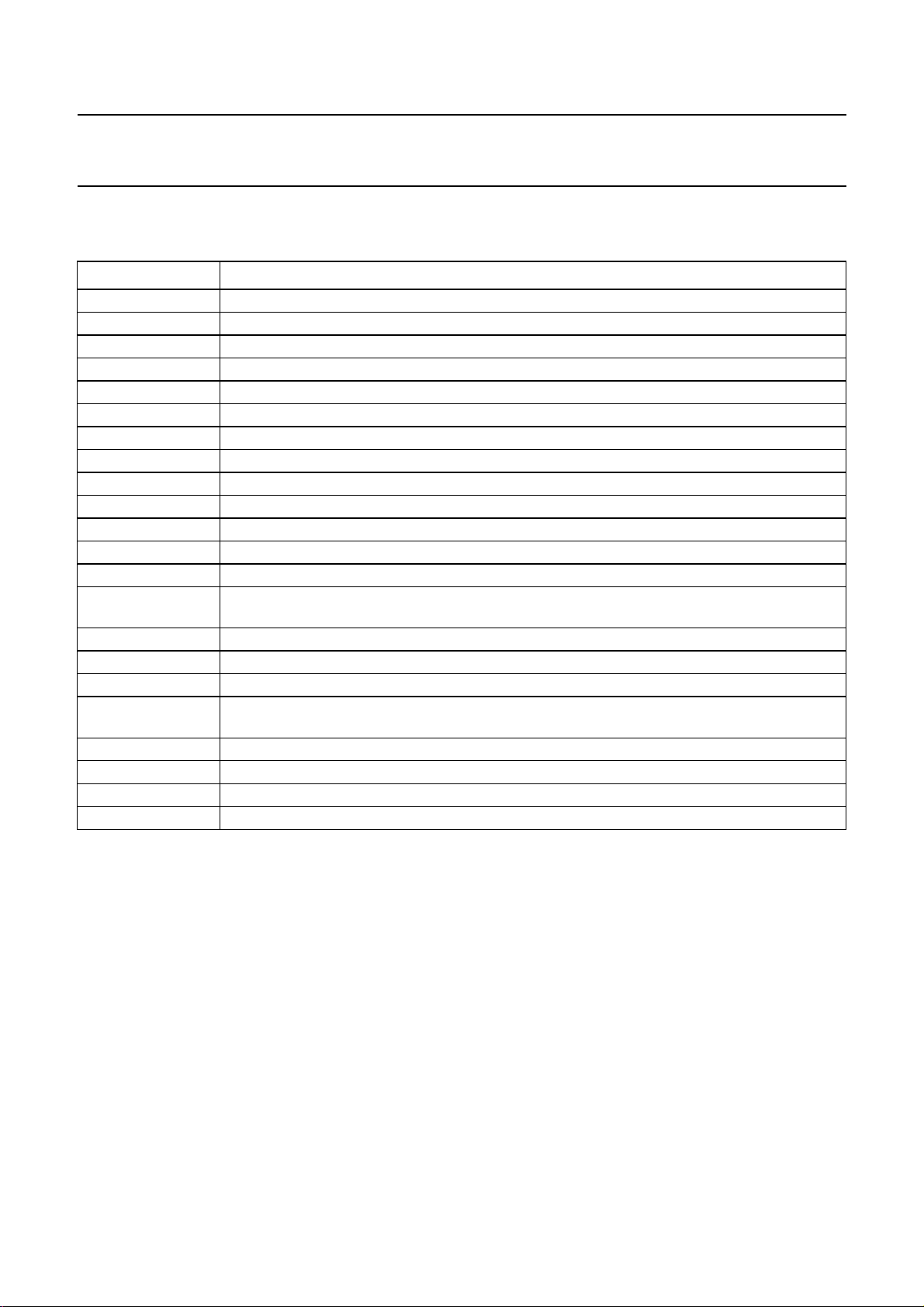

6.3 Pin description

Table 8 Characteristics of pin types and remarks

PIN TYPE DESCRIPTION

AG analog ground

AI analog input; video, audio and sound

AO analog output

AR analog reference support pin

AS analog supply voltage (3.3 V)

CI CMOS input; 3.3 V level (not 5 V tolerant)

CO CMOS output; 3.3 V level (not 5 V tolerant)

GI digital input (GPIO); 3.3 V level (5 V tolerant)

GIO digital input/output (GPIO); 3.3 V level (5 V tolerant)

GO digital output (GPIO); 3.3 V level (5 V tolerant)

I JTAG test input

IO2 digital input and output of the I

O JTAG test output

O/D open-drain output (for PCI-bus); multiple clients can drive LOW at the same time, wired-OR,

floating back to 3-state over several clock cycles

PI input according to PCI-bus requirements

PIO input and output according to PCI-bus requirements

PO output according to PCI-bus requirements

S/T/S sustained 3-state (for PCI-bus); previous owner drives HIGH for one clock cycle before leaving

to 3-state

T/S 3-state I/O (for PCI-bus); bi-directional

VG ground for digital supply

VS supply voltage (3.3 V)

With overscore or # this pin or ‘signal’ is active LOW, i.e. the function is ‘true’ if the logic level is LOW

2

C-bus interface; 3.3 and 5 V compatible, auto-adapting

2002 Apr 23 14

Philips Semiconductors Product specification

PCI video broadcast decoder SAA7130HL

handbook, full pagewidth

V

DDD

GNT#

REQ#

AD31

AD30

AD29

AD28

AD27

AD26

AD25

AD24

CBE#3

IDSEL

AD23

AD22

AD21

AD20

AD19

V

DDD

V

SSD

AD18

AD17

AD16

CBE#2

FRAME#

IRDY#

TRDY#

DEVSEL#

STOP#

PERR#

SERR#

PAR

CBE#1

AD15

AD14

AD13

AD12

V

DDD

SSD

PCI_RST#

V

INT_A

TDI

TDO

TMS

TCK

127

128

126

125

124

123

122

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

TRST

121

CV4

120

SSA

V

119

CV3_C

118

SAA7130HL

DRCV_C

CV1_Y

117

116

DDA

V

115

SSA

CV0_Y

V

114

113

DRCV_Y

n.c.

112

111

DDA

V

110

CV2_C

V

109

108

SSAVREF3

n.c.

107

106

PROP_RST

OUT_LEFT

OUT_RIGHT

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

n.c.

n.c.

RIGHT2

V

REF0

RIGHT1

V

SSA

LEFT1

V

DDA

LEFT2

V

SSD

V

DDD

SDA

SCL

GPIO25

GPIO26

GPIO27

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

V

SSD

V

DDD

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

GPIO17

V_CLK

V

DDD

40394142434445464748495051525354555657585960616263

AD6

AD5

AD4

AD3

SSD

V

AD11

PCI_CLK

AD10

AD9

AD8

AD7

CBE#0

AD2

Fig.3 Pin configuration.

2002 Apr 23 15

AD1

AD0

DDD

V

SSD

V

GPIO23

GPIO22

GPIO21

GPIO20

GPIO19

GPIO18

XTALI

XTALO

64

SSD

V

MHC168

Loading...

Loading...