INTEGRATED CIRCUITS

DATA SH EET

SAA7110; SAA7110A

One Chip Front-end 1 (OCF1)

Product specification

File under Integrated Circuits, IC22

1995 Oct 18

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

CONTENTS

1 FEATURES

2 APPLICATIONS

3 GENERAL DESCRIPTION

4 QUICK REFERENCE DATA

5 ORDERING INFORMATION

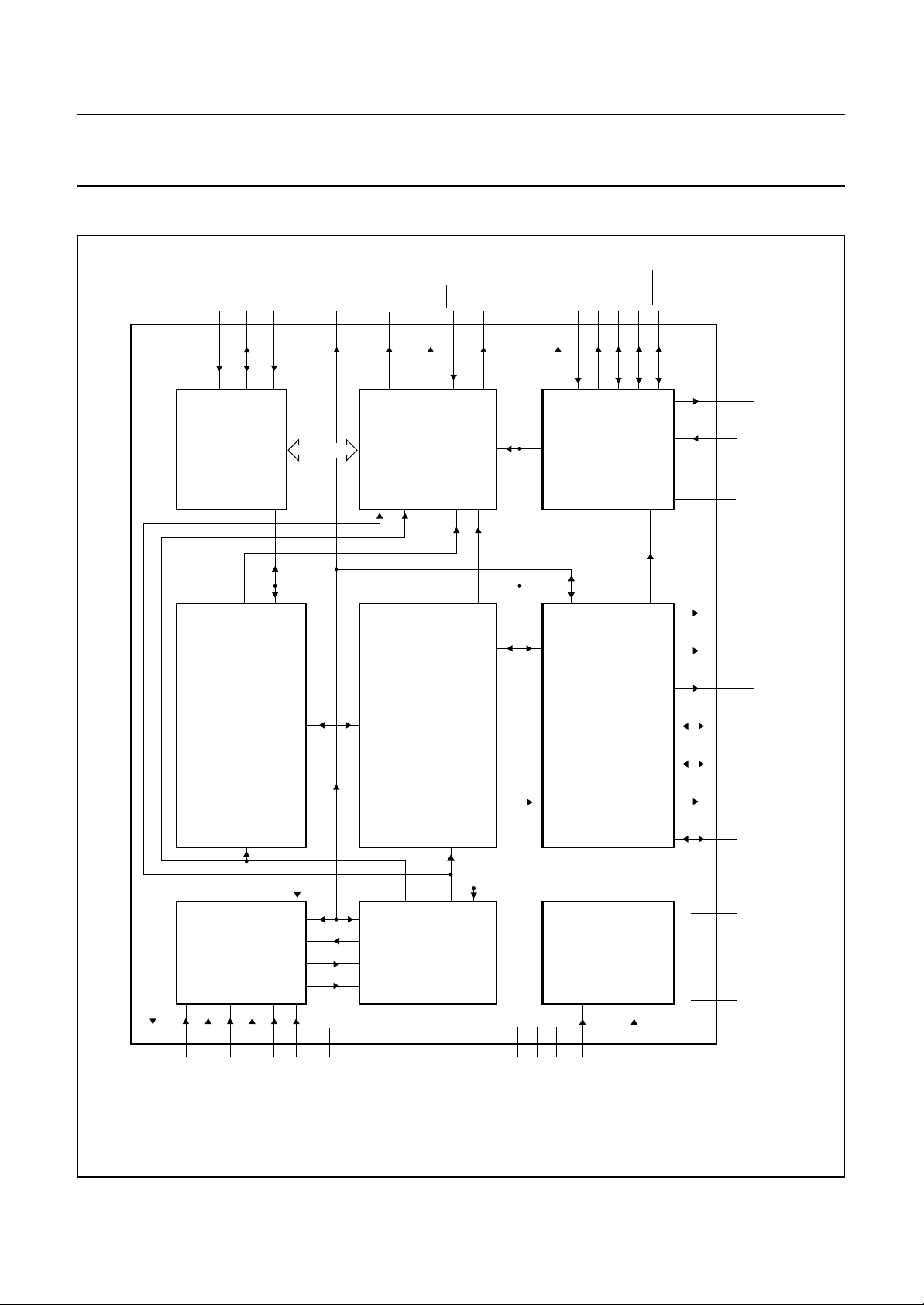

6 SYSTEM VIEW

7 BLOCK DIAGRAM

8 PINNING

9 FUNCTIONAL DESCRIPTION

9.1 Analog input processing (see Fig.5)

9.2 Analog control circuits

9.3 Chrominance processing (see Fig.6)

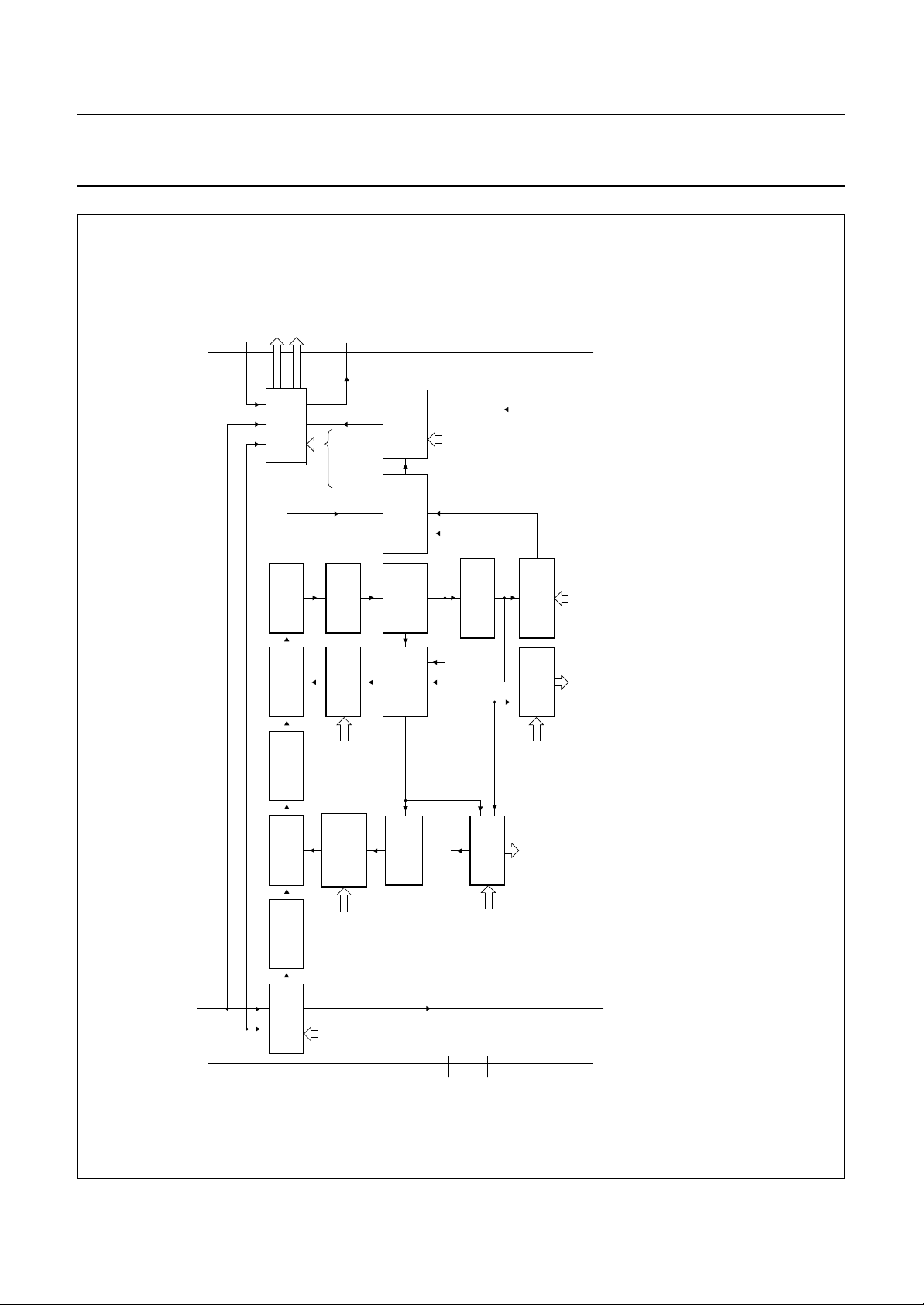

9.4 Luminance processing (see Fig.7)

9.5 YUV-bus (digital outputs)

9.6 Synchronization (see Fig.7)

9.7 Clock generation circuit

9.8 Power-on reset

9.9 RTCO output

10 GAIN CHARTS

11 LIMITING VALUES

12 CHARACTERISTICS

13 TIMING

14 OUTPUT FORMATS

15 CLOCK SYSTEM

15.1 Clock generation circuit

15.2 Power-on control

16 I2C-BUS DESCRIPTION

16.1 I2C-bus format

16.2 I2C-bus receiver/transmitter tables

16.3 I2C-bus detail

16.4 I2C-bus detail (continued)

17 SOURCE SELECTION MANAGEMENT

18 ANTI-ALIAS FILTER GRAPHS

19 CORING FUNCTION

19.1 Coring function adjustment by subaddress 06H

to affect band filter output adjustment

20 LUMINANCE FILTER GRAPHS

21 I2C-BUS START SET-UP

21.1 Remarks to Table 66

22 APPLICATION INFORMATION

23 START-UP, SOURCE SELECT AND

STANDARD DETECTION FLOW EXAMPLE

23.1 CODE 0 STARTUP and STANDARD

Procedure

23.2 MODE 0 Source Select Procedure

23.3 MODE 1 Source Select Procedure

23.4 MODE 2 Source Select Procedure

23.5 MODE 3 Source Select Procedure

23.6 MODE 4 Source Select Procedure

23.7 MODE 5 Source Select Procedure

23.8 MODE 6 Source Select Procedure

23.9 MODE 7 Source Select Procedure

23.10 MODE 8 Source Select Procedure

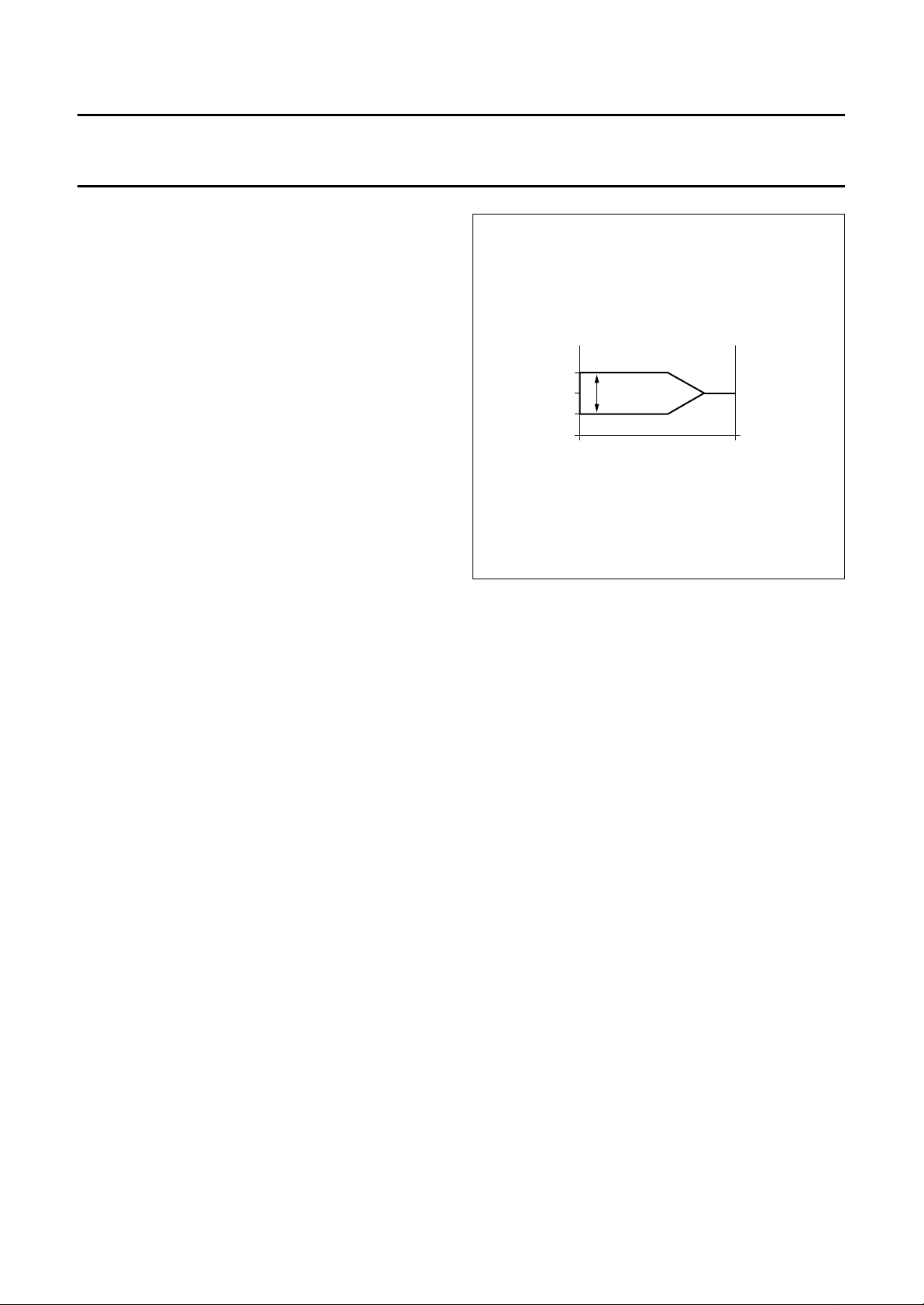

24 PACKAGE OUTLINE

25 SOLDERING

25.1 Introduction

25.2 Reflow soldering

25.3 Wave soldering

25.4 Repairing soldered joints

26 DEFINITIONS

27 LIFE SUPPORT APPLICATIONS

28 PURCHASE OF PHILIPS I2C COMPONENTS

1995 Oct 18 2

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

1 FEATURES

• Six analog inputs (6 × CVBS or 3 × Y/C or

combinations)

• Three analog processing channels

• Three built-in analog anti-aliasing filters

• Analog signal adding of two channels

• Two 8-bit video CMOS analog-to-digital converters

• Fully programmable static gain for the main channels or

automatic gain control for the selected CVBS/Y channel

• Selectable white peak control signal

• Luminance and chrominance signal processing for

PAL B/G, NTSC M and SECAM

• Full range HUE control

• Automatic detection of 50/60 Hz field frequency, and

automatic switching between standards PAL and NTSC,

SECAM forceable

• Horizontal and vertical sync detection for all standards

• Cross-colour reduction by chrominance comb filtering

for NTSC or special cross-colour cancellation for

SECAM

• UV signal delay lines for PAL to correct chrominance

phase errors

• The YUV-bus supports a data rate of:

– 780 × fh= 12.2727 MHz for 60 Hz (NTSC)

– 944 × fh= 14.75 MHz for 50 Hz (PAL/SECAM)

• Square pixel format with 768/640 active samples per

line on the YUV-bus

• CCIR 601 level compatible

• 4:2:2 and 4:1:1 YUV output formats in 8-bit

resolution

• User programmable luminance peaking for aperture

correction

• Compatible with memory-based features

(line-locked clock, square pixel)

• Requires only one crystal (26.8 MHz) for all standards

• Real time status information output (RTCO)

• Brightness Contrast Saturation (BCS) control for the

YUV-bus

• Negation of picture possible

• One user programmable general purpose switch on an

output pin

• Switchable between on-chip Clock Generation Circuit

(CGC) and external CGC (SAA7197)

• Power-on control

2

• I

C-bus controlled.

2 APPLICATIONS

• Desktop video

• Multimedia

• Digital television

• Image processing

• Video phone

• Video picture grabbing.

3 GENERAL DESCRIPTION

The one chip front-end SAA7110; SAA7110A is a digital

multistandard colour decoder (OCF1) on the basis of the

DIG-TV2 system with two integrated Analog-to-Digital

Converters (ADCs), a Clock Generation Circuit (CGC) and

Brightness Contrast Saturation (BCS) control.

The CMOS circuit SAA7110; SAA7110A, analog front-end

and digital video decoder, is a highly integrated circuit for

desktop video applications. The decoder is based on the

principle of line-locked clock decoding. It operates

square-pixel frequencies to achieve correct aspect ratio.

Monitor controls are provided to ensure best display. The

circuit is I2C-bus controlled.

4 QUICK REFERENCE DATA

SYMBOL PARAMETER MIN. MAX. UNIT

V

V

T

DDA

DDD

amb

analog supply voltage 4.75 5.25 V

digital supply voltage 4.5 5.5 V

operating ambient temperature 0 70 °C

1995 Oct 18 3

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

5 ORDERING INFORMATION

TYPE NUMBER

PACKAGE

NAME DESCRIPTION VERSION

SAA7110 PLCC68 plastic leaded chip carrier; 68 leads SOT188-2

SAA7110A PLCC68 plastic leaded chip carrier; 68 leads SOT188-2

6 SYSTEM VIEW

PC ISA - BUS

handbook, full pagewidth

2

I

C

six

video inputs

ONE

CHIP

FRONT-END

OCF1

clock

VIDEO

MEMORY

CONTROLLER

VMC

VIDEO

FRAME

MEMORY

YUV - BUS

Fig.1 System diagram.

MGC821

1995 Oct 18 4

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

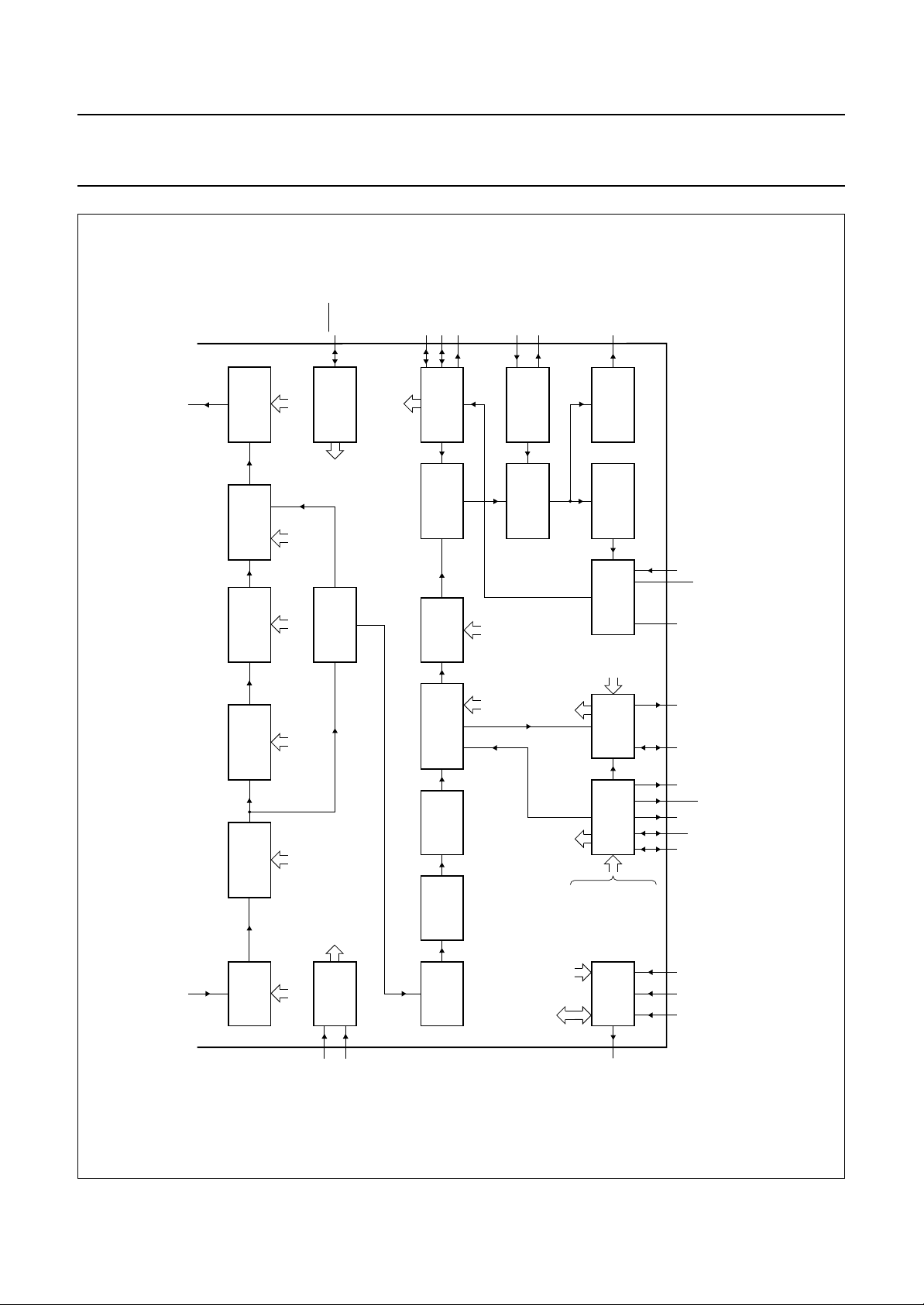

7 BLOCK DIAGRAM

LLC2

CREF

RESET

XTALO

65

XTALI

66

CLOCK

GENERATION

30

CIRCUIT

UV7

to

UV0

SA

6

5

4

C-BUS

2

I

INTERFACE

GPSW

(VBLK)

64

55 to 62

8

C-BUS

2

I

CONTROL

SCL

SDA

Y7 to Y0

53, 54

45 to 50,

AND

CONTROL

CONTRAST

SATURATION

BRIGHTNESS

FEIN

(MUXC)

63

OUTPUT

FORMATTER

Y

UV

HREF

42

CLOCKS

LLC

312932

POWER-ON

CONTROL

33

2524

MGC820

CGCE

DDA0

V

LFCO

SSA0

V

BYPASS

CIRCUIT

CHROMINANCE

C/CVBS

CON

ANALOG

PROCESSING

AD2 AD3

CIRCUIT

LUMINANCE

Y/CVBS

ANALOG

CONTROL

SAA7110

SAA7110A

3 26

RTCO

39

PLIN (HL)

40

handbook, full pagewidth

Fig.2 Block diagram.

HSY HCLVS

HS

V

V

SS

DD

ODD (VL)

36

CIRCUIT

SYNCHRONIZATION

Y

Y

TEST

BLOCK

CONTROL

37

41 38

67, 51, 43,

35, 28

68, 52, 44,

34, 27

23

AOUT

11

AI42

13

AI41

15

AI32

17

AI31

19

AI22

21

AI21

7, 8, 9

i.c.

1995 Oct 18 5

18, 14, 10

20, 16, 12

SSA4

DDA4

to V

to V

SSA2

DDA2

V

V

22

V

SS(S)

2

AP

1

SP

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

8 PINNING

SYMBOL PIN DESCRIPTION

SP 1 test pin input; (shift pin) connect to ground for normal operation

AP 2 test pin input; (action pin) connect to ground for normal operation

RTCO 3 Real Time Control Output. This pin is used to fit serially the increments of the HPLL and

FSC-PLL and information of the PAL or SECAM sequence.

2

SA 4 I

SDA 5 I

SCL 6 I

i.c. 7 reserved pin; do not connect

i.c. 8 reserved pin; do not connect

i.c. 9 reserved pin; do not connect

V

SSA4

10 ground for analog input 4

AI42 11 analog input 42

V

DDA4

12 supply voltage (+5 V) for analog input 4

AI41 13 analog input 41

V

SSA3

14 ground for analog input 3

AI32 15 analog input 32

V

DDA3

16 supply voltage (+5 V) for analog input 3

AI31 17 analog input 31

V

SSA2

18 ground for analog input 2

AI22 19 analog input 22

V

DDA2

20 supply voltage (+5 V) for analog input 2

AI21 21 analog input 21

V

SS(S)

22 substrate ground

AOUT 23 analog test output; do not connect

V

V

DDA0

SSA0

24 supply voltage (+5 V) for internal CGC (Clock Generation Circuit)

25 ground for internal CGC

LFCO 26 Line Frequency Control output; this is the analog clock control signal driving the external

V

DD

V

SS

27 supply voltage (+5 V)

28 ground

LLC 29 Line-Locked Clock input/output (CGCE = 1, output; CGCE = 0, input). This is the system

LLC2 30 Line-Locked Clock

CREF 31 Clock reference input/output (CGCE = 1, output; CGCE = 0, input). This is a clock qualifier

C-bus slave address select input. LOW: slave address = 9CH for write, 9DH for read;

HIGH = 9DH for write, 9FH for read.

2

C-bus serial data input/output

2

C-bus serial clock input

CGC. The frequency is a multiple of the actual line frequency (nominally 7.375/6.13636 MHz).

The signal has a triangular form with 4-bit accuracy.

clock, its frequency is 1888 × f

for 50 Hz/625 lines per field systems and 1560 × fh for

h

60 Hz/525 lines per field systems; or variable input clock up to 32 MHz in input mode.

1

⁄2output; f

LLC2

= 0.5 × f

(CGCE = 1, output; CGCE = 0, high

LLC

impedance).

signal distributed by the internal or an external clock generator circuit (CGC). Using CREF all

interfaces on the YUV-bus are able to generate a bus timing with identical phase.

1995 Oct 18 6

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

SYMBOL PIN DESCRIPTION

RESET 32 Reset active LOW input/output (CGCE = 1, output; CGCE = 0, input); sets the device into a

defined state. All data outputs are in high impedance state. The I2C-bus is reset (waiting for

START condition). Using the external CGC, the LOW period must be maintained for at least

30 LLC clock cycles.

CGCE 33 CGC Enable active HIGH input (CGCE = 1, on-chip CGC active; CGCE = 0, external CGC

mode, use SAA7197).

V

DD

V

SS

HCL 36 Horizontal Clamping input/output pulse (programmable via I

HSY 37 Horizontal Synchronization input/output indicator (programmable via I

HS 38 Horizontal Synchronization output (programmable; the HIGH period is 128 LLC clock cycles).

PLIN (HL) 39 PAL Identifier Not output; marks for demodulated PAL signals the inverted line (PLIN = LOW)

ODD (VL) 40 ODD/EVEN field identification output; a HIGH state indicates the odd field. Select ODD

VS 41 Vertical Synchronization input/output (programmable via I

HREF 42 Horizontal Reference output; this signal is used to indicate data on the digital YUV-bus. The

V

SS

V

DD

34 supply voltage (+5 V)

35 ground

output; PULIO = 0, input). This signal is used to indicate the black level clamping period for

the analog input interface. The beginning and end of its HIGH period (only in the output mode)

can be programmed via the I2C-bus registers 03H, 04H in 50 Hz mode and registers 16H,

17H in 60 Hz mode, active HIGH.

PULIO = 1, output; PULIO = 0, input). This signal is fed to the analog interface. The beginning

and end of its HIGH period (only in the output mode) can be programmed via the I2C-bus

registers 01H, 02H in 50 Hz mode and registers 14H, 15H in 60 Hz mode, active HIGH.

The position of the positive slope is programmable in 8 LLC increments over a complete line

2

(64 µs) via the I

C-bus register 05H in 50 Hz mode or register 18H in 60 Hz mode.

and a non-inverted line (PLIN = HIGH) and for demodulated SECAM the DR line

(PLIN = LOW) and the DB line (PLIN = HIGH). Select PLIN function via I

(H-PLL locked output; a HIGH state indicates that the internal PLL has locked. Select HL

function via I2C-bus bit RTSE = 1).

2

function via I

C-bus bit RTSE = 0.

(Vertical Locked output; a HIGH state indicates that the internal Vertical Noise Limiter (VNL)

is in a locked state. Select VL function via I2C-bus bit RTSE = 1).

output; OEHV = 0, input). This signal indicates the vertical synchronization with respect to the

YUV output. The high period of this signal is approximately six lines if the VNL function is

active. The positive slope contains the phase information for a deflection controller, for

example the TDA9150. In input mode this signal is used to synchronize the vertical gain and

clamp blanking stage, active HIGH.

positive slope marks the beginning of a new active line. The HIGH period of HREF is either

768 Y samples or 640 Y samples long depending on the detected field frequency

(50/60 Hz mode). HREF is used to synchronize data multiplexer/demultiplexers. HREF is also

present during the vertical blanking interval.

43 ground

44 supply voltage (+5 V)

2

C-bus bit PULIO: PULIO = 1,

2

C-bus bit PULIO:

2

C-bus bit RTSE = 0.

2

C-bus bit OEHV: OEHV = 1,

1995 Oct 18 7

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

SYMBOL PIN DESCRIPTION

Y7 45

Y6 46

Y5 47

Y4 48

Y3 49

Y2 50

V

SS

V

DD

51 ground

52 supply voltage (+5 V)

Y1 53

Y0 54

UV7 55

UV6 56

UV5 57

UV4 58

UV3 59

UV2 60

UV1 61

UV0 62

FEIN

63 Fast Enable input (active LOW); this signal is used to control fast switching on the digital

(MUXC)

GPSW

64 General Purpose Switch output; the state of this signal is programmable via I

(VBLK)

XTALO 65 Crystal oscillator output (to 26.8 MHz crystal); not used if TTL clock is used.

XTALI 66 Crystal oscillator input (from 26.8 MHz crystal) or connection of external oscillator with TTL

V

SS

V

DD

67 ground

68 supply voltage (+5 V)

Upper 6 bits of the 8-bit luminance (Y) digital output. As part of the digital YUV-bus

(data rate LLC/2), or A/D2(3) output (data rate LLC/2) selectable via I

2

C-bus bit SQPB = 1.

Lower 2 bits of the 8-bit luminance (Y) digital output. As part of the digital YUV-bus

2

(data rate LLC/2), or A/D2(3) output (data rate LLC/2) selectable via I

C-bus bit SQPB = 1.

8-bit digital UV (colour difference) output; multiplexed colour difference signal for U and V

component of demodulated CVBS or chrominance signal. The format and multiplexing

2

scheme can be selected via I

C-bus control. These signals are part of the digital YUV-bus

(data rate LLC/2), or A/D3(2) output (data rate LLC/2) selectable via I2C-bus bit SQPB = 1.

YUV-bus. A high at this input forces the IC to set its Y and UV outputs to the high impedance

state. To use this function set I2C-bus bits MS24 and MS34 and MUYC to LOW.

(Multiplex Components input; control signal for the analog multiplexers for fast switching

between locked Y/C signals or locked CVBS signals. FEIN automatically fixed to LOW (digital

YUV-bus enabled), if one of the three MUXC functions are selected (MS24 or MS34 or

MUYC = HIGH).

2

C-bus register

0Dh, bit 1. Select GPSW function via I2C-bus bit VBLKA = 0. (Vertical Blank test output; select

VBLK via I2C-bus bit VBLKA = 1).

compatible square wave clock signal.

1995 Oct 18 8

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

SS

handbook, full pagewidth

i.c.

9

i.c.

8

i.c.

7

SCL

6

SDA

5

SA

4

RTCO

3

AP

2

SP

1

VDDV

68

67

66 XTALI

XTALO

GPSW (VBLK)

65

64

FEIN (MUXC)

UV0

UV1

63

62

61

V

SSA4

V

DDA4

V

SSA3

V

DDA3

V

SSA2

V

DDA2

V

SS(S)

AOUT

V

DDA0

V

SSA0

LFCO

AI42

AI41

AI32

AI31

AI22

AI21

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

SAA7110

SAA7110A

60

UV2

59

UV3

58

UV4

57

UV5

56

UV6

55

UV7

54

Y0

53

Y1

52

V

DD

51

V

SS

50

Y2

49

Y3

48

Y4

47

Y5

46

Y6

45

Y7

44

V

DD

27

28

29LLC

30

31

32

33

34

SS

DD

V

V

LLC2

CREF

RESET

CGCE

DD

V

Fig.3 Pin configuration.

1995 Oct 18 9

35

36

37

38

39

40

41

42

43

MGC822

SS

V

HCL

HSY

HS

PLIN (HL)

VS

ODD (VL)

HREF

SS

V

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

9 FUNCTIONAL DESCRIPTION

9.1 Analog input processing (see Fig.5)

The SAA7110; SAA7110A offers six analog signal inputs,

two analog main channels with clamping circuit, analog

amplifier, anti-alias filter and video CMOS ADC. A third

analog channel also with clamping circuit, analog amplifier

and anti-alias filter can be added or switched to both main

channels directly before the ADCs.

9.2 Analog control circuits

The clamping control circuit controls the correct clamping

of the analog input signals. The coupling capacitor is also

used to store and filter the clamping voltage. The normal

digital clamping level for luminance or CVBS signals is 64

and for chrominance signals is128.

2

The gain control circuits generate via I

C-bus the static

gain levels for the three analog amplifiers or controls one

of these amplifiers automatically via a built-in Automatic

Gain Control (AGC). The AGC is used to amplify a

CVBS or Y signal to the required signal amplitude,

matched to the ADCs input voltage range.

The anti-alias filters are adapted to the clock frequency.

The vertical blanking control circuit generates an I2C-bus

programmable vertical blanking pulse. During the vertical

blanking time gain and clamping control are frozen.

The fast switch control circuit is used for special

applications.

9.2.1 C

LAMPING

The coupling capacitor is used as clamp capacitance for

each input. An internal digital clamp comparator generates

the information concerning clamp-up or clamp-down. The

clamping levels for the two ADC channels are adjustable

over the 8-bit range (1 to 254). Clamping time in normal

use is set with the HCL pulse at the back porch of the video

signal. The clamping pulse HCL is user adjustable.

9.2.2 G

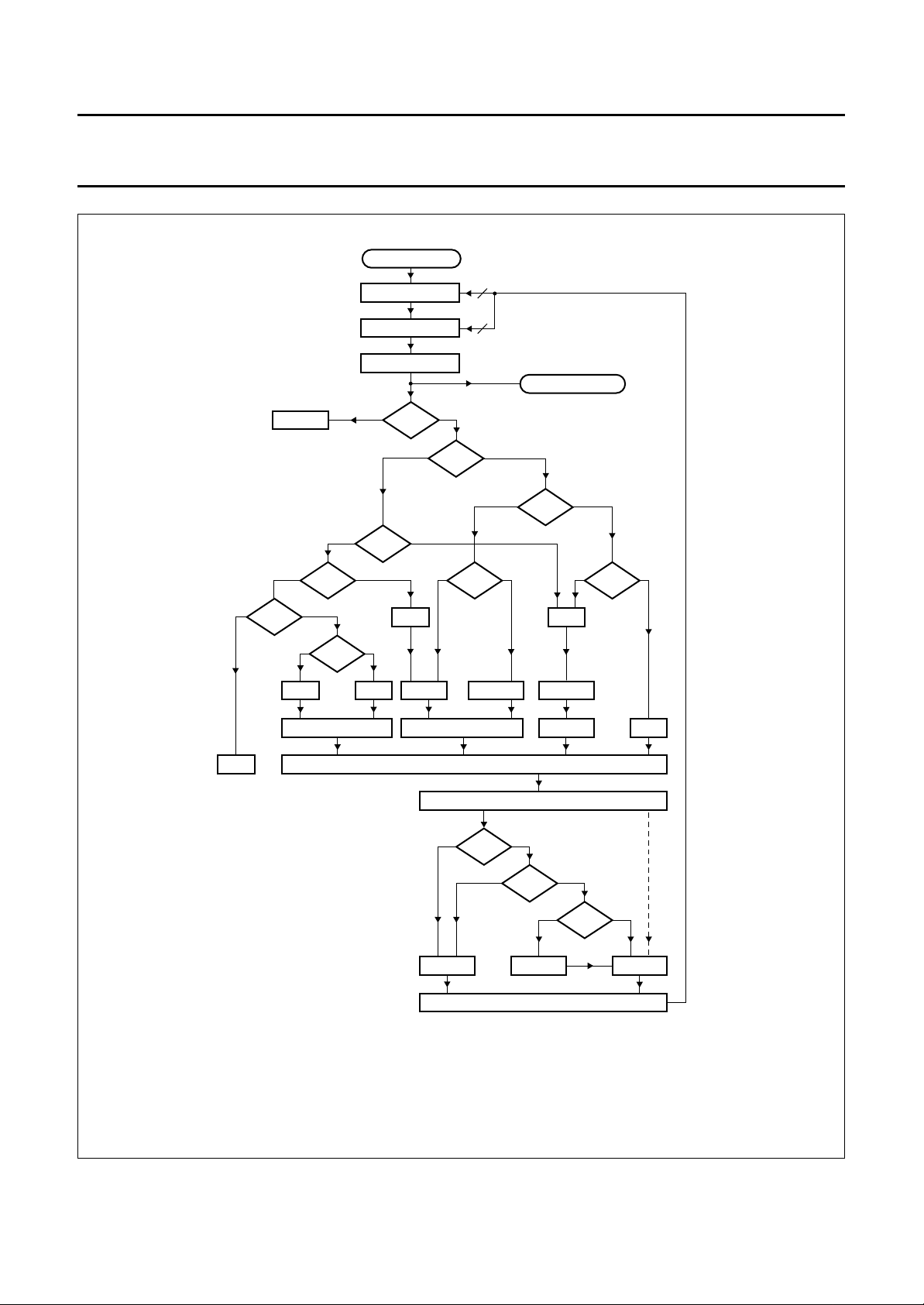

AIN CONTROL (see Fig.4)

The luminance AGC can be used for every channel were

luminance or CVBS is being received. AGC active time is

the sync tip of the video signal. The sync tip pulse HSY is

user adjustable. The AGC can be switched off and the gain

for the three main input channels can be adjusted

independently. Signal (white) peak control limits the gain

at signal overshoots. The flow charts (see Figs 8 and 9)

show more details of the AGC. The influence of supply

voltage variation within the specified range is automatically

eliminated by clamp and automatic gain control.

handbook, halfpage

analog input level

+2.8 dB

−6 dB

maximum

0 dB

minimum

range 8.8 dB

Fig.4 Automatic gain control range.

9.3 Chrominance processing (see Fig.6)

The 8-bit chrominance signal passes the input interface,

the chrominance bandpass filter to eliminate DC

components, and is finally fed to the multiplication inputs

of a quadrature demodulator, where two subcarrier signals

from the local oscillator DTO1 with 90 degrees phase shift

are applied. The frequency is dependent on the present

colour standard.

The multiplier operates as a quadrature demodulator for all

PAL and NTSC signals; it operates as a frequency down

mixer for SECAM signals.

The two multiplier output signals are converted to a serial

UV data stream and applied to two low-pass filter stages,

then to a gain controlled amplifier. A final multiplexed

low-pass filter achieves, together with the preceding

stages, the required bandwidth performance.

The PAL and NTSC originated signals are applied to a

comb filter.

The signal originated from SECAM is fed through a Cloche

filter (0 Hz centre frequency), a phase demodulator and a

differentiator to obtain frequency demodulated colour

difference signals. The SECAM signal is fed after

de-emphasis to a cross-over switch, to provide both the

serial transmitted colour difference signals. These signals

are fed to the BCS control and finally to the output fomatter

stage and to the output interface.

controlled

ADC input level

0 dB

MGC823

1995 Oct 18 10

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

9.4 Luminance processing (see Fig.7)

The 8-bit luminance signal, a digital CVBS format or a

luminance format (S-VHS, HI8), is fed through a

switchable prefilter. High frequency components are

emphasized to compensate for loss. The following

chrominance trap filter (fc= 4.43 or 3.58 MHz centre

frequency selectable) eliminates most of the colour carrier

signal, therefore, it must be bypassed for S-Video (S-VHS,

HI8) signals.

The high frequency components of the luminance signal

can be peaked (control for sharpness improvement via

I2C-bus) in two bandpass filters with selectable transfer

characteristics.

A coring circuit with selectable characteristics improves

the signal once more. This signal is then added to the

original (unpeaked) signal. A switchable amplifier achieves

common DC amplification, because the DC gains are

different in both chrominance trap modes.

The improved luminance signal is fed via the variable

delay to the BCS control and the output interface.

9.5 YUV-bus (digital outputs)

The 16-bit YUV-bus transfers digital data from the output

interfaces to a feature box, or a field memory, a digital

colour space converter (SAA 7192 DCSC) or a video

enhancement and digital-to-analog processor (SAA7165

VEDA2). The outputs are controlled by an output enable

FEIN on pin 63).

chain (

The YUV data rate equals LLC2. Timing is achieved by

marking each second positive rising edge of the clock LLC

in conjunction with CREF (clock reference).

The synchronization pulses are sliced and fed to the phase

detectors where they are compared with the sub-divided

clock frequency. The resulting output signal is applied to

the loop filter to accumulate all phase deviations.

Adjustable output signals HCL and HSY are generated in

accordance with analog front end requirements. The

output signals HS, VS, and PLIN are locked to the timing

reference, guaranteed between the input signal and the

HREF signal, as further improvements to the circuit may

change the total processing delay. It is therefore not

recommended to use them for applications which require

absolute timing accuracy to the input signals. The loop

filter signal drives an oscillator to generate the line

frequency control signal LFCO.

9.7 Clock generation circuit

The internal CGC generates all clock signals required for

the one chip front-end. The output signal LFCO is a

digital-to-analog converted signal provided by the

horizontal PLL. It is the multiple of the line frequency

(7.38 MHz = 472 × f

6.14 MHz = 360 × fh in 60 Hz systems). Internally the

LFCO signal is multiplied by a factor of 2 or 4 in the PLL

circuit (including phase detector, loop filtering, VCO and

frequency divider) to obtain the LLC and LLC2 output clock

signals. The rectangular output clocks have a 50% duty

factor.

It is also possible to operate the OCF1 with an external

CGC (SAA7197) providing the signals LLC and CREF.

The selection of the internal/external CGC will be

controlled by the CGCE input signal.

9.8 Power-on reset

in 50 Hz systems and

h

The output signals Y7 to Y0 are the bits of the digital

luminance signal. The output signals UV7 to UV0 are the

bits of multiplexed colour difference signals (B−Y) and

(R−Y). The frame in the format tables is the time, required

to transfer a full set of samples. In the event of 4 :2:2

format two luminance samples are transmitted in

comparison to one U and one V sample within the frame.

The time frames are controlled by the HREF signal.

Fast enable is achieved by setting inputFEIN to LOW. The

signal is used to control fast switching on the digital

YUV-bus. HIGH on this pin forces the Y and UV outputs to

a high-impedance state.

9.6 Synchronization (see Fig.7)

The pre-filtered luminance signal is fed to the

synchronization stage. It's bandwidth is reduced to 1 MHz

in a low-pass filter.

1995 Oct 18 11

Power-on reset is activated at power-on (using only

internal CGC), when the supply voltage decreases below

3.5 V. The indicator output

RESET signal can be applied to reset other circuits of the

digital TV system.

9.9 RTCO output

The real time control and status output signal contains

serial information about actual system clock, subcarrier

frequency and PAL/SECAM sequence. The signal can be

used for various applications in external circuits, for

example, in a digital encoder to achieve clean encoding.

RESET is LOW for a time. The

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

AOUT

23

MGC824

TEST

SELECTOR

SWITCH

BYPASS

FILTER

ANTI-ALIAS

ANALOG

AMPLIFIER

CLAMP

CIRCUIT

AOSL

FUSE

REFS4AINS4

ADC

FAST

ADDER

SWITCH

SWITCH

BYPASS

FILTER

ANTI-ALIAS

ANALOG

AMPLIFIER

CLAMP

CIRCUIT

FUSE

REFS3

ADC

FAST

ADDER

SWITCH

SWITCH

BYPASS

FILTER

ANTI-ALIAS

ANALOG

AMPLIFIER

CLAMP

CIRCUIT

FUSE

GAS2

GAS3

IVAL

WISL

GAD2

WVAL

REFS2

GAD3

WRSE

WIRS

GUDL

FAST

SWITCH

CONTROL

VERTICAL

CONTROL

BLANKING

CONTROL

ANTI-ALIAS

GAIN

CONTROL

CLAMP

CONTROL

GAI2

GACO

HOLD

GLIM

WIPA

CLL2n

MX24

MX34

MS24

MUYC

VBPS

VBPR

GAI3

WIPE

CLL3n

MUD1

MS34

VBCO

IWIP

GAI4

SBOT

MUD2

IGAI

GASL

CROSS

TWO2

TWO3

YSEL

CSEL

MULTIPLEXER

handbook, full pagewidth

Fig.5 Analog input processing and analog control part.

AINS2

AIND2

20, 16, 12

18, 14, 10

SSA4

DDA4

to V

to V

SSA2

DDA2

V

V

SOURCE

11

13

AI42

SWITCH

AI41

AIND4

SOURCE

15

17

AI32

SWITCH

AI31

AINS3

AIND3

SWITCH

SOURCE

19

21

AI22

AI21

1995 Oct 18 12

ANALOG

CONTROL

CLS2

CLTS

987

i.c.

CLS3

CLS4

i.c.

22

i.c.

SS(S)

V

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

Y7 to Y0

UV7 to UV0

FEIN

63

(MUXC)

62

55 to

53, 54

45 to 50,

HREF

42

MGC825

OUTPUT

FORMATTER

AND INTERFACE

GAIN

CONTROL

LOW-PASS LOW-PASS

QUADRATURE

DEMODULATOR

HRFS

SQPB

HRMV

OFTS

CHSB

OEYC

OEHV

CLOCH FILTER

PI2

LOOPFILTER

LFIS

CKTS

CKTQ

CHCV

(DTO1)

OSCILLATOR

AND DIVIDER

DISCRETE TIME

CONTROL

CONTRAST

SATURATION

BRIGHTNESS

AND SECAM

COMB FILTERS

RECOMBINATION

PHASE

DETECTOR

AMPLITUDE

DEMODULATOR

BURST GATE

ACCUMULATOR

PI1

LOOP FILTER

BRIG

SEQA

SEQA

SATN

CONT

DIFFERENTIATOR

SEQUENCE

DE-EMPHASIS

STANDARD

COLO

ALTD

PROCESSOR

SXCRCODE

handbook, full pagewidth

CONTROL

SECS

Fig.6 Multi-standard decoder part.

HUEC

BANDPASS

CHROMINANCE

INPUT

INTERFACE

BYPS

CHRS

34, 27

68, 52, 44,

DD

V

1995 Oct 18 13

PLSE

SESE

35, 28

67, 51, 43,

SS

V

CHROMINANCE CIRCUIT

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

DELAY

VARIABLE

AND

WEIGHTING

ADDING STAGE

CORING

FILTER

VARIABLE

BANDPASS

BFBY

PREF

RESET

32

CONTROL

POWER-ON

AMPLIFIER

MATCHING

BPSS

CREF

LLC

29

31

CLOCK

CLOCK(3 to 0)

LINE-LOCKED

DELAY

LOOP FILTER

PHASE

DETECTOR

LLC2

30

GENERATOR

ADJUSTMENT

2

HPLL

HLCK

COARSE

XTALI

65

66

CLOCK

CRYSTAL

OSCILLATOR

DISCRETE TIME

HLCK

VTRC

XTALO

GENERATOR

(DTO2)

FIDT

LFCO

26

DAC4

DAC6

CLOCK

CIRCUIT

GENERATION

VNOI

FSEI

AUFD

VERTICAL

PROCESSOR

4137 38 39 40 25 24 333

MGC826

CGCEODD (VL)

SSA0

V

DDA0

V

handbook, full pagewidth

FINE

PHASE

DETECTOR

TRAP

CHROMINANCE

SYNC

SLICER

LUMINANCE CIRCUIT

PREFILTER

PREF BYPS CORI APER YDEL

2

AP

BLOCK

CONTROL

1

SP

SYNC

PREFILTER

TEST

1995 Oct 18 14

COUNTER

STTC

HLCK

IDEL

HSYB

HSYS

HCLB

HCLS

HPHI

HS6B

HS6S

HC6B

HC6S

PULIO

OEHV

SYNCHRONIZATION CIRCUIT

VBLKA

C-BUS

2

I

CONTROL

SSTB

GPSW

C-BUS

2

I

INTERFACE

64

GPSW

(VBLK)

HP6I

SCEN

36

456

RTCO

HSY

HCL HS VS

SA SCL SDA

PLIN (HL)

Fig.7 Luminance and synchronization part.

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

10 GAIN CHARTS

handbook, full pagewidth

NO BLANKING ACTIVE

CLAA = 1

10

<

CCL

CLAU = 1 CLAU = 0

+ CLAMP − CLAMP + GAIN − GAIN − GAIN SLOW + GAINNO CLAMP

CLAU = clamp up.

VBLK = vertical blanking pulse.

WIPE = white peak level (adjustable).

SBOT = sync bottom level (adjustable).

CLL = clamp level (adjustable).

CLAA = clamp active.

HSY = horizontal sync pulse.

HCL = horizontal clamp pulse.

10

HCL

ANALOG IN

ADC

10

VBLK

<− CLAMP GAIN −>

10

CLAA = 0

10 10

>

SBOT

HSY

> WIPE

MGC827

Fig.8 Clamp and gain flow chart.

1995 Oct 18 15

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

handbook, full pagewidth

0

no action

WRSE

0

+4/F

analog input

amplifier

anti-alias amplifier

ADC8

1

VBLK

1

>WIPE

0

1

−

IVAL

0

1

1

1

WIRS

+4/L

MSB

2

LSB

0

X

1

<SBOT<SBOT

+IVAL −WVAL

6

decoder input

0

1

0

HSY

0

1

>WIPE

X = 1X = 0

0

STOP

X = system variable (start with logic 0).

Y = IAGV-FGVI > GUDL.

VBLK = vertical blanking pulse.

HSY = horizontal sync pulse.

SBOT = sync bottom level (adjustable).

WIPE = white peak level (adjustable).

IVAL = integration value gain (adjustable).

WVAL = integration value WIPE (adjustable).

IGAI = integration factor gain (adjustable).

IWIP = integration factor WIPE (adjustable).

AGV = actual gain value.

FGV = frozen gain value.

GUDL = gain update level (adjustable).

WRSE = white peak reset enable.

WIRS = white peak reset select.

L = line.

F = field.

*IWIP *IGAI *IWIP

gain accumulator (20 bits)

actual gain value 8-bit (AGV) [−3/+6 dB]

1

AGV

0

X

1

gain value 8-bit

HSY

update

0

1

Fig.9 Luminance AGC flow chart.

+/− 0

0

Y

FGV

MGC828

1995 Oct 18 16

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

11 LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134); all ground pins and all supply pins connected

together.

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

DDA

V

DDD

V

I(A)

V

I(D)

V

diff

T

stg

T

amb

T

amb(bias)

P

tot

V

esd

analog supply voltage −0.5 +7.0 V

digital supply voltage −0.5 +7.0 V

analog input voltage −0.5 +7.0 V

digital input voltage −0.5 +7.0 V

voltage difference between V

SSAall

and V

SSall

− 100 mV

storage temperature −65 +150 °C

operating ambient temperature 0 70 °C

operating ambient temperature under bias −10 +80 °C

total power dissipation V

DDA=VDDD

= 7 V; note 1 − 2.5 W

electrostatic discharge all pins note 2 −2000 +2000 V

Note

1. Compare with typical total power consumption in Chapter “Characteristics”.

2. Equivalent to discharging a 100 pF capacitor through a 1.5 kΩ series resistor.

12 CHARACTERISTICS

V

DDD

=5V; V

DDA

=5V; T

=25°C; unless otherwise specified.

amb

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Supplies

V

DDA

V

DDD

I

DDA(tot)

I

DDD(tot)

P

tot

analog supply voltage 4.75 5.0 5.25 V

digital supply voltage 4.5 5.0 5.5 V

total analog supply current −−150 mA

total digital supply current −−250 mA

total power dissipation − 1.2 1.7 W

Analog part

I

clamp

V

i(p-p)

clamping current VI= 1.25 V DC −2 − +2 µA

input voltage (peak-to-peak

C

= 10 nF 0.5 1.0 1.38 V

couple

value), AC coupling required

input impedance clamping current off 200 −− kΩ

Z

i

C

i

α

ct

input capacitance −−10 pF

channel crosstalk fi< 5 MHz −−50 − dB

Analog-to-digital converters

B analog bandwidth at −3dB − 15 − MHz

φ

diff

G

diff

f

LLC

DLE DC differential linearity error −

differential phase amplifier + AAF = bypass − 2 − deg

differential gain amplifier + AAF = bypass − 2 − %

ADC clock rate 11 − 16 MHz

1

⁄

2

− LSB

ILE DC integral linearity error − 1 − LSB

1995 Oct 18 17

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Digital inputs

V

IL

LOW level input voltage

SDA and SCL

V

IH

HIGH level input voltage

SDA and SCL

V

IL(clk)

LOW level input voltage for

clocks

V

IH(clk)

HIGH level input voltage for

clocks

V

IH(XTALI)

V

IL(n)

HIGH level input voltage XTALI 3.0 − VDD+ 0.5 V

LOW level input voltage all other

inputs

V

IH(n)

HIGH level input voltage all other

inputs

I

LI

C

i(clk)

C

i(I/O)

C

i(n)

input leakage current −−10 µA

input capacitance for clocks −−10 pF

input capacitance I/Os at high impedance −−8pF

input capacitance all other inputs −−8pF

Digital outputs

V

LFCO

LFCO output voltage

(peak-to-peak value)

V

OL

V

OH

V

OL(clk)

LOW level output voltage note 2 0 − 0.6 V

HIGH level output voltage note 2 2.4 − V

LOW level output voltage for

clocks

V

OH(clk)

HIGH level output voltage for

clocks

note 1 1.4 − 2.6 V

−0.5 − +1.5 V

3.0 − VDD+ 0.5 V

−0.5 − +0.6 V

2.4 − VDD+ 0.5 V

−0.5 − +0.8 V

2.0 − VDD+ 0.5 V

DD

−0.5 − +0.6 V

2.6 − VDD+ 0.5 V

V

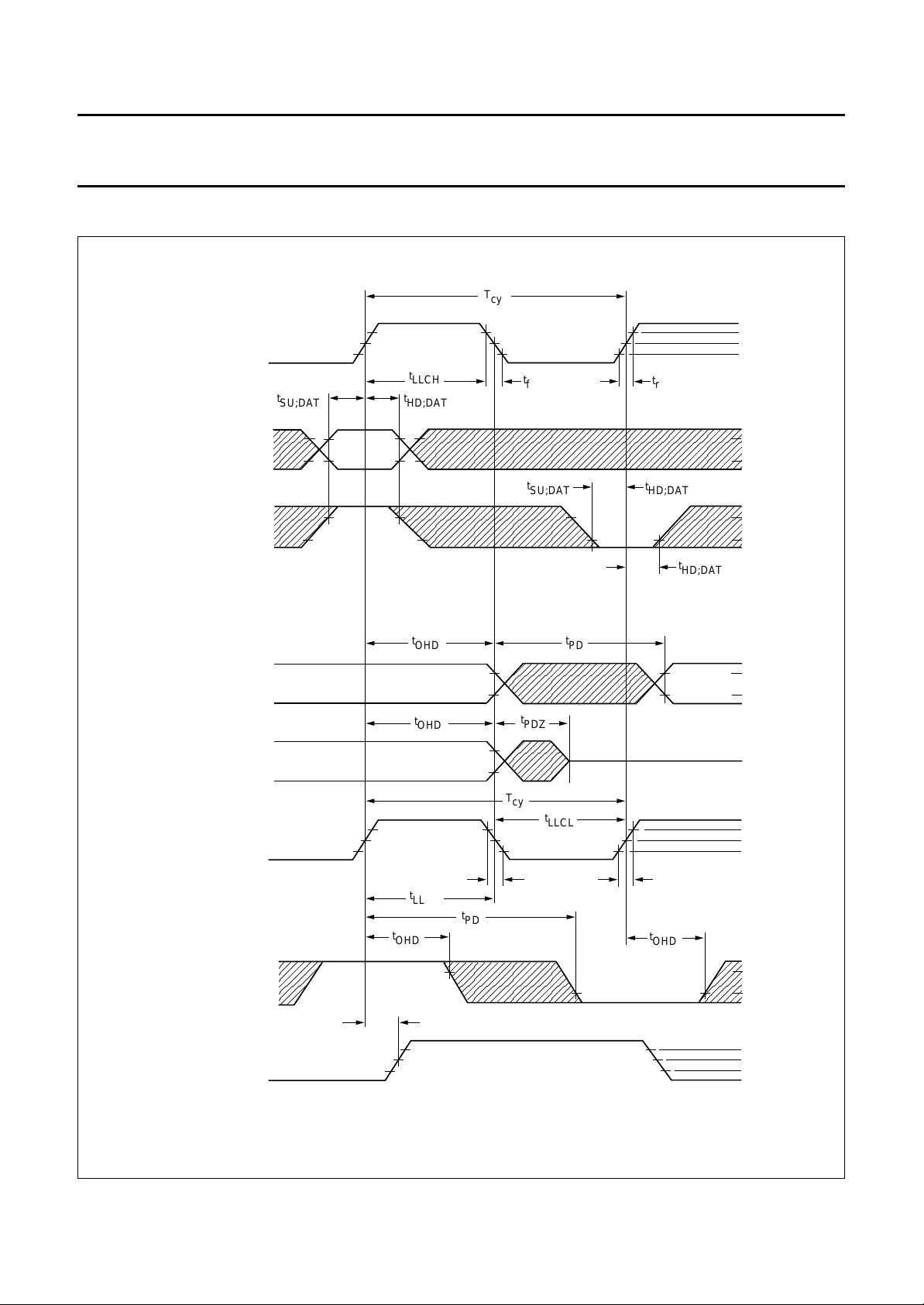

Clock input timing (LLC)

T

cy

δ duty factor for t

t

r

t

f

cycle time 31 − 45 ns

LLCH/Tcy

rise time Vi= 0.6 to 2.4 V −−5ns

fall time Vi= 2.4 to 0.6 V −−5ns

Control and CREF input timing (note 3)

t

SU;DAT

t

HD;DAT

t

HD;FEIN

t

HD;OTHER

input data set-up time 11 −− ns

input data hold time 3 −− ns

input data hold time for FEIN 3 −− ns

input data hold time all other

note 3 6 −− ns

inputs

1995 Oct 18 18

40 − 60 %

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Data and control output timing (note 4)

C

L(data)

output load capacitance

(data, HREF and VS)

C

L(control)

t

HD;DAT

t

PD(data)

output load capacitance (control) 7.5 − 25 pF

output data hold time CL=15pF 13 −− ns

propagation delay from negative

edge of LLC (data, HREF and

VS)

t

PD(control)

propagation delay from negative

edge of LLC (control)

t

PD(Z))

propagation delay from negative

edge of LLC (to 3-state)

Clock output timing (LLC and LLC2)

C

L(LLC)

T

cy

δ duty factors for t

t

r

t

f

t

d

output load capacitance 15 − 40 pF

cycle time LLC 31.5 − 45 ns

LLCH/tLLC

t

LLC2H/tLLC2

rise time 0.6 to 2.6 V −−5ns

fall time 2.6 to 0.6 V −−5ns

delay time LLC output to LLC2

output

Data qualifier output timing (CREF)

t

HD;CREF

t

PD;CREF

output hold time CL=15pF 4 −− ns

propagation delay from positive

edge of LLC

and

CL=50pF −−29 ns

CL=25pF −−29 ns

note 5 −−15 ns

LLC2 63 − 90 ns

Vi= 1.5 V;

C

LLC/LLC2

= 40 pF; note 6

CL=40pF −−20 ns

15 − 50 pF

40 − 60 %

−−8ns

Horizontal PLL

f

Hnom

nominal line frequency 50 Hz field − 15625 − Hz

60 Hz field − 15734 − Hz

∆f

H/fHnom

permissible static deviation 50 Hz field −−5.6 %

60 Hz field −−6.7 %

Subcarrier PLL

f

Hnom

nominal subcarrier frequency PAL − 4433618 − Hz

NTSC − 3579545 − Hz

∆fH/f

Hnom

lock-in range 400 −− Hz

1995 Oct 18 19

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Crystal oscillator

f

n

∆f/f

n

∆T/f

n

CRYSTAL SPECIFICATION (X1); note 7

T

amb

C

L

R

s

C1 motional capacitance − 1.1 ±20% − fF

C0 parallel capacitance − 3.5 ±20% − pF

Notes

1. The LFCO output level must be measured with a load circuit of 10 kΩ in parallel with 15 pF.

2. The levels must be measured with load circuits, the loads depend on the type of output stage. Control outputs (except

HREF and VS); 1.2 kΩ at 3 V (TTL load); CL= 25 pF: data outputs (plus HREF and VS); 1.2 kΩ at 3 V (TTL load);

CL=50pF.

3. Other control input signals are CGCE, VS, SA, HCL and HSY.

4. Data output signals are YUV (15 to 0). Control output signals are HREF, VS, HS, HSY, HCL, RTCO, PLIN (HL),

ODD (VL) and GPSW0 (VBLK). The effects of rise and fall times are included in the calculation of t

t

PDZ

5. The minimum propagation delay from 3-state to data active related to falling edge of LLC is 0 ns.

6. LLC2 is not active while CGCE = 0.

7. Philips catalogue number 9922 520 30004.

nominal frequency 3rd harmonic − 26.8 − MHz

permissible frequency deviation −50 × 10−6− +50 × 10

permissible frequency deviation

−20 × 10−6− +20 × 10

with temperature

operating ambient temperature 0 − 70 °C

load capacitance 8 −− pF

series resonance resistance − 50 80 Ω

HD;DAT

. Timings and levels refer to drawings and conditions illustrated in Fig.10.

−6

−6

, tPD and

Table 1 Processing delay

FUNCTION

TYPICAL ANALOG DELAY

AI21 TO ADCIN (AOUT) (ns)

Without amplifier or anti-alias filter 10

With amplifier, without anti-alias filter 30

With amplifier plus anti-alias filter (50 Hz) 30 + 40

With amplifier plus anti-alias filter (60 Hz) 30 + 50

1995 Oct 18 20

DIGITAL DELAY

ADCIN (AOUT) TO YUVOUT

(1/LLC)

(YDEL = 0; CAD2/3 = 1)

248

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

13 TIMING

T

handbook, full pagewidth

CLOCK INPUT LLC

t

SU;DAT

t

LLCH

t

HD;DAT

cy

2.4 V

1.5 V

0.6 V

t

f

t

r

INPUTS CONTROL

INPUT CREF

OUTPUTS YUV, HREF, VS AND HS

OUTPUTS YUV (to 3-state)

CLOCK OUTPUT LLC

t

OHD

t

OHD

t

OHD

t

LLCH

2.0 V

0.8 V

t

SU;DAT

t

PD

t

PDZ

T

cy

t

LLCL

t

f

t

PD

t

HD;DAT

t

r

t

OHD

t

HD;DAT

2.0 V

0.8 V

2.4 V

0.6 V

2.6 V

1.5 V

0.6 V

OUTPUT CREF

t

dLLC2

CLOCK OUTPUT LLC2

Fig.10 Clock/data timing.

1995 Oct 18 21

MGC829

2.4 V

0.6 V

2.6 V

1.5 V

0.6 V

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

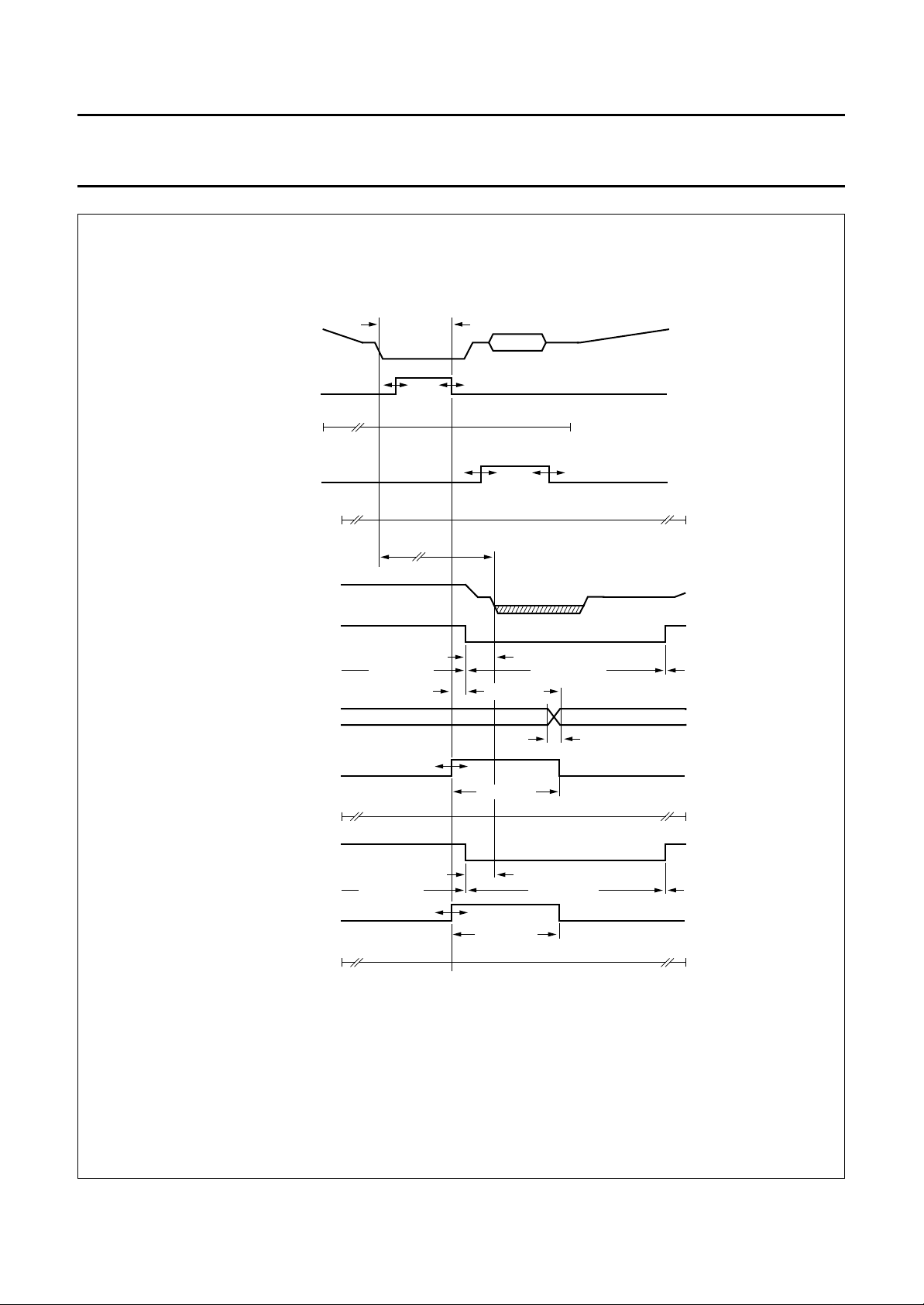

handbook, full pagewidth

CVBS

HSY

HSY

programming range

(step size: 2/LLC)

HCL

HCL

programming range

(step size: 2/LLC)

Y output

HREF (50 Hz)

PLIN (50 Hz)

HS (50 Hz)

+191

+127

62 × 2/LLC

768 × 2/LLC

30 × 2/LLC

0

burst

−64

processing delay CVBS−>YUV

18 × 2/LLC

176 × 2/LLC

94 × 2/LLC

4/LLC

−128

(1)

HS (50 Hz)

programming range

(step size: 8/LLC)

HREF (60 Hz)

HS (60 Hz)

HS (60 Hz)

programming range

(step size: 8/LLC)

(1) See Table 1.

HRMV = 1 and HRFS = 0.

+117

+97

0

640 × 2/LLC

0

Fig.11 Horizontal timing.

1995 Oct 18 22

64 × 2/LLC

−118

18 × 2/LLC

140 × 2/LLC

64 × 2/LLC

−97

MGC830

Philips Semiconductors Product specification

One Chip Front-end 1 (OCF1) SAA7110; SAA7110A

handbook, full pagewidth

LL27

CREF

INTERNAL

BUS CLOCK

HREF

Yn

UVn

HREF

Yn

(50 Hz)

UVn

START OF ACTIVE LINE

01234

U0 V0 U1 V1 U2

ONE BUS CYCLE

END OF ACTIVE LINE

767766765764763

U766 V766V764U764V762

Yn

(60 Hz)

UVn

V636U636V634

Fig.12 HREF timing.

1995 Oct 18 23

639638637636635

U638 V638

MGC831

Loading...

Loading...