Philips saa6579 DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

SAA6579

Radio Data System (RDS)

demodulator

Product specification

Supersedes data of January 1994

File under Integrated Circuits, IC01

1997 Feb 24

Philips Semiconductors Product specification

Radio Data System (RDS) demodulator SAA6579

FEATURES

• Anti-aliasing filter (2nd order)

• Integrated 57 kHz band-pass filter (8th order)

• Reconstruction filter (2nd order)

• Clocked comparator with automatic offset compensation

• 57 kHz carrier regeneration

• Synchronous demodulator for 57 kHz modulated RDS

signals

GENERAL DESCRIPTION

The integrated CMOS circuit SAA6579 is an RDS

demodulator. It recovers the additional inaudible RDS

information which is transmitted by FM radio broadcasting.

The data signal RDDA and the clock signal RDCL are

provided as outputs for further processing by a suitable

decoder (microcomputer).

The operational functions of the device are in accordance

with the

“CENELEC EN 50067”

.

• Selectable 4.332/8.664 MHz crystal oscillator with

variable dividers

• Clock regeneration with lock on biphase data rate

• Biphase symbol decoder with integrate and dump

functions

• Differential decoder

• Signal quality detector

• Subcarrier output.

QUICK REFERENCE DATA

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

V

DDA

V

DDD

I

tot

V

i(rms)

V

OH

V

OL

T

amb

analog supply voltage (pin 5) 3.6 5.0 5.5 V

digital supply voltage (pin 12) 3.6 5.0 5.5 V

total supply current − 6 − mA

RDS input amplitude (RMS value; pin 4) 1 −−mV

HIGH level output voltage for signals RDDA, RDCL, QUAL and T57 4.4 −−V

LOW level output voltage for signals RDDA, RDCL, QUAL and T57 −−0.4 V

operating ambient temperature −40 − +85 °C

ORDERING INFORMATION

TYPE

NUMBER

NAME DESCRIPTION VERSION

PACKAGE

SAA6579 DIP16 plastic dual in-line package; 16 leads (300 mil); long body SOT38-1

SAA6579T SO16 plastic small outline package; 16 leads; body width 7.5 mm SOT162-1

1997 Feb 24 2

Philips Semiconductors Product specification

Radio Data System (RDS) demodulator SAA6579

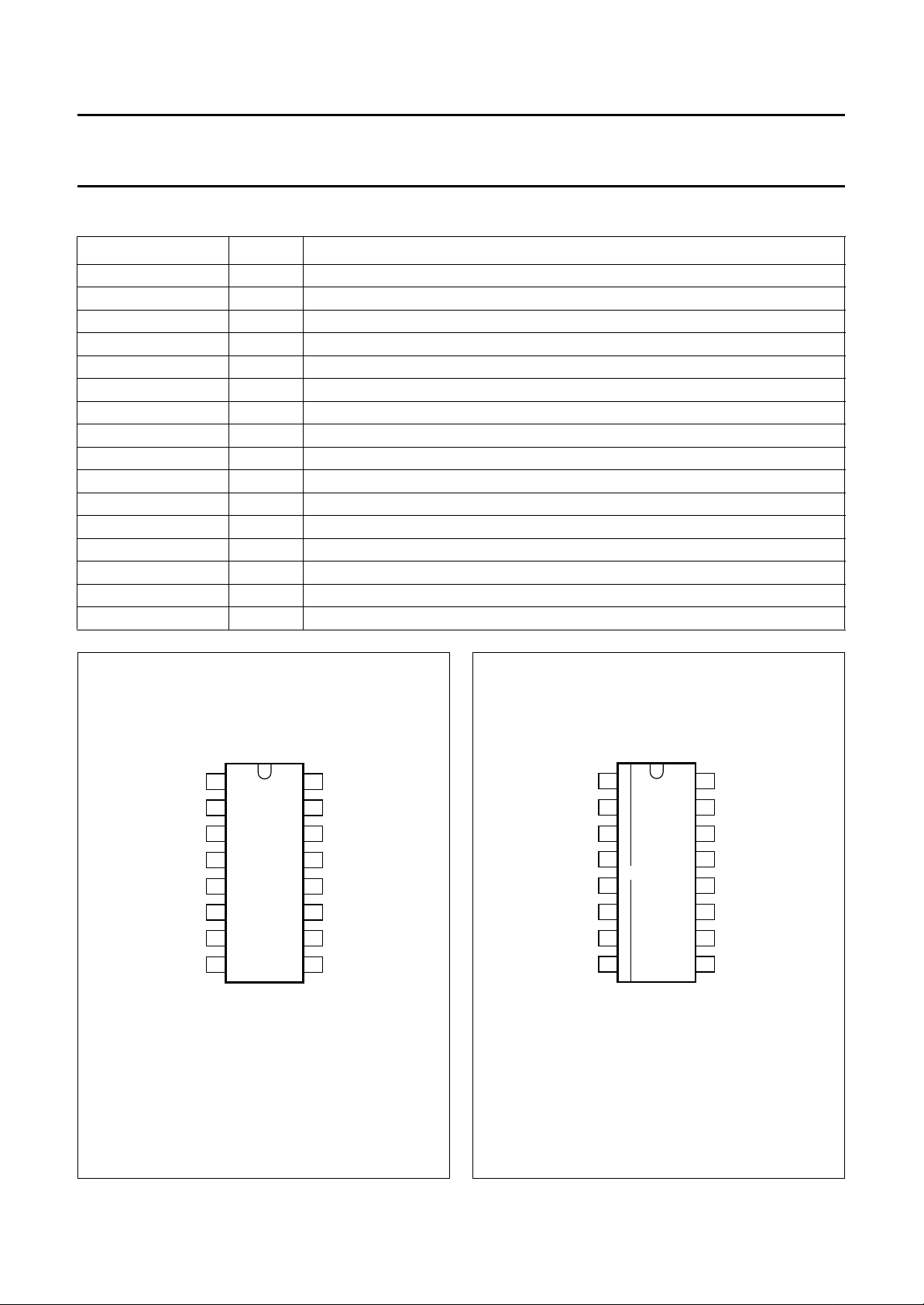

BLOCK DIAGRAM

handbook, full pagewidth

47 pF

4.332/8.664 MHz

82 pF

2.2 k

+5 V

Ω

0.1 µF

MPX

signal

+5 V

2.2 µF

330 pF

SCOUT

560 pF

V

0.1 µF

MUX

CIN

DDA

V

ref

4

ALIASING

FILTER

8

7

CLOCKED

COMPARATOR

5

3

REFERENCE

VOLTAGE

ANTI-

OSCOOSCI

57 kHz

BANDPASS

(8th ORDER)

COSTAS LOOP

VARIABLE AND

FIXED DIVIDER

RECONSTRUCTION

FILTER

13

OSCILLATOR

DIVIDER

BIPHASE

SYMBOL

DECODER

14

AND

SAA6579

V

P1

CLOCK

REGENERATION

AND SYNC

6

V

SSA

TEST LOGIC AND OUTPUT

SELECTOR SWITCH

9

MODE TEST

10

V

DDD

12

QUALITY BIT

GENERATOR

DIFFERENTIAL

DECODER

11

V

SSD

QUAL

1

RDDA

2

RDCL

16

T57

15

MEH162

Via pin MODE two different crystal frequencies can be used.

MODE CRYSTAL CLOCK

LOW 4.332 MHz

HIGH 8.664 MHz

Fig.1 Block diagram and application circuit.

1997 Feb 24 3

Philips Semiconductors Product specification

Radio Data System (RDS) demodulator SAA6579

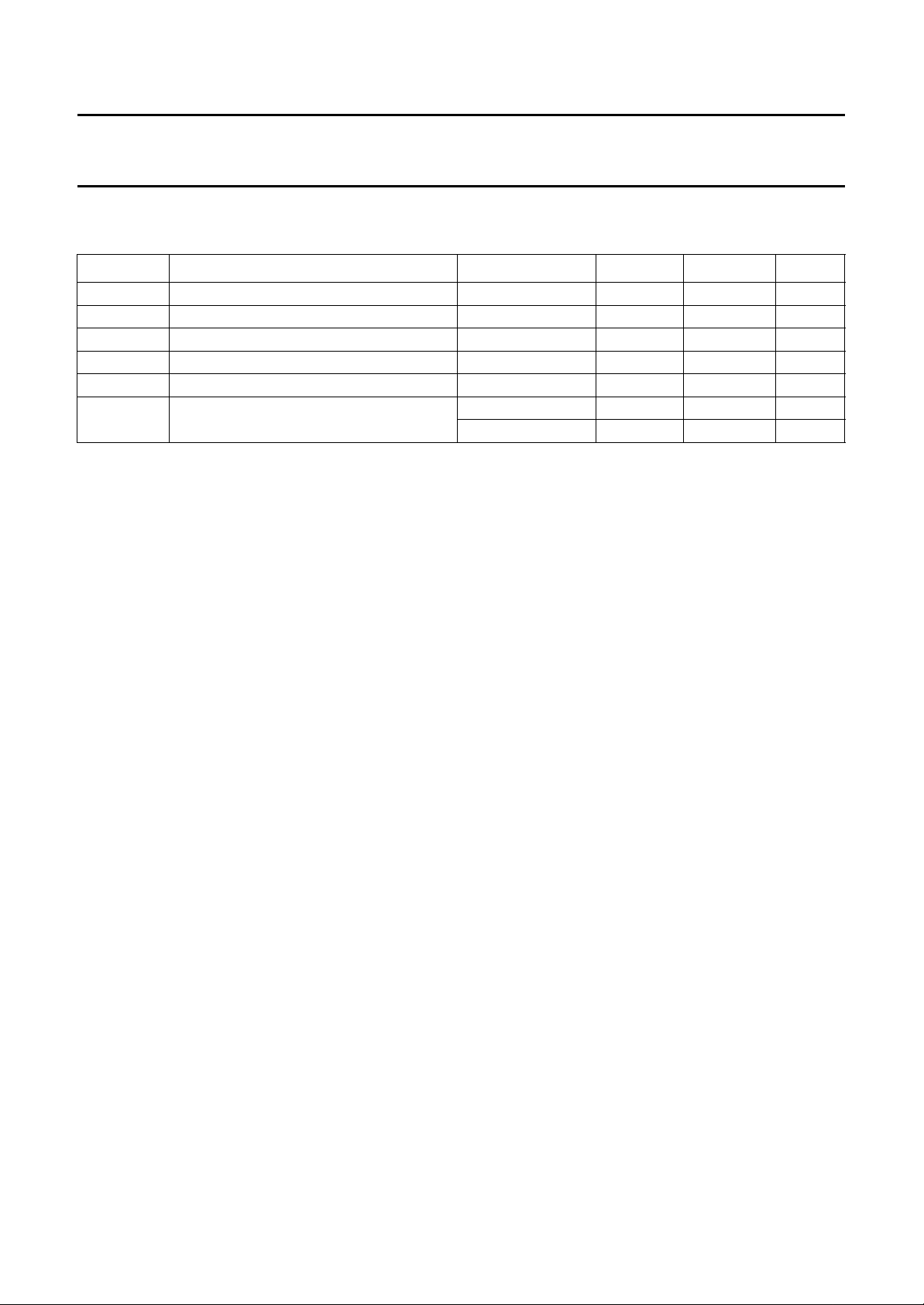

PINNING

SYMBOL PIN DESCRIPTION

QUAL 1 quality indication output

RDDA 2 RDS data output

V

ref

3 reference voltage output (0.5V

MUX 4 multiplex signal input

V

V

DDA

SSA

5 +5 V supply voltage for analog part

6 ground for analog part (0 V)

CIN 7 subcarrier input to comparator

SCOUT 8 subcarrier output of reconstruction filter

MODE 9 oscillator mode/test control input

TEST 10 test enable input

V

V

SSD

DDD

11 ground for digital part (0 V)

12 +5 V supply voltage for digital part

OSCI 13 oscillator input

OSCO 14 oscillator output

T57 15 57 kHz clock signal output

RDCL 16 RDS clock output

DDA

)

handbook, halfpage

QUAL

RDDA

V

ref

MUX

V

DDA

V

SSA

CIN

SCOUT

1

2

3

4

5

6

7

8

SAA6579

MGD684

16

15

14

13

12

11

10

9

RDCL

T57

OSCO

OSCI

V

DDD

V

SSD

TEST

MODE

Fig.2 Pin configuration. Fig.3 Pin configuration.

1997 Feb 24 4

handbook, halfpage

QUAL

RDDA

V

ref

MUX

V

DDA

V

SSA

CIN

SCOUT

1

2

3

4

SAA6579T

5

6

7

8

MGD685

16

15

14

13

12

11

10

9

RDCL

T57

OSCO

OSCI

V

DDD

V

SSD

TEST

MODE

Philips Semiconductors Product specification

Radio Data System (RDS) demodulator SAA6579

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134); ground pins 6 and 11 connected together.

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

DDA

V

DDD

V

n

T

stg

T

amb

V

es

Notes

1. Equivalent to discharging a 200 pF capacitor via a 0 Ω series resistor.

2. Equivalent to discharging a 100 pF capacitor via a 1.5 kΩ series resistor.

analog supply voltage (pin 5) 0 6 V

digital supply voltage (pin 12) 0 6 V

voltage on all pins; grounds excluded −0.5 V

+ 0.5 V

DDX

storage temperature −40 +150 °C

operating ambient temperature −40 +85 °C

electrostatic handling for all pins except

pins 9 and 10

note 1 ±300 − V

note 2 +1500 −3000 V

FUNCTIONAL DESCRIPTION

The SAA6579 is a demodulator circuit for RDS

applications. It contains a 57 kHz bandpass filter and a

digital demodulator to regenerate the RDS data stream out

of the multiplex signal (MPX).

Filter part

The MUX signal is band-limited by a second-order

anti-aliasing-filter and fed through a 57 kHz band-pass

filter (8th order band-pass filter with 3 kHz bandwidth) to

separate the RDS signals. This filter uses switched

capacitor technique and is clocked by a clock frequency of

541.5 kHz derived from the 4.332/8.664 MHz crystal

oscillator. Then the signal is fed to the reconstruction filter

to smooth the sampled and filtered RDS signal before it is

output on pin 8. The signal is AC-coupled to the

comparator (pin 7). The comparator is clocked with a

frequency of 228 kHz (synchronized by the 57 kHz of the

demodulator).

Digital part

The synchronous demodulator (Costas loop circuit) with

carrier regeneration demodulates the internal coupled,

digitized signal. The suppressed carrier is recovered from

the two sidebands (Costas loop). The demodulated signal

is low-pass-filtered in such a way that the overall pulse

shape (transmitter and receiver) approaches a

cosinusoidal form in conjunction with the following

Integrate and dump circuit.

The data-spectrum shaping is split into two equal parts and

handled in the transmitter and in the receiver. Ideally, the

data filtering should be equal in both of these parts.

The overall data-channel-spectrum shaping of the

transmitter and the receiver is approximately 100% roll-off.

The Integrate and dump circuit performs an integration

over a clock period. This results in a demodulated and

valid RDS signal in form of biphase symbols being output

from the integrate and dump circuit. The final stages of

RDS data processing are the biphase symbol decoding

and the differential decoding. After synchronization by

data clock RDCL (pin 16) data appears on the RDDA

output (pin 2). The output of the biphase symbol decoder

is evaluated by a special circuit to provide an indication of

good data (QUAL = HIGH) or corrupt data (QUAL = LOW).

Timing

Fixed and variable dividers are applied to the

4.332/8.664 MHz crystal oscillator to generate the

1.1875 kHz RDS clock RDCL, which is synchronized by

the incoming data. Which ever clock edge is considered

(positive or negative going edge) the data will remain valid

for 399 µs after the clock transition. The timing of data

change is 4 µs before a clock change. Which clock

transition (positive or negative going clock) the data

change occurs in, depends on the lock conditions and is

arbitrary (bit slip).

During poor reception it is possible that faults in phase

occur, then the clock signal stays uninterrupted, and data

is constant for 1.5 clock periods. Normally, faults in phase

do not occur on a cyclic basis. If however, faults in phase

occur in this way, the minimum spacing between two

possible faults in phase depends on the data being

transmitted. The minimum spacing cannot be less than

16 clock periods. The quality bit changes only at the time

of a data change.

1997 Feb 24 5

Loading...

Loading...