Philips saa5233 DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

SAA5233

Dual standard PDC decoder

Objective specification

File under Integrated Circuits, IC02

Philips Semiconductors

June 1994

Philips Semiconductors Objective specification

Dual standard PDC decoder SAA5233

FEATURES

• Digital data slicer

• Acquisition and decoding of VPS data

(EBU PDC System A)

• Acquisition and decoding of Teletext packet 8/30/2 data

(EBU PDC System B)

• Separate storage of VPS data and packet 8/30/2

allowing dual standard PDC decoders

• I2C-bus interface with automatic word address

increment

• Programmable interrupt for data received

• Programmable error level detection

• Single +5 V power supply.

GENERAL DESCRIPTION

The SAA5233 is a dual standard Program Delivery Control

(PDC) decoder, allowing the reception and decoding of

both VPS data (EBU PDC System A) and Teletext packet

8/30/2 data (EBU PDC System B). It is intended for use in

European video recorders which are manually

programmed, so that they receive broadcast real time

switching signals for accurate timing of program recording.

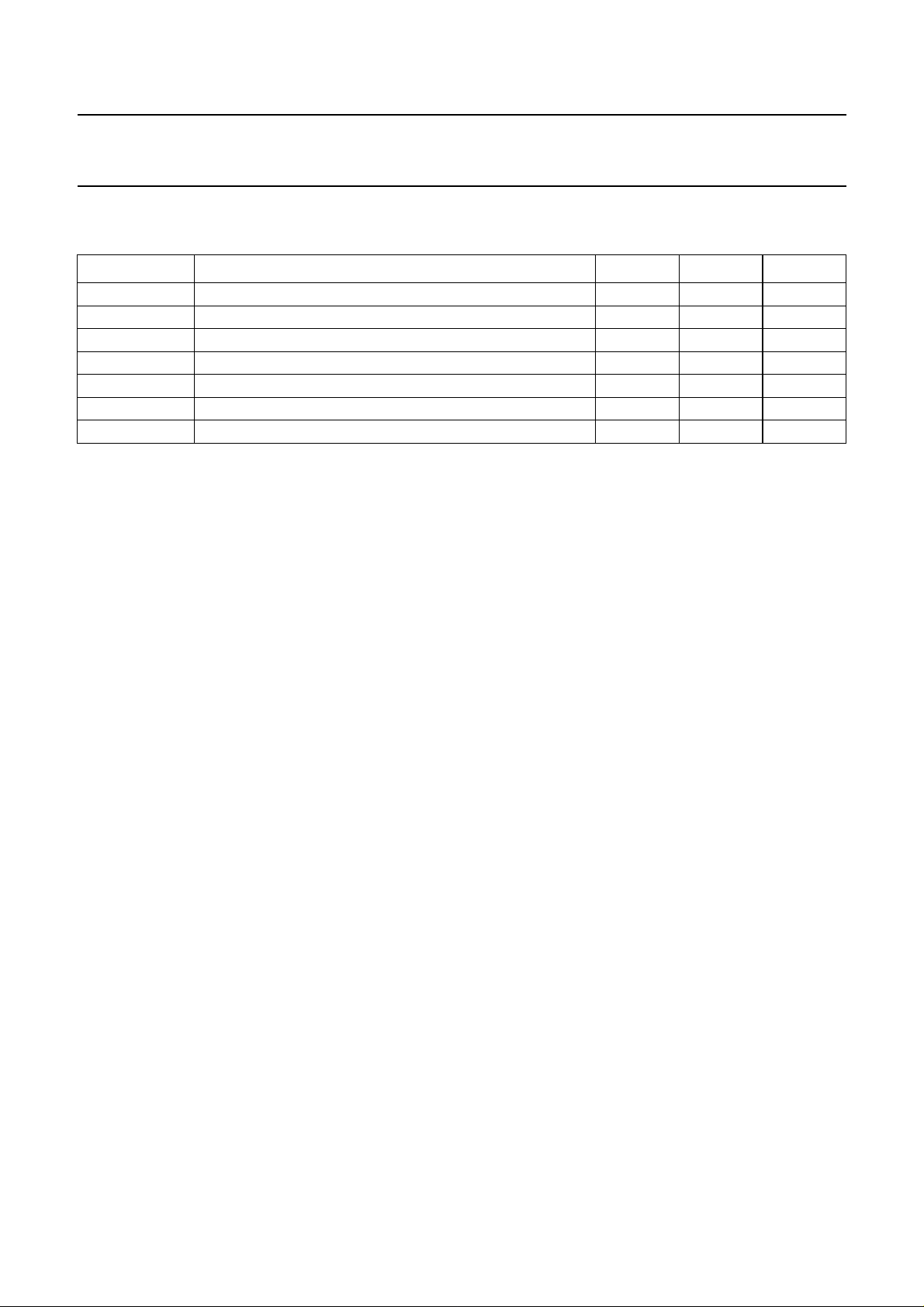

QUICK REFERENCE DATA

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

V

DD

I

DD

f

clk

V

sync

V

vid(p-p)

supply voltage 4.5 5.0 5.5 V

supply current − 30 45 mA

crystal input frequency − 27 − MHz

CVBS sync voltage amplitude 0.1 0.3 0.6 V

CVBS video voltage amplitude

0.7 1.0 1.4 V

(peak-to-peak value)

T

amb

T

stg

operating ambient temperature −20 − +70 °C

storage temperature −55 − +125 °C

ORDERING INFORMATION

PACKAGE

TYPE NUMBER

PINS PIN POSITION MATERIAL CODE

SAA5233P 16 DIP16 plastic SOT38-1

SAA5233T 20 SO20L plastic SOT163-1

June 1994 2

Philips Semiconductors Objective specification

Dual standard PDC decoder SAA5233

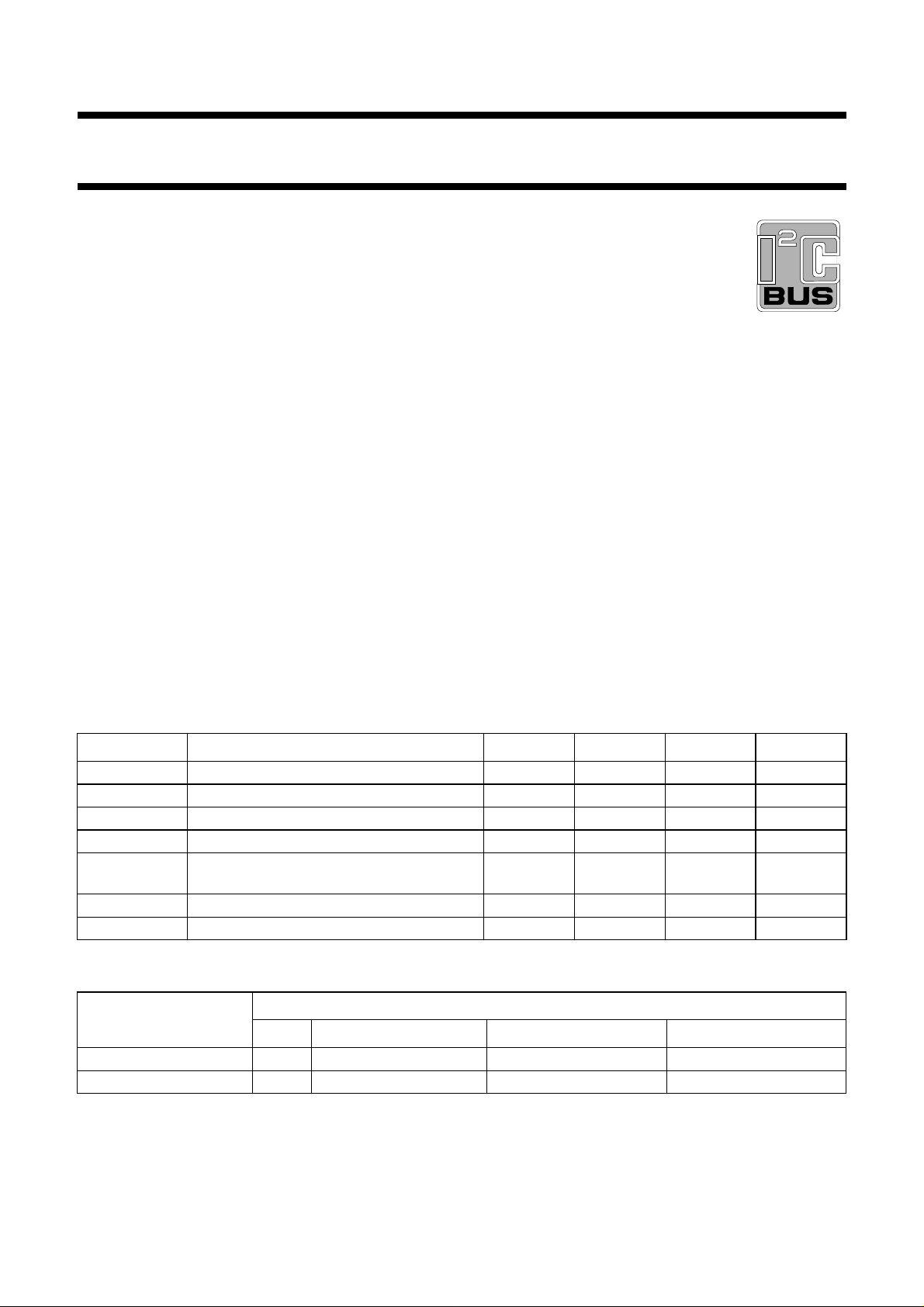

BLOCK DIAGRAM

SCL SDA

handbook, full pagewidth

V

V

V

V

V

INT

V

SS1

SS2

SS3

SS4

SS5

AD

DD

14

15

4

5

9

10

11

16

27 MHz

POWER

ON RESET

13.5 MHz

1.125 MHz

27 MHz

OSCILLATOR

AND DIVIDER

12 13

2

I C BUS

INTERFACE

INTERRUPT

CONTROL

TELETEXT

AND VPS

CONTROL

DATA SLICER

AND CLOCK

REGENERATOR

ANALOGUE

TO DIGITAL

CONVERTER

MEMORY

INTERFACE

AND RAM

SAA5233

8/30/2

ACQUISITION

AND

DECODING

VPS

ACQUISITION

AND

DECODING

PLL AND

TIMING

INPUT

CLAMP

AND SYNC

SEPARATOR

OSCOUT OSCIN OSCGND CVBS BLACK IREF

Fig.1 Block diagram; pin numbers for DIP16.

June 1994 3

321876

MLB725

Philips Semiconductors Objective specification

Dual standard PDC decoder SAA5233

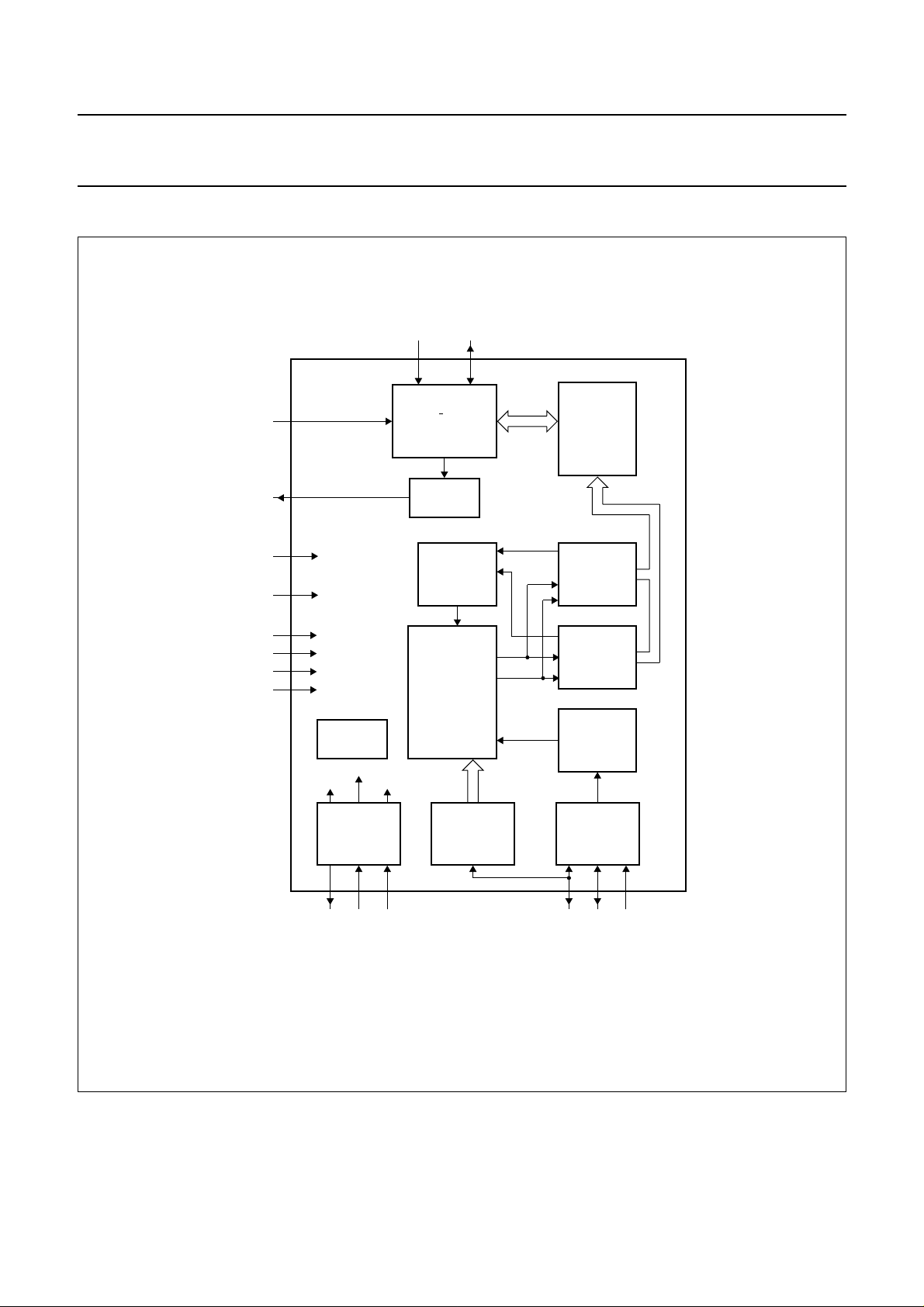

PINNING

SYMBOL

DESCRIPTION

DIP16 SO20L

CVBS 1 1 composite video input

BLACK 2 2 video black level storage pin

n.c. − 3 not connected

IREF 3 4 reference current input

PIN

V

DD

V

SS1

4 5 +5 V supply

5 6 0 V ground 1 (main ground pin)

OSCOUT 6 7 27 MHz crystal oscillator output

n.c. − 8 not connected

OSCIN 7 9 27 MHz crystal oscillator input

OSCGND 8 10 27 MHz crystal oscillator ground

V

SS2

V

SS3

9 11 0 V ground 2; connect to V

10 12 0 V ground 3; connect to V

SS1

SS1

n.c. − 13 not connected

V

SS4

SCL 12 15 serial clock open-drain input for I

SDA 13 16 serial data open-drain input/output for I

11 14 connect to V

in normal operation

SS1

2

C-bus

2

C-bus

i.c. − 17 internally connected; do not connect in normal operation

AD 14 18 programmable I2C-bus address bit input

INT 15 19 interrupt open-drain output

V

SS5

16 20 connect to V

in normal operation

SS1

handbook, halfpage

CVBS

BLACK

IREF

V

DD

V

SS1

OSCOUT

OSCIN

OSCGND

1

2

3

4

SAA5233

5

6

7

8

MLB726

V

16

SS5

15

INT

14

AD

13

SDA

12

SCL

V

11

SS4

V

10

SS3

V

9

SS2

Fig.2 Pin configuration; DIP16.

June 1994 4

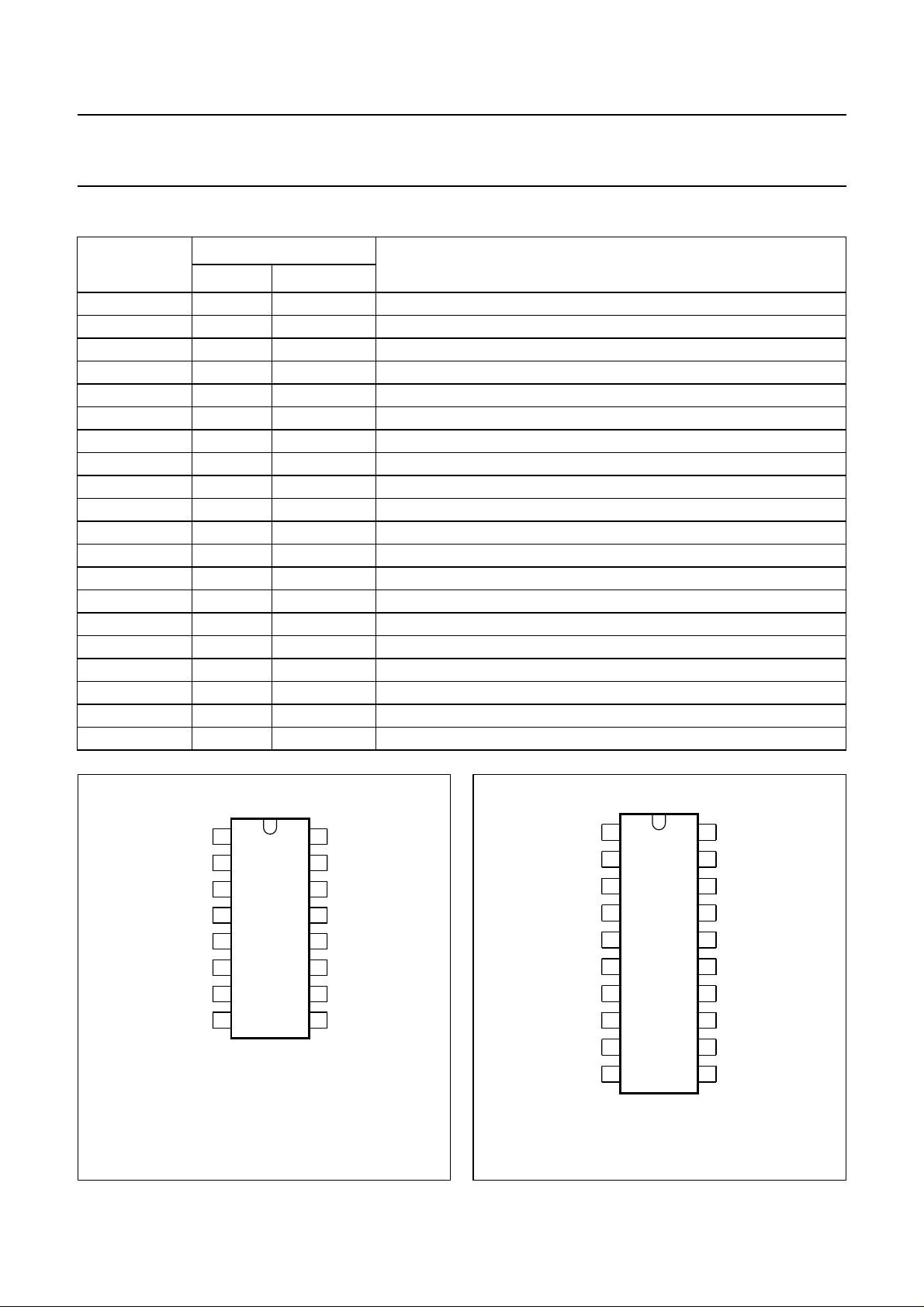

handbook, halfpage

OSCOUT

OSCGND

1

CVBS

BLACK

OSCIN

2

3

n.c.

4

V

5

DD

V

SS1

n.c. n.c.

SAA5233

6

7

8

9

10

MLB727

20

19

18

17

16

15

14

13

12

11

V

SS5

INT

AD

i.c.IREF

SDA

SCL

V

SS4

V

SS3

V

SS2

Fig.3 Pin configuration; SO20L.

Philips Semiconductors Objective specification

Dual standard PDC decoder SAA5233

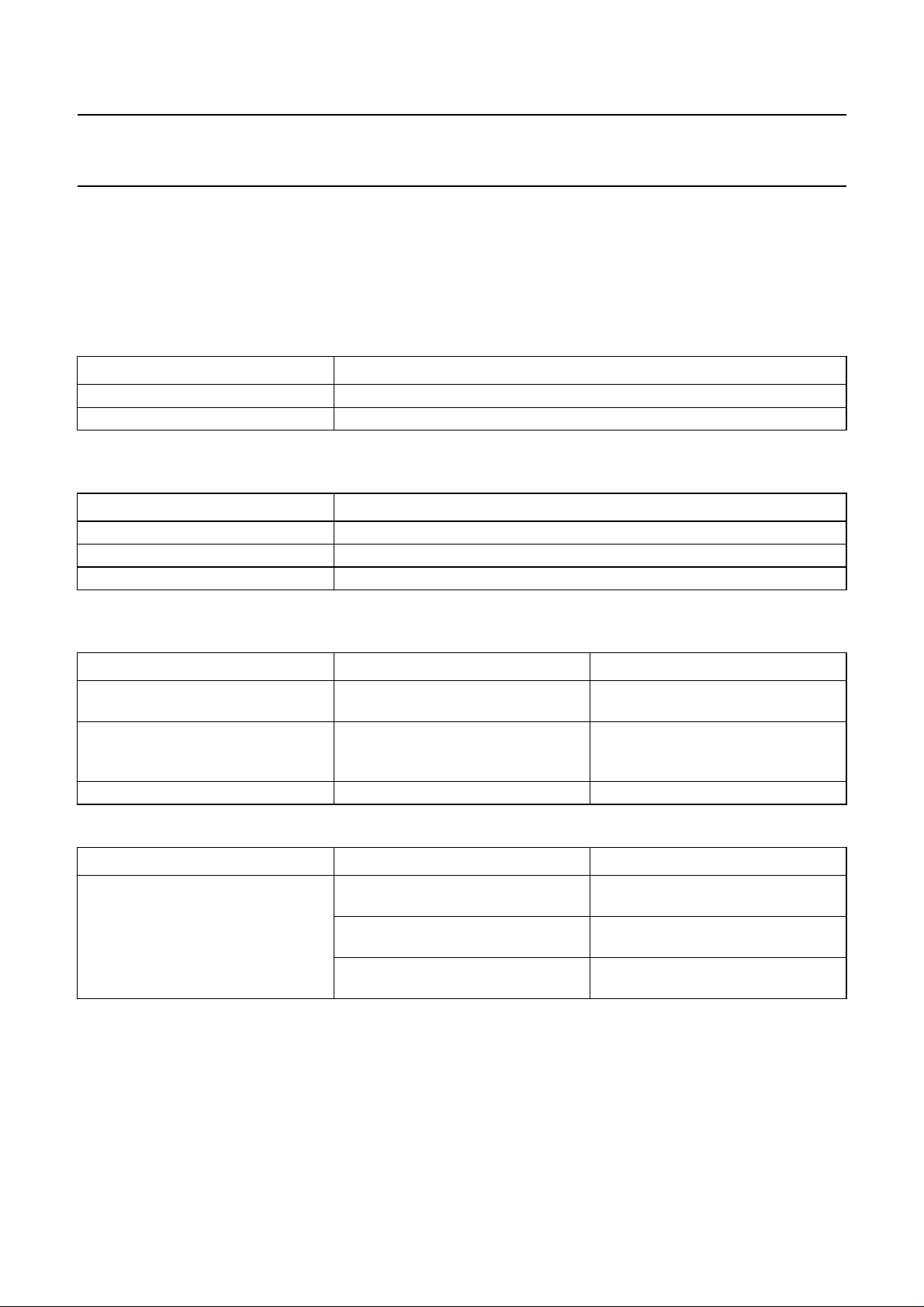

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

SYMBOL PARAMETER MIN. MAX. UNIT

V

DD

V

Imax

V

Omax

I

IOmax

I

Omax

T

amb

T

stg

supply voltage −0.3 +6.5 V

maximum input voltage (any input) −0.3 VDD+ 0.3 V

maximum output voltage (any output) −0.3 VDD+ 0.3 V

maximum DC input or output diode current −±20 mA

maximum output current (any output) −±10 mA

operating ambient temperature −20 +70 °C

storage temperature −55 +125 °C

June 1994 5

Philips Semiconductors Objective specification

Dual standard PDC decoder SAA5233

QUALITY AND RELIABILITY

This device will meet the requirements of the

accordance with

“Quality Reference Pocketbook (order number 9398 510 34011)”

“Philips Semiconductors General Quality Specification SNW-FQ-611E”

. The principal requirements are as

shown in Tables 1 to 4.

Group A

Table 1 Acceptance tests per lot.

TEST REQUIREMENTS

(1)

Mechanical cumulative target: <100 ppm

Electrical cumulative target: <100 ppm

Group B

Table 2 Processability tests (by package family).

TEST REQUIREMENTS

(1)

Solderability <7% LTPD

Mechanical <15% LTPD

Solder heat resistance <15% LTPD

Group C

Table 3 Reliability tests (by process family).

TEST CONDITIONS REQUIREMENTS

(1)

Operational life 168 hours at Tj= 150 °C <1500 FPM; equivalent to <100 FITS

at Tj=70°C

Humidity life temperature, humidity, bias

<2000 FPM

(1000 hours, 85 °C, 85% RH or

equivalent test)

Temperature cycling performance T

stg(min)

to T

stg(max)

<2000 FPM

in

Table 4 Reliability tests (by device type).

TEST CONDITIONS REQUIREMENTS

ESD and latch-up ESD Human body model

2000 V; 100 pF; 1.5 kΩ

ESD Machine model

200 V; 200 pF; 0 Ω

latch-up 100 mA; 1.5 × V

DD

(absolute maximum)

Note to Tables 1 to 4.

1. ppm = fraction of defective devices, in parts per million.

LTPD = Lot Tolerance Percent Defective.

FPM = fraction of devices failing at test condition, in Failures Per Million.

FITS = Failures In Time Standard.

June 1994 6

(1)

<15% LTPD

<15% LTPD

<15% LTPD

Loading...

Loading...