Philips SAA5191 Datasheet

INTEGRATED CIRCUITS

DATA SH EET

SAA5191

Teletext video processor

Preliminary specification

File under Integrated Circuits, IC02

March 1991

Philips Semiconductors Preliminary specification

Teletext video processor SAA5191

FEATURES

• Adaptive data slicer

• Crystal-controlled data clock regeneration with a bit rate

of 6.9375 MHz

• Adaptive sync separator, horizontal phase detector and

13.5 MHz VCO to provide display phase locked loop

(PLL)

GENERAL DESCRIPTION

The SAA5191 is a bipolar integrated circuit that extracts

teletext data from the video signal (CVBS), regenerates

the teletext clock (TTC) and synchronizes the text display

to the television signals (VCS). This device operates in

conjunction with the Digital Video Teletext (back-end)

Decoder (DVTB - SAA9042A) or any other compatible

device.

• TV synchronization at teletext mode

QUICK REFERENCE DATA

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

V

P

I

P

V

i CVBS

supply voltage (pin 16) − 12 − V

supply current − 70 − mA

CVBS input signal on pin 27 (peak-to-peak value)

at pin 2 LOW − 1 − V

at pin 2 open-circuit − 2.5 − V

V

o

outputs signals TTC and TTD

2.5 3.5 4.5 V

(peak-to-peak value, pins 14, 15)

V

F13

13.5 MHz clock output signal

123V

(peak-to-peak value pin 17)

V

SYNC

video sync output signal (peak-to-peak value, pin 1) −−1V

SYNC output signal

TCS 200 450 650 mV

VCS video composite sync level on output pin 25

LOW −−0.4 V

HIGH 2.4 − 5.5 V

T

amb

operating ambient temperature 0 −+70 °C

ORDERING AND PACKAGE INFORMATION

EXTENDED TYPE

NUMBER

PINS PIN POSITION MATERIAL CODE

PACKAGE

SAA5191 28 DIL plastic SOT117

Note

1. SOT117-1;1996 November 14

March 1991 2

(1)

Philips Semiconductors Preliminary specification

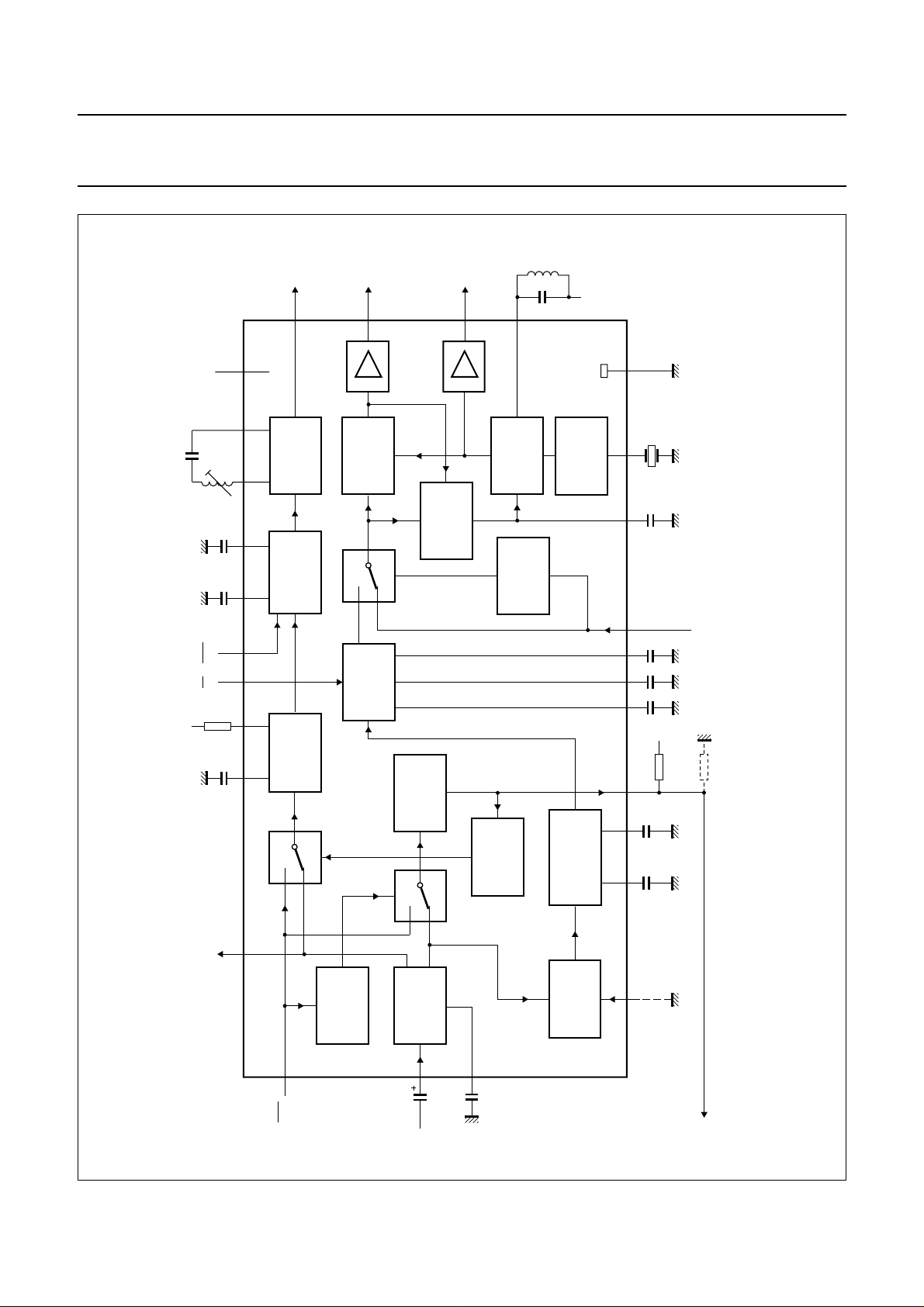

Teletext video processor SAA5191

P

(data)

F13

(13.5 MHz

clock)

17

+12 V

P

V

TTD

15

TTC

14

(clock)

12

V

1311978651432

GND

XTAL

MEH149

13.875 MHz

handbook, full pagewidth

VCO

19

PHASE

DETECTOR

HORIZONTAL

PL CBB

P

V

PULSE

GENERATOR

LATCHES

DATA

SLICER

ADAPTIVE

SAA5191

CLOCK

DUAL

BUFFER

POLARITY

PHASE

DETECTOR

PHASE

SENSE

SENSE

"NO LOAD"

SHIFTER

DATA

EXTERNAL

BY 2

DIVIDER

OSCILLATOR

HF LOSS

COMPENSATOR

data

P

V

input

polarity

set sync

Fig.1 Block diagram.

25 24 23 22 10 21 20 18 16

VCS

ADAPTIVE

27

composite

video

input

SYNC

SEPARATOR

28

TCS

SENSE

"NO INPUT"

March 1991 3

set video

input level

GAIN

SWITCH

26

sync output

Loading...

Loading...