INTEGRATED CIRCUITS

DATA SH EET

SAA4997H

VErtical Reconstruction IC (VERIC)

for PALplus

Preliminary specification

File under Integrated Circuits, IC02

1996 Oct 24

Philips Semiconductors Preliminary specification

VErtical Reconstruction IC (VERIC) for

SAA4997H

PALplus

FEATURES

• PALplus decoding

• Vertical reconstruction

• Quadrature mirror filter

• Luminance and chrominance processing

• Controlling.

QUICK REFERENCE DATA

SYMBOL PARAMETER MIN. MAX. UNIT

V

DD

T

amb

ORDERING INFORMATION

TYPE

NUMBER

SAA4997H QFP64

supply voltage − 5.25 V

operating ambient temperature 0 70 °C

NAME DESCRIPTION VERSION

plastic quad flat package; 64 leads (lead length 1.95 mm); body 14 × 20 × 2.8 mm SOT319-2

GENERAL DESCRIPTION

The VErtical Reconstruction IC (VERIC) for PALplus

(VERIC) is especially designed for use in conjunction with

the Motion Adaptive Colour Plus And Control IC

(MACPACIC) to decode the transmitted PALplus video

signal in PALplus colour TV receivers. It provides the full

vertical resolution of a PALplus picture from the letter box

part and the decoded helper information.

PACKAGE

1996 Oct 24 2

Philips Semiconductors Preliminary specification

VErtical Reconstruction IC (VERIC) for

PALplus

BLOCK DIAGRAMS

Y_VE_0 to 7

8

36

CLK_32B3

23

CLK_16B2

SAA4997H

UV

F/C

U/V_VE_0/1

4

FORMATTER

bypass

OE_FM2

RSTR_FM23

39

56

54

multi-PIP

OE_FM3

RE_FM2

40

55

TRSTN

TDO_VE

RE_FM3

30

29

BOUNDARY SCAN TEST

28 26 27

SAA4997H

MGE443

handbook, full pagewidth

mode select

F/C

LUMINANCE

(QM-FILTER)

PROCESSING

PIXEL

SELECT

8

multi-PIP

bypass

DELAY

COMPENSATOR

8

8

(LP-FILTER)

PROCESSING

CHROMINANCE

8

8

UV

REFORMATTER

PIXEL

SELECT

4

4

19

5

FM-control

UV-control

Y - UV - FM

Y-control

LINE COUNTER

CONTROL LOGIC

DECODER

PIXEL COUNTER

17

Fig.1 Block diagram.

EVEN_FIELD TDI TCK TMS

INTPOL

21 20 22

FILM

DECODER

Y_FM23_0 to 7

U/V_FM23_0/1

1996 Oct 24 3

VA_AI

HREF_MA

Philips Semiconductors Preliminary specification

VErtical Reconstruction IC (VERIC) for

PALplus

Vertical

VERIC

Reconstruction IC

CLK_32B1

U_FM23_0,1

V_FM23_0,1

Y_FM23_0 to 7

4

8

8

4

FM2

TMS4C2970

V_VE_[0,1]

U_VE_[0,1]

8

4

V_VE_0,1

U_VE_0,1

Y_VE_0 to 7 Y_VE_[0 to 7]

8

4

FM3

TMS4C2970

TDO_VE

4

4

DD1-4

V

V

CLK_32B3

OE_FM3

OE_FM2

- Inverse QMF

reconstruction

SS1-4

CLK_16B2

CLK_32B3

RE_FM2

RE_FM3

RSTR_FM23

filter- Vertical

chrominance

FILM

VA_AI

HREF_MA

SRC- FM2/FM3

read control

TDI

TRSTN

INTPOL

EVEN_FIELD

TMS

3

TCK

SAA4997H

MGE444

11

NC

TEST1-3

ok, full pagewidth

CLK_16B1, 2, 3

3

3

MACPACIC

and Control IC

Motion Adaptive Colour Plus

Y_ADC_0 to 7

8

4

8

CLK_32B1, 2, 3

8

Y_FM1_0 to 7

8

TMS4C2970

8

4

U_MA_0,1

Y_MA_0 to 7

U_FM1_0,1

V_FM1_0,1

4

SRCK

FM1

SWCK

4

8

V_MA_0,1

U_ADC_0,1

4

CLK_16 CLK_16B1

(1)

(1)

Y_TO_FM1_0 to 7

U_TO_FM1_0

WE_FM2

U_TO_FM1_1

RSTW_FM23

- BB-decompanding

- Motion adaptive

V_ADC_0,1

5

5

SS1-5

DD1-5

V

V

CLK_16

CLK_32

(1)

WE_FM3

V_TO_FM1_1

V_TO_FM1_0

WE_FM1, RE_FM1

2

luminance/chrominance

separation

- Memory control

CLAMP

VA_FRONT

WE_FRONT

VA_AI

WE_FM4, RE_FM4

RST_FM14

2

- PALplus control

- Clock generation

SNERT_CL

SNERT_DA

SNERT_RST

HREF_MA

WE_MA

FILM

EVEN_FIELD

INTPOL

- Sync generation

- SNERT interface

3

TDI

TCK

TMS

TRSTN

TEST1-3

TDO_MA

4

V_FM4_0,1

U_FM4_0,1

4

V_TO_FM4_0,1

U_TO_FM4_0,1

(2)

VERIC_AV_N

CLK_16B1

FM4

TMS4C2970

Fig.2 Block diagram of the PALplus decoder module.

.

SS

Y_FRONT[0 to 7]

V_FRONT[0,1]

U_FRONT[0,1]

1996 Oct 24 4

(1) In case of stand alone MACPACIC the output signals are U_TO_FM1_1, V_TO_FM1_0 or V_TO_FM1_1; otherwise the output signals are WE_FM2, RSTW_FM23 or WE_FM3.

(2) VERIC available: VERIC_AV_N is connected to V

Philips Semiconductors Preliminary specification

VErtical Reconstruction IC (VERIC) for

SAA4997H

PALplus

PINNING

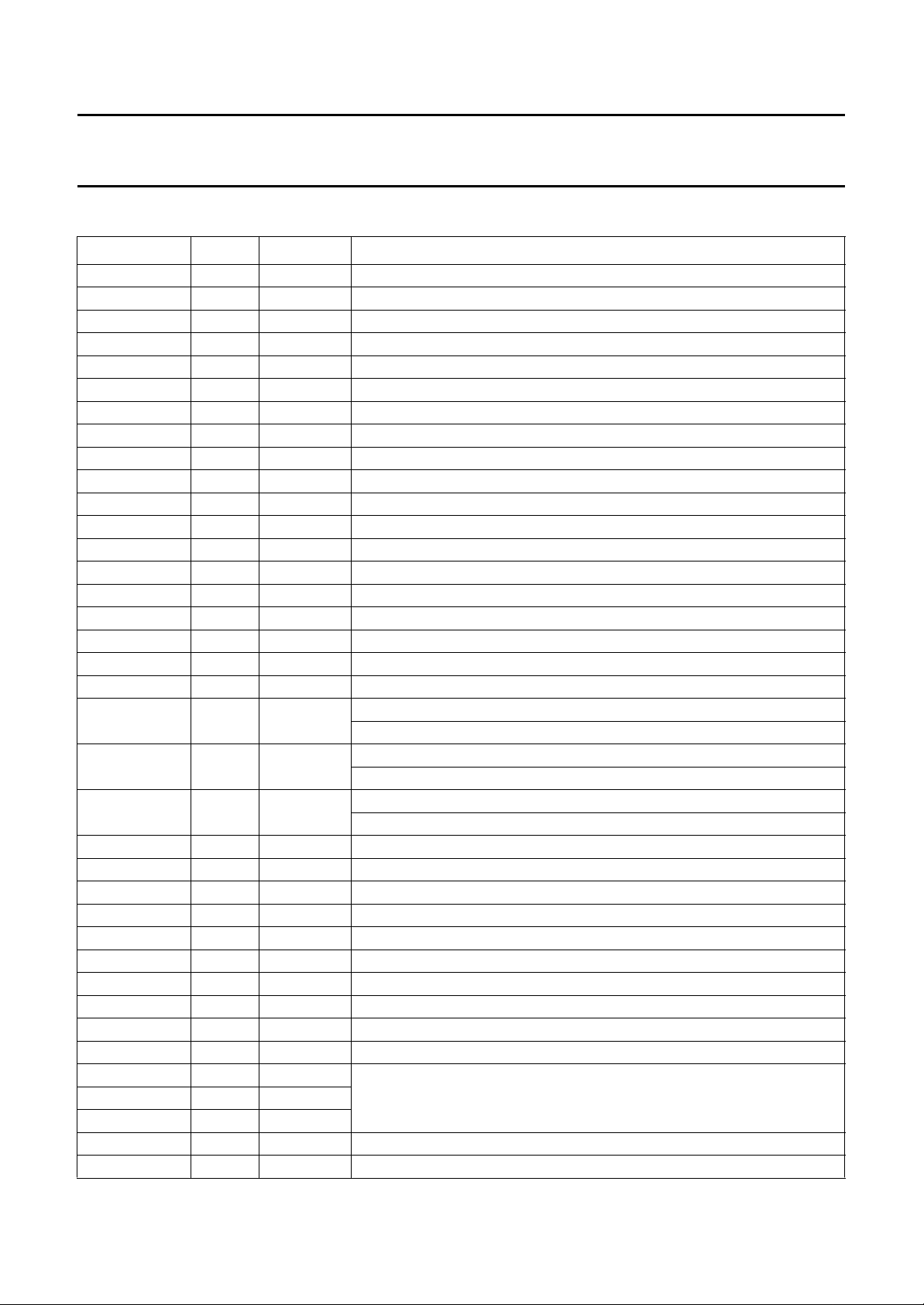

SYMBOL PIN TYPE DESCRIPTION

Y_VE_1 1 output luminance output data bit 1

Y_VE_0 2 output luminance output data bit 0

U_VE_1 3 output chrominance output data bit 1 U-component

U_VE_0 4 output chrominance output data bit 0 U-component

V_VE_1 5 output chrominance output data bit 1 V-component

V_VE_0 6 output chrominance output data bit 0 V-component

V

SS1

V

DD1

n.c. 9 − not connected

n.c. 10 − not connected

n.c. 11 − not connected

n.c. 12 − not connected

n.c. 13 − not connected

n.c. 14 − not connected

n.c. 15 − not connected

n.c. 16 − not connected

HREF_MA 17 input horizontal reference

n.c. 18 − not connected

VA_AI 19 input vertical reference pulse related to output data

INTPOL 20 input INTPOL = 1: PALplus interpolation active

FILM 21 input FILM = 0: CAMERA mode

EVEN_FIELD 22 input EVEN_FIELD = 0: odd field related to MACPACIC input data

CLK_16B2 23 input buffered clock input (16 MHz)

V

SS2

V

DD2

TCK 26 input boundary scan test clock input

TMS 27 input boundary scan test mode select input

TDI 28 input boundary scan test data input

TDO_VE 29 output boundary scan test data output

TRSTN 30 input boundary scan test reset input

n.c. 31 − not connected

n.c. 32 − not connected

TEST1 33 tbf test pins

TEST2 34 tbf

TEST3 35 tbf

CLK_32B3 36 input buffered clock input (32 MHz)

V

SS3

7 input ground 1

8 input positive supply voltage 1 (+5 V)

INTPOL = 0: VERIC switched to bypass mode (standard signal)

FILM = 1: FILM mode

EVEN_FIELD = 1: even field related to MACPACIC input data

24 input ground 2

25 input positive supply voltage 2 (+5 V)

37 input ground 3

1996 Oct 24 5

Philips Semiconductors Preliminary specification

VErtical Reconstruction IC (VERIC) for

PALplus

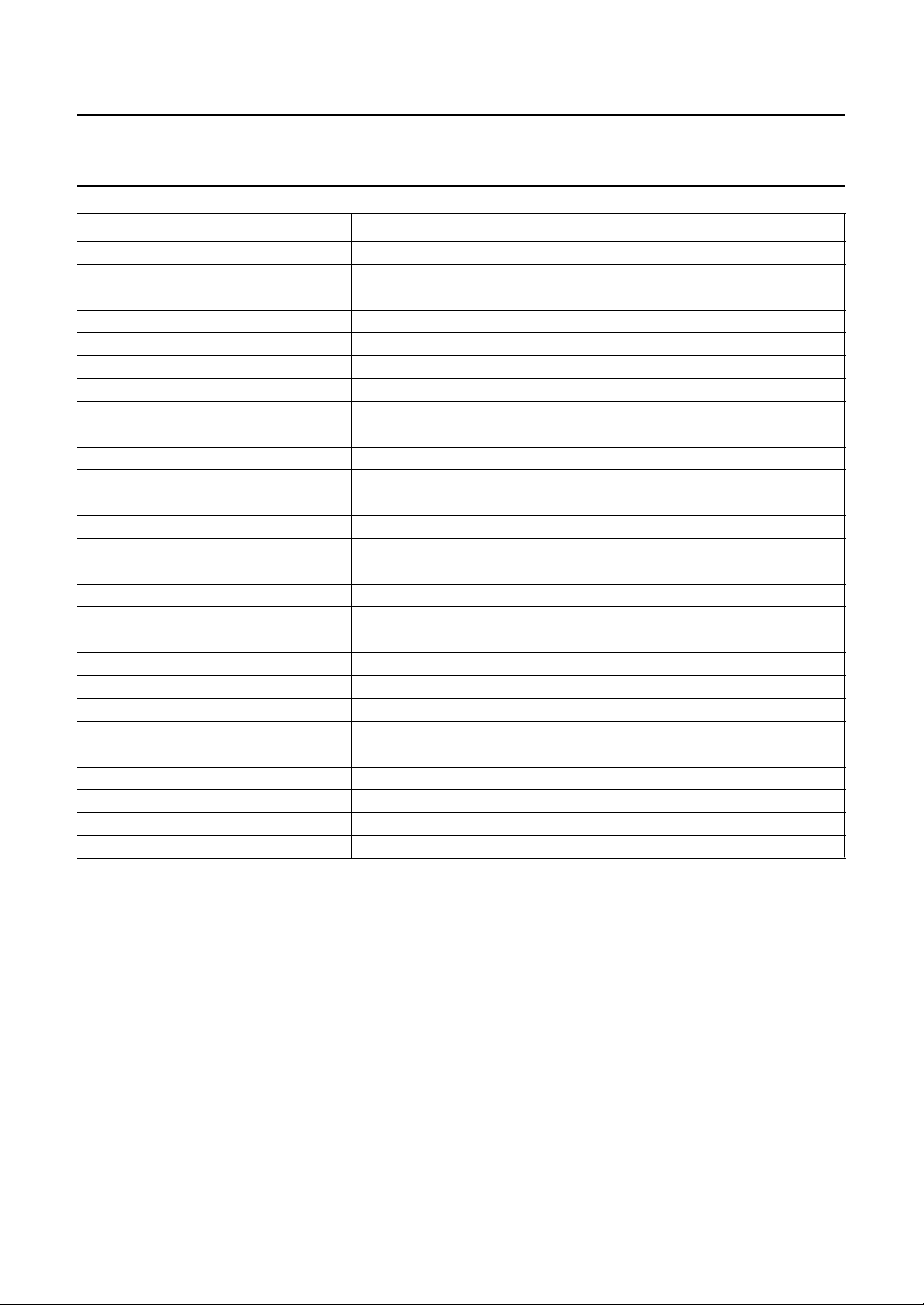

SYMBOL PIN TYPE DESCRIPTION

V

DD3

OE_FM3 39 output output enable field memory 3

RE_FM3 40 output read enable field memory 3

V_FM23_1 41 input chrominance input data bit 1 V-component

V_FM23_0 42 input chrominance input data bit 0 V-component

U_FM23_1 43 input chrominance input data bit 1 U-component

U_FM23_0 44 input chrominance input data bit 0 U-component

Y_FM23_7 45 input Y input data bit 7

Y_FM23_6 46 input Y input data bit 6

Y_FM23_5 47 input Y input data bit 5

Y_FM23_4 48 input Y input data bit 4

Y_FM23_3 49 input Y input data bit 3

n.c. 50 − not connected

Y_FM23_2 51 input Y input data bit 2

Y_FM23_1 52 input Y input data bit 1

Y_FM23_0 53 input Y input data bit 0

RSTR_FM23 54 output reset read field memory 2 and 3

RE_FM2 55 output read enable field memory 2

OE_FM2 56 output output enable field memory 2

V

DD4

V

SS4

Y_VE_7 59 output luminance output data bit 7

Y_VE_6 60 output luminance output data bit 6

Y_VE_5 61 output luminance output data bit 5

Y_VE_4 62 output luminance output data bit 4

Y_VE_3 63 output luminance output data bit 3

Y_VE_2 64 output luminance output data bit 2

38 input positive supply voltage 3 (+5 V)

57 input positive supply voltage 4 (+5 V)

58 input ground 4

SAA4997H

1996 Oct 24 6

Philips Semiconductors Preliminary specification

VErtical Reconstruction IC (VERIC) for

PALplus

handbook, full pagewidth

Y_VE_3

Y_VE_4

62

Y_VE_5

Y_VE_6

61

60

SAA4997H

Y_VE_1

Y_VE_0

U_VE_1

U_VE_0

V_VE_1

V_VE_0

V

SS1

V

DD1

n.c.

n.c.

n.c.

n.c.

n.c.

n.c.

n.c.

n.c

HREF_MA

n.c.

VA_AI

Y_VE_2

64

63

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

V

Y_VE_7

59

58

SS4

DD4

V

57

OE_FM2

RE_FM2

56

55

RSTR_FM23

Y_FM23_0

54

53

Y_FM23_1

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

Y_FM23_2

n.c.

Y_FM23_3

Y_FM23_4

Y_FM23_5

Y_FM23_6

Y_FM23_7

U_FM23_0

U_FM23_1

V_FM23_0

V_FM23_1

RE_FM3

OE_FM3

V

DD3

V

SS3

CLK_32B3

TEST3

TEST2

TEST1

SAA4997H

20

21

22

23

24

25

SS2

FILM

INTPOL

CLK_16B2

EVEN_FIELD

DD2

V

V

Fig.3 Pin configuration.

1996 Oct 24 7

26

TCK

27

TMS

28

TDI

29

30

TRSTN

TDO_VE

31

n.c.

32

n.c.

MGE442

Philips Semiconductors Preliminary specification

VErtical Reconstruction IC (VERIC) for

PALplus

FUNCTIONAL DESCRIPTION

Introduction

As shown in Fig.2 the PALplus module consists of two

special integrated circuits:

• Motion Adaptive Colour Plus And Control IC

(MACPACIC)

• VErtical Reconstruction IC (VERIC)

and four field memories TMS4C2970.

The MACPACIC and the VERIC are intended to generate

digitally decoded 50 Hz YUV signals. The MACPACIC

performs the decompanding function for the helper lines

and the motion adaptive luminance/chrominance

separation. Furthermore, PALplus system controlling,

memory controlling and clock generation are carried out in

this circuit.

The function of the VERIC is to reconstruct the separated

2 × 72 helper lines and the 430 main lines into a standard

576 lines frame according the PALplus system description

“REV 2.0”

576 lines using a vertical sample rate converter.

The data of the VERIC are clocked out with 16 MHz.

The Y :U:V bandwidth ratio is 4:1:1.

The functional block diagram of the VERIC is shown in

Fig.1. The device consists of 3 main parts:

• Luminance processing

• Chrominance processing

• Controlling.

. Chrominance is converted from 430 lines to

SAA4997H

The luminance vertical conversion process in the decoder

is complementary to that of the encoder.

In the decoder the inverse QMF function is implemented to

recombine the two separated sub-bands and to generate

the original video signal with 576 active lines per frame.

Each output line is calculated from up to seven input lines

stored in line memories containing main or helper

information. The various lines are multiplied by switched

coefficients, changing every line within a sequence of four

lines, depending on the specific mode (CAMERA or FILM).

In case of standard PAL reception, the VERIC is switched

to bypass mode controlled by the signal INTPOL.

For multi-PIP processing the VERIC is also switched to

bypass mode, but controlling of FM2/3 is different (see

Fig.6). The total signal delay between the MACPACIC

input and the VERIC output is one line for this mode.

FM2/3 are driven with 32 MHz clock frequency.

The non-multiplexed input data are clocked out with

16 MHz.

Chrominance processing

The chrominance processing is carried out by the vertical

interpolation filter (poly phase filter).

In CAMERA and FILM mode, intra-field vertical sample

rate conversion is carried out.

One output line is calculated out of three or four lines in

CAMERA or FILM mode using different coefficients or

passed through in bypass mode.

The input data are delivered by the field memories FM2

and FM3, which include multiplexed first and second field

data processed by the MACPACIC. The luminance and

chrominance input data of the VERIC are clocked with

32 MHz (CLK_32B3). Internally the device operates at

32 or 16 MHz clock frequency.

Luminance processing

In the PALplus encoder the luminance signal is separated

vertically into two sub-bands by a special Quadrature

Mirror Filter (QMF).

A vertical low-pass sub-band consists of the 430 main

letter box lines per frame, and a vertical high-pass

sub-band includes the 144 helper lines per frame.

The used QMF technique has two advantages:

• Essentially loss-free data processing

• Cancellation of alias components in the main and helper

signal in the decoder.

1996 Oct 24 8

Control functions

The VERIC controller generates the necessary internal

control signals for the line memories, formatters,

reformatters, the selector signals for the multiplexers and

the read signals for the field memories FM2/3.

The system control input signals EVEN_FIELD, INTPOL

and FILM are derived from the control part of the

MACPACIC. The field selection information EVEN_FIELD

is related to the input data of the MACPACIC and is

adapted in the VERIC to its input data.

The control functions are described in Tables 1 and 2.

Table 1 EVEN_FIELD

VALUE STATUS

EVEN_FIELD = 1 even field selected

EVEN_FIELD = 0 odd field selected

Philips Semiconductors Preliminary specification

VErtical Reconstruction IC (VERIC) for

PALplus

Table 2 INTPOL and FILM

VALUE STATUS

INTPOL = 0 FILM = 0 bypass mode;

standard signals

INTPOL = 1 FILM = 0 interpolation active;

PALplus CAMERA mode

INTPOL = 0 FILM = 1 bypass mode; multi-PIP

INTPOL = 1 FILM = 1 interpolation active;

PALplus FILM mode

Modes and delays

The PALplus module can operate in two different

hardware configurations:

• Full PALplus configuration (MACPACIC and VERIC)

• Stand alone MACPACIC.

The vertical interpolation of the VERIC can be activated by

the signal INTPOL depending on the PALplus signalling

bits, transmitted in line 23 indicating the type of signal

being received.

However, the delay between input data of the MACPACIC

and output data of the VERIC always has to be 1.5 fields.

This is achieved with a suitable read timing of the field

memories FM2 and FM3 controlled by VA_AI which is

derived from the field length measurement in the

MACPACIC.

In case of INTPOL = LOW and additionally FILM = HIGH

(FILM mode), the VERIC is switched to multi-PIP mode.

In case the delay between input of the MACPACIC and

output of the VERIC is one line (1024 CLK_16 periods).

SAA4997H

Table 3 Delays

MODE FIELD VERIC I/O DELAY

FILM mode first 2 lines

second 3 lines

CAMERA mode first 3 lines

second 4 lines

Input/Output formats

NPUT FORMATS

I

The luminance input range of the main and helper signal

has the following values:

Main signal: black = 16, white = 191 (straight binary)

Helper signal: ±70, mid = 128 (straight binary)

Chrominance format: ±90, mid = 0 (two’s complement).

UTPUT FORMATS

O

Luminance format: black = 16, white = 191 (straight

binary)

Blanking: code 16

Chrominance format: ±90, mid = 0 (two’s complement)

Blanking: code 0.

Test activities

The pins TEST1, TEST2 and TEST3 are provided to

perform the IC test activities, such as scan test.

The pins TRSTN, TDI, TMS, TCK and TDO_VE are

intended for a boundary scan test.

The line and pixel timings of the VERIC are shown in

Figures 5 to 14.

1996 Oct 24 9

Loading...

Loading...