Philips SAA4978H Datasheet

INTEGRATED CIRCUITS

DATA SH EET

SAA4978H

Picture Improved Combined

Network (PICNIC)

Product specification

Supersedes data of 1998 Oct 07

File under Integrated Circuits, IC02

1999 May 03

Philips Semiconductors Product specification

Picture Improved Combined Network

(PICNIC)

CONTENTS

1 FEATURES

2 GENERAL DESCRIPTION

3 QUICK REFERENCE DATA

4 ORDERING INFORMATION

5 BLOCK DIAGRAM

6 PINNING INFORMATION

7 FUNCTIONAL DESCRIPTION

7.1 Analog input blocks

7.1.1 Gain elements for automatic gain control (9 dB

range)

7.1.2 Clamp circuit, clamping Y to digital level 32 and

UV to 0 (2’s complement)

7.1.3 Analog anti-aliasing prefilter

7.1.4 9-bit analog-to-digital conversion

7.2 Digital processing blocks

7.2.1 Overflow detection

7.2.2 Y delay

7.2.3 Transient noise suppression

7.2.4 Non-linear phase filter after ADC

7.2.5 4 MHz notch

7.2.6 Digital clamp correction for UV

7.2.7 4:4:4 downsampled to4:2:2 or4:1:1

7.2.8 Bus A format: interface formatting, timed with

enabling signal (see Table 1 and Fig.9)

7.2.9 Bus B format (see Table 1 and Fig.9)

7.2.10 Time base correction and sample rate

conversion

7.2.11 Noise reduction

7.2.12 Histogram

7.2.13 Subtitle detection

7.2.14 Black bar detection

7.2.15 Bus C format (see Table 1)

7.2.16 Bus D reformatter: the various input formats

are all converted to the internal 9 bits 4 :2:2

(see Table 1)

7.2.17 Peaking

7.2.18 Non-linear phase filter before DAC

7.2.19 DCTI

7.2.20 Border blank

7.3 Analog output blocks

7.3.1 Triple 10-bit digital-to-analog conversion

7.3.2 Analog anti-aliasing post-filter

7.3.3 PLL

7.3.4 SNERT

7.3.5 PSP

7.3.6 Microcontroller

7.3.7 Board level testability

7.3.8 Power-on reset

SAA4978H

8 CONTROL REGISTER DESCRIPTION

9 LIMITING VALUES

10 THERMAL CHARACTERISTICS

11 CHARACTERISTICS

12 APPLICATION

13 PACKAGE OUTLINE

14 SOLDERING

14.1 Introduction

14.2 Reflow soldering

14.3 Wave soldering

14.4 Repairing soldered joints

15 DEFINITIONS

16 LIFE SUPPORT APPLICATIONS

17 PURCHASE OF PHILIPS I2C COMPONENTS

1999 May 03 2

Philips Semiconductors Product specification

Picture Improved Combined Network

(PICNIC)

1 FEATURES

• Clamp

• Analog AGC

• Triple YUV 9-bit Analog-to-Digital Converter (ADC)

• Triple bypassable analog anti-alias filter

• 4 MHz notch filter

• Non-linear phase filter after ADC

• 4:1:1 or 4:2:2 digital processing

• 4:1:1 or 4:2:2 selectable I/O interface

• Asynchronous digital input

• Time base correction

• Histogram analysis

• Histogram modification

• Subtitle detection

• Black bar detection

• Line memory based noise reduction (spatial)

• Noise level measurement

• Clamp noise reduction

• Dynamic peaking

• Energy measurement

• Multi Picture-In-Picture (multi PIP) decimation

• Differential Pulse Code Modulation (DPCM) data

decompression for colour

SAA4978H

• 2D-peaking and coring

• Non-linear phase filter before DAC

• Coaxial Transceiver Interface (CTI)

• Triple 10-bit Digital-to-Analog Converter (DAC)

• Triple bypassable analog reconstruction filter

• Embedded microcontroller (80C51 core)

• Programmable signal positioner

• SNERT interface

2

• I

C-bus user control interface

• Boundary Scan Test (BST).

2 GENERAL DESCRIPTION

The SAA4978H is a monolithic integrated circuit suitable

either for 1f

of picture improvement functions. It combines

analog-to-digital and digital-to-analog conversion for YUV

signals, digital processing, line-locked clock regeneration

and an 80C51 microcontroller core in one IC.

or 2fH applications that contain a large variety

H

3 QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

V

I

DDA

I

DDD

f

clk

DDA

DDD

analog supply voltage 3.15 3.3 3.45 V

digital supply voltage 3.0 3.3 3.6 V

analog supply current V

digital supply current V

= 3.45 V − 145 180 mA

DDA

= 3.6 V − 210 270 mA

DDD

clock frequency − 16 − MHz

S/N signal-to-noise ratio default settings 50 −−dB

4 ORDERING INFORMATION

TYPE

NUMBER

NAME DESCRIPTION VERSION

SAA4978H QFP160 plastic quad flat package; 160 leads (lead length 1.6 mm);

PACKAGE

SOT322-2

body 28 × 28 × 3.4 mm; high stand-off height

1999 May 03 3

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

o

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

1999 May 03 4

k, full pagewidth

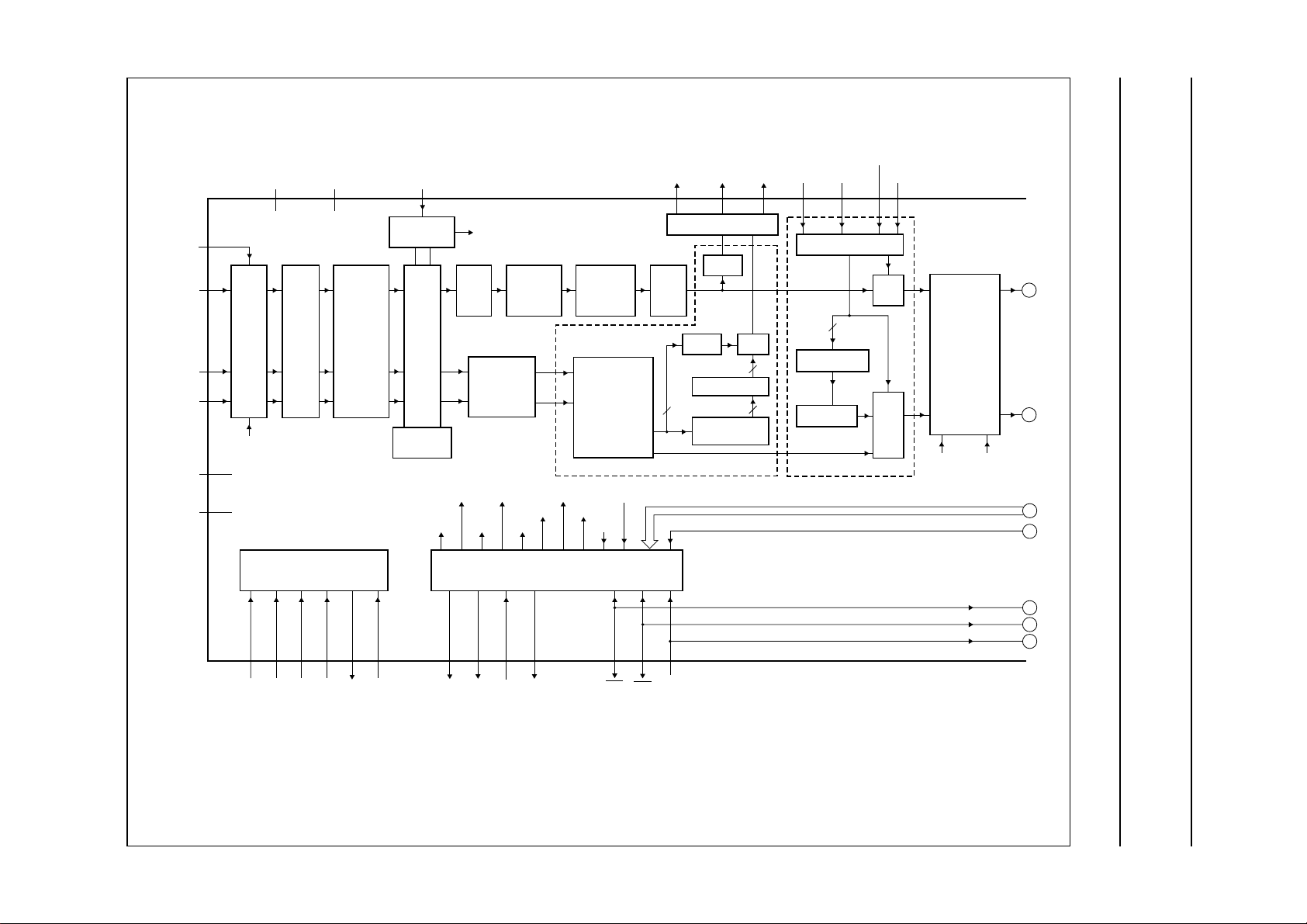

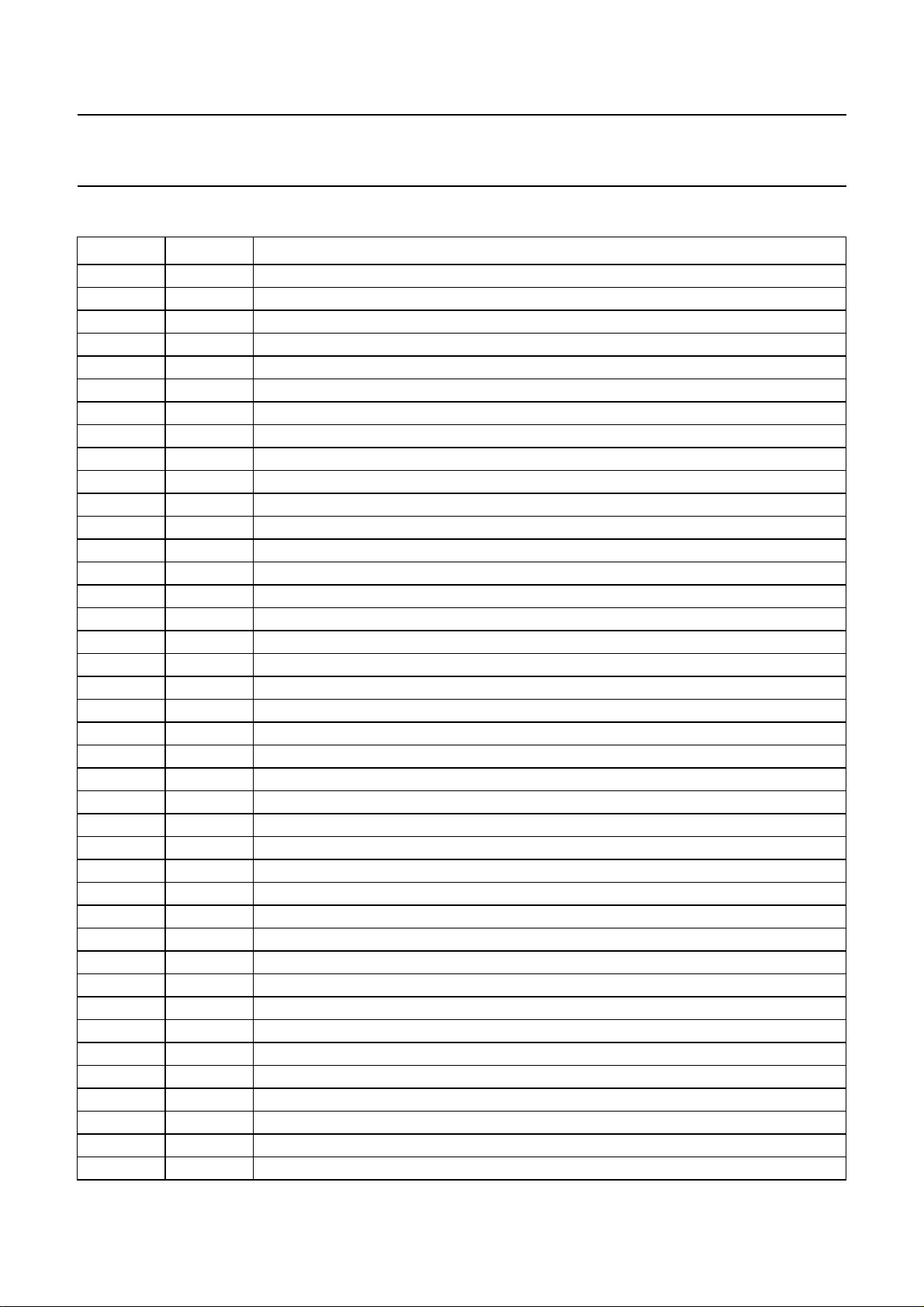

5 BLOCK DIAGRAM

Picture Improved Combined Network

(PICNIC)

Philips Semiconductors Product specification

V

DDA1

V

SSA1

DIFFIN

YIN

UIN

VIN

V

DDA4

V

SSA4

to

to

21

23

CLAMP

25

26

CLP

11, 22, 24, 31

13, 16, 27, 32

V

DDD1

V

DDD4

64, 87,

100, 135

to

V

SSD1

V

64, 90,

134, 139

TRIPLE

AGC

9-BIT

SAA4978H

to

SSD4

TRIPLE

ANALOG

PREFILTER

BGEXT

17

BAND GAP

REFERENCES

Ref L

Ref H

ADC

TRIPLE

9-BIT

OVERFLOW

DETECTOR

CLP

various

bias controls

Y

DELAY

CORRECTION

RED

WEC

UV

CLAMP

WEA

MAJORITY

FOLLOWER

FILTER

BLANKING

BORDER

IEC

PIXREP

PSPBST/TEST

NON-LINEAR

PHASE

FILTER

DOWNSAMPLER

HA

HREF

YA0

to

DITHER

11

DOWNSAMPLER

YA8

3-STATE

DITHER

MUX

FORMATTER

DITHER

WEA

4 MHz

NOTCH

bus A bus B

to

UVA8

5

10

to

UVB8

SYNCHRONIZE

REFORMATTER

UPSAMPLER

UVB0

UVA0

YB0

YB8

5

WEB

to

CLKAS

MUX

MUX

856675 to 6784 to 7643 to 5153 to 6162

TIME BASE

CORRECTION/

CONVERTER

SKEWEN SKEW

SAMPLE

RATE

A

B

C

D

41

40

39

38

37

36

TCK

TDO

TDI

TMS

TRST

TEST

HDFL

Standard bus width in data path is 9 bits; exceptions are marked.

10

157

INT1

158

INT0

FBL

30

29

19

18

HREFEXT

VA

VDFL

Fig.1 Block diagram (continued in Fig.2).

E

F

G

MHB172

SAA4978H

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

b

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

1999 May 03 5

ook, full pagewidth

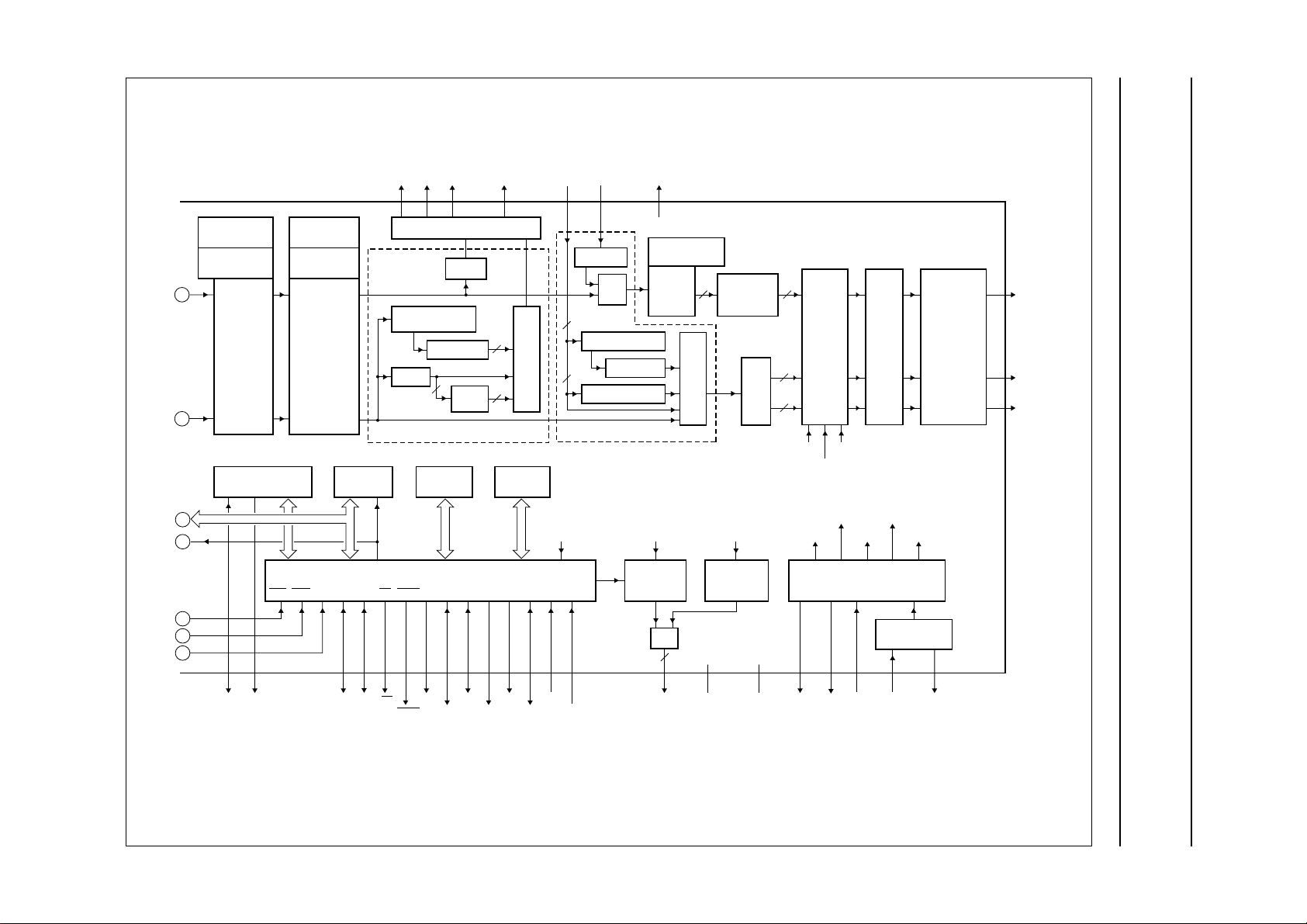

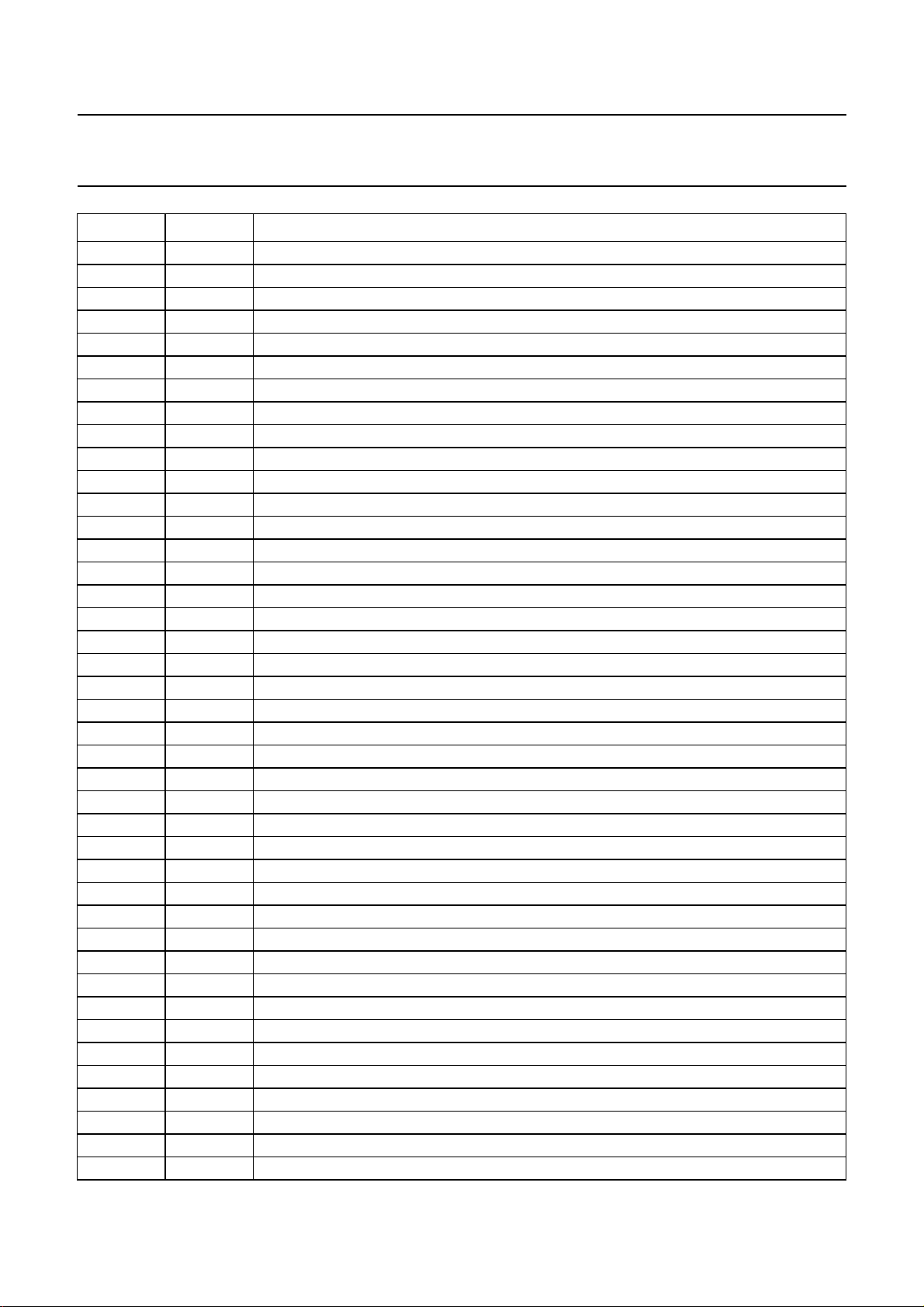

Philips Semiconductors Product specification

Picture Improved Combined Network

(PICNIC)

SPECTRAL

MEASUREMENT

ESTIMATION

A

B

C

D

E

F

G

SNDA

NOISE

NOISE

REDUCTION

SPECIAL FUNCTION

REGISTERS

INT1 INT0 P1.4

2

1

SNCL

SUBTITLE

DETECTION

BLACK BAR

DETECTION

HISTOGRAM

MODIFICATION

VARIOUS

REGISTERS

P2.7

to

P2.0

140

to

147

P0.7

to

P0.0

149

to

156

P1.1

YC8

to

WEC

DITHER

DATA8

EA PSEN

EA

YC0

IEC

112

3-STATE

DITHER

DOWNSAMPLER

DITHER

FORMATTER

8

DPCM

CODER

bus C

AUXILIARY

RAM

80C51 MICROCONTROLLER CORE

P3.5

P3.4 P1.2

137136

160138

159

ALE

T0

T1

PSEN

RSTW

UVC8

to

UVC0

5

4

PROGRAM

P1.3 P1.7

8

RSTR

MUX

ROM

SDA

YD0

UVD0

to

to

YD8

UVD8

91

to 99

UNDITHER

5

4

REFORMATTER

DPCM DECODER

101 to 109 110124 to 132114 to 122113

MUX

UPSAMPLER

bus D

RED

SPECTRAL

MEASUREMENT

DYNAMIC

10

PEAKING

MUX

NON-LINEAR

PHASE

FILTER

DCTI

10

10

10

PIXREP

BORDER

BLANK

BLANKING

BORDER

DAC

TRIPLE

10-BIT

TRIPLE

ANALOG

POST-FILTER

12

YOUT

14

UOUT

15

VOUT

SAA4978H

SKEWEN

CL16

bone

P1.5

P1.6

RST

64

59

SCL

RST

WATCHDOG

OR

WDRST V

7

FREQUENCY

42, 63, 86,

111, 133, 3

SSO1

to

V

SSO6

GUARD

52, 123, 148

V

DDO1

V

DDO3

89

88

CLK16

to

CLK32

SKEW

HA

PLL

28

CL16

CL32HREFCL16 CL16

CRYSTAL

OSCILLATOR

34

OSCI

35

MHB173

OSCO

SAA4978H

Standard bus width in data path is 9 bits; exceptions are marked.

Fig.2 Block diagram (continued from Fig.1).

Philips Semiconductors Product specification

Picture Improved Combined Network

SAA4978H

(PICNIC)

6 PINNING INFORMATION

SYMBOL PIN DESCRIPTION

SNDA 1 SNERT data input/output

SNCL 2 SNERT clock output

V

SSO6

SCL 4 I

SDA 5 I

RST 6 microcontroller reset input

WDRST 7 watchdog reset output

RSTW 8 reset write signal output/SNERT reset (only PALplus) Port 1.2

RSTR 9 reset read signal output/SNERT reset (SAA4991WP or SAA4992H) Port 1.3

FBL 10 fast blanking input to PSP and Port 1.4

V

DDA1

YOUT 12 Y analog output

V

SSA1

UOUT 14 Uanalog output

VOUT 15 V analog output

V

SSA2

BGEXT 17 band gap external/reference currents input

HDFL 18 horizontal synchronization signal output, deflection part

VDFL 19 vertical synchronization signal output, deflection part

AGND 20 analog ground

DIFFIN 21 differential Y input

V

DDA2

YIN 23 Y analog input

V

DDA3

UIN 25 Uanalog input

VIN 26 V analog input

V

SSA3

HA 28 horizontal synchronization input, acquisition part

VA 29 vertical synchronization input, acquisition part

HREFEXT 30 horizontal reference external output

V

DDA4

V

SSA4

V

SSX

OSCI 34 oscillator input

OSCO 35 oscillator output

TEST 36 test input/external 32MHz clock input

TRST 37 BST reset input

TMS 38 BST test mode select input

TDI 39 BST test data input

TDO 40 BST test data output

3 digital microcontroller I/O ground 6; internally connected to all other V

2

C-bus serial clock input (P1.6)

2

C-bus serial data input/output (P1.7)

11 analog back-end supply voltage 1

13 analog back-end ground 1

16 analog input ground 2; internally connected to substrate

22 analog input supply voltage 2

24 analog input supply voltage 3

27 analog input ground 3; internally connected to substrate

31 analog PLL supply voltage 4

32 analog PLL ground 4; internally connected to substrate

33 oscillator ground

SSO

pins

1999 May 03 6

Philips Semiconductors Product specification

Picture Improved Combined Network

(PICNIC)

SYMBOL PIN DESCRIPTION

TCK 41 BST test clock input

V

SSO1

UVA0 43 bus A output UVL

UVA1 44 bus A output UV0

UVA2 45 bus A output UV1

UVA3 46 bus A output UV2

UVA4 47 bus A output UV3

UVA5 48 bus A output UV4

UVA6 49 bus A output UV5

UVA7 50 bus A output UV6

UVA8 51 bus A output UV7

V

DDO1

YA0 53 bus A output YL

YA1 54 bus A output Y0

YA2 55 bus A output Y1

YA3 56 bus A output Y2

YA4 57 bus A output Y3

YA5 58 bus A output Y4

YA6 59 bus A output Y5

YA7 60 bus A output Y6

YA8 61 bus A output Y7

WEA 62 write enable bus A output

V

SSO2

V

DDD1

V

SSD1

WEB 66 write enable bus B input

YB8 67 bus B input Y7

YB7 68 bus B input Y6

YB6 69 bus B input Y5

YB5 70 bus B input Y4

YB4 71 bus B input Y3

YB3 72 bus B input Y2

YB2 73 bus B input Y1

YB1 74 bus B input Y0

YB0 75 bus B input YL

UVB8 76 bus B input UV7

UVB7 77 bus B input UV6

UVB6 78 bus B input UV5

UVB5 79 bus B input UV4

UVB4 80 bus B input UV3

UVB3 81 bus B input UV2

42 digital bus A/B ground 1; internally connected to all other V

52 digital I/O bus A/B supply voltage 1; internally connected to all other V

63 digital bus A/B ground 2; internally connected to all other V

64 digital core supply voltage 1; internally connected to all other V

65 digital core ground 1; internally connected to all other V

SSD

SSO

SSO

pins

pins

pins

DDD

SAA4978H

pins

DDO

pins

1999 May 03 7

Philips Semiconductors Product specification

Picture Improved Combined Network

(PICNIC)

SYMBOL PIN DESCRIPTION

UVB2 82 bus B input UV1

UVB1 83 bus B input UV0

UVB0 84 bus B input UVL

CLKAS 85 asynchronous clock input

V

SSO3

V

DDD2

CLK16 88 16 MHz clock output

CLK32 89 32 MHz clock output

V

SSD2

UVD0 91 bus D input UVL

UVD1 92 bus D input UV0

UVD2 93 bus D input UV1

UVD3 94 bus D input UV2

UVD4 95 bus D input UV3

UVD5 96 bus D input UV4

UVD6 97 bus D input UV5

UVD7 98 bus D input UV6

UVD8 99 bus D input UV7

V

DDD3

YD0 101 bus D input YL

YD1 102 bus D input Y0

YD2 103 bus D input Y1

YD3 104 bus D input Y2

YD4 105 bus D input Y3

YD5 106 bus D input Y4

YD6 107 bus D input Y5

YD7 108 bus D input Y6

YD8 109 bus D input Y7

RED 110 read enable bus D output

V

SSO4

IEC 112 input enable bus C output

WEC 113 write enable bus C output

YC8 114 bus C output Y7

YC7 115 bus C output Y6

YC6 116 bus C output Y5

YC5 117 bus C output Y4

YC4 118 bus C output Y3

YC3 119 bus C output Y2

YC2 120 bus C output Y1

YC1 121 bus C output Y0

YC0 122 bus C output YL

86 digital I/O bus B/clock ground 3; internally connected to all other V

87 digital core supply voltage 2; internally connected to all other V

90 digital core ground 2; internally connected to all other V

100 digital core supply voltage 3; internally connected to all other V

111 digital I/O bus C/D ground 4; internally connected to all other V

SSD

pins

DDD

DDD

SSO

SAA4978H

pins

SSO

pins

pins

pins

1999 May 03 8

Philips Semiconductors Product specification

Picture Improved Combined Network

(PICNIC)

SYMBOL PIN DESCRIPTION

V

DDO2

UVC8 124 bus C output UV7

UVC7 125 bus C output UV6

UVC6 126 bus C output UV5

UVC5 127 bus C output UV4

UVC4 128 bus C output UV3

UVC3 129 bus C output UV2

UVC2 130 bus C output UV1

UVC1 131 bus C output UV0

UVC0 132 bus C output UVL

V

SSO5

V

SSD3

V

DDD4

EA 136 external access output (active LOW)

PSEN 137 program store enable output (active LOW)

ALE 138 address latch enable output

V

SSD4

P2.7 140 Port 2 data input/output signal 7

P2.6 141 Port 2 data input/output signal 6

P2.5 142 Port 2 data input/output signal 5

P2.4 143 Port 2 data input/output signal 4

P2.3 144 Port 2 data input/output signal 3

P2.2 145 Port 2 data input/output signal 2

P2.1 146 Port 2 data input/output signal 1

P2.0 147 Port 2 data input/output signal 0

V

DDO3

P0.7 149 Port 0 data input/output signal 7

P0.6 150 Port 0 data input/output signal 6

P0.5 151 Port 0 data input/output signal 5

P0.4 152 Port 0 data input/output signal 4

P0.3 153 Port 0 data input/output signal 3

P0.2 154 Port 0 data input/output signal 2

P0.1 155 Port 0 data input/output signal 1

P0.0 156 Port 0 data input/output signal 0

INT0 157 interrupt 0, I/O Port 3.2 (active LOW)

INT1 158 interrupt 1, I/O Port 3.3 (active LOW)

T0 159 timer 0 I/O Port 3.4

T1 160 timer 1 I/O Port 3.5

123 digital I/O supply voltage 2 to bus C/D; internally connected to all other V

133 digital I/O ground 5 to bus D and microcontroller; internally connected to all other

V

pins

SSO

134 digital core ground 3; internally connected to all other V

135 digital core supply voltage 4; internally connected to all other V

139 digital core ground 4; internally connected to all other V

148 microcontroller I/O pad supply voltage 3

SSD

SSD

pins

pins

DDD

SAA4978H

pins

DDO

pins

1999 May 03 9

Philips Semiconductors Product specification

Picture Improved Combined Network

(PICNIC)

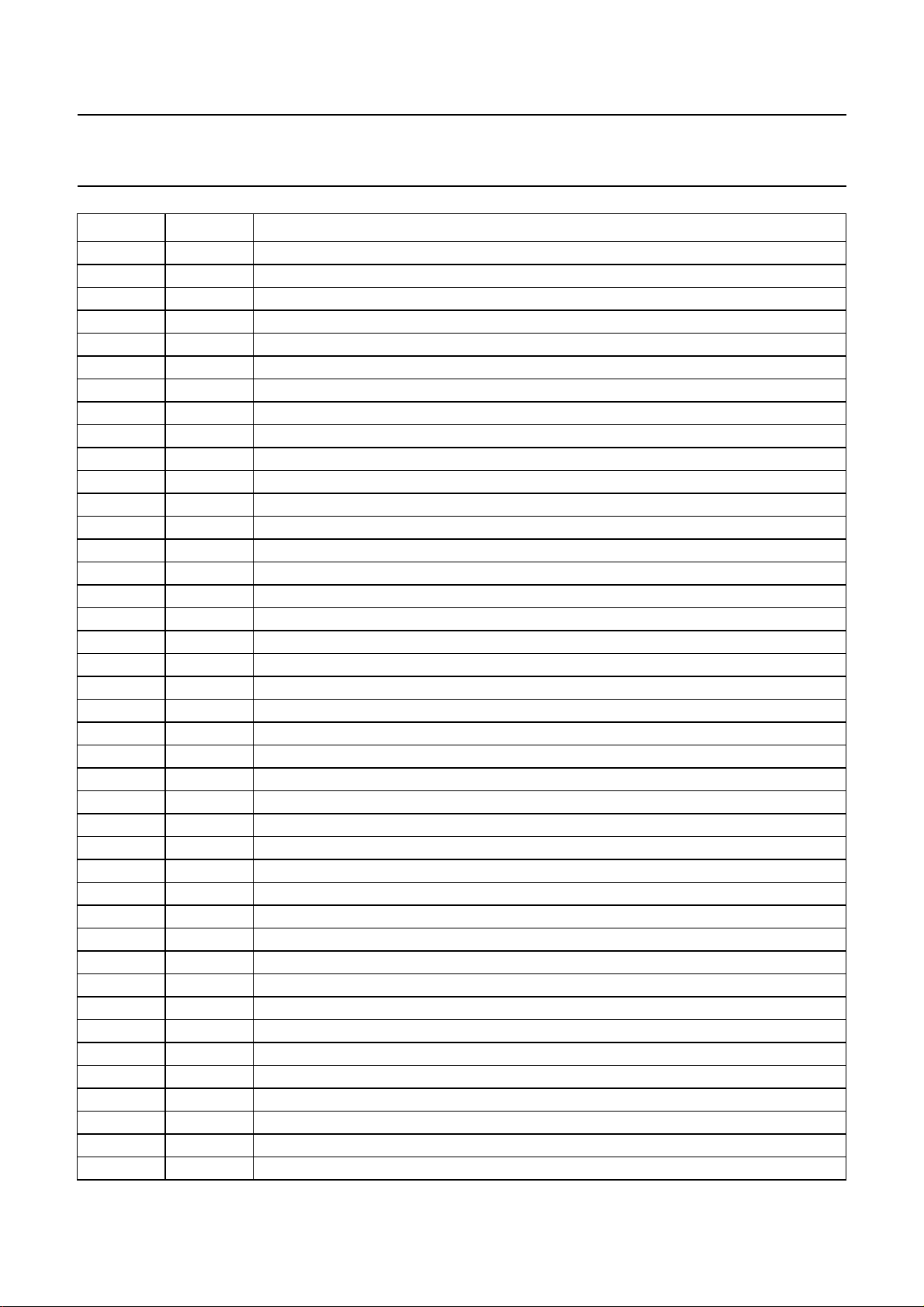

handbook, halfpage

40

160

1

SAA4978H

41

121

80

SAA4978H

120

81

MHB174

Fig.3 Pin configuration.

7 FUNCTIONAL DESCRIPTION

The SAA4978H consists of the following main functional

blocks:

• Analog preprocessing and analog-to-digital conversion

• Digital processing at 1fH level

• Digital processing at 2fH level

• Digital-to-analog conversion

• Line-locked clock generation

• Crystal oscillator

• Control interfacing I2C-bus and SNERT

• Register I/O

• Programmable Signal Positioner (PSP)

• 80C51 microcontroller core

• Board level testability provisions.

7.1 Analog input blocks

7.1.1 GAIN ELEMENTS FOR AUTOMATIC GAIN CONTROL

(9 dB RANGE)

A variable amplifier is used to map the possible YUV input

range to the analog-to-digital converter range e.g. as

defined for SCART signals.

According to this specification, a lift of 6 dB up to a drop of

3 dB may be necessary with respect to the nominal values.

The gain setting within the required minimum 9 dB range

is performed digitally via the internal microcontroller.

For this purpose a gain setting digital-to-analog converter

is incorporated. The smallest step in the gain setting

should be hardly visible on the picture, this can be met with

smaller steps of 0.4%/step.

Luminance and chrominance gain settings can be

separately controlled. The reason for this split is that

U and V may have already been gain adjusted by an

Automatic Chrominance Control (ACC), whereas

luminance is to be adjusted by the SAA4978H AGC.

However, for RGB originated sources, Y, U and V should

be adjusted with the same AGC gain.

7.1.2 C

LAMP CIRCUIT, CLAMPING Y TO DIGITAL LEVEL 32

AND UV TO 0(TWOS COMPLEMENT)

A clamp circuit is applied to each input channel, to map the

colourless black level in each video line (on the sync back

porch) to level 32 at 9 bits for Y and to the centre level of

the converters for U and V. During the clamp period, an

internally generated clamp pulse is used to switch-on the

clamp action.

1999 May 03 10

Philips Semiconductors Product specification

Picture Improved Combined Network

(PICNIC)

A voltage controlled current source construction, which

references to voltage reference points in the ladders of the

analog-to-digital converters, provides a current on the

input of the YUV signals in order to bring the signals to the

correct DC value. This current is proportional to the DC

error, but is limited to±150 µA. It is essential that the clamp

current becomes zero with a zero error and that the

asymmetry between positive and negative clamp currents

is limited to within 10%. When the clamping action is off,

the residual clamp current should be very low, so that the

clamp level will not drift away within a video line.

The clamp level in the Y channel has a minimum value of

600 mV to ensure undisturbed clamping for maximum

Y input signals with top sync levels up to 600 mV. In order

to improve common mode rejection it is recommended to

connect the same source impedance as used in the YIN

input at the DIFFIN input to ground.

7.1.3 A

A 3rd-order linear phase filter is applied to each of the

Y, U and V channels. It provides a notch on f

at Y, U and V) to strongly prevent aliasing to low

frequencies, which would be the most disturbing.

The bandwidth of the filters is designed for −3 dB at

5.6 MHz. The filters can be bypassed if external filtering

with other characteristics is desired. In the bypass mode

the gain accuracy of the front-end part is 4% instead of 8%

for the filter-on mode.

7.1.4 9-

NALOG ANTI-ALIASING PREFILTER

BIT ANALOG-TO-DIGITAL CONVERSION

(16 MHz

clk

SAA4978H

7.2.2 Y

The Y samples can be shifted onto 4 positions with

respect to the UV samples. This shift is meant to account

for a possible difference in delay prior to the SAA4978H,

e.g. from a prefilter in front of an analog-to-digital

converter. The zero delay setting is suitable for the

nominal case of aligned input data according to the

interface format standard. One setting provides one

sampleless delay in Y, the other two settings provide more

delay in the Y path.

7.2.3 T

A circuit is added in the luminance channel to suppress the

typical multi-step trip level noise. This majority follower

filter compares the neighbouring pixels to a +1 or −1 LSB

difference. If the majority of these differences is +1 then 1

is added to the actual pixel. If the majority of these

differences is −1 then 1 is subtracted from the actual pixel.

The number of pixels included in the filter is selectable;

1 (bypass), 3, 5, 7 or 9.

7.2.4 N

The non-linear phase filter adjusts for possible group delay

differences in the luminance channel. The filter coefficients

are [−L × (1 − u); 1 + L; −L × u]; where L determines the

strength of the filter and u determines the asymmetry.

The effect of the asymmetry is that for higher frequencies

the delay is decreased for u ≤ 0.5. Settings are provided

for L = 0,1⁄16,2⁄16and3⁄16 and u = 0,1⁄4and1⁄2.

DELAY

RANSIENT NOISE SUPPRESSION

ON-LINEAR PHASE FILTER AFTER ADC

Three identical multi-step type analog-to-digital converters

are used to convert the Y, U and V inputs with a 16 MHz

data rate. The ADCs have a 2-bit overflow detection, and

an underflow detection for U and V, to be used for AGC

control. The 2 bits are coded for one in-range level and

three overflow levels; 1 dB, 1 to 2 dB and 2 to 3 dB.

7.2 Digital processing blocks

7.2.1 O

VERFLOW DETECTION

A histogram of the three overflow levels is made every field

and can be read in a 2-byte accuracy. An input selector

defines which ADC is monitored.

In the event of U or V selection the underflow information

is also added to the first histogram level, in this way the

data can be handled as out-of-range information.

The histogram content provides information for the AGC to

make an accurate estimate of the decrease in gain, in the

event of overflow for luminance or out-of-range detection

for U and V.

1999 May 03 11

7.2.5 4 MH

Z NOTCH

The 4 MHz notch provides a zero on1⁄4 of the sample

frequency. With fs= 16 MHz the notch is thus at 4 MHz.

The 3 dB notch width is 2 MHz. The filter coefficients are

1

⁄8× [−1; 0; 5; 0; 5; 0; −1]. This filter gives a relative gain of

0.75 dB at 1.7 and 6.3 MHz.

The notch can be bypassed without changing the group

delay.

7.2.6 D

IGITAL CLAMP CORRECTION FOR UV

During 32 samples within the active clamping the clamp

error is measured and accumulated to determine a

low-pass filtered value of the clamp error. A vertical

recursive filter is then used to further reduce this error

value. This value can be read by the microcontroller or be

used directly to correct the clamp error. It is also possible

for the microcontroller to give a fixed correction value.

Philips Semiconductors Product specification

Picture Improved Combined Network

(PICNIC)

7.2.7 4:4:4DOWNSAMPLED TO 4:2:2OR 4:1:1

4:4:4 data is downsampled to 4 : 2 : 2, by first filtering

with a [1; 0; −7; 0; 38; 64; 38; 0; −7; 0; 1] filter, before being

subsampled by a factor of 2. The U and V samples from

the 4 :2:2 data are filtered again by a [−1; 0; 9; 16; 9; 0;

−1] filter, before being subsampled a second time by a

factor of 2. Bypassing this function keeps the data in the

4:2:2 format.

7.2.8 B

The chosen 4:1:1 or 4:2:2 formatted output data is

presented to bus A (YUV_A bus), consistent with the WEA

data enable signal. After the rising edge of WEA the first,

respectively second, data word contains the first phase of

the 4 :1:1 or 4:2:2 format, depending on the qualifier

respectively prequalifier mode of WEA. If the data has to

be formatted to 8 bits, a choice can be made between

rounding and dithered rounding. Dithered rounding may be

applied in the sense that every odd output sample has had

an addition of 0.25 LSB (relative to 8 bits) before

truncation and every even output sample has had an

addition of 0.75 LSB before truncation. In this way, on

average, correct rounding is realized (no DC shift).

Especially for low frequency signals, the resolution is

increased by a factor of 2 by the high frequency

modulation. The phase of dithering can be switched 180°

from line-to-line, field-to-field or frame-to-frame, in order to

decrease the visibility of the dithering pattern.

The not connected output pins of bus A, including WEA

(depending on the application), can be set to 3-state to

allow short-circuiting of these pins at board production.

Short-circuiting at not connected outputs can not be tested

by Boundary Scan Test (BST). For outputs in 3-state mode

it is not allowed to apply voltages higher than

V

DDO

7.2.9 B

Bus B can accommodate the following formats; 4 :1:1

serial, 4:2:2 parallel, 4:2:2 double clock UYVY, all

synchronous and asynchronous. All external formats are

selectable with prequalifier or qualifier WEB. All of the

various input formats are converted to the internal 9 bits

4:2:2. For the 8-bit inputs, the LSB of the input bus

should be connected externally to a fixed logic level. In the

event of a 4:1:1 input, the U and V channels are

reformatted and upsampled by generating the extra

samples with a1⁄16× [−1; 9; 9; −1] filter. The other U and V

samples remain equal to the original 4 :1:1 sample

values.

US A FORMAT: INTERFACE FORMATTING,TIMED

WITH ENABLING SIGNAL

+ 0.3 V.

US B FORMAT (see Table 1 and Fig.9)

(see Table 1 and Fig.9)

SAA4978H

It is possible, in bus B reformatter, to invert the UV data so

that the SAA4978H can handle any polarity convention of

the UV data.

In the event of an asynchronous input the clock has to be

provided externally to pin CLKAS.

When applying an external PALplus decoder with 30 ms

processing delay, the vertical field start can be set via

software in a PSP register. For

format input, inversion of the MSB of the (synchronized)

bus B UV input can be selected. Synchronization signals

included in this format will be ignored.

7.2.10 T

The Time Base Correction (TBC) and Sample Rate

Conversion (SRC) block provides a dynamically controlled

delay with an accuracy of up to1⁄64 of a pixel and a range

of −0.5 to +0.5 lines (plus processing delay).

The time base correction block has an input for skew data.

This skew data can be the phase error measured by a

HPLL, which is located in the PLL block of the SAA4978H.

The skew is used as a shift of the complete active video

part of a line. Added with a static (user controlled) shift, up

to1⁄2video line (32 µs) can be shifted in both directions,

related to a nominal1⁄2line delay.

For sample rate conversion, the delay is also varied along

the line with the subpixel accuracy. With a zero-order

variation of the delay, a linear compress or expand

function can be obtained. The range for the compression

factor is 0 to 2, meaning infinite zoom up to a compression

with a factor of 2. With a 2nd-order variation of the delay

added to the control, the compression factor can be

modulated with a parabolic shape, thus giving a panoramic

view option to display e.g. 4 : 3 video on a 16 : 9 screen or

vice versa.

The static shift may also be used to make the delay of the

SAA4978H plus periphery equal to an integer number of

lines. This is useful for 1fH applications, in which the

horizontal sync signal is not delayed with the video data.

This will then make the function of time base correction

obsolete for 1fH applications.

Another main task for the sample rate converter is to

resynchronize external data at a non-system clock sample

rate, for instance, MPEG decoder signals at 13.5 MHz.

A requirement for these signals is that they are line and

frame locked to the SAA4978H.

IME BASE CORRECTION AND SAMPLE RATE

CONVERSION

“CCIR 656”

standard data

1999 May 03 12

Philips Semiconductors Product specification

Picture Improved Combined Network

(PICNIC)

7.2.11 NOISE REDUCTION

The noise reduction part consists of clamp noise reduction

and spatial noise reduction for low frequency noise. Within

this ensemble a two dimensional band split is used,

enabling also the functions of 2D low passing, adding the

multi Picture-In-Picture (multi PIP) function and 2D

peaking.

The clamp noise reduction is realized with an adaptive

temporal recursive filter. This filter will correct the DC level

of each line when it is varying from field-to-field in the

segments with the least likely movement. This clamp noise

filtering is intended to correct for clamp errors in a

complete chain, which cannot be removed with traditional

clamping on the back porch of the video. Clamp noise is

only reduced for luminance.

The spatial noise reduction is targeted for reduction of the

mid frequency noise spectrum, where adaptive filtering

combines pixels around the centre pixel and pixels from

the lines above in a recursive way. This spatial noise

reduction is only realized for luminance.

The 2D low-pass filter is a [1; 2; 1] filter in both the

horizontal and vertical direction. 2D high-pass is realized

by taking the centre tap and subtracting the 2D low-pass

output from it. Also added in the 2D high-pass is the

vertical low-passed data, which is subtracted from the

centre tap and multiplied by a user selectable gain

(0 to7⁄8). The 2D high-pass data is multiplied by a user

selectable gain of 0 and2⁄4to8⁄4 and cored before adding

it to the 2D low-pass branch for the 2D peaking function.

The HF signal bypasses both the LF temporal and the

spatial noise reduction, therefore sharpness in the high

frequencies is not reduced by the noise reduction parts.

The factor 0 on the HF signal yields a pure 2D low-passed

signal at the output. Multi PIP with pure subsampling of this

signal yields a much better result than without the low-pass

operation.

7.2.12 H

Histogram modification consists of acquiring the histogram

of the luminance levels and correcting the luminance

transfer curve in order to provide more perceptual contrast

in the picture.

ISTOGRAM

SAA4978H

The histogram acquisition uses 32 baskets on the grey

scale from (ultra) black to (ultra) white. Pixels that are

found around the centre of a basket increase a counter for

that basket with the value 8, pixels that come around the

edge between two baskets increase the counters in both

baskets, such as 3 in the left one and 5 in the right one.

By this method, the quantization distortion is overcome

from having a discrete set of baskets.

Between acquisition of the histogram and correction of the

transfer curves, the microcontroller included in the

SAA4978H processes the counter values from the

32 baskets. The outcome of the microcontrollers algorithm

defines a differential transfer curve for the luminance. This

means that only differences from a 1 : 1 transfer curve are

coded. This is done in 32 LUT points, with a linear

interpolation for all input values in between the LUT points.

When changes are made to the luminance level of pixels,

the saturation has to be restored by using the same

relative gain for the U and V channels.

The histogram data also provides the information of the

minimum and maximum levels of Y, U and V, by which the

microcontroller can affect an AGC gain before the video

analog-to-digital conversion.

Another main part of the histogram is the display-bars

block. This block can insert up to 32 horizontal bars in the

YUV data path. Size, spacing, luminance, colour and

length are fully programmable. This can be used to

construct a visual display of the histogram or transfer

curve.

7.2.13 S

Subtitle detection searches in a large area of the video

field for patterns that are characteristic for subtitles.

The expectation is to encounter in a video line a

considerable number of crossings through both a dark

grey and a light grey threshold and in its vicinity also

crossings in the other direction. This part is realized with

valid crossing (event) counting on each line in the target

area. This event value is stored for 128 lines in the subtitle

RAM, which is located at the top of the auxiliary RAM.

The subtitle logic has higher priority to access the subtitle

RAM than the microcontroller.

UBTITLE DETECTION

For economy, a subsampling is realized on the video with

a factor of 4 before the histogram is produced. From

line-to-line, a two pixel offset is used on the subsample

pattern.

1999 May 03 13

The internal microcontroller can filter out this data. In a

number of adjacent lines, there must be a similar high

count value for the number of events. If this condition holds

then the detection of subtitles on that vertical position is

more definite.

Philips Semiconductors Product specification

Picture Improved Combined Network

(PICNIC)

This information can be used in combination with other

information on how to display the video source on the

screen. Such decisions are made entirely by the internal

microcontroller.

7.2.14 B

Black bar detection searches in the upper and in the lower

part of the screen to respectively the last black line and the

first black line. To avoid disturbances of Logos in the video,

measurements can be performed in only the horizontal

centre part of the lines.

7.2.15 B

The U and V samples from the 4 :2:2 data are filtered

again by a [−1; 0; 9; 16; 9; 0; −1] filter, before being

subsampled by a factor of 2. Bypassing this function keeps

the data in the 4 : 2 : 2 format.

Should it be required to format the data to 8 bits, a choice

can be made between rounding and dithered rounding.

Dithered rounding may be applied in the sense that every

odd output sample has had an addition of 0.25 LSB

(relative to 8 bits) before truncation and every even output

sample has had an addition of 0.75 LSB before truncation.

In this way, normally, correct rounding is realized (no DC

shift). Especially for low frequency signals, the resolution

is increased by a factor of 2 by the high frequency

modulation. The phase of dithering is switched 180° from

line-to-line, field-to-field or frame-to-frame in order to

decrease the visibility of the dithering pattern.

This block also performs the subsampling for multi PIP,

with subsampling factors of 1, 2, 3 and 4.

Another output format at bus C is Differential Pulse Code

Modulation (DPCM) 4 : 2 : 2. This data compression

method is applied on the U and V channels, and gives a

50% data reduction. In this way it is possible to convert a

4:2:2 picture to 2fH using a single 12-bit wide field

memory. This format is especially useful for graphics

conversion with high amplitude and high saturation input

signals. The not connected output pins of bus C including

WEC and IEC (depending on the application) can be set to

3-state to allow short-circuiting of these pins at board

production. Short-circuiting at not connected outputs can

not be tested by BST. For outputs in 3-state mode it is not

allowed to apply voltages higher than V

LACK BAR DETECTION

US C FORMAT (see Table 1)

DDO

+ 0.3 V.

SAA4978H

7.2.16 B

Bus D can handle 4 :1:1 external 8 or 9 bits, 4 : 2 : 2

external 8 or 9 bits, 4 : 2 : 2 internal 9 bits and DPCM

4:2:2.

Bus D is selectable in 1fH and 2fH mode. In 1fH mode the

internal input can also be used.

For dithered 8-bit luminance signals an undither block is

provided that restores the 9th bit for low frequency and low

noise. This is needed before the peaking circuit to prevent

amplification of the1⁄2fs dither modulation.

In the event of 8-bit inputs, the LSB of the input bus should

be externally connected to a fixed logic level.

In the event of a 4:1:1 input, the U and V channels are

reformatted and upsampled by generating the extra

samples with a1⁄16× [−1; 9; 9; −1] filter. The other U and V

samples remain equal to the original 4 :1:1 sample

values.

7.2.17 P

Peaking in the SAA4978H can be used in two ways:

1. The first way is to give the luminance a linear boost of

2. The second way is to use the peaking dynamically, in

Basically, the three peaking filters (1 high-pass and

2 band-pass) filter the incoming luminance signal.

The high-pass filter is made with [−1; 2; −1] coefficients,

giving a maximum throughput at1⁄2fs (equals 8 MHz).

The first band-pass filter has [−1; 0; 2; 0; −1] coefficients,

giving a maximum throughput at1⁄4fs (equals 4 MHz).

The second band-pass filter has a cascade of

[−1; 0; 0; 2; 0; 0; −1] and [1; 2; 1] coefficients, giving a

maximum throughput at 2.38 MHz.

With a separate gain control on each of the peaking filters

[possible gain settings of (0,1⁄16,2⁄16,3⁄16,4⁄16,5⁄16,6⁄

and8⁄16)], a desired frequency characteristic can be

obtained with steps of maximum 2 dB gain difference at

the centre frequencies.

US D REFORMATTER: THE VARIOUS INPUT

FORMATS ARE ALL CONVERTED TO THE INTERNAL

9 BITS 4:2:2(seeTable 1)

EAKING

the higher frequency ranges, which makes no

distinction between small and large details or edges.

order to boost smaller details and provide less gain on

large details and edges. The effect is detail

enhancement without the creation of unnaturally large

overshoots and undershoots on large details and

edges.

16

1999 May 03 14

Philips Semiconductors Product specification

Picture Improved Combined Network

(PICNIC)

The sum of the filter outputs is fed through a coring circuit

with a user definable transfer curve between

−7 and +7 LSB at a 12-bit level. The definition of the coring

LUT is realized with two control registers. Herein, for each

of the points in the transfer curve, the user can define an

output between 0 and the input value. For the LUT

points +7 (and −7), a choice can be made from

(−4) +4 to (−7) +7. By setting control bit CORING to LOW,

the coring transfer curve is switched to a coarse coring

which is only dependent on the threshold (see Fig.13).

The so formed peaking signal can be added to the original

luminance signal, the sum of which then becomes the 9-bit

output signal (black-to-white), with an additional DA shift

fitting within 10 bits.

For dynamic use of the peaking circuit, an additional gain

is provided on the peaking signal. This gain is made

dependent on the energy in the peaking signal.

To overcome an unwanted coring on structured small

signals, the output of the low-pass filter is also used to

monitor if the high frequency contents are large enough to

refrain from coring. Therefore the coring is set off if the HF

energy level rises above a user definable threshold.

SAA4978H

7.2.19 DCTI

The Digital Colour Transient Improvement (DCTI) is

intended for U and V signals originating from a 4:1:1

source. Horizontal transients are detected and enhanced

without overshoots by differentiating, making absolute and

again differentiating the U and V signals separately. This

signal is used as a pointer to make a time modulation.

This results in a 4:4:4 UandV bandwidth. To prevent

third harmonic distortion, typical for this processing, a so

called ‘over the hill protection’ prevents peak signals from

becoming distorted. It is possible to control gain, width,

connect U and V and over the hill range via the

microcontroller.

At the output of the DCTI a post-filter is situated to make a

correction for the simple upsampling in DCTI which is a

linear interpolation [1; 2; 1]. The post-filter coefficients are

[−1; 2; 6; 2; −1], convolution of both filters gives

[−1; 0; 9; 16; 9; 0; −1]. This post-filter should only be used

when the DCTI is off, and the source material is 4 : 2 : 2

bandwidth.

7.2.20 B

ORDER BLANK

Spectral measurements are performed with the

spectr_meas subpart, by calculating the sum of the

absolute values from a chosen one of the three (high-pass

and band-pass) filter outputs over a vertical window in a

video field. With this window it is possible to disable

subtitles. The maximum value of the chosen filter output

within a windowed video field is also monitored. For the

generally lower HF contents of the video signal, a

weighting by a factor 4 can be switched in, while

measuring on the High-Pass Filter (HPF).

7.2.18 N

This non-linear phase filter adjusts for possible group

delay differences in the Y, U and V output channels, and

for sinus x/x bandwidth loss of the ADCs. The filter

coefficients are [−L × (1 − u); 1 + L; −L × u]; where

L determines the strength of the filter and u determines the

asymmetry. The effect of the asymmetry is that for higher

frequencies the delay is decreased for u ≤ 0.5. Settings

are provided for L = 0,1⁄8,2⁄8,3⁄8and u = 0,1⁄4,1⁄2.

ON-LINEAR PHASE FILTER BEFORE DAC

The border and blanking processing is operating at a

4:4:4 level, just before the analog-to-digital conversion.

Here it is possible to generate a blanking window and

within this window a border window. The blanking window

is used to blank the non-visible part of the output to the

clamp level. The border window is the visible part of the

video that contains no video, such as the sides in

compression mode, this part can be programmed to

display any luminance or colour level in an 8-bit accuracy;

pixel repetition is also possible here. In case of multi PIP

this block can generate separation borders in the

horizontal and vertical direction.

1999 May 03 15

Philips Semiconductors Product specification

Picture Improved Combined Network

(PICNIC)

7.3 Analog output blocks

7.3.1 T

Three identical DACs are used to convert Y, U and V with

a 32 or 16 MHz data rate.

7.3.2 A

A 3rd-order linear phase filter is applied to each of the Y,

U and V channels. It provides a notch on f

U and V) to strongly prevent aliasing to low frequencies,

which would be most disturbing. The filters can be

bypassed if external filtering with other characteristics is

desired. Bandwidth and gain accuracy are given in

Chapter 11.

7.3.3 PLL

The PLL consists of a ring oscillator, Discrete Time

Oscillator (DTO) and digital control loop. The PLL

characteristic is controlled by means of the

microcontroller.

7.3.4 SNERT

A SNERT interface is built-in to transform the parallel data

from the microcontroller into 1 or 2 Mbaud switchable

SNERT data. This interface is also capable of reading data

from the SNERT bus should it be required to access read

registers.

The read or write operation must be set by the

microcontroller. When writing to the bus, 2 bytes are

loaded by the microcontroller; one for the address, the

other for the data. When reading from the bus, 1 byte is

loaded by the microcontroller for the address, the received

byte is the data from the addressed SNERT location.

The SNERT interface replaces the standard UART

interface. In contrast to the 80C51 UART interface there

are additional control registers, other I/O pads and no byte

separation time between address and data. After

power-on reset the 1 Mbaud mode is active. Switching

baud rate during transmission should be avoided.

7.3.5 PSP

For dynamically changing data such as timing signals, the

programmable signal positioner generates them on the

basis of parameters sent by the microcontroller. For the

reset function of the microcontroller, a watchdog timer is

also built-in that creates a reset pulse unless it is triggered

by a change in the Bone signal within a preset time

(1.05 s).

RIPLE 10-BIT DIGITAL-TO-ANALOG CONVERSION

NALOG ANTI-ALIASING POST-FILTER

(32 MHz at Y,

clk

SAA4978H

7.3.6 M

The SAA4978H contains an embedded 80C51

microcontroller core including a 1 kbyte RAM and a

32 kbyte ROM. It also includes an I2C-bus user control

interface. For development reasons an external ROM can

be accessed with 64 kbyte maximum size. An external

emulator can be connected.

The main difference to most existing 80C51 derivatives is:

• 768 byte auxiliary RAM from which 128 bytes can be

accessed as subtitle RAM

• Interrupt vector address for the I2C-bus is 33H

• On-chip ROM code protection

• SNERT at 1 or 2 Mbaud with additional Sample

Frequency Registers (SFRs) instead of UART

• Host interface containing all control registers access

e.g. via MOVX instruction.

7.3.7 B

Boundary scan test is implemented, according to

“IEEE standard 1149.1”

digital pins and will cover all connections from the

SAA4978H to other ICs that are also equipped with BST.

The connectivity of the analog YUV input/output pins can

also be tested with the use of BST.

The digital outputs UVAL, UVA0, UVA1, UVA2, UVA3,

YAL, UVCL, UVC0, UVC1, UVC2, UVC3, YCL, WEA,

WEC and IEC can be set in 3-state mode if not connected

in the application. This means that these outputs with

index 0 to 3 are set in 3-state if 4 :1:1 is chosen, and the

outputs with index L are set in 3-state if 8 bits output is

chosen.

7.3.8 P

All digital blocks except PLL are reset by a HIGH level at

the reset pin. Only the watchdog counter is reset by the

falling edge of the reset pulse. The PLL needs no reset.

The frequency guard generates a single reset pulse with a

duration of 0.875 ms when the actual frequency enters the

desired range of 14 to 18 MHz. If the frequency leaves this

range then no reset pulse is generated.

ICROCONTROLLER

OARD LEVEL TESTABILITY

. The boundary scan affects all

OWER-ON RESET

1999 May 03 16

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

1999 May 03 17

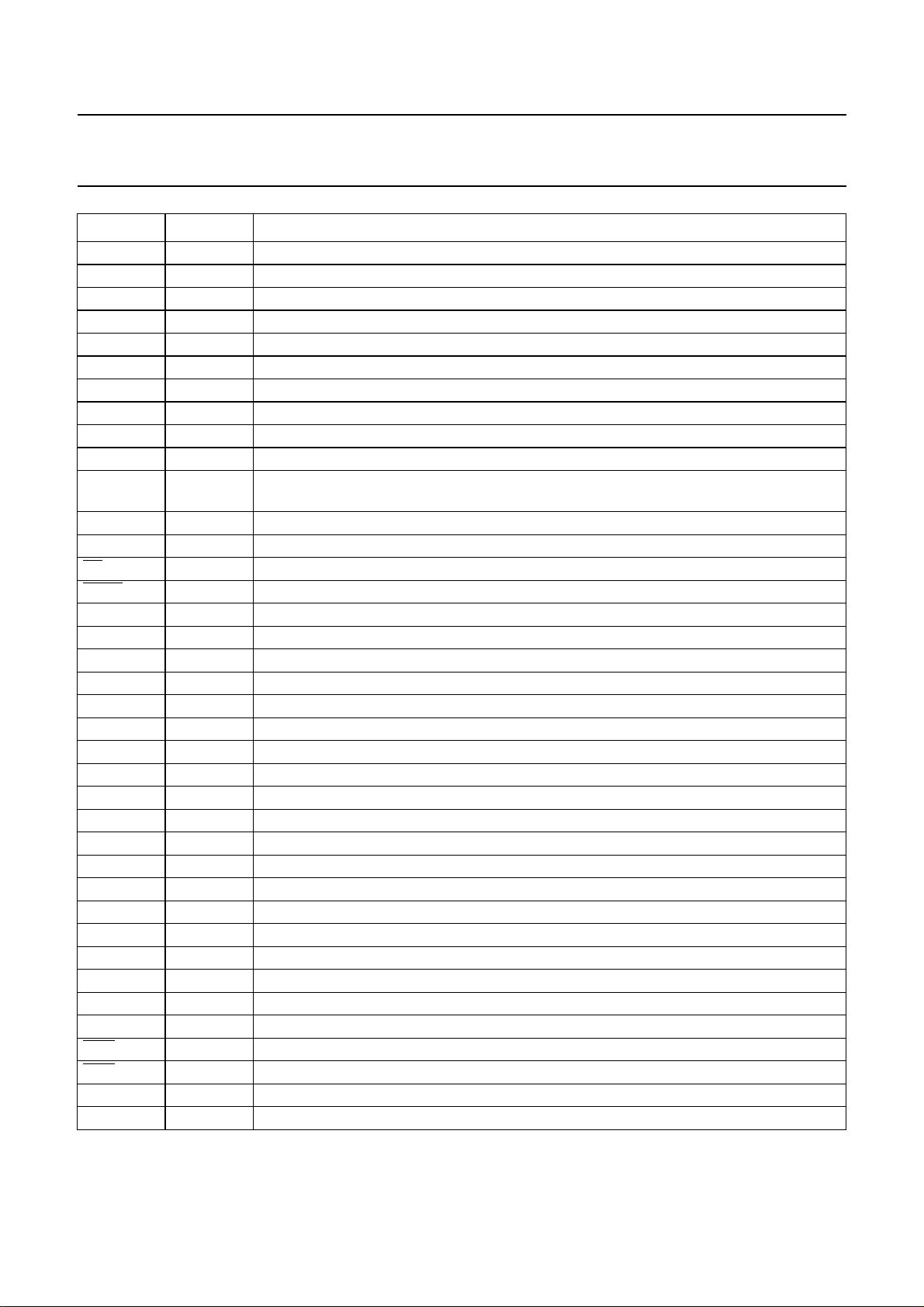

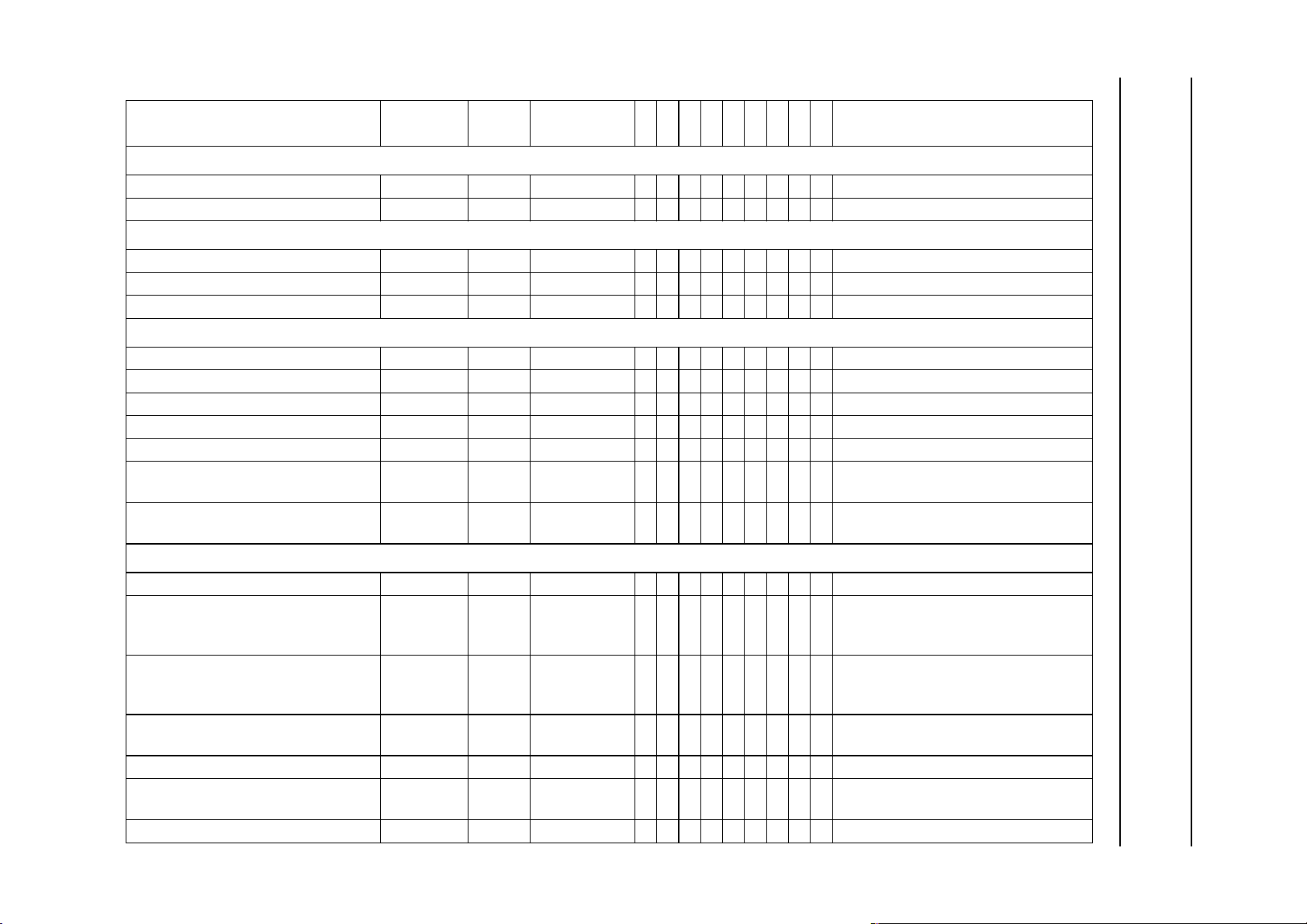

8 CONTROL REGISTER DESCRIPTION

NAME

Clamp registers (clamp position in steps of one pixel, only first quarter of line available)

CLAMP_START 300 write XXXXXXXXclamp start position

CLAMP_STOP 301 write XXXXXXXXclamp stop position

AGC

AGC_GAIN_Y 302 write XXXXXXXXXset Y gain (−3to+6dB)

AGC_GAIN_U 303 write XXXXXXXXXset U gain (−3to+6dB)

AGC_GAIN_V 304 write XXXXXXXXXset V gain (−3to+6dB)

Overflow detection control

YUV_SELECT 305 write X X select ADC (Y, U, V, V)

OVERFLOW_11_HIGH 300 read E XXXXXXXXread HIGH byte level 11

OVERFLOW_11_LOW 301 read E XXXXXXXXread LOW byte level 11

OVERFLOW_10_HIGH 302 read E XXXXXXXXread HIGH byte level 10

OVERFLOW_10_LOW 303 read E XXXXXXXXread LOW byte level 10

OVERFLOW_01_HIGH 304 read E XXXXXXXXread HIGH byte level 01;

OVERFLOW_01_LOW 305 read E XXXXXXXXread LOW byte level 01;

ADDRESS

HEX

READ/

WRITE

DOUBLE

BUFFERED

876543210 DESCRIPTION

(1)

underflow/overflow

underflow/overflow

Philips Semiconductors Product specification

Picture Improved Combined Network

(PICNIC)

Digital front-end

DFRONTEND_CONTROLS1 306 write XXXXXXXX

U_CLAMP_COR_FVAL XXXUclamp correction value

(twos complement) used in external

correction mode

V_CLAMP_COR_FVAL X X X V clamp correction value

(twos complement) used in external

correction mode

UV_COR_MODE X X UV clamp correction mode (internal,

external, keep, keep)

DFRONTEND_CONTROLS2 307 write XXXXXXX

UV_TAU X X select UV clamp time constant

(4, 9, 19 and 39 lines)

Y_DELAY X X select Y delay (−1, 0, 1, 2)

SAA4978H

Loading...

Loading...