Philips saa2023 DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

SAA2023

Drive processor for DCC systems

Preliminary specification

File under Integrated Circuits, IC01

Philips Semiconductors

May 1994

Philips Semiconductors Preliminary specification

Drive processor for DCC systems SAA2023

FEATURES

• Operating supply voltage: 4.5 to 5.5 V

• Low power dissipation: 260 mW at 5.0 V

• Single chip digital equalizer, tape formatting and error

correction

• 8-bit flash analog-to-digital converter (ADC) for low

symbol error rate

• Two switchable Infinite Impulse-Response (IIR) filter

sections

• 10-tap Finite Impulse-Response (FIR) filter per main

data channel, with 8 bit coefficients, identical for all main

channels

• 10-tap FIR filter for the AUX channel

• Analog and digital eye outputs

• Interrupt line triggered by internal auxiliary envelope

processing e.g. label, counter, and others

• Robust programmable digital PLL clock extraction unit

• Low power SLEEP mode

• Slew rate limited Electromagnetic Compatibility (EMC)

friendly output

• Digital Compact Cassette (DCC) optimized error

correction

• Programmable symbol synchronization strategy for tape

input data

• Microcontroller control of capstan servo possible during

playback and recording

• Frequency and phase regulation of capstan servo

during playback

• Choice of Dynamic Random Access Memory (DRAM)

and Static Random Access Memory (SRAM) types for

system Random Access Memory (RAM)

• Scratch pad RAM for microcontroller in system RAM

• Integrated interface for Precision Adaptive Sub-band

Coding (PASC) data bus

• Three wire microcontroller ‘L3’ interface

• Protection against invalid auxiliary data

• Seamless joins between recordings.

GENERAL DESCRIPTION

The SAA2023 performs the drive processor function in the

DCC system. This function is built up of digital equalizer,

error correction and tape formatting functions. The digital

equalizer is intended for use with DCC read amplifiers

TDA1318 or TDA1380. The tape formatting and error

correction circuit is intended for use with PASC ICs

SAA2003 and SAA2013, and write amplifiers TDA1319 or

TDA1381.

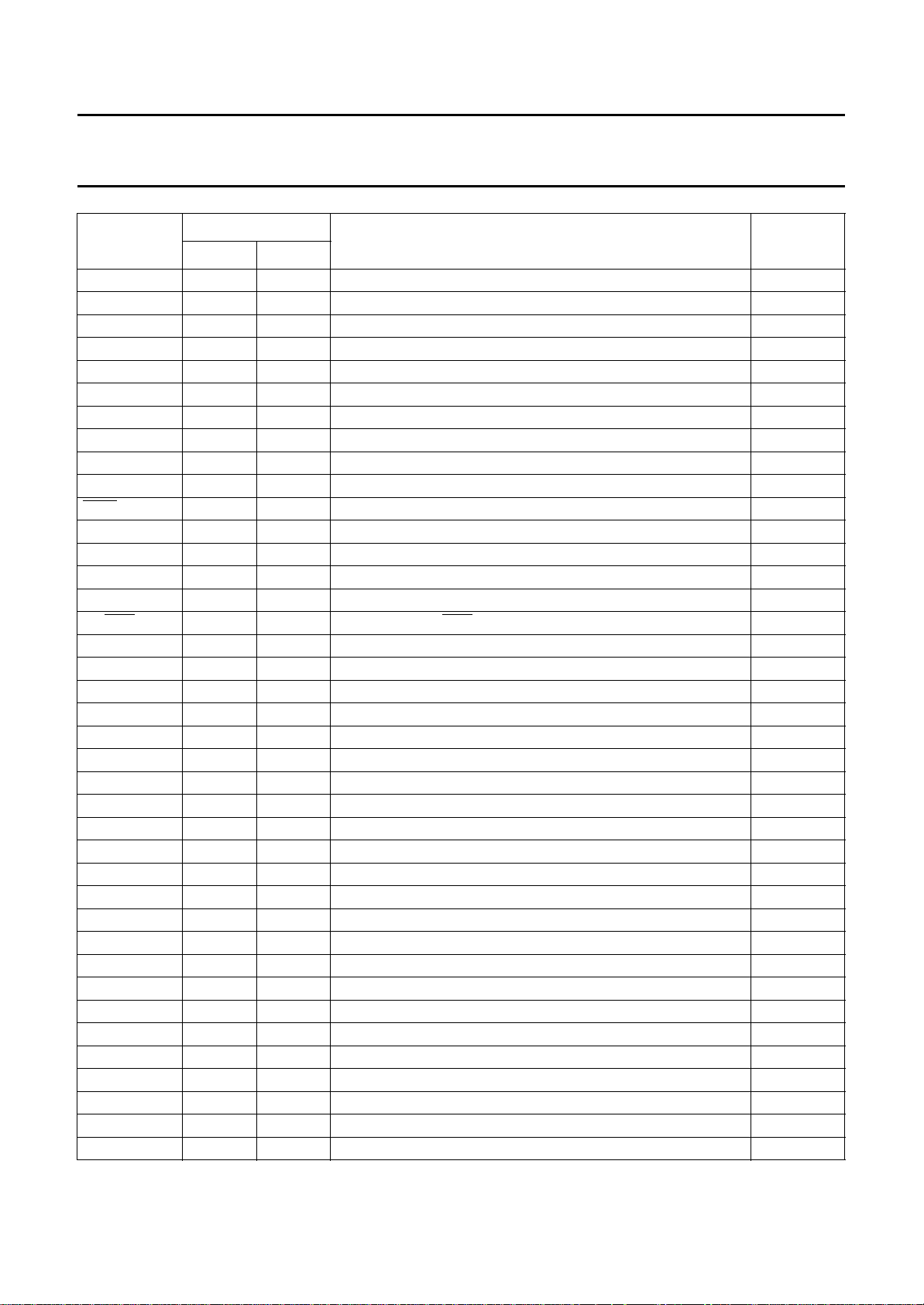

ORDERING INFORMATION

TYPE NUMBER

SAA2023H 80 TQFP80

SAA2023GP 80 QFP80

Note

1. When using reflow soldering it is recommended that the Dry Packing instructions in the

Pocketbook”

May 1994 2

are followed. The pocketbook can be ordered using the code 9398 510 34011.

PACKAGE

PINS PIN POSITION MATERIAL CODE

(1)

(1)

plastic SOT315-1

plastic SOT318-2

“Quality Reference

Philips Semiconductors Preliminary specification

Drive processor for DCC systems SAA2023

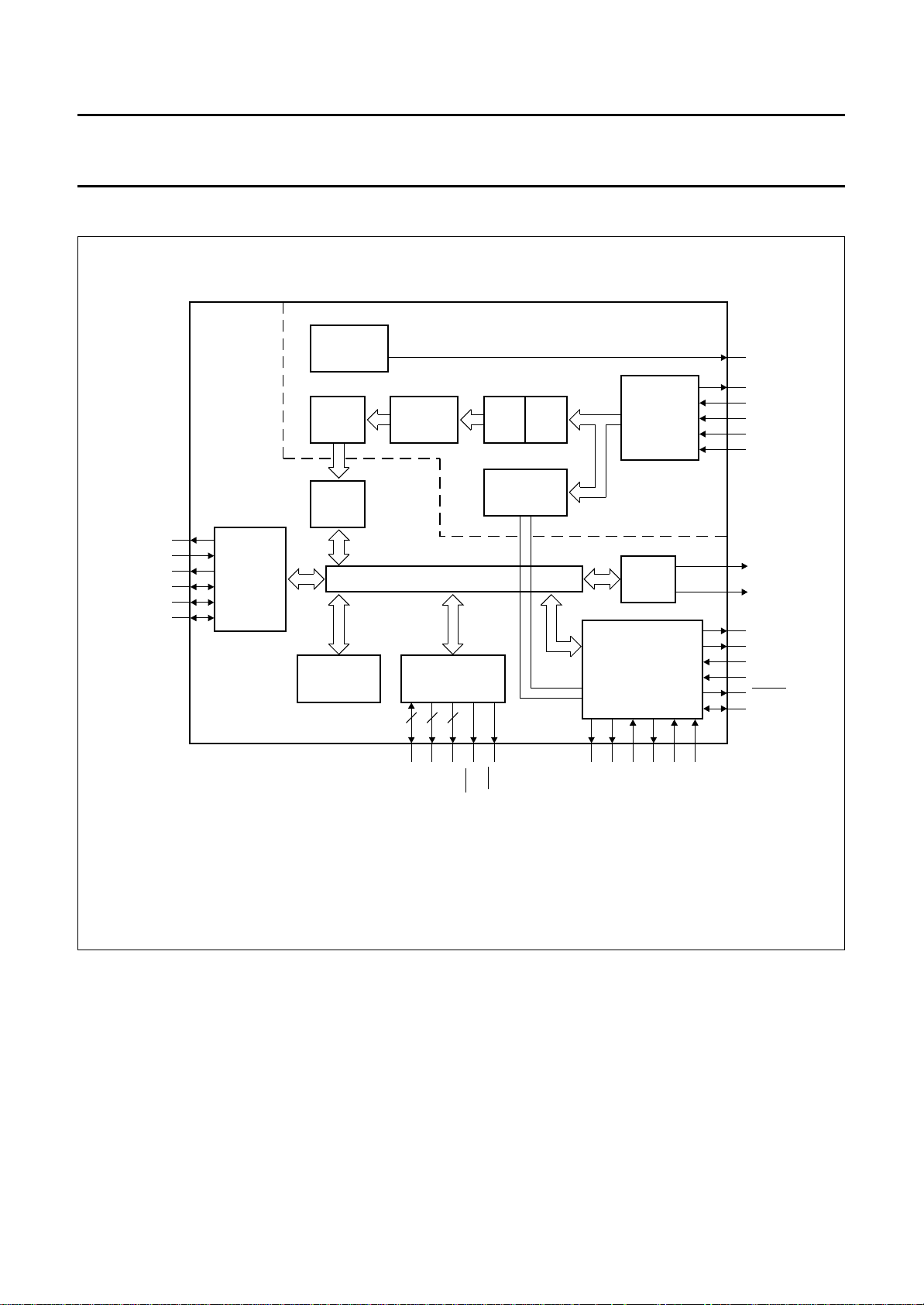

BLOCK DIAGRAM

handbook, full pagewidth

SBDIR

SBMCLK

SBEF

SBDA

SBCL

SBWS

SAA2023

SUB-BAND

2

I S

INTERFACE

DIGITAL-

TO-ANALOG

CONVERTER

PHASE

LOCKED

LOOP

TAPE

INPUT

BUFFER

ERROR

CORRECTOR

ZERO

CROSSING

INTERNAL DATA BUS

RAM

INTERFACE

8116

(1)

FIR

IIR

AUXILIARY

ENVELOPE

DETECTION

ANAEYE

RDSYNC

(2)

ANALOG

TO-DIGITAL

CONVERTER

EQUALIZER

MODULE

TAPE

OUTPUT

BUFFER

CONTROL

INTERFACE

RDMUX

BIAS

V

ref(p)

V

ref(n)

TCLOCK

WDATA

SPEED

URDA

RESET

SLEEP

L3REF

L3DATA

(1) FIR = Finite Impulse-Response.

(2) IIR = Infinite Impulse-Response.

OEN

WEN

D0 to D7

A0 to A10

A11 to A16

Fig.1 Block diagram.

PINO1

PINO2

PINI

L3INT

L3CLK

L3MODE

MGB378

May 1994 3

Philips Semiconductors Preliminary specification

Drive processor for DCC systems SAA2023

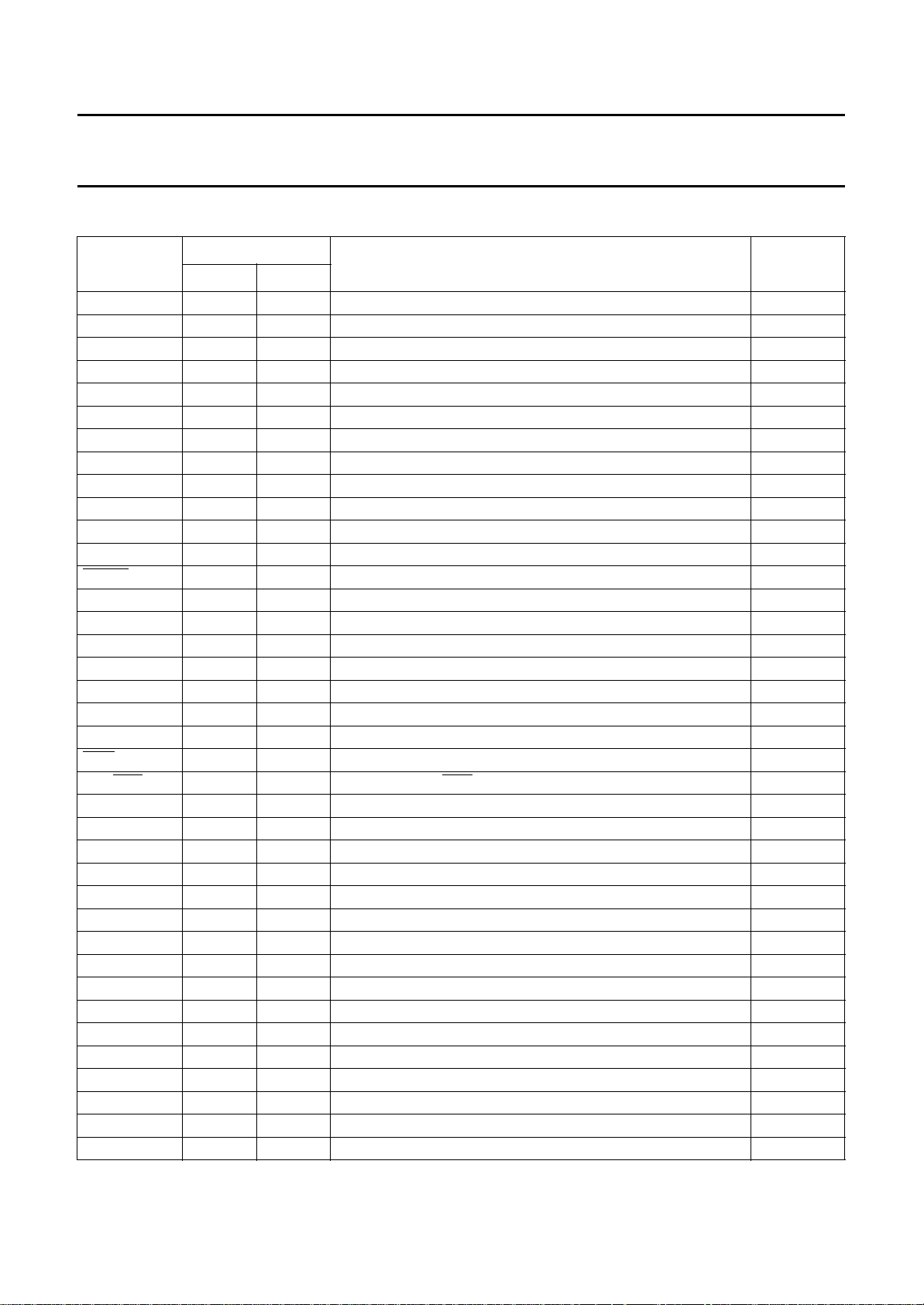

PINNING

SYMBOL

PIN

DESCRIPTION TYPE

(1)

QFP80 TQFP80

SBWS 1 79 word select for sub-band PASC interface I/O (1 mA)

SBCL 2 80 bit clock for sub-band PASC interface I/O (1 mA)

SBDA 3 1 data line for sub-band PASC interface I/O (1 mA)

SBDIR 4 2 direction line for sub-band PASC interface O (1 mA)

SBMCLK 5 3 master clock for sub-band PASC interface I

URDA 6 4 unreliable data O (1 mA)

L3MODE 7 5 mode line for L3 interface I

L3CLK 8 6 bit clock line for L3 interface I

L3DATA 9 7 serial data line for L3 interface I/O (2 mA)

L3INT 10 8 L3 interrupt output O (1 mA)

V

V

DD1

SS1

11 9 digital supply voltage S

12 10 digital ground S

L3REF 13 11 L3 bus timing reference O (1 mA)

RESET 14 12 reset SAA2023 I

SLEEP 15 13 sleep mode selection of SAA2023 I

CLK24 16 14 24.576 MHz clock input I

AZCHK 17 15 channel 0 and channel 7 azimuth monitor O (1 mA)

MCLK 18 16 6.144 MHz clock output O (1 mA)

TEST3 19 17 TEST3 output; do not connect O (1 mA)

ERCOSTAT 20 18 ERCO status, for symbol error rate measurements O (1 mA)

OEN 21 19 output enable for RAM O (2 mA)

RAS 22 20 address SRAM; RAS DRAM O (2 mA)

A10/

V

V

DD2

SS2

23 21 digital supply voltage S

24 22 digital ground S

D7 25 23 data SRAM I/O (4 mA)

D6 26 24 data SRAM I/O (4 mA)

D5 27 25 data SRAM I/O (4 mA)

D4 28 26 data SRAM I/O (4 mA)

D3 29 27 data SRAM; data DRAM I/O (4 mA)

D2 30 28 data SRAM; data DRAM I/O (4 mA)

D1 31 29 data SRAM; data DRAM I/O (4 mA)

V

V

DD7

SS7

32 30 digital supply voltage for RAM S

33 31 digital ground for RAM S

D0 34 32 data SRAM; data DRAM I/O (4 mA)

A0 35 33 address SRAM; address DRAM O (2 mA)

A1 36 34 address SRAM; address DRAM O (2 mA)

A2 37 35 address SRAM; address DRAM O (2 mA)

A3 38 36 address SRAM; address DRAM O (2 mA)

May 1994 4

Philips Semiconductors Preliminary specification

Drive processor for DCC systems SAA2023

SYMBOL

DESCRIPTION TYPE

QFP80 TQFP80

A4 39 37 address SRAM; address DRAM O (2 mA)

PIN

V

V

SS3

DD3

40 38 digital ground S

41 39 digital supply voltage S

A5 42 40 address SRAM; address DRAM O (2 mA)

A6 43 41 address SRAM; address DRAM O (2 mA)

A7 44 42 address SRAM; address DRAM O (2 mA)

A12/PINO5 45 43 address SRAM; Port expander output 5 O (2 mA)

A14/PINO1 46 44 address SRAM; Port expander output 1 O (2 mA)

A16/PINO3 47 45 address SRAM; Port expander output 3 O (2 mA)

A15/PINO4 48 46 address SRAM; Port expander output 4 O (2 mA)

WEN 49 47 write enable for RAM O (2 mA)

A13/PINO2 50 48 address SRAM; Port expander output 2 O (2 mA)

A8 51 49 address SRAM; address DRAM O (2 mA)

V

DD4

V

SS4

CAS 54 52 address SRAM; CAS for DRAM O (2 mA)

A9/

52 50 digital supply voltage S

53 51 digital ground S

A11 55 53 address SRAM O (2 mA)

SPEED 56 54 Pulse Width Modulation (PWM) capstan control output for deck O

PINO2 57 55 Port expander output 2 O

(1 mA)

t

(1 mA)

t

WDATA 58 56 serial output to write amplifier O (1 mA)

TCLOCK 59 57 3.072 MHz clock output for tape I/O O (1 mA)

V

SS5

V

DD5

TEST2 62 60 TEST mode select; do not connect I

RDMUX 63 61 analog multiplexed input from read amplifier I

V

ref(p)

V

ref(n)

SUBSTR 66 64 substrate connection I

BIAS 67 65 bias current for ADC I

V

SSA

V

DDA

ANAEYE 70 68 analog eye pattern output O

60 58 digital ground S

61 59 digital supply voltage S

64 62 ADC positive reference voltage I

65 63 ADC negative reference voltage I

68 66 analog ground S

69 67 analog supply voltage S

pd

A

A

A

A

A

A

RDSYNC 71 69 synchronization output for read amplifier O (1 mA)

V

V

DD6

SS6

72 70 digital supply voltage S

73 71 digital ground S

CHTST1 74 72 channel test pin 1 O (1 mA)

CHTST2 75 73 channel test pin 2 O (1 mA)

TEST0 76 74 TEST mode select; do not connect I

TEST1 77 75 TEST mode select; do not connect I

pd

pd

(1)

May 1994 5

Philips Semiconductors Preliminary specification

Drive processor for DCC systems SAA2023

SYMBOL

PIN

DESCRIPTION TYPE

(1)

QFP80 TQFP80

PINI 78 76 Port expander input I

PINO1 79 77 Port expander output 1 O (1 mA)

SBEF 80 78 sub-band PASC error flag line O (1 mA)

Note

1. I = input; IA= analog input; Ipd= input with pull-down resistance; I/O = bidirectional; O = output; OA= analog output;

Ot= 3-state output; S = supply.

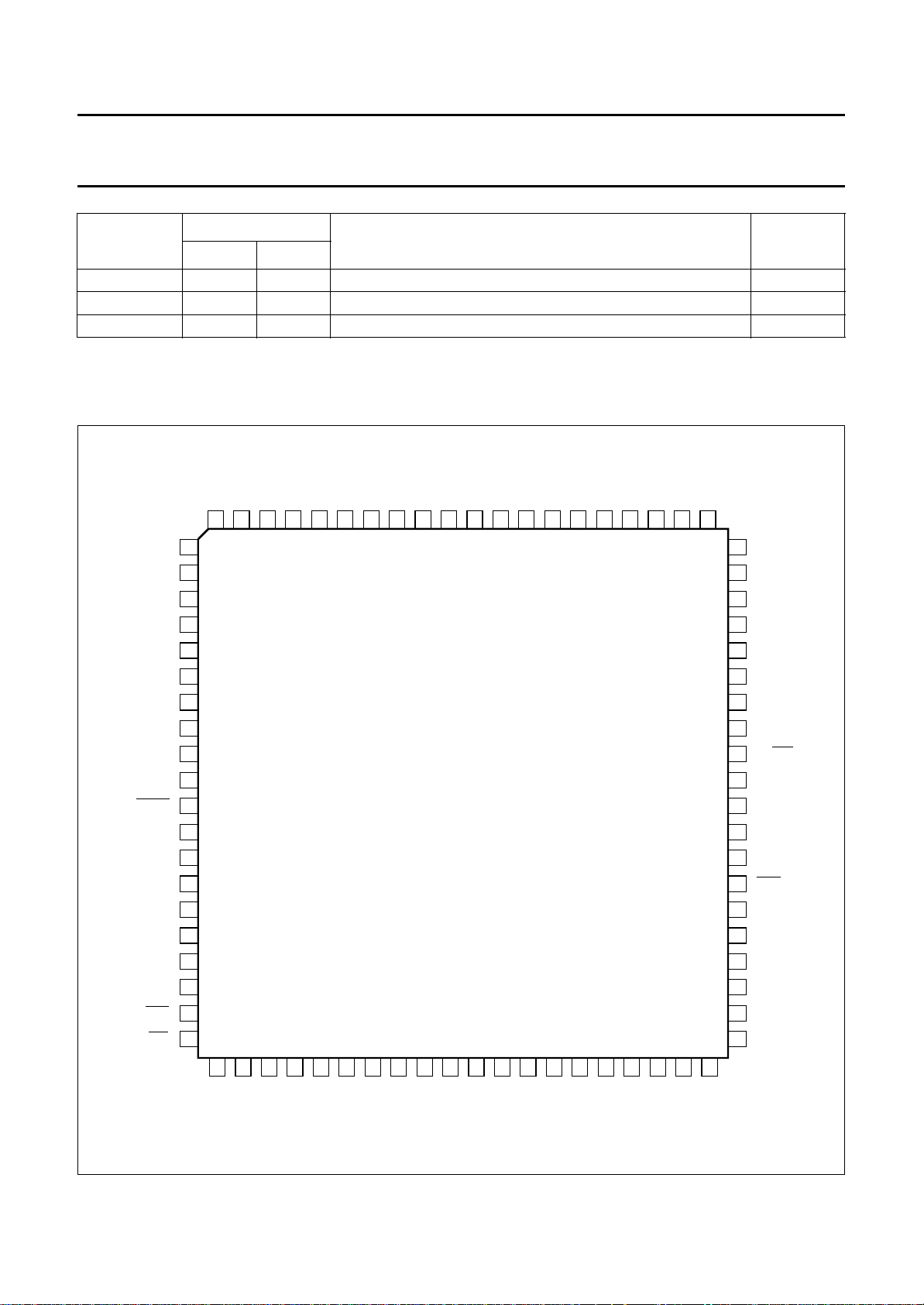

handbook, full pagewidth

SBDA

SBDIR

SBMCLK

URDA

L3MODE

L3CLK

L3DATA

L3INT

V

DD1

V

SS1

L3REF

RESET

SLEEP

SBCL

80

79

1

2

3

4

5

6

7

8

9

10

11

12

13

PINO1

78

77

SBEF

SBWS

PINI

76

TEST1

75

74

CHTST1

CHTST2

73

72

SAA2023

TEST0

V

71

SS6

V

70

DD6

RDSYNC

ANAEYE

69

68

V

67

DDA

V

SSA

66

BIAS

65

ref(n)Vref(p)

V

SUBSTR

64

63

62

RDMUX

61

60

59

58

57

56

55

54

53

52

51

50

49

48

TEST2

V

DD5

V

SS5

TCLOCK

WDATA

PINO2

SPEED

A11

A9/CAS

V

SS4

V

DD4

A8

A13/PINO2

MCLK

OEN

14

15

16

17

18

19

20

CLK24

AZCHK

TEST3

ERCOSTAT

A10/RAS

May 1994 6

21

DD2

V

SS2

V

47

WEN

A15/PINO4

46

A16/PINO3

45

A14/PINO1

44

A12/PINO5

43

A7

42

A6

41

25

26

D4

27

D3

23

D7

24

D6

D5

22

28

D2

29

D1

V

30

DD7

31

SS7

V

32

D0

33

A0

34

A1

35

A2

36

A3

37

A4

38

SS3

V

39

DD3

V

40

A5

MGB379

Fig.2 Pin configuration (SOT315-1; TQFP80).

Loading...

Loading...