Philips saa2013 DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

SAA2013

Adaptive allocation and scaling for

PASC coding in DCC systems

Preliminary specification

File under Integrated Circuits, IC01

Philips Semiconductors

May 1994

Philips Semiconductors Preliminary specification

Adaptive allocation and scaling for PASC

coding in DCC systems

FEATURES

• Wide operating voltage range: 2.7 to 5.5 V

• Low power consumption: 13 mW; 3.0 V

• Low power decode mode: 1 mW; 5.0 V

• Sleep mode for low power and low Electromagnetic

Interference (EMI)

• Sophisticated allocation algorithm

• Optimum sound quality

• Three-wire L3 bus microcontroller interface

• Stereo or 2-channel mono recording

• Small surface mounted package (QFP; SOT307).

ORDERING INFORMATION

TYPE NUMBER

PINS PIN POSITION MATERIAL CODE

SAA2013H 44 QFP

GENERAL DESCRIPTION

The SAA2013 performs the adaptive allocation and

scaling function in the Precision Adaptive Sub-band

Coding (PASC) system. It is not required in playback only

applications, and is only used during recording. To

complete the PASC processor, a SAA2003 stereo filter

and codec is required.

(1)

SAA2013

PACKAGE

plastic SOT307-2

Note

1. When using reflow soldering it is recommended that the Dry Packing instructions in the

Pocketbook”

are followed. The pocketbook can be ordered using the code 9398 510 34011.

“Quality Reference

May 1994 2

Philips Semiconductors Preliminary specification

Adaptive allocation and scaling for PASC

coding in DCC systems

BLOCK DIAGRAM

V

handbook, full pagewidth

L3MODEM

L3CLKM

L3DATAM

L3MODEC

L3CLKC

L3DATAC

V

DD1

14 24 40

3

4

MICROCONTROLLER

5

9

10

11

DD2

SFC

BUS

V

DD3

BUS

SAA2013

ALLOCATION AND SCALE FACTOR

FS256

CONTROL

AND

SYNC

FRESET

FDIR

39

COMPUTATION

37 36 35 34

COMPENSATION

DELAY

FSYNC

FDAI

SAA2013

32

FDCL

31

FDWS

30

SLEEP

26

CLK24

23

RESET

33

FDAO

6 25 44

V

V

SS1

SS2

V

SS3

Fig.1 Block diagram.

222120

NODONE RESOL0 RESOL1

MGB355

May 1994 3

Philips Semiconductors Preliminary specification

Adaptive allocation and scaling for PASC

SAA2013

coding in DCC systems

PINNING

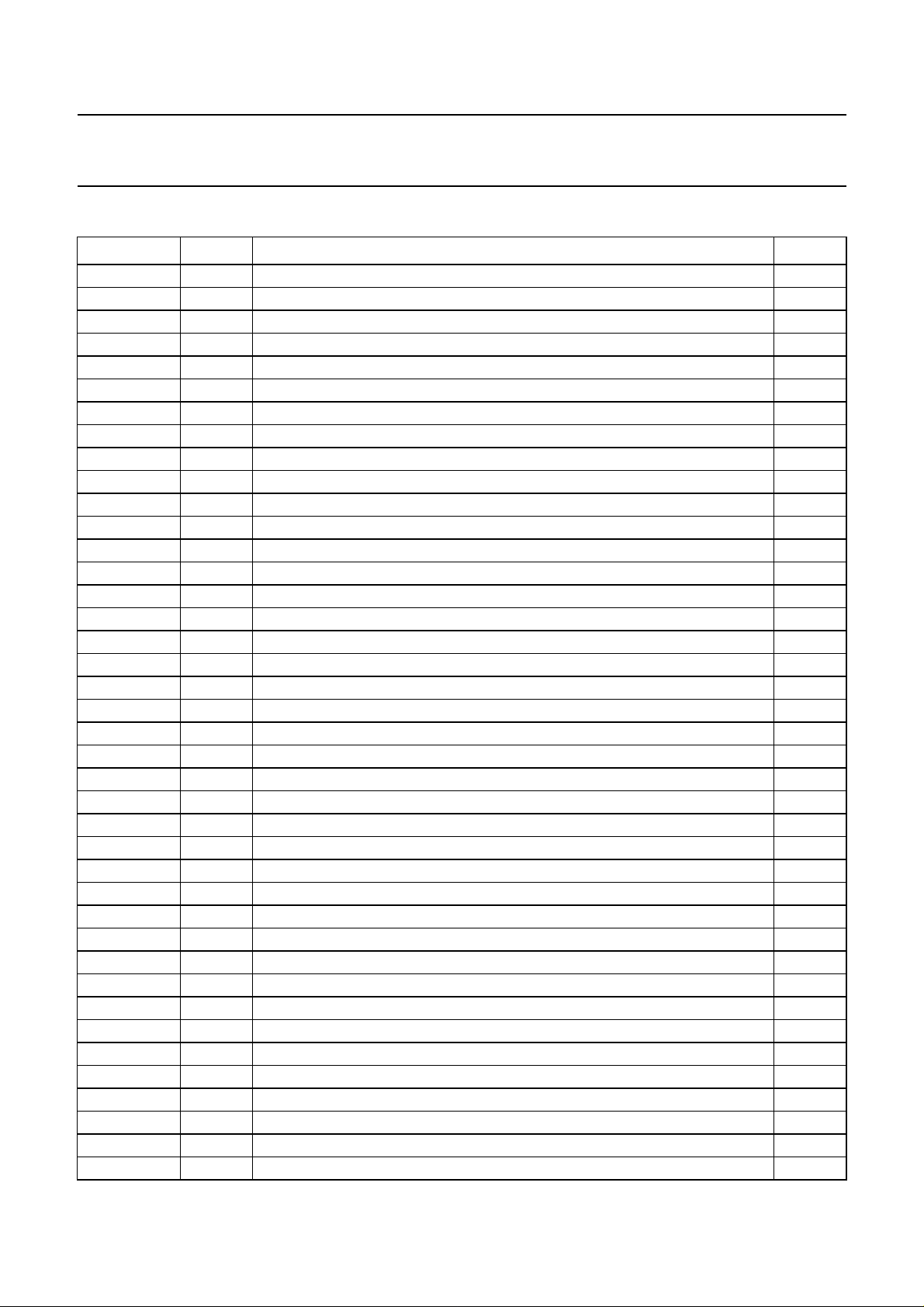

SYMBOL PIN DESCRIPTION TYPE

TEST10 1 test input; connect to V

TEST11 2 test input; connect to V

L3MODEM 3 microcontroller interface mode input I

L3CLKM 4 microcontroller interface clock input I

L3DATAM 5 microcontroller interface data 3-state input/output I/O

V

SS1

6 supply ground −

TEST12 7 test output; do not connect O

TEST13 8 test output; do not connect O

L3MODEC 9 codec interface mode output O

L3CLKC 10 codec interface clock output O

L3DATAC 11 codec interface data 3-state input/output I/O

TEST1 12 test output; do not connect O

TEST2 13 test output; do not connect O

V

DD1

14 supply voltage −

TEST3 15 test mode input; connect to V

TEST4 16 test mode input; connect to V

TEST5 17 test input; connect to V

TEST6 18 test input; connect to V

TEST7 19 test input; connect to V

NODONE 20 nodone state selection input; connect to V

RESOL0 21 resolution selection 0 input I

RESOL1 22 resolution selection 1 input I

RESET 23 reset input; active HIGH I

V

V

DD2

SS2

24 supply voltage −

25 supply ground −

CLK24 26 24.576 MHz clock input I

LOWPWR 27 low power decode select input I

POR 28 power on reset input I

TEST8 29 test input; connect to V

SLEEP 30 sleep mode select input I

FDWS 31 filtered data word select I

FDCL 32 filtered data clock I

FDAO 33 filtered data output O

FDAI 34 filtered data input I

FSYNC 35 sub-band synchronization on filtered I

FRESET 36 reset signal input from SAA2003 I

FDIR 37 filtered data direction input I

TEST9 38 test input; connect to V

FS256 39 system clock input; 256 × sample frequency (f

V

DD3

40 supply voltage −

SS

SS

SS

SS

SS

SS

SS

DD

DD

DD

2

S bus I

)I

s

I

I

I

I

I

I

I

I

I

I

May 1994 4

Philips Semiconductors Preliminary specification

Adaptive allocation and scaling for PASC

SAA2013

coding in DCC systems

SYMBOL PIN DESCRIPTION TYPE

n.c. 41 not connected −

n.c. 42 not connected −

n.c. 43 not connected −

V

SS3

handbook, full pagewidth

44 supply ground −

TEST10

TEST11

L3MODEM

L3CLKM

L3DATAM

V

SS1

TEST12

TEST13

L3MODEC

L3CLKC

L3DATAC

SS3

V

n.c.

n.c.

44

43

42

1

2

3

4

5

6

7

8

9

10

11

DD3

n.c.

V

41

40

SAA2013

FS256

39

TEST9

38

FDIR

37

FRESET

FSYNC

36

35

FDAI

34

33

32

31

30

29

28

27

26

25

24

23

FDAO

FDCL

FDWS

SLEEP

TEST8

POR

LOWPWR

CLK24

V

SS2

V

DD2

RESET

12

13

14

15

16

DD1

V

TEST1

TEST2

TEST3

TEST4

Fig.2 Pin configuration.

May 1994 5

17

TEST5

18

TEST6

19

TEST7

20

21

RESOL0

NODONE

22

RESOL1

MGB356

May 1994 6

FUNCTIONAL DESCRIPTION

coding in DCC systems

RAM

41464

analog

output

analog

input

IEC958

analog CC

L output

analog CC

R output

L

DAC

TDA1305

R

SFC3

SAA2003

STEREO

FILTER CODEC

2

ADAS3

SAA2013

ADAPTIVE

ALLOCATION

L

R

baseband

I S

ADC

SAA7366

DIGITAL

AUDIO I/O

TDA1315

2

filtered I S

AUDIO IN/OUT PASC PROCESSOR

sub-band

2

I S

BUFFER

64K x 4

DRP

SAA2023

OR

SAA3323

DRIVE

PROCESSOR

search data

TAPE DRIVE PROCESSING

speed control

WRAMP

TDA1381

WRITE AMP.

RDAMP

TDA1380

READ AMP.

FIXED

HEAD

CAPSTAN

DRIVE

TAPE

MECHANICS

DRIVERS

detect

switch

Philips Semiconductors Preliminary specification

Adaptive allocation and scaling for PASC

Fig.3 DCC system block diagram.

handbook, full pagewidth

SYSTEM

MICROCONTROLLER

SYSTEM CONTROL

MBD620

SAA2013

Philips Semiconductors Preliminary specification

Adaptive allocation and scaling for PASC

coding in DCC systems

PASC processor

The PASC processor is a dedicated Digital Signal

Processor (DSP) engine which efficiently codes digital

audio data at a bit rate of 384 kbits/s without affecting the

sound quality. This is achieved using an efficient adaptive

data notation and by only encoding the audio information

which can be heard by the human ear.

The audio data is split into 32 equal sub-bands during

encoding. For each of the sub-bands a masking threshold

is calculated. The samples from each of the sub-bands are

included in the PASC data with an accuracy that is

determined by the available bit-pool and by the difference

between the signal power and the masking threshold for

that sub-band. In decode, the sub-band signals are

reconstructed into the full bandwidth audio signal.

The stereo filter codec performs the splitting (encoding)

and reconstruction (decoding), including the necessary

formatting functions. During encoding, the adaptive

allocation and scaling circuit calculates the required

accuracy (bit allocation) and scale factors of the

sub-band samples.

Decode/encode control

SAA2013

to determine the operation mode. When FDIR is HIGH,

SAA2013 is in decode mode. When FDIR is LOW the

SAA2013 is in encode mode. See Fig.4.

Reset

When used with low-power mode disabled

(LOWPWR = VSS), and with the SLEEP input LOW,

SAA2013 is reset if the RESET pin is held HIGH for at least

5 periods of the CLK24 clock, see Fig.5. SAA2013 defaults

to decode mode. When in low-power mode, the RESET

pin is disabled.

Sleep mode

Sleep mode is entered by taking the SLEEP input HIGH

with the LOWPWR pin connected to V

FS256 are stopped internally to the SAA2013, the 3-state

buffers will have a high impedance, and outputs will freeze

in the same state as just before the sleep mode became

active (clocks stopped). To come out of sleep mode, the

SLEEP input must be taken LOW again. To clear data

present from before sleep was entered, this should be

followed by a reset, see Fig.5.

; CLK24 and

SS

Selection of decode or encode is controlled using FRESET

and FDIR. FRESET causes a general reset. The FDIR

signal is sampled at the falling edge of the FRESET signal

t

handbook, full pagewidth

FRESET

FDIR

H

t

su

Fig.4 FDIR and FRESET timing.

t

h

MGB357

May 1994 7

Philips Semiconductors Preliminary specification

Adaptive allocation and scaling for PASC

coding in DCC systems

handbook, full pagewidth

Low-power decode mode

Low-power decode mode is made available by connecting

the LOWPWR pin to VDD. With LOWPWR = VDD,

low-power decode mode is entered 9 cycles of CLK24

after the SLEEP input is taken HIGH. In low-power decode

mode, the L3 bus connections are connected straight

trough the SAA2013, which is effectively bypassed. The

compensation delay connection between pins FDAI and

FDAO is no longer needed by the SAA2003, and CLK24

and FS256 are stopped internally to the SAA2013.

SLEEP

RESET

CLK24

t

d

Fig.5 SLEEP and RESET timing.

handbook, halfpage

t

h

MGB359

150

k

SAA2013

MGB358

V

DD

µ1 F

Ω

POR

V

DD

V

SS

V

SS

To get out of low-power decode mode, it is necessary to

take SLEEP LOW, FDIR LOW, and FRESET HIGH (in a

normal application taking FDIR LOW and FRESET HIGH

can be achieved by setting SAA2003 into encode mode),

SAA2013 then performs an internal reset, and defaults to

normal decode mode. The RESET pin does not reset the

circuit from low-power decode mode.

Power-On Reset (POR)

When low-power decode mode is enabled

(LOWPWR = V

), a power-on reset circuit is required to

DD

ensure that the internal clocks are connected correctly at

power-on. A suitable circuit is shown in Fig.6. This circuit

will correctly reset the internal clock connection provided

that the nominal value of the VDD supply is reached within

40 ms at power-on.

May 1994 8

Fig.6 POR circuit.

Encode mode

In encode mode the SAA2013 receives sub-band filtered

samples from SAA2003 on the FDAI pin. The SAA2013

has to collect a complete frame of sub-band data before

the allocation and scale factor information can be

calculated. So that the allocation and scale factor

information is available in the same time frame as the

audio samples at the output, the sub-band filtered samples

are delayed by 480 FDWS periods.

One FDWS period is equal to where f

1

--- f

s

is the audio

s

sample rate of 32, 44.1 or 48 kHz. The delayed samples

are passed to the codec part of SAA2003 on the

FDAO pin.

Philips Semiconductors Preliminary specification

Adaptive allocation and scaling for PASC

coding in DCC systems

For each sub-band frame, SAA2013 calculates the

allocation and scale factor index information required by

the SAA2003. In order to synchronize the codec part of

SAA2003, SAA2013 frequently requests status

information from the codec. It monitors sample frequency,

emphasis information and stereo mode, and uses the

ready-to-receive bit of the codec to determine when to

transfer information.

Decode mode

In decode the SAA2003 will transfer samples from FDAI to

FDAO with a delay of 480 FDWS periods. Settings and

status information can be sent to SAA2003 via SAA2013,

but the SAA2013 does not itself act on this information.

Transfer of this information is automatically synchronized

to the ready-to-receive bit of SAA2003 by SAA2013.

Filtered data interface

The filtered data interface signals are given in Table 2.

SAA2013

Audio sample resolution section

The SAA2013 is designed for operation with audio input

sources of 14, 15, 16 or 18-bit resolution.

For optimum audio performance the bit allocation

algorithm of the SAA2013 can be varied to suit the bit

resolution of the audio source. This is done with the pins

RESOL0 and RESOL1 as shown in Table 1.

Table 1 Resolution set by pins RESOL0 and RESOL1.

RESOLUTION RESOL0 RESOL1

16 bits 0 0

18 bits 0 1

14 bits 1 0

15 bits 1 1

Table 2 Filtered data interface signals.

PIN INPUT/OUTPUT FUNCTION FREQUENCY

FDWS input filtered data interface word select f

FDCL input filtered data interface bit clock 64f

FDAI input filtered data input −

FDAO output filtered data output −

FSYNC input filtered data sub-band synchronization −

The filtered data interface transfers sub-band filtered

samples between the stereo filter codec SAA2003 and

SAA2013. The interface is similar to a normal I2S interface,

consisting of clock (FDCL), data (FDAI/FDAO) and word

select lines (FDWS), except that the samples sent

represent signals divided into 32 sub-bands. One frame of

data consists of 12 samples from 32 sub-bands for both

left and right channels, i.e.: 768 audio samples. Each

audio sub-band sample is represented by a 24-bit two’s

complement number.

The order in which the samples are sent is shown in

Table 3.

For two channel mono, the order is the same, but with

Channel 1 samples in the place of left and Channel 2

samples in place of right.

Table 3 Order of samples.

SUB-BAND 001122...3131

Channel L R L R L R ... L R

Sample 000000...00

111111...11

222222...22

...........

...........

11 11 11 11 11 11 ... 11 11

The signal FSYNC is used between each PASC frame to

indicate the sending of samples for sub-band 0 (Fig.7).

s

s

May 1994 9

Philips Semiconductors Preliminary specification

Adaptive allocation and scaling for PASC

coding in DCC systems

channel

andbook, full pagewidth

FDWS

FDCL

FDWS

FSYNC

sub-band

left

23 22 21 20

1 bit

L

FDCL

FDAO

FDAI

FDWS

R

31 0 1 31 0

L

t

cH

t

d3

32 bits

01

R

t

d4

L

T

c

t

cL

t

su1

SAA2013

right

7 bit

R

t

h1

L

R

L

MGB360

FSYNC

timing

R

Fig.7 Filtered interface format.

Control interfaces

Two 3-wire control interfaces are provided (referred to as

‘L3’ interfaces). One is connected to the system

microcontroller (L3MODEM, L3CLKM, L3DATAM where

‘M’ represents microcontroller), the other to SAA2003

(L3MODEC, L3CLKC, L3DATAC where ‘C’ represents

codec). In general, control data is passed between

SAA2003 and the microcontroller via SAA2013. This

ensures that the microcontroller is buffered from the

time-critical SAA2013 to SAA2003 interface during

encode.

The SAA2013 does not interpret the data from the

microcontroller interface.

Status information from the codec is interpreted to ensure

that SAA2013 quickly acts upon the status of SAA2003.

The L3 bus operation is shown in Fig.8. There are three

modes:

1. Address.

2. Data.

3. Halt.

Each interface operates as either a master or a slave,

where the master provides L3CLK and L3MODE. For the

microcontroller to SAA2013 interface, the microcontroller

is the master. For the SAA2013 to SAA2003 interface,

SAA2013 is the master.

May 1994 10

Loading...

Loading...