Philips saa2002 DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

SAA2002

Stereo filter and codec

Product specification

Supersedes data of February 1993

File under Integrated Circuits, Miscellaneous

Philips Semiconductors

December 1993

Philips Semiconductors Product specification

Stereo filter and codec SAA2002

FEATURES

• Stereo filtering and codec functions in a single chip

• Drive processing interface

• Filtered data interface

• Baseband audio data interface

• LT interface to microcontroller

• Clock generator

• Low operating voltage capability.

GENERAL DESCRIPTION

The SAA2002 performs the sub-band filtering and audio

frame codec functions in a Precision Adaptive Sub-band

Coding (PASC) system. It is capable of functioning as a

stand-alone decoder, but requires the addition of an

Adaptive Allocation and Scale factor processor (SAA2012)

in order to perform PASC encoding in a DCC

record system.

ORDERING INFORMATION

EXTENDED TYPE

NUMBER

SAA2002GP 44 QFP

Note

1. When using reflow soldering it is recommended that the Dry Packing instructions in the Quality Reference

Pocketbook are followed. The pocketbook can be ordered using the code 9398 510 34011.

PINS PIN POSITION MATERIAL CODE

(1)

PACKAGE

plastic SOT205AG

December 1993 2

Philips Semiconductors Product specification

Stereo filter and codec SAA2002

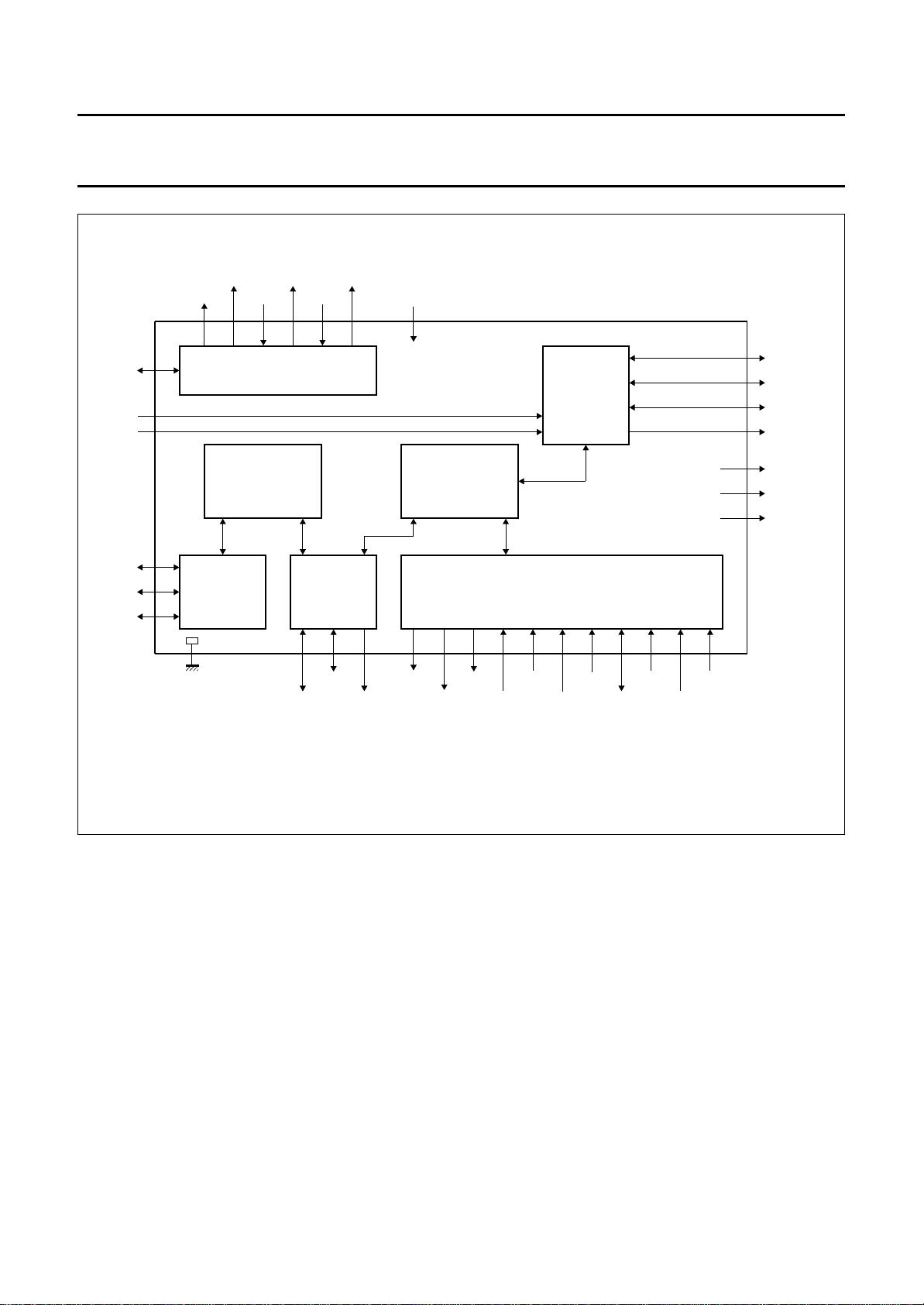

FS256

SBDIR

SBEF

SWS

SCL

SDA

CLK24 X22OUT X24OUT

CLK22 X22IN X24IN

38 39 40 41 42 43 28,44

1

7

11

20

19

21

CLOCK GENERATOR

SUB-BAND

PROCESSOR

BASEBAND

SERIAL

INTERFACE

5,37

V

SS

STEREO

FILTER

FILTERED

DATA

INTERFACE

FDAF

FDAC FSYNC

V

DD

15

FRESET

SAA2002

PASC

CODEC

PROCESSOR

14 13 36 35 34 33 32 22 29 618 17 16

SYNCDAI

FDIR

SUB-BAND

SERIAL

INTERFACE

MICROPROCESSOR

INTERFACE & CONTROL

LTCLK

LTCNT1 LTENSFC

PWRDWN

LTDATA

RESET

8

SBDA

9

SBCL

10

SBWS

12

SBMCLK

2

MUTEDAC

3

DEEMDAC

4

ATTDAC

MEA655 - 1

URDALTCNT0

Fig.1 Block diagram.

December 1993 3

Philips Semiconductors Product specification

Stereo filter and codec SAA2002

PINNING

SYMBOL PIN DESCRIPTION

FS256 1 filtered-I2S clock; 256 x fs; 12 mA, 3-state output + CMOS input with pull-down

MUTEDAC 2 DAC control/output expander

DEEMDAC 3 DAC control/output expander

ATTDAC 4 DAC control/output expander

V

SS

URDA 6 unreliable drive processing data; CMOS level

SBDIR 7 sub-band I

SBDA 8 sub-band I

SBCL 9 sub-band I

SBWS 10 sub-band I

SBEF 11 sub-band I

SBMCLK 12 sub-band I

SYNCDAI 13 Digital Audio Interface (DAI) synchronization pulse

FDIR 14 filtered-I

FRESET 15 reset signal for SAA2012

FSYNC 16 filtered-I

FDAF 17 filtered-I

FDAC 18 filtered-I

SCL 19 I

SWS 20 I

SDA 21 I

PWRDWN 22 sleep mode; CMOS level

DSC4 23 test pin; not to be connected

DSC3 24 test pin; not to be connected

DSC2 25 test pin; not to be connected

DSC1 26 test pin; not to be connected

DSC0 27 test pin; not to be connected

V

DD

RESET 29 system reset input; CMOS level with pull-down and hysteresis

T1 30 test pin; not to be connected

T0 31 test pin; not to be connected

LTDATA 32 LT interface data; 4 mA, 3-state output + CMOS input with pull-down

LTCLK 33 LT interface bit clock input; CMOS level

LTENSFC 34 LT interface enable input; CMOS level

LTCNT0 35 LT interface control input; CMOS level

LTCNT1 36 LT interface control input; CMOS level

V

SS

CLK22 38 22.5792 MHz buffered output

CLK24 39 24.576 MHz buffered output

5 supply ground (0 V)

2

S direction: (SWBS, SBCL, SBDA); CMOS level

2

S data; 4 mA, 3-state output + CMOS input with pull-down

2

S bit-clock; 4 mA, 3-state output + CMOS input with pull-down

2

S word select; 4 mA, 3-state output + CMOS input with pull-down

2

S byte error flag input; CMOS level

2

S clock; 6.144 MHz locked to FS256; 8 mA, 3-state output + CMOS input

with pull-down

2

S direction: (FDAC, FDAF and SDA)

2

S synchronization signal for SAA2012

2

S sub-band filter data; 4 mA, 3-state output + CMOS input with pull-down

2

S sub-band codec data; 4 mA, 3-state output + CMOS input with pull-down

2

S bit-clock; 4 mA, 3-state output + CMOS input with pull-down

2

S word select; 4 mA, 3-state output + CMOS input with pull-down

2

S baseband data filter; 4 mA, 3-state output + CMOS input with pull-down

28 supply voltage (+5 V)

37 supply ground (0 V)

December 1993 4

Philips Semiconductors Product specification

Stereo filter and codec SAA2002

SYMBOL PIN DESCRIPTION

X22IN 40 22.5792 MHz crystal input

X22OUT 41 22.5792 MHz crystal output

X24IN 42 24.576 MHz crystal input

X24OUT 43 24.576 MHz crystal output

V

DD

44 supply voltage (+5 V)

FS256

MUTEDAC

DEEMDAC

ATTDAC

V

SS

URDA

SBDIR

SBDA

SBCL

SBWS

SBEF

FDAF

V

CLK22

38

18

FDAC

SS

37

19

SCL

LTCNT0

LTCNT1

36

35

21

20

SDA

SWS

LTENSFCPWRDWN

34

33

32

31

30

29

28

27

26

25

24

23

22

LTCLK

LTDATA

T0

T1

RESET

V

DD

DSC0

DSC1

DSC2

DSC3

DSC4

MEA640 - 1

DD

X24IN

42

14

FDIR

X22IN

X22OUT

41

40

SAA2002

15

16

FSYNC

FRESET

CLK24

39

17

V

X24OUT

44

43

1

2

3

4

5

6

7

8

9

10

11

12

13

SBMCLK

SYNCDAI

December 1993 5

Fig.2 Pin configuration.

Philips Semiconductors Product specification

Stereo filter and codec SAA2002

and

drive

capstan

heads

tape

write

TDA1319

TDA1316 or

speed control

2

codec

SAA2002

stereo filter

I S

(sub-band)

read

SAA2032

SAA2022

adaptive

SAA2012

TDA1318

TDA1317 or

digital

equalizer

RAM

scale factors

allocation and

TAPE DRIVE PROCESSING

256 kbits

MEA695 - 2

MICROCONTROLLER

Fig.3 DCC data flow diagram.

December 1993 6

2

I S

ADC

SAA7360

RECORDING + PLAY BACK

input

analog

DAC

SAA7323

output

analog

DAIO

TDA1315

digital input

digital output

AUDIO INPUT/OUTPUT PASC PROCESSING

Philips Semiconductors Product specification

Stereo filter and codec SAA2002

FUNCTIONAL DESCRIPTION

PASC

Precision Adaptive Sub-band Coding achieves highly

efficient digital encoding of audio signals by using an

algorithm based on the characteristics of the human

auditory system.

The broad-band audio signal is split into 32 sub-band

signals during encoding. For each of the sub-band signals

the masking threshold is calculated. The samples of the

sub-bands are incorporated in the PASC signal with an

accuracy that is determined by the signal to masking

threshold ratio for that sub-band.

During decoding, the sub-band signals are reconstructed

and combined into a broadband audio signal. The

integrated filter processor performs the splitting (encoding)

and joining (decoding) including the corresponding

formatting functions.

For encoding, a SAA2012 is necessary to calculate the

masking threshold and required accuracy of the

sub-band samples.

Encoding (see Fig.4)

An encoding algorithm table is used during the recording

process but, due to the Adaptive Allocation functions of the

SAA2012, this may change with every frame. The table is

therefore calculated for each frame by the SAA2012 and

then transferred to the SAA2002.

A frame contains 2 x 384 samples of Left and Right audio

data. This results in 12 samples per sub-band

(32 sub-bands). The samples of the greatest amplitude

are used to determine the scale factor for a given

sub-band. All samples are then scaled to represent a

fraction of the greatest amplitude.

Once scaled, the samples are quantified to reduce the

number of bits to correspond with the allocation table as

calculated by the SAA2012. Synchronization and coding

information data is then added to result in a fully encoded

PASC signal.

This is followed by a process of multiplication to provide

de-quantification and de-scaling of the PASC samples.

The decoded sub-band samples, which are represented in

24-bit two’s complement notation, are processed by the

sub-band filters and reconstituted into a single digital

audio signal.

RESET

Reset must be active from system power-up, or the end of

sleep mode (falling edge of PWRDWN), for a period

equivalent to 24 cycles of CLK24 plus the crystal oscillator

start-up time.

Sleep mode

A HIGH input applied to the PWRDWN pin will halt all

internally generated clock signals. As a result, chip activity

will halt completely with outputs frozen in the state which

was current at the time of PWRDWN activation. The

bi-directional outputs: LTDATA, FDAC, FDAF, SDA,

SBWS, SBCL and SBDA will be in 3-state.

Crystal Oscillators

A 24.576 MHz crystal together with some external

components form the 24.576 MHz oscillator

(pins 42 and 43). Similarly a 22.5792 MHz oscillator (pins

40 and 41) is performed by similar peripheral components

together with an appropriate crystal (see Fig.6).

The component values shown apply only to crystals from

the Philips 4322 156 series which exhibit an equivalent

series resistance of ≤ 40 Ω.

Decoding (see Fig.5)

All essential information (synchronization, system

information, scale factors and encoded sub-band

samples) are conveyed by incoming data. Decoding is

repeated for every frame.

After sync and coding information, allocation data and the

scale factors are used to correctly fill the scale factor array.

December 1993 7

Philips Semiconductors Product specification

Stereo filter and codec SAA2002

ndbook, full pagewidth

allocation information

and scale factor indices

SYNC AND

CODING

INFORMATION

quantified samples

FORMATTER

MEA803 - 2

PASC

OUTPUT

DATA

baseband

samples

from SAA2012

SUB-BAND

FILTER

sub-band

samples

ALLOCATION AND

SCALE FACTOR

INFORMATION

TABLE

SCALING AND

QUANTIFICATION

andbook, full pagewidth

PASC

data

input

FORMATTER

DE–

sync/coding

allocation

scale factor

quantified

samples

Fig.4 Encoding mode.

CONTROL

SCALE

FACTOR

ARRAY

AND ALLOCATION

DE-QUANTIZATION

MULTIPLY

OUTPUT

CONTROL

sub-band

samples

MEA804 - 1

SUB-BAND

FILTER

baseband

samples

December 1993 8

Fig.5 Decoding mode.

Philips Semiconductors Product specification

Stereo filter and codec SAA2002

C2 33 pF

C1 33 pF

C3 33 pF

C4 33 pF

22.5792

MHz

X1

24.576

MHz

X2

R1

1 MΩ

R2 220Ω

R4

1 MΩ

R3 1 kΩ

X22IN

X22OUT

X24IN

X24OUT

40

41

42

43

Component values apply only to crystals from the Philips 4322 156 series.

Fig.6 Crystal oscillator components.

channel

left 32 bits

SAA2002

MEA641 - 1

right

SWS

SCL

1

SDA

bit :

MSB LSB

18 bits

4

0001716151

210

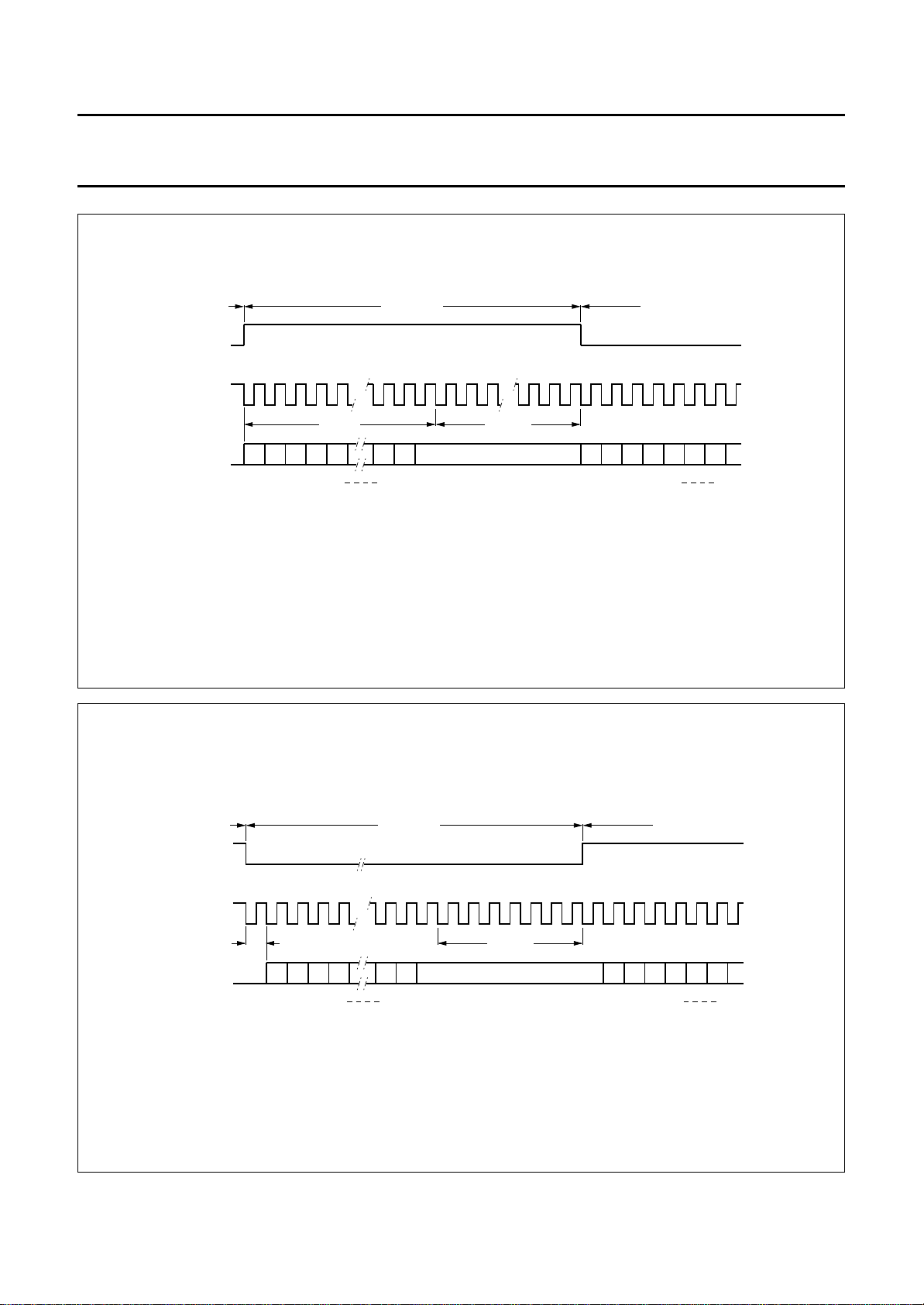

Fig.7 Transfer of SDA data (standard I2S default format).

December 1993 9

13 bits

1716151

MSB

4

MLA923 - 2

Philips Semiconductors Product specification

Stereo filter and codec SAA2002

channel

SWS

SCL

SDA

bit :

left 32 bits

18 bits

1

0001716151

3

4

MSB LSB

210

14 bits

Fig.8 Transfer of SDA data (alternative format).

1716151

MSB

right

4

MLA924 - 2

channel

SWS

SCL

FDAC/

FDAF

bit :

1

2322212

MSB LSB

0

left 32 bits

02010

0

Fig.9 Transfer of FDAF and FDAC (filtered) data.

December 1993 10

7 bits

2322212

MSB

right

0

MLA925 - 2

Philips Semiconductors Product specification

Stereo filter and codec SAA2002

channel

SWS

FSYNC

sub-band

LRLLLLLLRRRRRR

31 0 1 31 0 1

Fig.10 SWS related to phase of FSYNC.

Baseband Interface Signals

Table 1 Interface between the SAA2002 and the baseband input/output circuitry.

SIGNAL MODE DESCRIPTION

SWS bi-directional

SCL bi-directional

SDA bi-directional

word (channel) select

bit clock

baseband data

MBC148 - 1

OPERATING

FREQUENCY

f

s

64f

s

−

FDIR output

decoding mode (direction control)

The SWS signal indicates the channel of the sample signal

(either Left or Right) and is equal to the sampling

frequency fs.

Operating at a frequency of 64 x fs that is used for

sampling, the bit clock dictates that each SWS period

contains 64 SDA data bits. Of these, a maximum of 36 are

used to transfer data (samples may have a length up to

December 1993 11

−

18-bits). Samples are transferred most significant bit

(MSB) first. Both SWS and SDA change state at the

negative edge of SCL.

This baseband data is transferred between the SAA2002

and the input/output using either standard I2S (default) or

the alternative format shown in Fig.8.

Philips Semiconductors Product specification

Stereo filter and codec SAA2002

Interface between SAA2002 and SAA2012

2

Table 2 Filtered I

S interface.

SIGNAL MODE DESCRIPTION

SWS bi-directional word select (common to I

2

S) f

s

SCL bi-directional bit clock (common to I2S) 64f

FDAC bi-directional codec data −

FDAF bi-directional filter data −

FSYNC output synchronization fs/32

Filtered data is transferred between SAA2002 filter/codec

functions and the SAA2012 using the format shown

in Fig.9.

PASC CODED INTERFACE

The interface that carries the P ASC coded signal uses the

signals as indicated in Table 3.

The frequency of the SWS signal is equal to the sample

frequency fs and the bit clock SCL is 64 times the sample

frequency. Each period of SWS contains 64 data-bits, 48

of which are used to transfer data. The half period in which

Table 3 The PASC I

SIGNAL MODE DESCRIPTION

2

S interface.

SWS is LOW is used to transfer the information of the Left

channel while the following half period during which SWS

is HIGH carries the data of the Right channel. The 24-bit

samples are transferred Most Significant Bit (MSB) first.

This bit is transferred in the bit clock period with a 1-bit

delay following the change in SWS. Both SWS and FDAF/

FDAC change state at the negative edge of SCL.

The SAA2012 may be synchronized to the sub-band

codec using the FSYNC signal, which defines the SWS

period in which the samples of sub-band 0 (containing the

lowest frequency components) are transferred

SBWS bi-directional word selection

SBCL bi-directional bit clock

SBDA bi-directional sub-band coded data

SBEF input error signal

Operation is further controlled by:

• SBDIR: input; direction of data flow

• URDA: input; unreliable encoded data signal.

(see Fig.9).

SAA2012

AND INPUT/OUTPUT MODE CONTROL

The SBMCLK signal is the main frequency from which

other clock signals are derived. In encode mode this

The operation of SAA2012 and the input/output circuitry is

controlled by three signals shown in Table 4.

division is performed internally. In decode mode the

external source should provide SBWS and SBCL. The

frequency of the signal is equal to 1/32nd of the bit rate.

The frequency of the bit clock SBCL is twice that of the

FRESET and SYNCDAI are given whenever:

bit rate.

• FS256, SCL and SWS outputs switch between high and

low impedance

• FS256 frequency is changed

(12.288/11.2896/8.192 MHz)

• FDIR is switching

• The bit rate is changing

• System reset is active.

OPERATING

FREQUENCY

s

December 1993 12

Loading...

Loading...