Philips SA7025DK Datasheet

INTEGRATED CIRCUITS

SA7025

Low-voltage 1GHz fractional-N

synthesizer

Product specification 1996 Aug 6

IC17 Data Handbook

Philips Semiconductors Product specification

SA70251GHz low-voltage Fractional-N synthesizer

DESCRIPTION

The SA7025 is a monolithic low power, high performance dual

frequency synthesizer fabricated in QUBiC BiCMOS technology.

Featuring Fractional-N division with selectable modulo 5 or 8

implemented in the Main synthesizer to allow the phase detector

comparison frequency to be five or eight times the channel spacing.

This feature reduces the overall division ratio yielding a lower noise

floor and faster channel switching. The phase detectors and charge

pumps are designed to achieve phase detector comparison

frequencies up to 5MHz. A triple modulus prescaler (divide by

64/65/72) is integrated on chip with a maximum input frequency of

1.04GHz. Programming and channel selection are realized by a

high speed 3-wire serial interface.

FEA TURES

•Operation up to 1.04GHz

•Fast locking by “Fractional-N” divider

•Auxiliary synthesizer

•Digital phase comparator with proportional and integral charge

pump output

•High speed serial input

•Low power consumption

•Programmable charge pump currents

•Supply voltage range 2.7 to 5.5V

•Excellent input sensitivity: V

RF_IN

= –20dBm

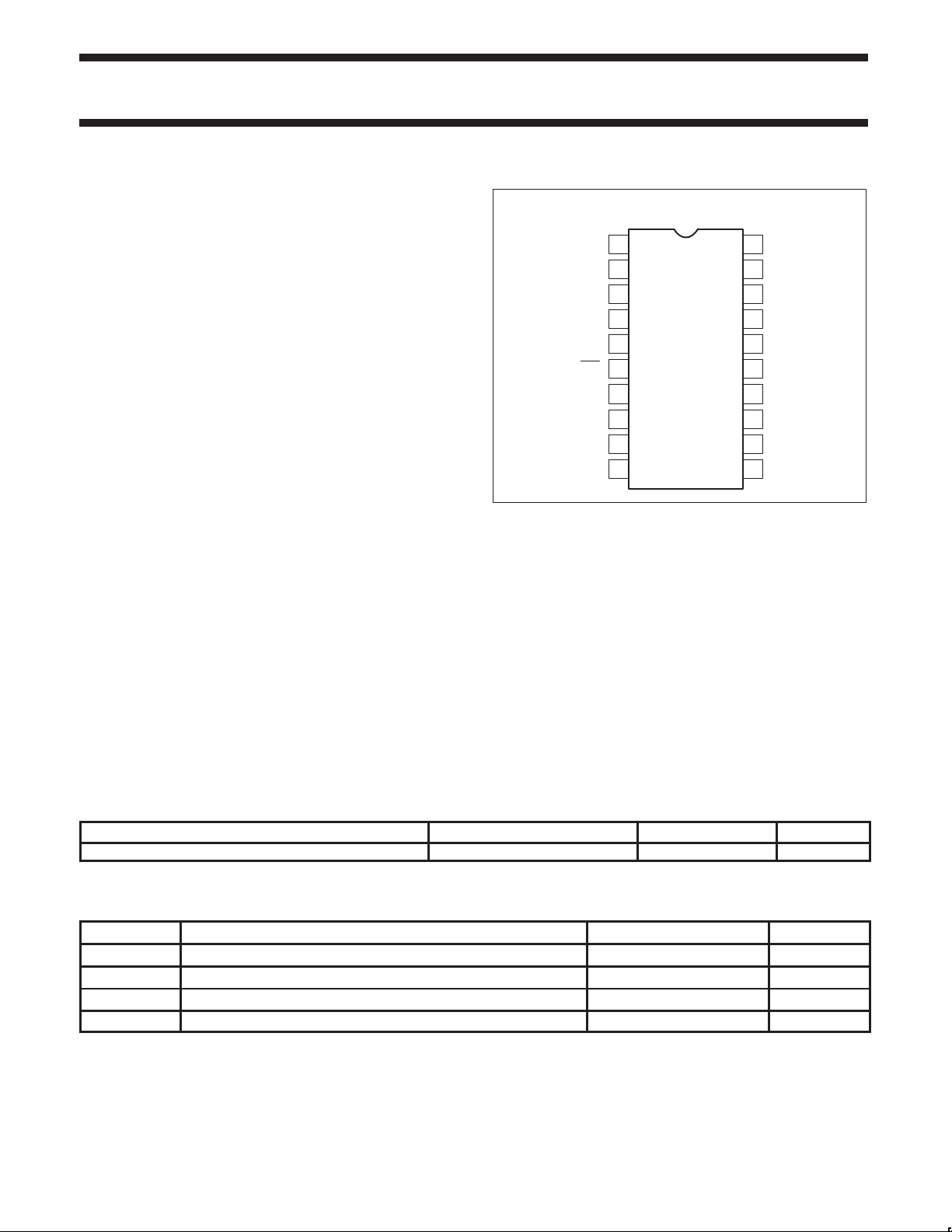

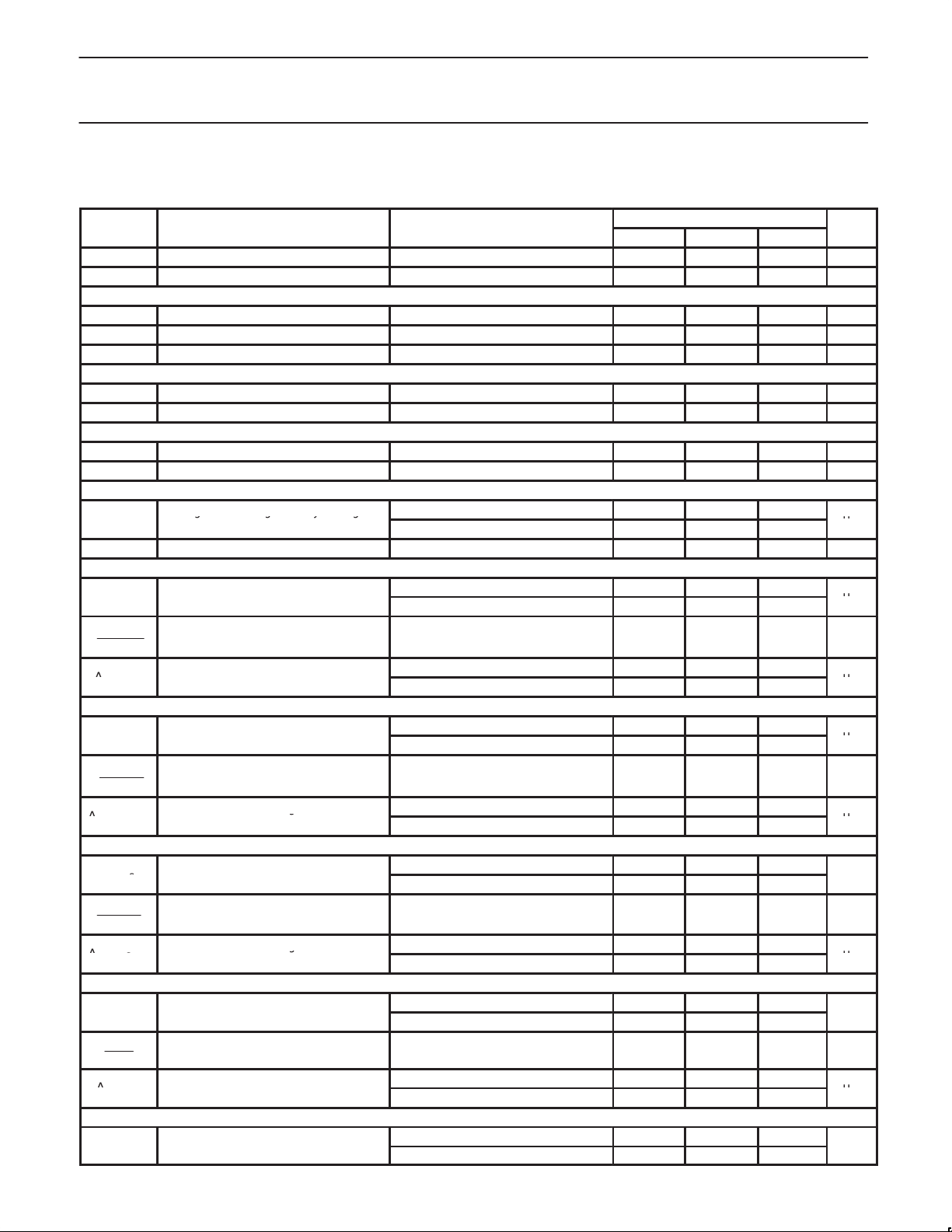

PIN CONFIGURATION

CLOCK

STROBE

1

DATA

2

3

V

4

SS

RF

5

IN

RF

6

IN

7

V

CCP

8

REF

IN

9

RA

AUX

10

IN

Figure 1. Pin Configuration

DK Package

V

20

DD

TEST

19

LOCK

18

17

RF

16

RN

15

V

DDA

PHP

14

PHI

13

12

V

SSA

PHA

11

SR00600

APPLICATIONS

•NADC (North American Digital Cellular)

•PDC (Personal Digital Cellular)

•Cellular radio

•Spread-spectrum receivers

ORDERING INFORMATION

DESCRIPTION TEMPERATURE RANGE ORDER CODE DWG #

20-Pin Plastic Shrink Small Outline Package (SSOP) –40 to +85°C SA7025DK SOT266-1

ABSOLUTE MAXIMUM RATINGS

SYMBOL PARAMETER RATING UNITS

V Supply voltage, VDD, V

T

V

STG

T

IN

A

Voltage applied to any other pin -0.3 to (VDD + 0.3) V

Storage temperature range -65 to +150 °C

Operating ambient temperature range -40 to +85 °C

NOTE: Thermal impedance (θJA) = 117°C/W. This device is ESD sensitive.

DDA

, V

CCP

-0.3 to +6.0 V

1996 Aug 6 853-1786 17157

2

Philips Semiconductors Product specification

SA70251GHz low-voltage Fractional-N synthesizer

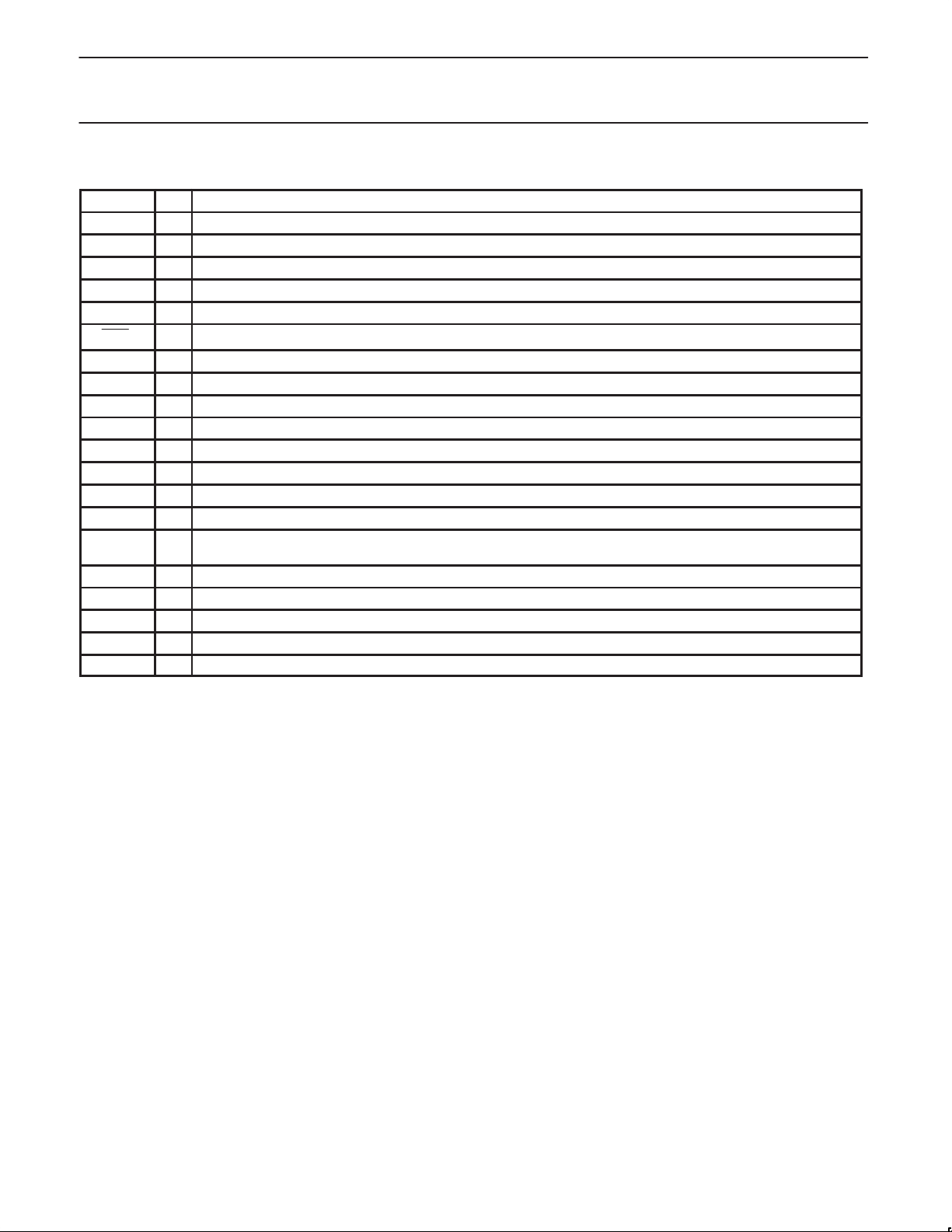

PIN DESCRIPTIONS

Symbol Pin Description

CLOCK 1 Serial clock input

DATA 2 Serial data input

STROBE 3 Serial strobe input

V

SS

RF

IN

RF

IN

V

CCP

REF

RA 9 Auxiliary current setting; resistor to V

AUX

PHA 11 Auxiliary phase detector output

V

SSA

PHI 13 Integral phase detector output

PHP 14 Proportional phase detector output

V

DDA

RN 16 Main current setting; resistor to V

RF 17 Fractional compensation current setting; resistor to V

LOCK 18 Lock detector output

TEST 19 Test pin; connect to V

V

DD

4 Digital ground

5 Prescaler positive input

6 Prescaler negative input

7 Prescaler positive supply voltage. This pin supplies power to the prescaler and RF input buffer

8 Reference divider input

IN

SSA

10 Auxiliary divider input

IN

12 Analog ground

15 Analog supply voltage. This pin supplies power to the charge pumps, Auxiliary prescaler, Auxiliary and Reference

buffers.

SSA

SSA

DD

20 Digital supply voltage. This pin supplies power to the CMOS digital part of the device

1996 Aug 6

3

Philips Semiconductors Product specification

SA70251GHz low-voltage Fractional-N synthesizer

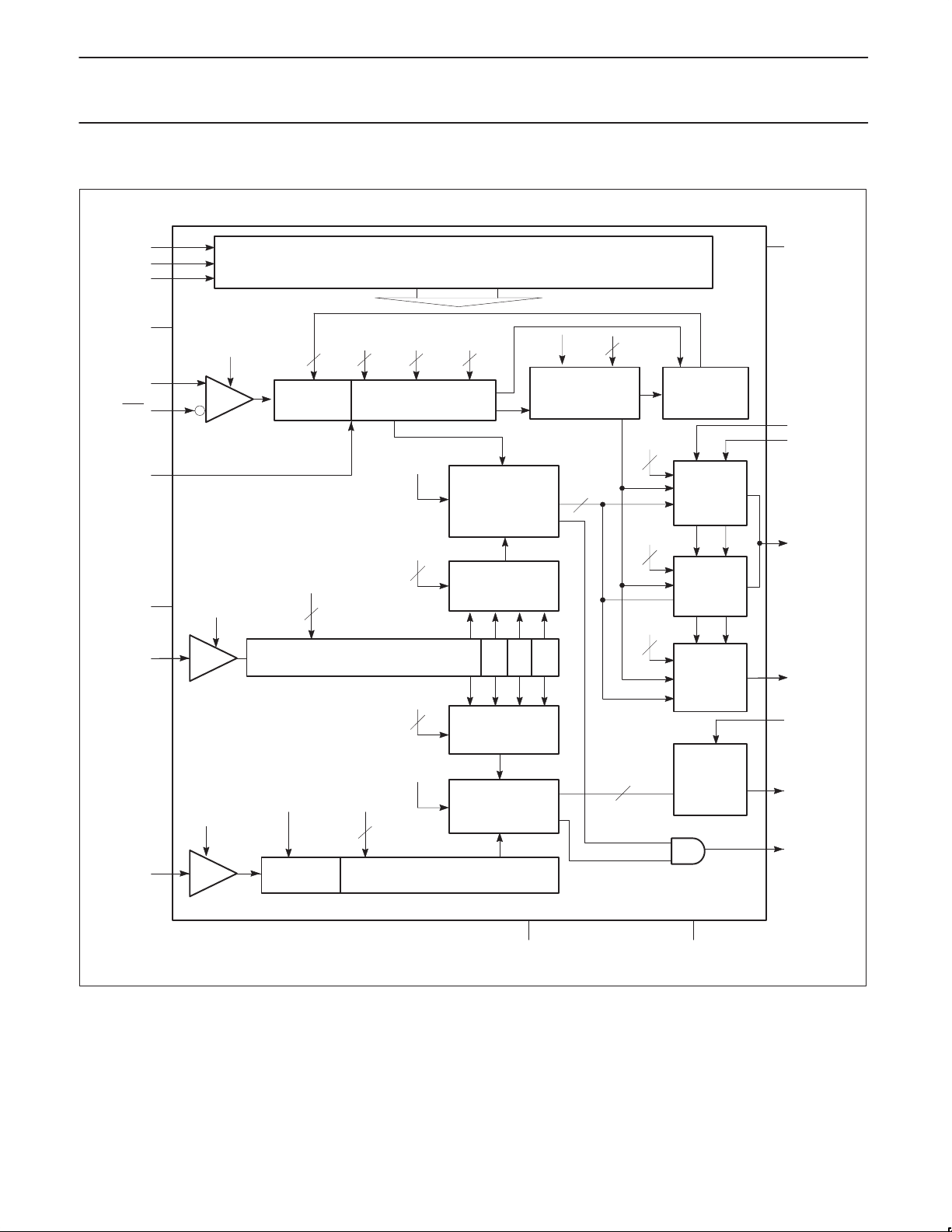

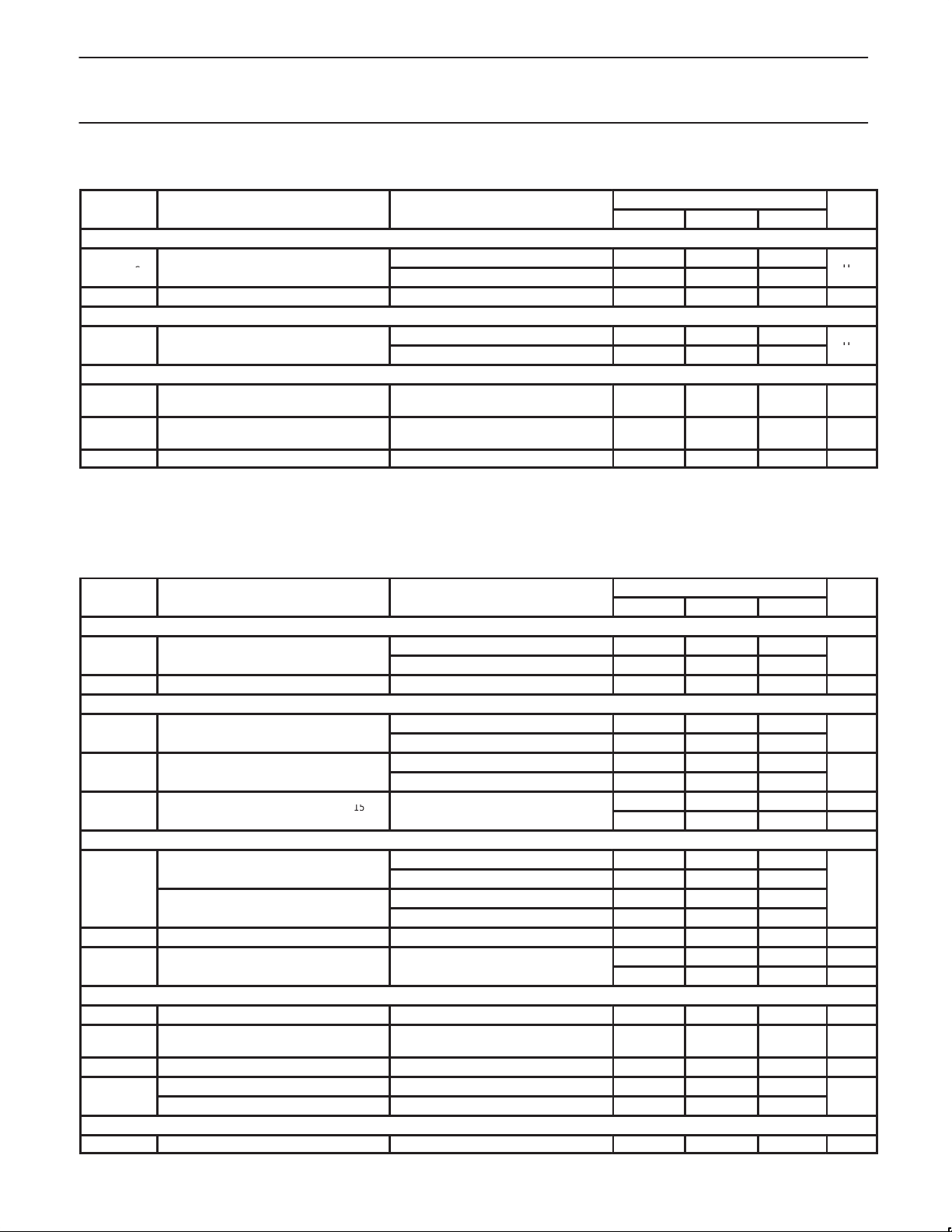

BLOCK DIAGRAM

CLOCK

DATA

STROBE

V

SS

RF

RF

TEST

V

CCP

REF

AUX

V

SERIAL INPUT + PROGRAM LATCHES

EM

IN

IN

EM+EA

FB

64/65/72

PRESCALER

NR

IN

EA

IN

PA NA

1/4

PRESCALER

PR NM1

2

12

REFERENCE DIVIDER ÷2 ÷2 ÷2

2

MAIN DIVIDERS

EM

SM

2

SA

2

EA

12

AUXILIARY DIVIDER

NM2

NM3

12 8

MAIN

PHASE

DETECTOR

MAIN

REFERENCE

SELECT

AUXILIARY

REFERENCE

SELECT

AUXILIARY

PHASE

DETECTOR

FMOD

FRACTIONAL

ACCUMULATOR

3

NF

FRD

CN

8

2

CL

2

CK

4

2

FB

PRESCALER

MODULUS

CONTROL

NORMAL

OUTPUT

CHARGE

PUMP

SPEED-UP

OUTPUT

CHARGE

PUMP

INTEGRAL

OUTPUT

CHARGE

PUMP

AUXILIARY

OUTPUT

CHARGE

PUMP

DD

RF

RN

PHP

PHI

RA

PHA

LOCK

1996 Aug 6

V

DDA

Figure 2. Block Diagram

4

V

SSA

SR00601

Philips Semiconductors Product specification

SYMBOL

PARAMETER

TEST CONDITIONS

UNITS

|IRX|

ggyg

A

|I

|

Output current PHA

A

∆I

Output current matching PHA pump

A

|I

|

Output current PHP

A

∆I

g

A

|I

|

Output current PHP

mA

∆I

g

A

|I

|

Output current PHI

mA

∆I

Output current matching PHI pump

A

I

nA

SA70251GHz low-voltage Fractional-N synthesizer

DC ELECTRICAL CHARACTERISTICS

VDD = V

V

I

STANDBY

Operational supply currents: I = IDD + I

Digital inputs CLK, DATA, STROBE

Digital outputs LOCK

Charge pumps: V

V

Charge pump PHA

I

|I

Charge pump PHP, normal mode

PHP_N_M

Charge pump PHP, speed-up mode

I

PHP_S_M

Charge pump PHI, speed-up mode

Fractional compensation PHP, normal mode

PHP_F_N

DDA

SUPPLY

I

AUX

I

MAIN

I

TOTAL

V

IH

V

IL

V

OL

V

OH

PHOUT

PHA

PHP_A

PHP_A

PHA_M

PHP_N

I

PHP_N

I

PHP_N

PHP_S

PHP_S

I

PHP_S

PHI

I

PHI

I

PHI

PHI_M

= V

= 3V; TA = 25°C, unless otherwise specified.

CCP

LIMITS

MIN TYP MAX

Recommended operating conditions V

CCP

= VDD, V

DDA

≥ V

DD

2.7 5.5 V

Total standby supply currents EM = EA = 0, IRN = IRF = IRA = 0 50 500 µA

+ I

CCP

; IRN = 25µA, IRA = 25µA, (see Note 5)

DDA

Operational supply currents EM = 0, EA = 1 3.5 mA

Operational supply currents EM = 1, EA = 0 5.5 mA

Operational supply currents EM = EA = 1 7.5 mA

High level input voltage range 0.7xV

DD

Low level input voltage range 0 0.3xV

V

DD

DD

Output voltage LOW IO = 2mA 0.4 V

Output voltage HIGH IO = –2mA VDD–0.4 V

= 3V / IRX = 25µA or V

DDA

Setting current range for any setting resistor

Output voltage range 0.7 V

p

Relative output current variation PHA IRA = –62.5µA

|

p

1, 4, 6

VRF = V

p

Relative output current variation PHP IRN = –62.5µA

Output current matching PHP

normal mode

1, 4, 7

p

Relative output current variation PHP IRN = –62.5µA

Output current matching PHP

speed-up mode

1, 4, 8

p

Relative output current variation PHI IRN = –62.5µA

p

Fractional compensation output current

PHP vs F

RD

3

= 5V / IRX = 62.5µA, V

DDA

p

p

DDA

VRF = V

VRF = V

p

p

1, 9

DDA

DDA

VRN = V

in range, unless otherwise specified. (See Note 16)

PHX

2.7V < V

4.5V < V

IRA = –62.5µA; V

IRA = –25µA; V

V

= 3V, IRA = 25µA ±50

DDA

V

= 5V, IRA = 62.5µA ±65

DDA

IRN = –62.5µA; V

IRN = –25µA; V

V

= 3V, IRA = 25µA ±50

DDA

V

= 5V, IRA = 62.5µA ±65

DDA

IRN = –62.5µA; V

IRN = –25µA; V

V

= 3V, IRA = 25µA ±250

DDA

V

= 5V, IRA = 62.5µA ±300

DDA

IRN = –62.5µA; V

IRN = –25µA; V

V

= 3V, IRA = 25µA ±500

DDA

V

= 5V, IRA = 62.5µA ±600

DDA

, V

DDA

PHP

IRF = –62.5µA;FRD = 1 to 7

< 5.5V 25

DDA

< 5.5V 62.5

DDA

13

/2

DDA

/2 160 200 240

DDA

13

/2

DDA

/2 175 220 265

DDA

13

/2

DDA

/2 0.85 1.1 1.35

DDA

13

/2

DDA

/2 1.75 2.2 2.65

DDA

13

400 500 600

440 550 660

2.20 2.75 3.30

–625 –400 –250

= V

PHA

PHA

PHP

PHP

PHP

PHP

PHI

PHI

DDA

= V

= V

2, 13

= V

= V

2, 13

= V

= V

2, 13

= V

= V

2, 13

/2

2 6 %

2 6 %

2 6 %

4.4 5.5 6.6

2 8 %

IRF = –25µA;FRD = 1 to 7 –250 –180 –100

–0.8 V

DDA

V

V

µ

µ

µ

µ

µ

µ

µ

1996 Aug 6

5

Philips Semiconductors Product specification

SYMBOL

PARAMETER

TEST CONDITIONS

UNITS

I

A

I

A

SYMBOL

PARAMETER

TEST CONDITIONS

UNITS

f

Input signal frequenc

GH

f

Input signal frequenc

MH

V

Input signal range, AC coupled

mV

Z

Reference divider input impedance

15

f

MH

Z

Auxiliary divider input impedance

t

ns

SA70251GHz low-voltage Fractional-N synthesizer

DC ELECTRICAL CHARACTERISTICS (Continued)

LIMITS

MIN TYP MAX

Fractional compensation PHP, speed up mode

PHP_F_S

Fractional compensation output current

PHP vs F

RD

3

Pump leakage –20 20 nA

Fractional compensation PHI, speed up mode

PHI_F

Fractional compensation output current

PHI vs F

RD

3

Charge pump leakage currents, charge pump not active

I

PHP_L

I

PHI_L

I

PHA_L

Output leakage current PHP; normal

1

mode

Output leakage current PHI; normal

1

mode

Output leakage current PHA V

1, 10

1, 11

V

= V

DDA

, VRN = V

PHP

IRF = –62.5µA;FRD = 1 to 7

IRF = –25µA;FRD = 1 to 7 –1.35 –1.0 –0.5

V

= V

PHP

/2, VRN = V

DDA

IRF = –62.5µA;FRD = 1 to 7

IRF = –25µA;FRD = 1 to 7 –2.15 –1.6 –1.05

V

= 0.7 to V

PHP

V

= 0.7 to V

PHI

= 0.7 to V

PHA

DDA

DDA

DDA

DDA

13

DDA

13

–3.35 –2.0 –1.1

–5.4 –4.0 –2.6

– 0.8 0.1 10 nA

– 0.8 0.1 10 nA

– 0.8 0.1 10 nA

µ

µ

AC ELECTRICAL CHARACTERISTICS

VDD = V

listed below are tested using automatic test equipment to assure consistent electrical characteristics. The limits do not represent the ultimate

performance limits of the device. Use of an optimized RF layout will improve many of the listed parameters.

Main divider

V

Reference divider (VDD = V

Auxiliary divider

V

Serial interface

f

In-Loop Performance17 V

RF_IN

RF_IN

REF_IN

REF_IN

REF_IN

AUX_IN

AUX_IN

AUX_IN

CLOCK

t

SU

t

H

W

R

MM

= V

DDA

= 3V; TA = 25°C; f

CCP

= 1GHz, input level = –20dBm; unless otherwise specified. Test Circuit, Figure 4. The parameters

RF_IN

LIMITS

MIN TYP MAX

p

y

Direct coupled input

1000pF input coupling 1.04

14

Input sensitivity 1040MHz –20 0 dBm

= 3V or VDD = 3V / V

DDA

p

p

y

p

p

p

DDA

= 5V)

2.7 < VDD and V

2.7 < VDD and V

2.7 < VDD and V

2.7 < VDD and V

< 5.5V 25

DDA

< 4.5V 30

DDA

< 5.5V 500

DDA

< 4.5V 300

DDA

100 kΩ

3 pF

Input signal frequency 0 50

PA = “0”, prescaler enabled 4.5V ≤ V

≤ 5.5V 0 150

DDA

Input signal frequency 0 30

PA = “1”, prescaler disabled 4.5V ≤ V

≤ 5.5V 0 40

DDA

Input signal range, AC coupled 200 mV

p

p

15

100 kΩ

3 pF

Clock frequency 10 MHz

Set-up time: DATA to CLOCK,

CLOCK to STROBE

30 ns

Hold time; CLOCK to DATA 30 ns

Pulse width; CLOCK 30

Pulse width; STROBE B, C, D, E words 30

= 5V, VDD = 2.7V

DDA

Main loop residual FM FVCO = 1030MHz 300 600 Hz

1.04

z

z

P-P

z

P-P

1996 Aug 6

6

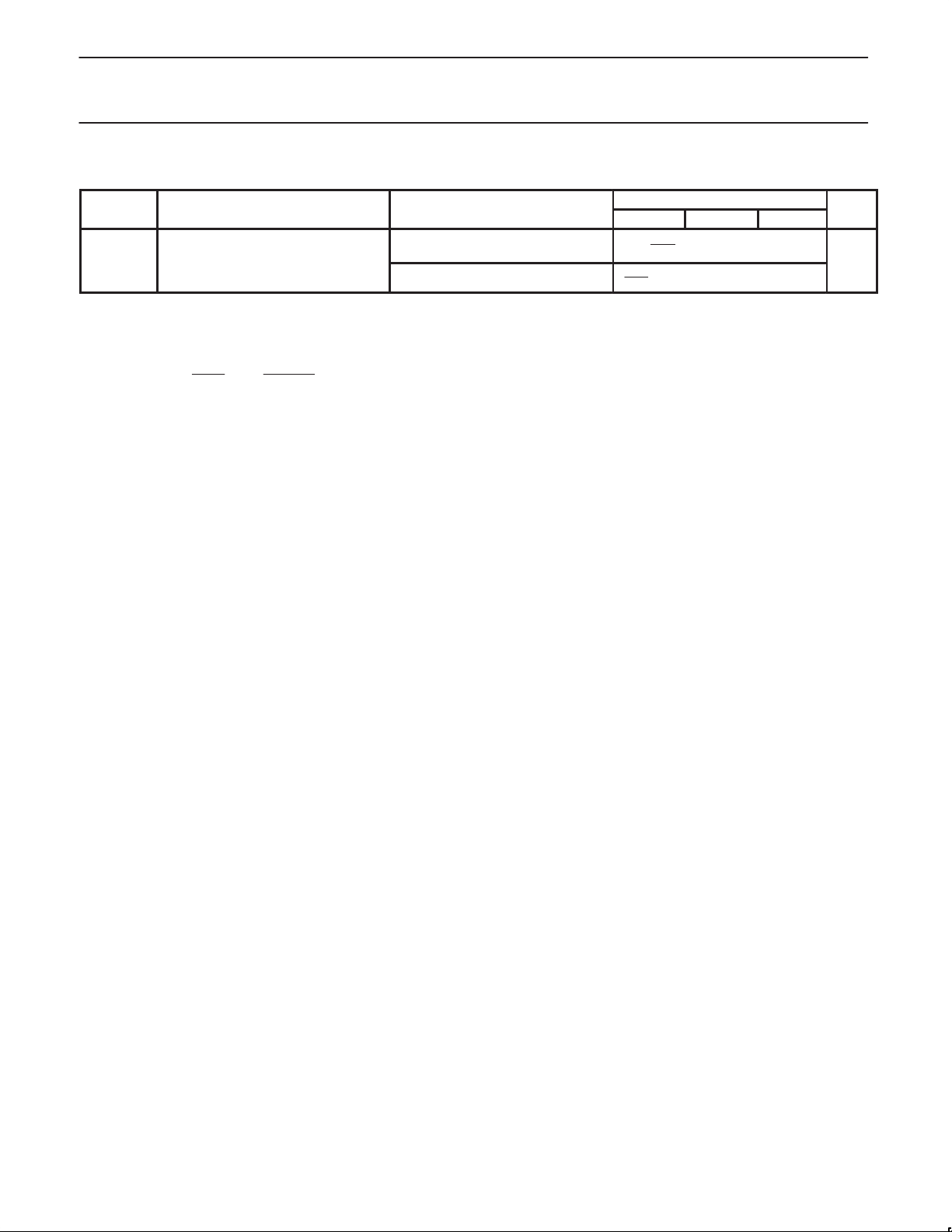

Philips Semiconductors Product specification

SYMBOL

PARAMETER

TEST CONDITIONS

UNITS

tSWPulse width STROBE

ns

SA70251GHz low-voltage Fractional-N synthesizer

AC ELECTRICAL CHARACTERISTICS (continued)

LIMITS

MIN TYP MAX

;

A word, PR = ‘01’

A word, PR = ‘10’

NOTES:

1. When a serial input “A” word is programmed, the main charge pumps on PHP and PHI are in the “speed up mode” as long as STROBE = H.

When this is not the case, the main charge pumps are in the “normal mode”.

2. The relative output current variation is defined thus:

I

OUT

2

I

3. F

is the value of the 3 bit fractional accumulator.

RD

4. Monotonicity is guaranteed with C

OUT

5. Power supply current measured with V

Main comp frequency = 240kHz, Auxiliary comp frequency = 120kHz, CN = 160, CL = 0, CK = 0. Internal registers NM1 = 52, NM2 = 0,

|(I

(I

I1)

2

I1)|

2

N

; with V1 = 0.7V, V2 = V

= 0 to 255.

= V

CCP

= 3V, V

DD

DDA

– 0.8V (see Figure 3).

DDA

= 5V, f

= 915.99MHz, XTAL at 21.36MHz, AUX at 85.92MHz (PA = ‘0’),

RF IN

NM3 = 4, PR = ‘10’, SM = ‘00’, SA = ‘01’, NA = 179, NF = 5, FMOD = 8, NR = 89, PA = 0, IRN = IRA = IRF = 25µA, lock condition, normal

mode. Operational supply current = I

6. Specification condition: CN = 255

DDA

+ IDD + I

CCP

.

7. Specification conditions:

1) CN = 255; CL = 1, or

8. Typical output current | I

2) CN = 75; CL = 3

1) CN = 160; CL = 3; CK = 1, or

| = –IRN x CN x 2

PHI

(CL+1)

x CK/32:

2) CN = 160; CL = 2; CK = 2, or

3) CN = 160; CL = 1; CK = 4, or

4) CN = 160; CL = 0; CK = 8

9. Any RFD, CL = 1 for speed-up pump. The integral pump is intended for switching only and the fractional compensation is not guaranteed.

10.Specification conditions: F

11.Specification conditions:

1) F

2) F

12.The matching is defined by the sum of the P and the N pump for a given output voltage.

= 1 to 7; CL = 1.

RD

= 1 to 7; CL = 1; CK = 2, or

RD

= 1 to 7; CL = 2; CK = 1.

RD

13.Limited analog supply voltage range 4.5 to 5.5V.

14.For f

15.Guaranteed by design.

< 50MHz, low frequency operation requires DC-coupling and a minimum input slew rate of 32V/µs.

IN

16.Close in noise for the charge pumps is tested on a sample basis in a typical application in order to eliminate parts outside the normal

distribution.

17.F

= 14.4MHz, V

XTAL

XTAL

= 500mV

, comparison frequency = 200kHz, Loop bandwidth = 5kHz, Audio filter = 300Hz to 15kHz.

P-P

1

(NM2 65) t

f

VCO

1

[(NM2 65) (NM31) 72] t

f

VCO

W

W

1996 Aug 6

7

Loading...

Loading...