Philips SA701D, SA7015DK Datasheet

Philips Semiconductors RF Communications Products Product specification

SA701

Divide by: 128/129-64/65 dual modulus low power

ECL prescaler

2

June 17, 1993 853-1708 10044

DESCRIPTION

The SA701 is an advanced dual modulus

(Divide By 128/129 or 64/65) low power ECL

prescaler. The minimum supply voltage is

2.7V and is compatible with the CMOS

UMA1005 synthesizer from Philips and other

logic circuits. The low supply current allows

application in battery operated low-power

equipment. Maximum input signal frequency

is 1.1GHz for cellular and other land mobile

applications. There is no lower frequency

limit due to a fully static design. The circuit is

implemented in ECL technology on the

QUBiC process. The circuit will be available

in an 8-pin SO package with 150 mil package

width and in 8-pin dual in-line plastic

package, and is pin compatible with Fujitsu

MB501, Plessey SP8704 and Motorola

MC12022.

FEATURES

•Low voltage operation

•Low current consumption

•Operation up to 1.1GHz

•ESD hardened

APPLICATIONS

•Cellular phones

•Cordless phones

•RF LANs

•Test and measurement

•Military radio

•VHF/UHF mobile radio

•VHF/UHF hand-held radio

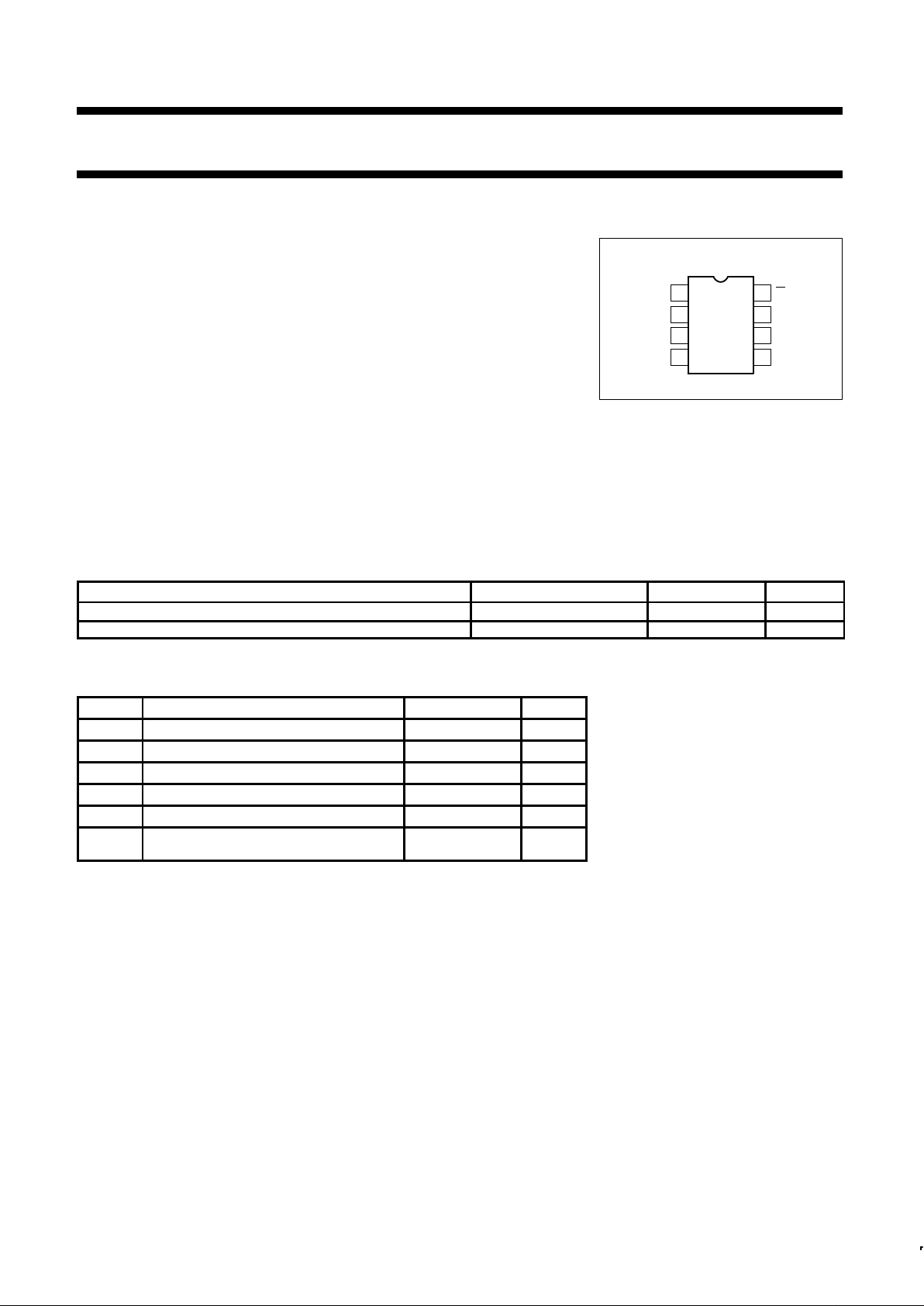

PIN CONFIGURATION

IN

V

C

C

SW

OUT

IN

MC

1

2

3

4 5

6

78nc

GND

N, D Package

ORDERING INFORMATION

DESCRIPTION TEMPERATURE RANGE ORDER CODE DWG #

8-Pin Plastic Dual In-Line Package (DIP) -40 to +85°C SA701N 0404B

8-Pin Plastic Small Outline (SO) package (Surface-mount) -40 to +85°C SA701D 0174C

ABSOLUTE MAXIMUM RATINGS

SYMBOL PARAMETER RATING UNITS

V

CC

Supply voltage -0.3 to +7.0 V

V

IN

Voltage applied to any other pin -0.3 to (VCC + 0.3) V

I

O

Output current 10 mA

T

STG

Storage temperature range -65 to +125 °C

T

A

Operating ambient temperature range -55 to +125 °C

θ

JA

Thermal impedance D package

N package

158

108

°C/W

Philips Semiconductors RF Communications Products Product specification

SA701

Divide by: 128/129-64/65 dual modulus low power

ECL prescaler

June 17, 1993

3

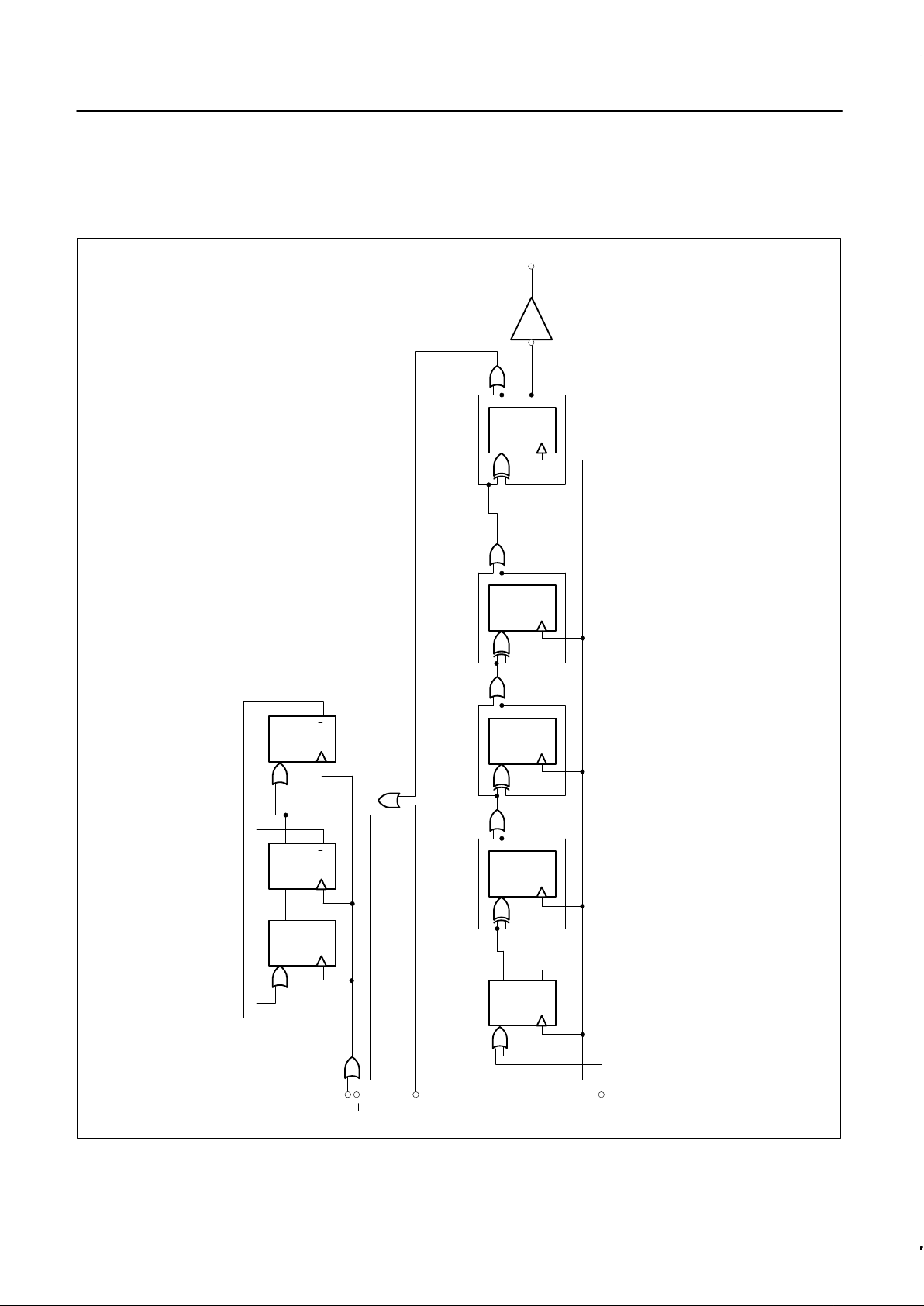

BLOCK DIAGRAM

D

Q

D

Q Q

D

Q Q

D

Q

D

Q Q

D

Q

D

Q

D

Q

OUT

IN

IN

MC

SW

Philips Semiconductors RF Communications Products Product specification

SA701

Divide by: 128/129-64/65 dual modulus low power

ECL prescaler

June 17, 1993

4

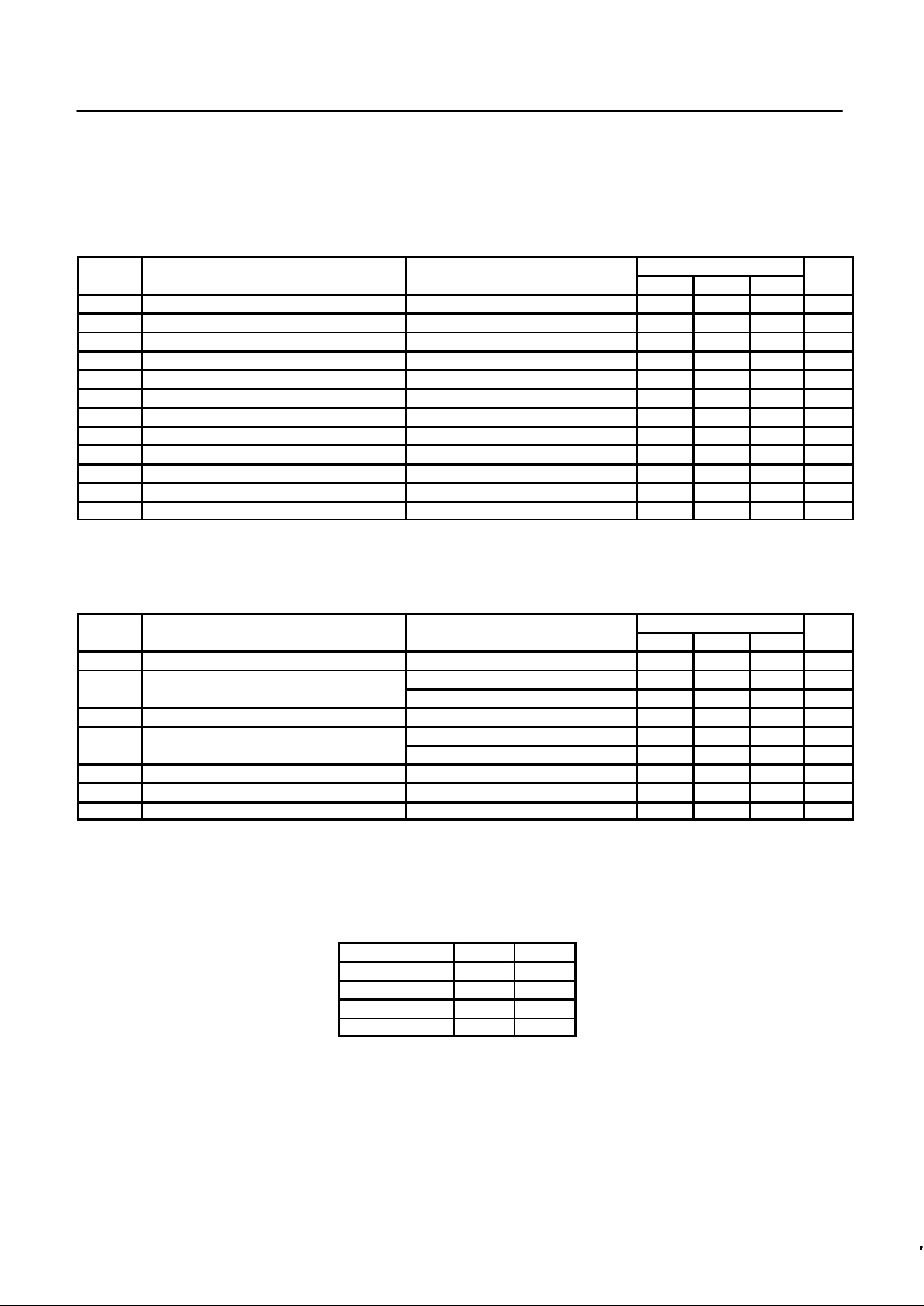

DC ELECTRICAL CHARACTERISTICS

The following DC specifications are valid for TA = 25°C and VCC = 3.0V; unless otherwise stated. Test circuit Figure 1.

SYMBOL

PARAMETER TEST CONDITIONS LIMITS UNITS

MIN TYP MAX

V

CC

Power supply voltage range fIN = 1GHz, input level = 0dBm 2.7 6.0 V

I

CC

Supply current No load 4.5 mA

V

OH

Output high level I

OUT

= 1.2mA VCC-1.4 V

V

OL

Output low level VCC-2.6 V

V

IH

MC input high threshold 2.0 V

CC

V

V

IL

MC input low threshold –0.3 0.8 V

V

IH

SW input high threshold 2.0 V

CC

V

V

IL

SW input low threshold –0.3 0.8 V

I

IH

MC input high current VMC = VCC = 6V 0.1 50 µA

I

IL

MC input low current VMC = 0V, VCC = 6V –100 –30 µA

I

IH

SW input high current VSW = VCC = 6V 35 100 µA

I

IL

SW input low current VSW = 0V, VCC = 6V –50 –0.1 µA

AC ELECTRICAL CHARACTERISTICS

The following AC specifications are valid for VCC = 3.0V, fIN = 1GHz, input level = 0dBm, TA = 25°C; unless otherwise stated. Test circuit Fig. 1.

SYMBOL

PARAMETER TEST CONDITIONS LIMITS UNITS

MIN TYP MAX

V

IN

Input signal amplitude

1

1000pF input coupling 0.05 2.0 V

P-P

f

IN

Input signal frequency Direct coupled input

2

0 1.1 GHz

1000pF input coupling 1.1 GHz

R

ID

Differential input resistance DC measurement 5 kΩ

V

O

Output voltage VCC = 5.0V 1.6 V

P-P

VCC = 3.0V 1.2 V

P-P

t

S

Modulus set-up time

1

5 ns

t

H

Modulus hold time

1

0 ns

t

PD

Propagation time 10 ns

NOTES:

1. Maximum limit is not tested, however, it is guaranteed by design and characterization.

2. For f

IN

< 50MHz, minimum input slew rate of 32V/µs is required.

DESCRIPTION OF OPERATION

The SA701 comprises a frequency divider

circuit implemented using a divide by 4 or 5

synchronous prescaler followed by a 5 stage

synchronous counter, see BLOCK

DIAGRAM. The normal operating mode is for

SW (Modulus Set Switch) input to be set low

and MC (Modulus Control) input to be set

high in which case the circuit comprises a

divide by 128. For divide by 129 the MC

signal is forced low, causing the prescaler

circuit to switch into divide by 5 operation for

the last cycle of the synchronous counter.

Similarly, for divide by 64 and 65 the SA701

will generate those respective moduli with the

SW signal forced high, in which the fourth

stage of the synchronous divider is

bypassed. A truth table for the modulus

values is given below:

Table 1.

Modulus MC SW

128 1 0

129 0 0

64 1 1

65 0 1

For minimization of propagation delay effects,

the second divider circuit is synchronous to

the divide by 4/5 stage output.

The prescaler input is positive edge sensitive,

and the output at the final count is a falling

edge with propagation delay t

PD

relative to

the input. The rising edge of the output

occurs at the count 64 for modulus 128/129

or count 32 for modulus 64/65 with delay t

PD

.

The SW input is not designed for

synchronous switching.

The MC and SW inputs are TTL compatible

threshold inputs operating at a reduced input

current. CMOS and low voltage interface

capability are allowed. The SW input has an

internal pull-down simplifying modulus group

selection. With SW open the divide by

128/129 mode is selected and with SW

connected to V

CC

divide by 64/65 is selected.

The prescaler input is differential and ECL

compatible. The output is single-ended ECL

compatible.

Loading...

Loading...