Page 1

Colour Television Chassis

18310_000_090317.eps

090317

Q549.2E

LA

Contents Page Contents Page

1. Revision List 2

2. Technical Specifications and, Connections 2

3. Precautions, Notes, and Abbreviation List 6

4. Mechanical Instructions 10

5. Service Modes, Error Codes, and Fault Finding 15

6. Alignments 36

7. Circuit Descriptions 42

8. IC Data Sheets 53

9. Block Diagrams

Wiring Diagram 32" (Elite Core) 59

Wiring Diagram 37" (Elite Core) 60

Block Diagram Video 62

Block Diagram Audio 63

Block Diagram Control & Clock Signals 64

Block Diagram I2C 65

Supply Lines Overview 66

10. Circuit Diagrams and PWB Layouts Drawing PWB

Interface Ambilight: Interface + Single DC-DC

Interface Ambilight: Dual DC-DC (AB2) 68 70

Interface Ambilight: Microcontrollerblock (AB3) 69 70

6 LED Low-Pow: Microcontroller Block Liteon(AL1)71 74

6 LED Low-Pow: Microcontroller Block Liteon(AL2)72 74

6 LED Low-Pow: LED Liteon (AL3) 73 74

8 LED Low-Pow: Microcontroller Block Liteon(AL1)75 79

8 LED Low-Pow: Microcontroller Block Liteon(AL2)76 79

8 LED Low-Pow: LED Liteon (AL3) 77 79

8 LED Low-Pow: LED Drive Liteon (AL4) 78 79

10 LED Low-Pow: Microcontroller Block Liteon(AL1)80 84

10 LED Low-Pow: Microcontroller Block Liteon(AL2)81 84

10 LED Low-Pow: LED Liteon (AL3) 82 84

10 LED Low-Pow: LED Drive Liteon (AL4) 83 84

SSB (B01A-B10) 85-133 137-138

SSB: SRP List Explanation 134

SSB: SRP List Part 1 135

©

Copyright 2009 Koninklijke Philips Electronics N.V.

All rights reserved. No part of this publication may be reproduced, stored in a

retrieval system or transmitted, in any form or by any means, electronic, mechanical,

photocopying, or otherwise without the prior permission of Philips.

(AB1)67 70

SSB: SRP List Part 2 136

Light guide 139 140

Wi-Fi Antenna 141 141

Published by ER/EL 0965 BU TV Consumer Care, the Netherlands Subject to modification EN 3122 785 18311

2009-May-08

Page 2

EN 2 Q549.2E LA1.

Revision List

1. Revision List

Manual xxxx xxx xxxx.0

• First release.

Manual xxxx xxx xxxx.1

• All Chapters: the following sets to the manual: see Table

2-1 Described Model numbers.

• Chapter 5: paragraph 5.8.10 PCI bus

• Chapter 6: paragraph 6.6 Service SSB delivered without

main software loaded added.

added.

2. Technical Specifications and, Connections

Index of this chapter:

2.1 Technical Specifications

2.2 Directions for Use

2.3 Connections

2.4 Chassis Overview

Notes:

• Figures can deviate due to the different set executions.

• Specifications are indicative (subject to change).

2.1 Technical Specifications

For on-line product support please use the links in Table 2-1.

Here is product information available, as well as getting started,

user manuals, frequently asked questions and software &

drivers.

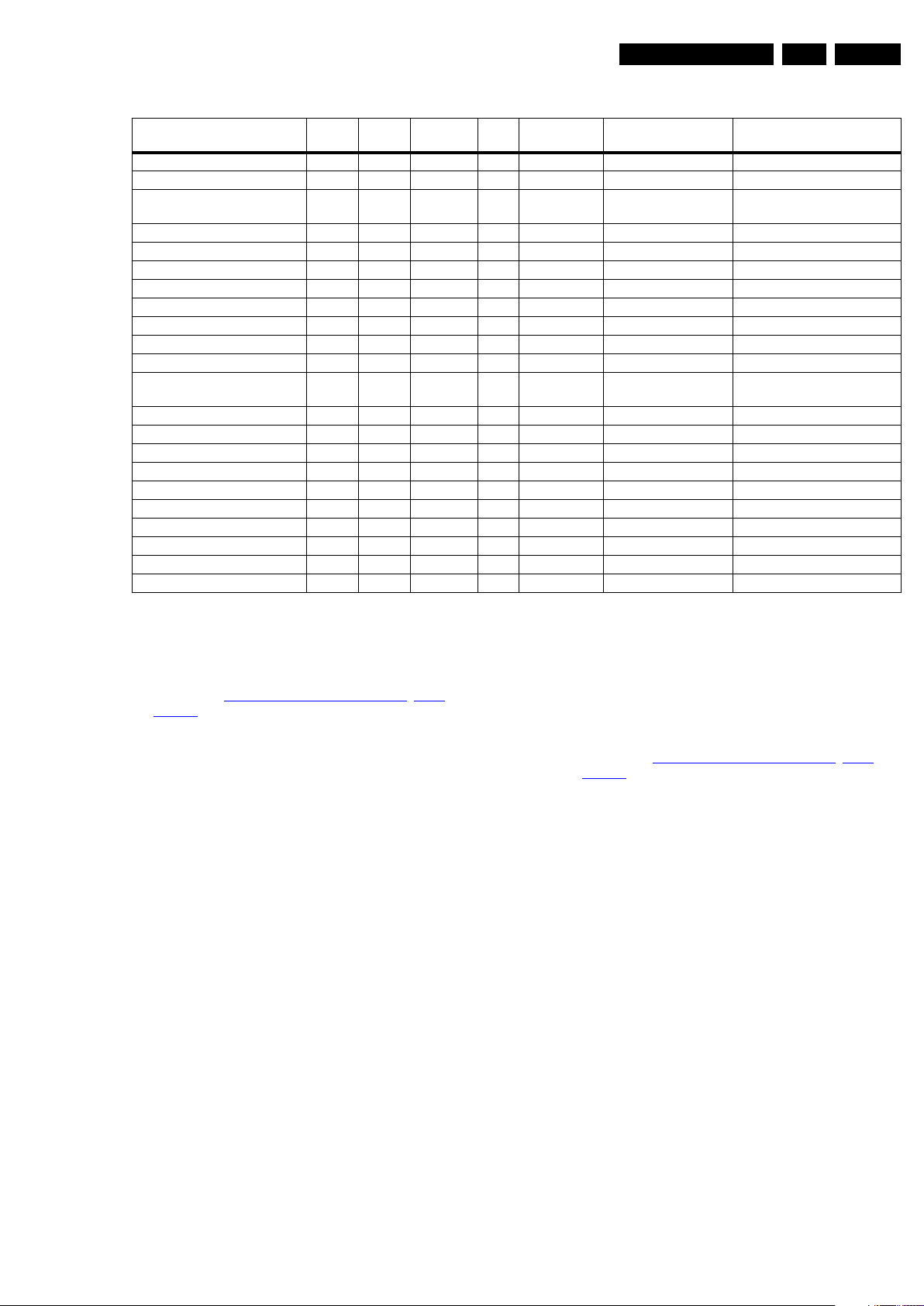

Table 2-1 Described Model numbers

CTN Styling Published in:

32PFL9604H/12

32PFL9604H/60

37PFL9604H/12

37PFL9604H/60

56PFL9954H/12

Elite Core 3122 785 18310

3122 785 18310

3122 785 18310

3122 785 18311

3122 785 18311

2.2 Directions for Use

You can download this information from the following websites:

http://www.philips.com/support

http://www.p4c.philips.com

2009-May-08

Page 3

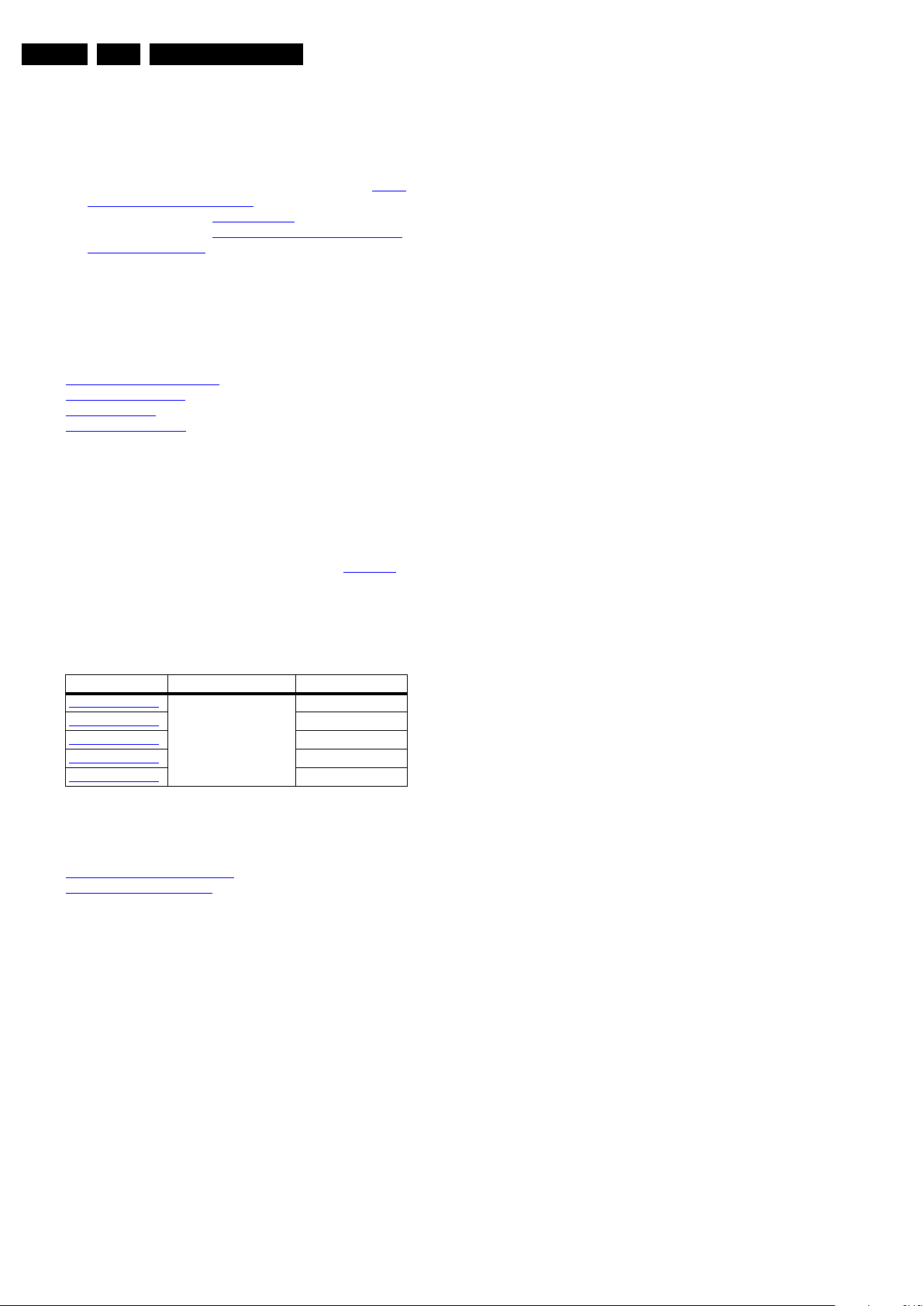

2.3 Connections

18310_001_090317.eps

090317

NETWORK

AUDIO IN VGA

VGASERVICE UART

1234

Technical Specifications and, Connections

EN 3Q549.2E LA 2.

Figure 2-1 Connection overview

2009-May-08

Page 4

EN 4 Q549.2E LA2.

1 2 3 4

10000_022_090121.eps

090121

1

6

10

11

5

15

10000_002_090121.eps

090127

112345678

E_06532_025.eps

210905

Technical Specifications and, Connections

Note: The following connector colour abbreviations are used

(acc. to DIN/IEC 757): Bk= Black, Bu= Blue, Gn= Green, Gy=

Grey, Rd= Red, Wh= White, Ye= Yellow.

2.3.1 Side Connections

Head phone (Output)

Bk - Head phone 32 - 600 ohm / 10 mW ot

Cinch: Video CVBS - In, Audio - In

Rd - Audio R 0.5 V

Wh - Audio L 0.5 V

Ye - Video CVBS 1 V

/ 10 kohm jq

RMS

/ 10 kohm jq

RMS

/ 75 ohm jq

PP

S-Video (Hosiden): Video Y/C - In

1 - Ground Y Gnd H

2 - Ground C Gnd H

3 - Video Y 1 V

4 - Video C 0.3 V

/ 75 ohm j

PP

/ 75 ohm j

PP

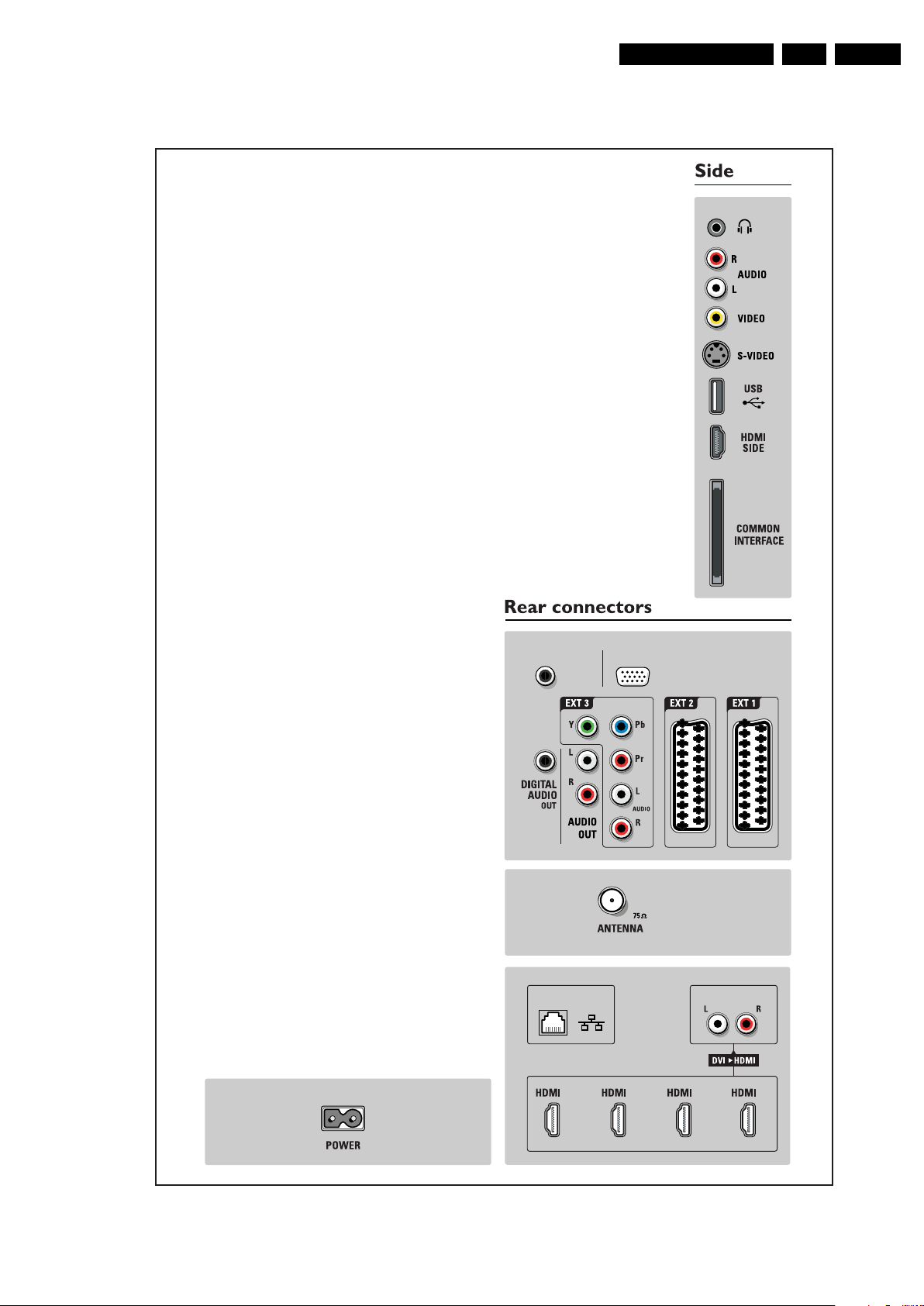

USB2.0

Figure 2-2 USB (type A)

1-+5V k

2 - Data (-) jk

3 - Data (+) jk

4 - Ground Gnd H

HDMI: Digital Video, Digital Audio - In (see HDMI 1, 2, 3 & 4 - Rear Connections)

Common Interface

68p - See diagram B07A SSB: CI: PCMCIA

Connector jk

2.3.2 Rear Connections

Service Connector (UART)

1 - Ground Gnd H

2 - UART_TX Transmit k

3 - UART_RX Receive j

VGA: Video RGB - In

Cinch: S/PDIF - Out

Bk - Coaxial 0.4 - 0.6V

/ 75 ohm kq

PP

Cinch: Audio - Out

Rd - Audio - R 0.5 V

Wh - Audio - L 0.5 V

/ 10 kohm kq

RMS

/ 10 kohm kq

RMS

EXT3: Cinch: Video YPbPr - In, Audio - In

Gn - Video Y 1 V

Bu - Video Pb 0.7 V

Rd - Video Pr 0.7 V

Rd - Audio - R 0.5 V

Wh - Audio - L 0.5 V

/ 75 ohm jq

PP

/ 75 ohm jq

PP

/ 75 ohm jq

PP

/ 10 kohm jq

RMS

/ 10 kohm jq

RMS

EXT1 & 2: Video RGB - In, CVBS - In/Out, Audio - In/Out

20

21

10000_001_090121.eps

2

1

090121

Figure 2-4 SCART connector

1 - Audio R 0.5 V

2 - Audio R 0.5 V

3 - Audio L 0.5 V

4 - Ground Audio Gnd H

/ 1 kohm k

RMS

/ 10 kohm j

RMS

/ 1 kohm k

RMS

5 - Ground Blue Gnd H

6 - Audio L 0.5 V

7 - Video Blue 0.7 V

8 - Function Select 0 - 2 V: INT

/ 10 kohm j

RMS

/ 75 ohm jk

PP

4.5 - 7 V: EXT 16:9

9.5 - 12 V: EXT 4:3 j

9 - Ground Green Gnd H

10 - n.c.

11 - Video Green 0.7 V

12 - n.c.

/ 75 ohm j

PP

13 - Ground Red Gnd H

14 - Ground P50 Gnd H

15 - Video Red 0.7 V

16 - Status/FBL 0 - 0.4 V: INT

/ 75 ohm j

PP

1 - 3 V: EXT / 75 ohm j

17 - Ground Video Gnd H

18 - Ground FBL Gnd H

19 - Video CVBS/Y 1 V

20 - Video CVBS 1 V

21 - Shield Gnd H

/ 75 ohm k

PP

/ 75 ohm j

PP

Aerial - In

- - IEC-type (EU) Coax, 75 ohm D

1 - Video Red 0.7 V

2 - Video Green 0.7 V

3 - Video Blue 0.7 V

4-n.c.

5 - Ground Gnd H

6 - Ground Red Gnd H

7 - Ground Green Gnd H

8 - Ground Blue Gnd H

9-+5V

10 - Ground Sync Gnd H

11 - n.c.

12 - DDC_SDA DDC data j

13 - H-sync 0 - 5 V j

14 - V-sync 0 - 5 V j

15 - DDC_SCL DDC clock j

2009-May-08

Figure 2-3 VGA Connector

/ 75 ohm j

PP

/ 75 ohm j

PP

/ 75 ohm j

PP

+5 V j

DC

RJ45: Ethernet (if present)

Figure 2-5 Ethernet connector

1 - TD+ Transmit signal k

2 - TD- Transmit signal k

3 - RD+ Receive signal j

4 - CT Centre Tap: DC level fixation

5 - CT Centre Tap: DC level fixation

6 - RD- Receive signal j

7 - GND Gnd H

8 - GND Gnd H

Page 5

Technical Specifications and, Connections

19

1

18 2

E_06532_017.eps

250505

EN 5Q549.2E LA 2.

Cinch: Audio - In (VGA/DVI)

Rd - Audio R 0.5 V

Wh - Audio L 0.5 V

/ 10 kohm jq

RMS

/ 10 kohm jq

RMS

HDMI 1, 2, 3 & 4: Digital Video, Digital Audio - In

Figure 2-6 HDMI (type A) connector

1 - D2+ Data channel j

2 - Shield Gnd H

3 - D2- Data channel j

4 - D1+ Data channel j

2.4 Chassis Overview

Refer to chapter Block Diagrams for PWB/CBA locations.

5 - Shield Gnd H

6 - D1- Data channel j

7 - D0+ Data channel j

8 - Shield Gnd H

9 - D0- Data channel j

10 - CLK+ Data channel j

11 - Shield Gnd H

12 - CLK- Data channel j

13 - Easylink/CEC Control channel jk

14 - n.c.

15 - DDC_SCL DDC clock j

16 - DDC_SDA DDC data jk

17 - Ground Gnd H

18 - +5V j

19 - HPD Hot Plug Detect j

20 - Ground Gnd H

2009-May-08

Page 6

EN 6 Q549.2E LA3.

Precautions, Notes, and Abbreviation List

3. Precautions, Notes, and Abbreviation List

Index of this chapter:

3.1 Safety Instructions

3.2 Warnings

3.3 Notes

3.4 Abbreviation List

3.1 Safety Instructions

Safety regulations require the following during a repair:

• Connect the set to the Mains/AC Power via an isolation

transformer (> 800 VA).

• Replace safety components, indicated by the symbol h,

only by components identical to the original ones. Any

other component substitution (other than original type) may

increase risk of fire or electrical shock hazard. Of de set

ontploft!

Safety regulations require that after a repair, the set must be

returned in its original condition. Pay in particular attention to

the following points:

• Route the wire trees correctly and fix them with the

mounted cable clamps.

• Check the insulation of the Mains/AC Power lead for

external damage.

• Check the strain relief of the Mains/AC Power cord for

proper function.

• Check the electrical DC resistance between the Mains/AC

Power plug and the secondary side (only for sets that have

a Mains/AC Power isolated power supply):

1. Unplug the Mains/AC Power cord and connect a wire

between the two pins of the Mains/AC Power plug.

2. Set the Mains/AC Power switch to the “on” position

(keep the Mains/AC Power cord unplugged!).

3. Measure the resistance value between the pins of the

Mains/AC Power plug and the metal shielding of the

tuner or the aerial connection on the set. The reading

should be between 4.5 MΩ and 12 MΩ.

4. Switch “off” the set, and remove the wire between the

two pins of the Mains/AC Power plug.

• Check the cabinet for defects, to prevent touching of any

inner parts by the customer.

picture carrier at 475.25 MHz for PAL, or 61.25 MHz for

NTSC (channel 3).

• Where necessary, measure the waveforms and voltages

with (D) and without (E) aerial signal. Measure the

voltages in the power supply section both in normal

operation (G) and in stand-by (F). These values are

indicated by means of the appropriate symbols.

3.3.2 Schematic Notes

• All resistor values are in ohms, and the value multiplier is

often used to indicate the decimal point location (e.g. 2K2

indicates 2.2 kΩ).

• Resistor values with no multiplier may be indicated with

either an “E” or an “R” (e.g. 220E or 220R indicates 220 Ω).

• All capacitor values are given in micro-farads (μ=× 10

nano-farads (n =× 10

• Capacitor values may also use the value multiplier as the

decimal point indication (e.g. 2p2 indicates 2.2 pF).

• An “asterisk” (*) indicates component usage varies. Refer

to the diversity tables for the correct values.

• The correct component values are listed on the Philips

Spare Parts Web Portal.

3.3.3 Spare Parts

For the latest spare part overview, consult your Philips Spare

Part web portal.

3.3.4 BGA (Ball Grid Array) ICs

Introduction

For more information on how to handle BGA devices, visit this

URL: http://www.atyourservice-magazine.com

“Magazine”, then go to “Repair downloads”. Here you will find

Information on how to deal with BGA-ICs.

BGA Temperature Profiles

For BGA-ICs, you must use the correct temperature-profile.

Where applicable and available, this profile is added to the IC

Data Sheet information section in this manual.

-9

), or pico-farads (p =× 10

. Select

-12

-6

),

).

3.2 Warnings

• All ICs and many other semiconductors are susceptible to

electrostatic discharges (ESD w). Careless handling

during repair can reduce life drastically. Make sure that,

during repair, you are connected with the same potential as

the mass of the set by a wristband with resistance. Keep

components and tools also at this same potential.

• Be careful during measurements in the high voltage

section.

• Never replace modules or other components while the unit

is switched “on”.

• When you align the set, use plastic rather than metal tools.

This will prevent any short circuits and the danger of a

circuit becoming unstable.

3.3 Notes

3.3.1 General

• Measure the voltages and waveforms with regard to the

chassis (= tuner) ground (H), or hot ground (I), depending

on the tested area of circuitry. The voltages and waveforms

shown in the diagrams are indicative. Measure them in the

Service Default Mode with a colour bar signal and stereo

sound (L: 3 kHz, R: 1 kHz unless stated otherwise) and

3.3.5 Lead-free Soldering

Due to lead-free technology some rules have to be respected

by the workshop during a repair:

• Use only lead-free soldering tin. If lead-free solder paste is

required, please contact the manufacturer of your soldering

equipment. In general, use of solder paste within

workshops should be avoided because paste is not easy to

store and to handle.

• Use only adequate solder tools applicable for lead-free

soldering tin. The solder tool must be able:

– To reach a solder-tip temperature of at least 400°C.

– To stabilize the adjusted temperature at the solder-tip.

– To exchange solder-tips for different applications.

• Adjust your solder tool so that a temperature of around

360°C - 380°C is reached and stabilized at the solder joint.

Heating time of the solder-joint should not exceed ~ 4 sec.

Avoid temperatures above 400°C, otherwise wear-out of

tips will increase drastically and flux-fluid will be destroyed.

To avoid wear-out of tips, switch “off” unused equipment or

reduce heat.

• Mix of lead-free soldering tin/parts with leaded soldering

tin/parts is possible but PHILIPS recommends strongly to

avoid mixed regimes. If this cannot be avoided, carefully

clear the solder-joint from old tin and re-solder with new tin.

2009-May-08

Page 7

Precautions, Notes, and Abbreviation List

10000_024_090121.eps

090121

MODEL :

PROD.NO:

~

S

32PF9968/10

MADE IN BELGIUM

220-240V 50/60Hz

128W

AG 1A0617 000001

VHF+S+H+UHF

BJ3.0E LA

EN 7Q549.2E LA 3.

3.3.6 Alternative BOM identification

It should be noted that on the European Service website,

“Alternative BOM” is referred to as “Design variant”.

The third digit in the serial number (example:

AG2B0335000001) indicates the number of the alternative

B.O.M. (Bill Of Materials) that has been used for producing the

specific TV set. In general, it is possible that the same TV

model on the market is produced with e.g. two different types

of displays, coming from two different suppliers. This will then

result in sets which have the same CTN (Commercial Type

Number; e.g. 28PW9515/12) but which have a different B.O.M.

number.

By looking at the third digit of the serial number, one can

identify which B.O.M. is used for the TV set he is working with.

If the third digit of the serial number contains the number “1”

(example: AG1B033500001), then the TV set has been

manufactured according to B.O.M. number 1. If the third digit is

a “2” (example: AG2B0335000001), then the set has been

produced according to B.O.M. no. 2. This is important for

ordering the correct spare parts!

For the third digit, the numbers 1...9 and the characters A...Z

can be used, so in total: 9 plus 26= 35 different B.O.M.s can be

indicated by the third digit of the serial number.

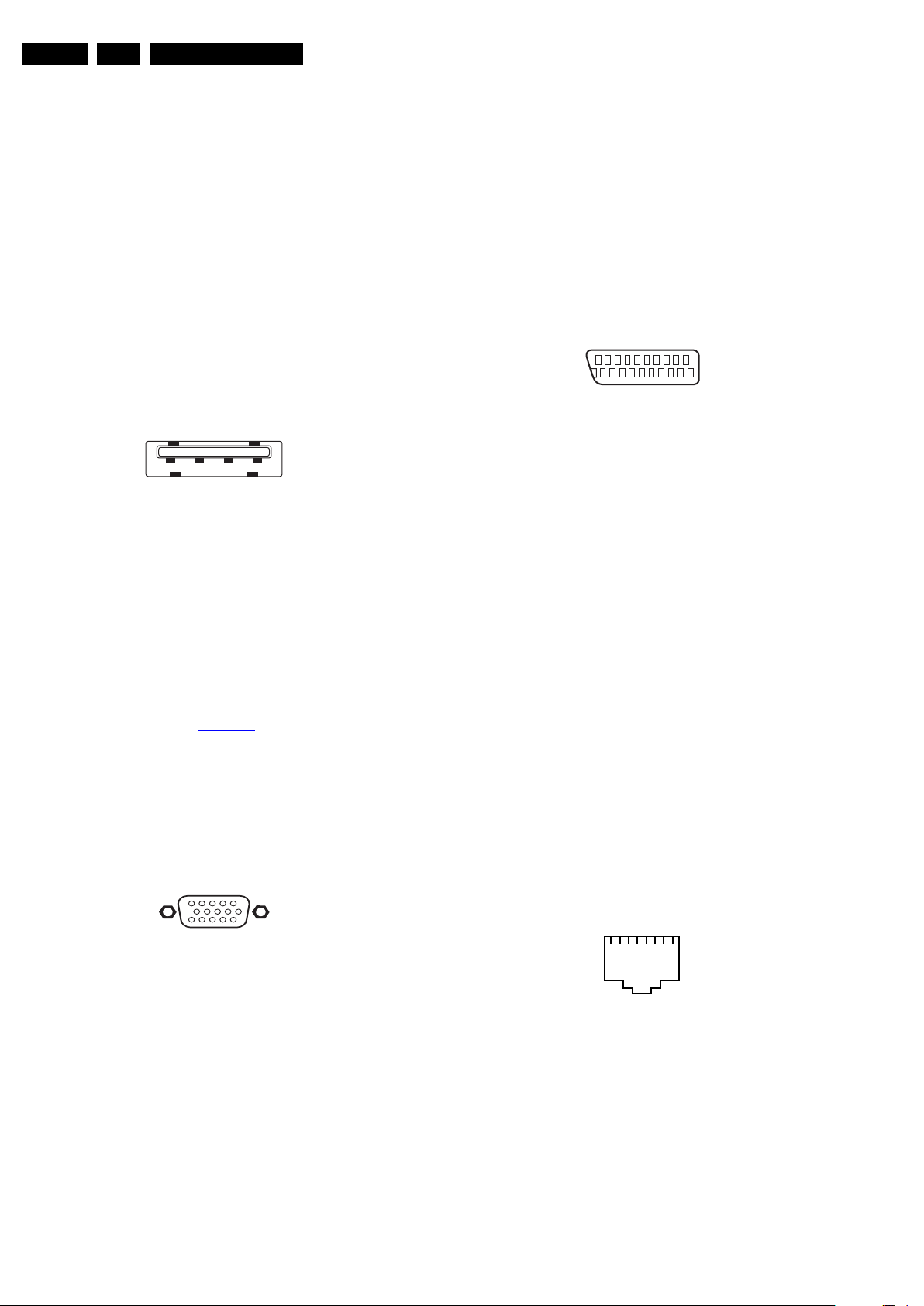

Identification: The bottom line of a type plate gives a 14-digit

serial number. Digits 1 and 2 refer to the production centre (e.g.

AG is Bruges), digit 3 refers to the B.O.M. code, digit 4 refers

to the Service version change code, digits 5 and 6 refer to the

production year, and digits 7 and 8 refer to production week (in

example below it is 2006 week 17). The 6 last digits contain the

serial number.

Figure 3-1 Serial number (example)

3.3.7 Board Level Repair (BLR) or Component Level Repair (CLR)

If a board is defective, consult your repair procedure to decide

if the board has to be exchanged or if it should be repaired on

component level.

If your repair procedure says the board should be exchanged

completely, do not solder on the defective board. Otherwise, it

cannot be returned to the O.E.M. supplier for back charging!

3.3.8 Practical Service Precautions

• It makes sense to avoid exposure to electrical shock.

While some sources are expected to have a possible

dangerous impact, others of quite high potential are of

limited current and are sometimes held in less regard.

• Always respect voltages. While some may not be

dangerous in themselves, they can cause unexpected

reactions that are best avoided. Before reaching into a

powered TV set, it is best to test the high voltage insulation.

It is easy to do, and is a good service precaution.

3.4 Abbreviation List

0/6/12 SCART switch control signal on A/V

board. 0 = loop through (AUX to TV),

6 = play 16 : 9 format, 12 = play 4 : 3

format

AARA Automatic Aspect Ratio Adaptation:

algorithm that adapts aspect ratio to

remove horizontal black bars; keeps

the original aspect ratio

ACI Automatic Channel Installation:

algorithm that installs TV channels

directly from a cable network by

means of a predefined TXT page

ADC Analogue to Digital Converter

AFC Automatic Frequency Control: control

signal used to tune to the correct

frequency

AGC Automatic Gain Control: algorithm that

controls the video input of the feature

box

AM Amplitude Modulation

AP Asia Pacific

AR Aspect Ratio: 4 by 3 or 16 by 9

ASF Auto Screen Fit: algorithm that adapts

aspect ratio to remove horizontal black

bars without discarding video

information

ATSC Advanced Television Systems

Committee, the digital TV standard in

the USA

ATV See Auto TV

Auto TV A hardware and software control

system that measures picture content,

and adapts image parameters in a

dynamic way

AV External Audio Video

AVC Audio Video Controller

AVIP Audio Video Input Processor

B/G Monochrome TV system. Sound

carrier distance is 5.5 MHz

BLR Board-Level Repair

BTSC Broadcast Television Standard

Committee. Multiplex FM stereo sound

system, originating from the USA and

used e.g. in LATAM and AP-NTSC

countries

B-TXT Blue TeleteXT

C Centre channel (audio)

CEC Consumer Electronics Control bus:

remote control bus on HDMI

connections

CL Constant Level: audio output to

connect with an external amplifier

CLR Component Level Repair

ComPair Computer aided rePair

CP Connected Planet / Copy Protection

CSM Customer Service Mode

CTI Color Transient Improvement:

manipulates steepness of chroma

transients

CVBS Composite Video Blanking and

Synchronization

DAC Digital to Analogue Converter

DBE Dynamic Bass Enhancement: extra

low frequency amplification

DDC See “E-DDC”

D/K Monochrome TV system. Sound

carrier distance is 6.5 MHz

DFI Dynamic Frame Insertion

DFU Directions For Use: owner's manual

DMR Digital Media Reader: card reader

DMSD Digital Multi Standard Decoding

DNM Digital Natural Motion

2009-May-08

Page 8

EN 8 Q549.2E LA3.

Precautions, Notes, and Abbreviation List

DNR Digital Noise Reduction: noise

reduction feature of the set

DRAM Dynamic RAM

DRM Digital Rights Management

DSP Digital Signal Processing

DST Dealer Service Tool: special remote

control designed for service

technicians

DTCP Digital Transmission Content

Protection; A protocol for protecting

digital audio/video content that is

traversing a high speed serial bus,

such as IEEE-1394

DVB-C Digital Video Broadcast - Cable

DVB-T Digital Video Broadcast - Terrestrial

DVD Digital Versatile Disc

DVI(-d) Digital Visual Interface (d= digital only)

E-DDC Enhanced Display Data Channel

(VESA standard for communication

channel and display). Using E-DDC,

the video source can read the EDID

information form the display.

EDID Extended Display Identification Data

(VESA standard)

EEPROM Electrically Erasable and

Programmable Read Only Memory

EMI Electro Magnetic Interference

EPLD Erasable Programmable Logic Device

EU Europe

EXT EXTernal (source), entering the set by

SCART or by cinches (jacks)

FDS Full Dual Screen (same as FDW)

FDW Full Dual Window (same as FDS)

FLASH FLASH memory

FM Field Memory or Frequency

Modulation

FPGA Field-Programmable Gate Array

FTV Flat TeleVision

Gb/s Giga bits per second

G-TXT Green TeleteXT

H H_sync to the module

HD High Definition

HDD Hard Disk Drive

HDCP High-bandwidth Digital Content

Protection: A “key” encoded into the

HDMI/DVI signal that prevents video

data piracy. If a source is HDCP coded

and connected via HDMI/DVI without

the proper HDCP decoding, the

picture is put into a “snow vision” mode

or changed to a low resolution. For

normal content distribution the source

and the display device must be

enabled for HDCP “software key”

decoding.

HDMI High Definition Multimedia Interface

HP HeadPhone

I Monochrome TV system. Sound

2

I

C Inter IC bus

2

I

D Inter IC Data bus

2

I

S Inter IC Sound bus

carrier distance is 6.0 MHz

IF Intermediate Frequency

IR Infra Red

IRQ Interrupt Request

ITU-656 The ITU Radio communication Sector

(ITU-R) is a standards body

subcommittee of the International

Telecommunication Union relating to

radio communication. ITU-656 (a.k.a.

SDI), is a digitized video format used

for broadcast grade video.

Uncompressed digital component or

digital composite signals can be used.

The SDI signal is self-synchronizing,

uses 8 bit or 10 bit data words, and has

a maximum data rate of 270 Mbit/s,

with a minimum bandwidth of 135

MHz.

ITV Institutional TeleVision; TV sets for

hotels, hospitals etc.

LS Last Status; The settings last chosen

by the customer and read and stored

in RAM or in the NVM. They are called

at start-up of the set to configure it

according to the customer's

preferences

LATAM Latin America

LCD Liquid Crystal Display

LED Light Emitting Diode

L/L' Monochrome TV system. Sound

carrier distance is 6.5 MHz. L' is Band

I, L is all bands except for Band I

LPL LG.Philips LCD (supplier)

LS Loudspeaker

LVDS Low Voltage Differential Signalling

Mbps Mega bits per second

M/N Monochrome TV system. Sound

carrier distance is 4.5 MHz

MIPS Microprocessor without Interlocked

Pipeline-Stages; A RISC-based

microprocessor

MOP Matrix Output Processor

MOSFET Metal Oxide Silicon Field Effect

Transistor, switching device

MPEG Motion Pictures Experts Group

MPIF Multi Platform InterFace

MUTE MUTE Line

NC Not Connected

NICAM Near Instantaneous Compounded

Audio Multiplexing. This is a digital

sound system, mainly used in Europe.

NTC Negative Temperature Coefficient,

non-linear resistor

NTSC National Television Standard

Committee. Color system mainly used

in North America and Japan. Color

carrier NTSC M/N= 3.579545 MHz,

NTSC 4.43= 4.433619 MHz (this is a

VCR norm, it is not transmitted off-air)

NVM Non-Volatile Memory: IC containing

TV related data such as alignments

O/C Open Circuit

OSD On Screen Display

OTC On screen display Teletext and

Control; also called Artistic (SAA5800)

P50 Project 50: communication protocol

between TV and peripherals

PAL Phase Alternating Line. Color system

mainly used in West Europe (color

carrier= 4.433619 MHz) and South

America (color carrier PAL M=

3.575612 MHz and PAL N= 3.582056

MHz)

PCB Printed Circuit Board (same as “PWB”)

PCM Pulse Code Modulation

PDP Plasma Display Panel

PFC Power Factor Corrector (or Pre-

conditioner)

PIP Picture In Picture

PLL Phase Locked Loop. Used for e.g.

FST tuning systems. The customer

can give directly the desired frequency

POD Point Of Deployment: a removable

CAM module, implementing the CA

system for a host (e.g. a TV-set)

POR Power On Reset, signal to reset the uP

PTC Positive Temperature Coefficient,

non-linear resistor

PWB Printed Wiring Board (same as “PCB”)

2009-May-08

Page 9

Precautions, Notes, and Abbreviation List

EN 9Q549.2E LA 3.

PWM Pulse Width Modulation

QRC Quasi Resonant Converter

QTNR Quality Temporal Noise Reduction

QVCP Quality Video Composition Processor

RAM Random Access Memory

RGB Red, Green, and Blue. The primary

color signals for TV. By mixing levels

of R, G, and B, all colors (Y/C) are

reproduced.

RC Remote Control

RC5 / RC6 Signal protocol from the remote

control receiver

RESET RESET signal

ROM Read Only Memory

RSDS Reduced Swing Differential Signalling

data interface

R-TXT Red TeleteXT

SAM Service Alignment Mode

S/C Short Circuit

SCART Syndicat des Constructeurs

d'Appareils Radiorécepteurs et

Téléviseurs

SCL Serial Clock I

SCL-F CLock Signal on Fast I

SD Standard Definition

SDA Serial Data I

SDA-F DAta Signal on Fast I

2

C

2

C bus

2

C

2

C bus

SDI Serial Digital Interface, see “ITU-656”

SDRAM Synchronous DRAM

SECAM SEequence Couleur Avec Mémoire.

Color system mainly used in France

and East Europe. Color carriers=

4.406250 MHz and 4.250000 MHz

SIF Sound Intermediate Frequency

SMPS Switched Mode Power Supply

SoC System on Chip

SOG Sync On Green

SOPS Self Oscillating Power Supply

SPI Serial Peripheral Interface bus; a 4-

wire synchronous serial data link

standard

S/PDIF Sony Philips Digital InterFace

SRAM Static RAM

SRP Service Reference Protocol

SSB Small Signal Board

STBY STand-BY

SVGA 800 × 600 (4:3)

SVHS Super Video Home System

SW Software

SWAN Spatial temporal Weighted Averaging

Noise reduction

SXGA 1280 × 1024

TFT Thin Film Transistor

THD Total Harmonic Distortion

TMDS Transmission Minimized Differential

Signalling

TXT TeleteXT

TXT-DW Dual Window with TeleteXT

UI User Interface

uP Microprocessor

UXGA 1 600 × 1 200 (4:3)

V V-sync to the module

VESA Video Electronics Standards

Association

VGA 640 × 480 (4:3)

VL Variable Level out: processed audio

output toward external amplifier

VSB Vestigial Side Band; modulation

method

WYSIWYR What You See Is What You Record:

record selection that follows main

picture and sound

WXGA 1280 × 768 (15:9)

XTAL Quartz crystal

XGA 1024 × 768 (4:3)

Y Luminance signal

Y/C Luminance (Y) and Chrominance (C)

signal

YPbPr Component video. Luminance and

scaled color difference signals (B-Y

and R-Y)

YUV Component video

2009-May-08

Page 10

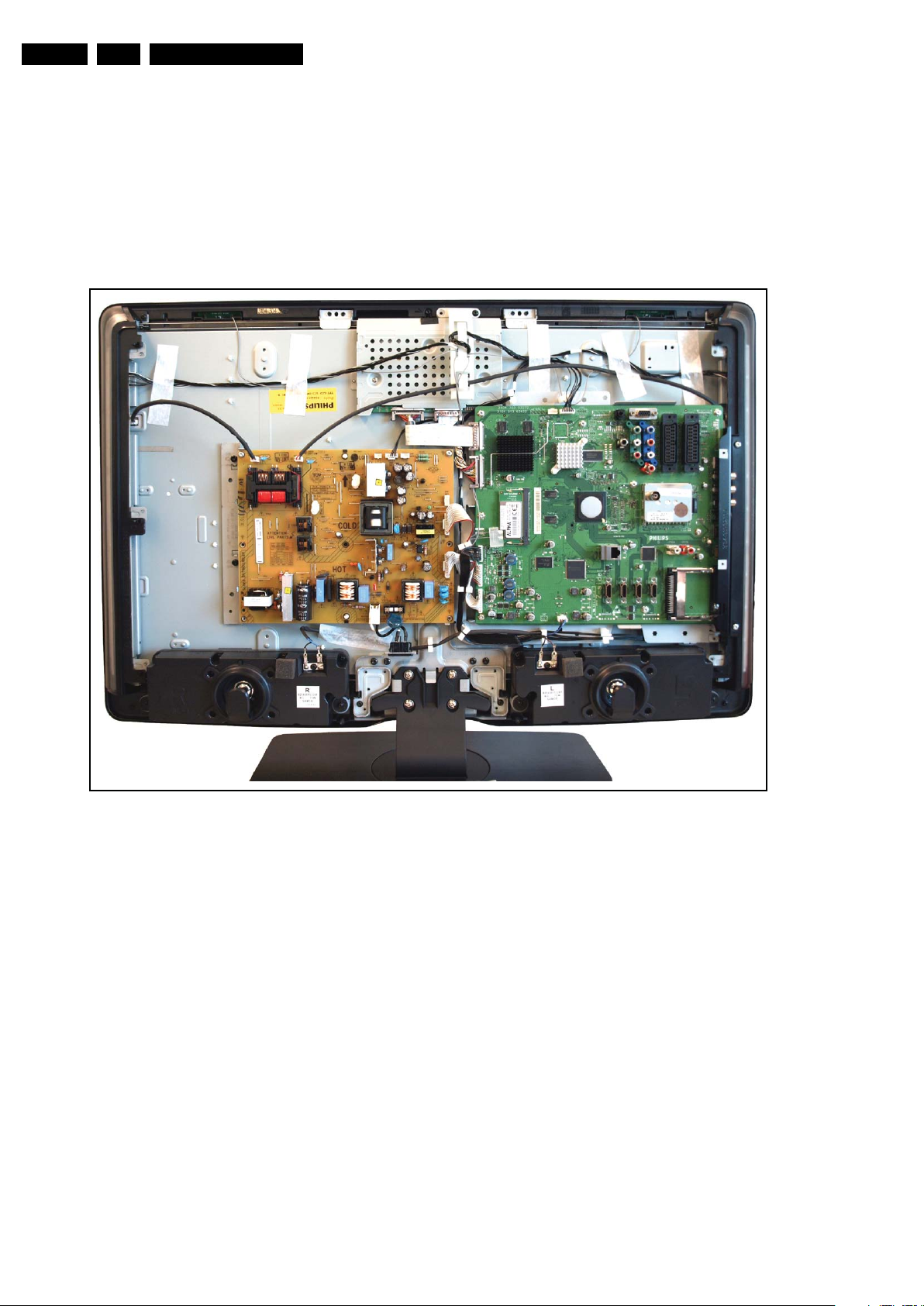

EN 10 Q549.2E LA4.

18310_210_090318.eps

090318

Mechanical Instructions

4. Mechanical Instructions

Index of this chapter:

4.1 Cable Dressing and Taping

4.2 Service Positions

4.3 Assy/Panel Removal

4.4 Set Re-assembly

4.1 Cable Dressing and Taping

Notes:

• Figures below can deviate slightly from the actual situation,

due to the different set executions.

2009-May-08

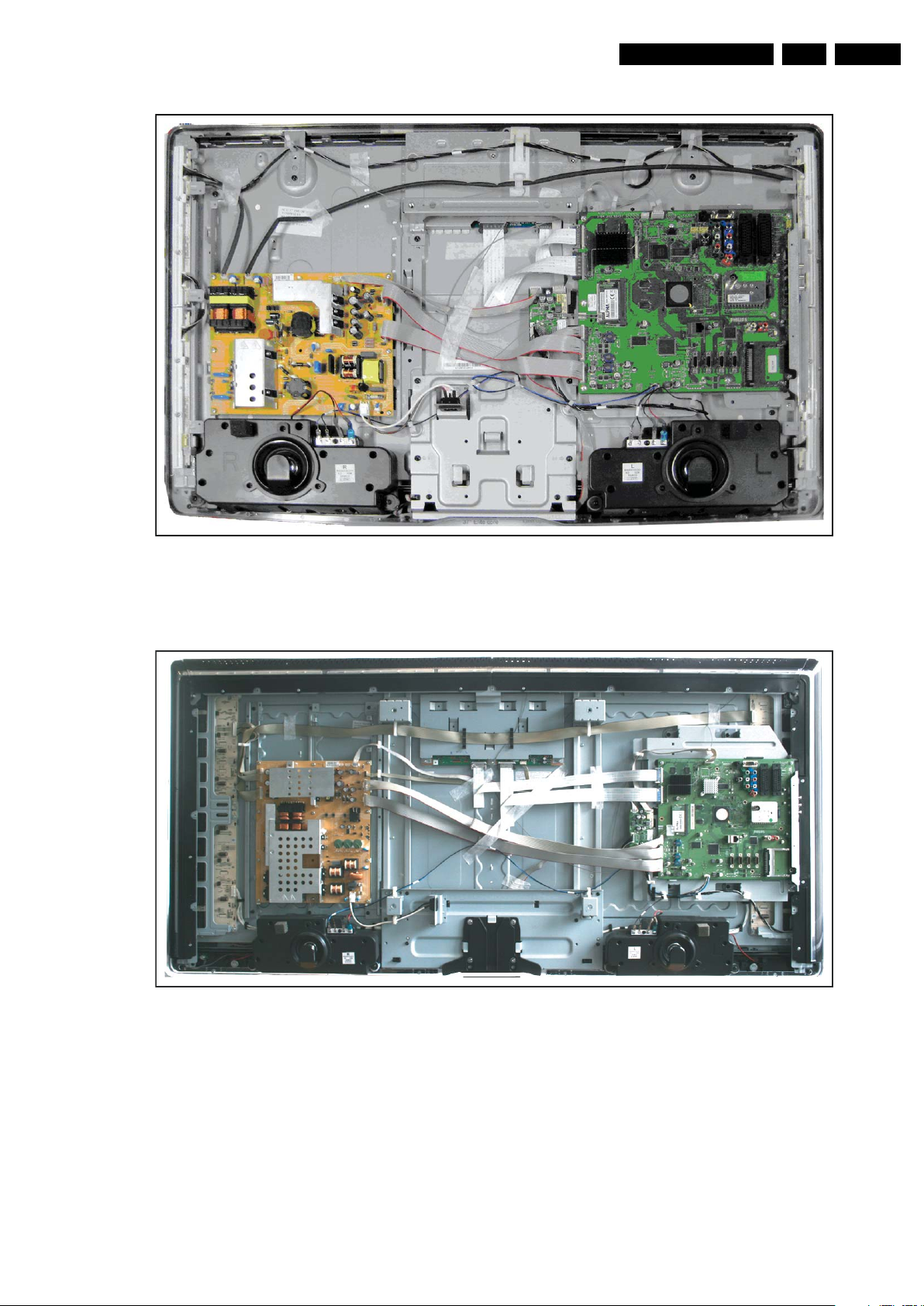

Figure 4-1 Cable dressing 32”

Page 11

Mechanical Instructions

18310_211_090318.eps

090318

18311_200_090506.eps

090506

EN 11Q549.2E LA 4.

Figure 4-2 Cable dressing 37"

Figure 4-3 Cable dressing 56" (21:9)

2009-May-08

Page 12

EN 12 Q549.2E LA4.

E_06532_018.eps

171106

1

Required for sets

42"

1

18310_212_090318.eps

090319

1

18310_213_090318.eps

090319

2

1

2

2

Mechanical Instructions

4.2 Service Positions

For easy servicing of this set, there are a few possibilities

created:

• The buffers from the packaging.

• Foam bars (created for Service).

4.2.1 Foam Bars

4.3.3 Ambi Light

Each Ambi Light unit is mounted on a subframe. Refer to

Figure 4-5

for details.

Figure 4-4 Foam bars

The foam bars (order code 3122 785 90580 for two pieces) can

be used for all types and sizes of Flat TVs.

See Figure 4-4

for details. Sets with a display of 42" and larger,

require four foam bars [1]. Ensure that the foam bars are

always supporting the cabinet and never only the display.

Caution: Failure to follow these guidelines can seriously

damage the display!

By laying the TV face down on the (ESD protective) foam bars,

a stable situation is created to perform measurements and

alignments. By placing a mirror under the TV, you can monitor

the screen.

4.3 Assy/Panel Removal

4.3.1 Rear Cover

Warning: Disconnect the mains power cord before you remove

the rear cover.

Note: it is not necessary to remove the stand while removing

the rear cover.

Removing the Piezo Touch Control Panel PWB requires

special attention. Refer to Piezo Touch Control Panel

details.

1. Remove all screws of the rear cover.

2. Lift the rear cover from the TV. Make sure that wires and

flat coils are not damaged while lifting the rear cover from

4.3.2 Speakers

the set.

Each speaker unit is mounted with two screws. A sticker on the

the unit indicates if it is the right (“R”) or left (“L”) box, seen from

the front side of the set.

When defective, replace the whole unit.

Figure 4-5 Ambi Light unit

1. Remove the Ambi Light cover [1].

2. Unplug the connector(s).

3. The PWB can now be taken from the subframe.

When defective, replace the whole unit.

Note: the screws that secure the AmbiLight units are longer

than the other screws.

4.3.4 Main Supply Panel

1. Unplug all connectors.

2. Remove the fixation screws.

3. Take the board out.

When defective, replace the whole unit.

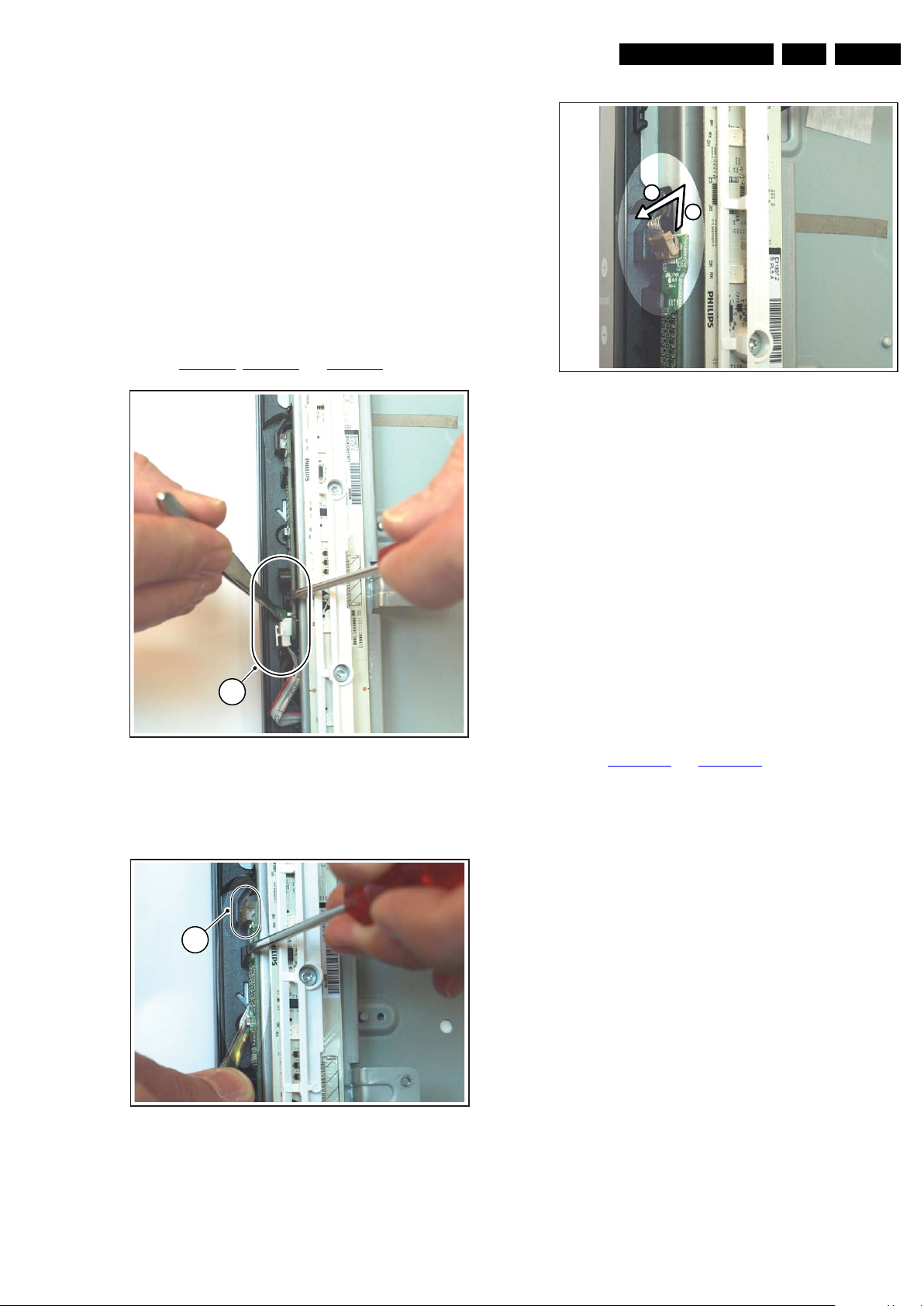

4.3.5 IR & LED Board

Refer to Figure 4-6

for details.

for

2009-May-08

Figure 4-6 IR & LED Board

Page 13

1. Remove the Main Supply Panel as earlier described.

18310_216_090318.eps

090319

2

18310_215_090318.eps

090319

3

4

2. Remove the stand [1] and its subframe [2].

3. Now you gain access the IR & LED board.

When defective, replace the whole unit.

4.3.6 Piezo Touch Control Panel

The flexfoil between Piezo Flexfoil Assy (mounted on the

plastic rim of the set), and the PWB as described below, is

extremely vulnerable. Do not pull hard at the PWB or

flexfoil.

Once the flexfoil has been damaged, the entire plastic rim

of the set (with the touch-control pads) has to be swapped!

The Piezo Touch Control Panel PWB contains ESD sensitive

components, implying that necessary industrial ESD

precautions must be taken during removing or remounting.

Refer to Figure 4-7

, Figure 4-8 and Figure 4-9 for details.

Mechanical Instructions

Figure 4-9 Piezo Touch Control Panel -3-

1. To unplug the flexfoil connector, first the outer part of the

connector has to be moved upwards [3], before this part

can be turned sidewards [4] as shown in the picture. Now

the flexfoil can be removed from the connector and the

PWB can be taken out of the set.

When defective, replace the whole unit.

EN 13Q549.2E LA 4.

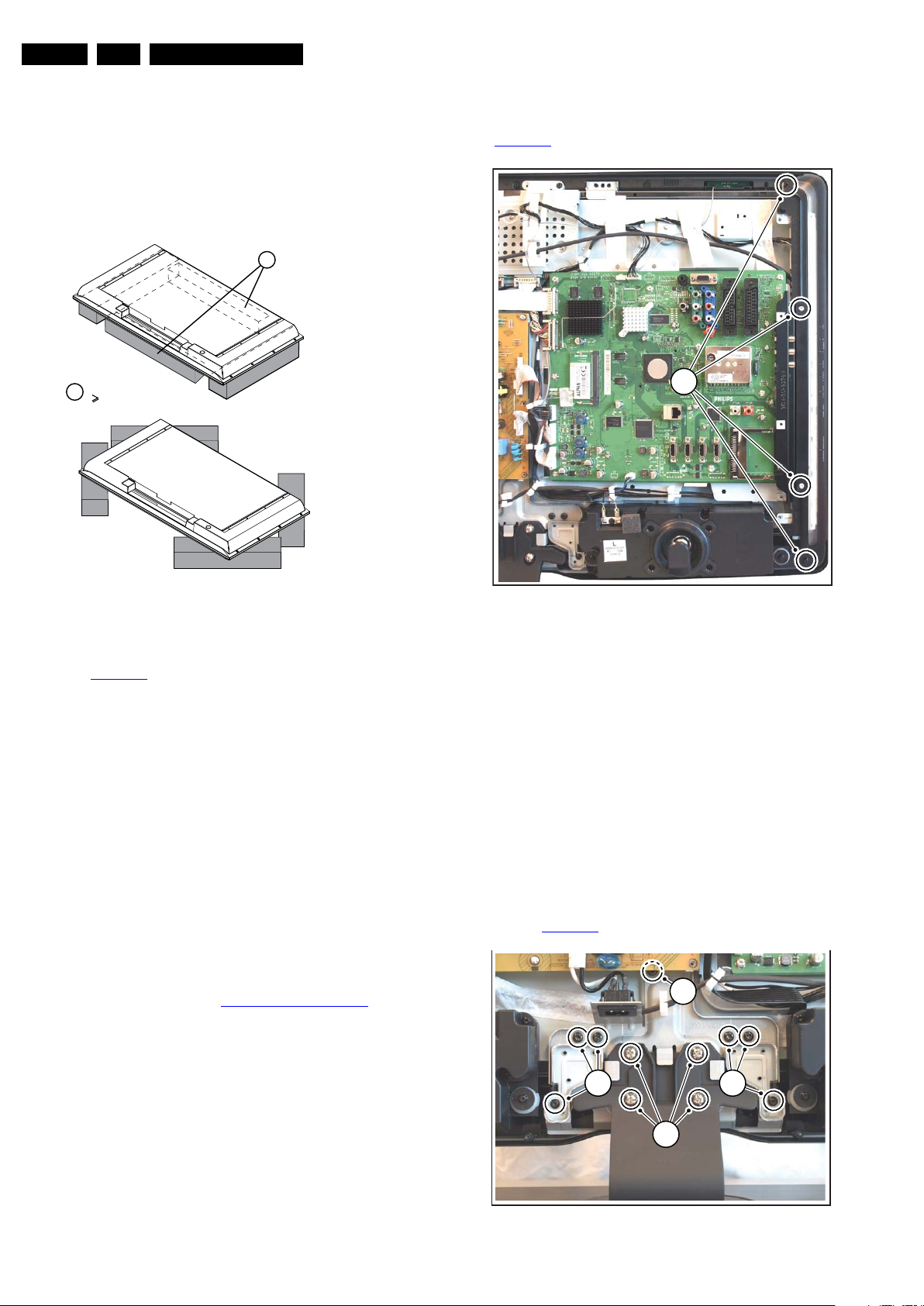

4.3.7 Small Signal Board (SSB)

Caution: It is mandatory to remount screws at their original

position during re-assembly. Failure to do so may result in

damaging the SSB.

1. Remove the Wi-Fi module that is mounted on the SSB.

2. Unplug all connectors.

3. Remove the screws that secure the board.

1

4. The SSB can now be taken out of the set.

4.3.8 LCD Panel

18310_214_090318.eps

Figure 4-7 Piezo Touch Control Panel -1-

1. Gently pull the bottom side of the PWB out of the cabinet

until you can unplug the connector [1].

090319

Refer to Figure 4-10

and Figure 4-11 for details.

1. Remove the Piezo Touch Control Panel PWB as earlier

described.

2. Remove the AL covers as earlier described.

3. Remove both Main Supply Panel and SSB as earlier

described.

4. Remove the subframes of Main Power Supply and SSB [1].

5. Remove both AL subframes (with the AL unit still mounted

on it) by unplugging the connector [2] and removing the

screws [3].

6. Remove all remaining adhesive tapes and remove all

cables from their clamps.

7. Carefully remove the conducting tape [4], it must be reused during re-assembly!

8. Remove the remaining screws (indicated with an arrow)

that hold the plastic rim and remove the rim.

9. Now the LCD Panel can be lifted from the front cabinet.

The panel has to be slided downwards once it has been

lifted, because the brackets on the top cannot be removed

from the cabinet. You will see a conducting foam between

metal front and panel, near the location of the Piezo Touch

Control Panel.

When mounting a new LCD Panel:

1. Check if this conducting foam between panel and metal

front is in place !

Figure 4-8 Piezo Touch Control Panel -2-

2. Re-attach the conducting tape between LCD Panel and

metal rim [4] !

1. Now gently pull the top side of the PWB out of the cabinet

without damaging the flexfoil until you can unplug the

connector [2].

2009-May-08

Page 14

EN 14 Q549.2E LA4.

18310_217_090318.eps

090320

1

4

1

18310_218_090318.eps

090319

3

2

Mechanical Instructions

Figure 4-10 LCD Panel -1-

Figure 4-11 LCD Panel -2-

4.3.9 Wi-Fi antenna

Follow the instructions for LCD Panel until “remove plastic rim”.

After removal of this rim, you gain access to the Wi-Fi

antennas.

4.4 Set Re-assembly

To re-assemble the whole set, execute all processes in reverse

order.

Notes:

• While re-assembling, make sure that all cables are placed

and connected in their original position.

• Pay special attention not to damage the EMC foams in the

set. Ensure that EMC foams are mounted correctly.

2009-May-08

Page 15

Service Modes, Error Codes, and Fault Finding

18310_219_090318.eps

090319

SDM

5. Service Modes, Error Codes, and Fault Finding

EN 15Q549.2E LA 5.

Index of this chapter:

5.1 Test Points

5.2 Service Modes

5.3 Stepwise Start-up

5.4 Service Tools

5.5 Error Codes

5.6 The Blinking LED Procedure

5.7 Protections

5.8 Fault Finding and Repair Tips

5.9 Software Upgrading

5.1 Test Points

As most signals are digital, it will be difficult to measure

waveforms with a standard oscilloscope. However, several key

ICs are capable of generating test patterns, which can be

controlled via ComPair. In this way it is possible to determine

which part is defective.

Perform measurements under the following conditions:

• Service Default Mode.

• Video: Colour bar signal.

• Audio: 3 kHz left, 1 kHz right.

5.2 Service Modes

Service Default mode (SDM) and Service Alignment Mode

(SAM) offers several features for the service technician, while

the Customer Service Mode (CSM) is used for communication

between the call centre and the customer.

This chassis also offers the option of using ComPair, a

hardware interface between a computer and the TV chassis. It

offers the abilities of structured troubleshooting, error code

reading, and software version read-out for all chassis.

(see also section “5.4.1 ComPair

”).

• All service-unfriendly modes (if present) are disabled, like:

– (Sleep) timer.

– Child/parental lock.

– Picture mute (blue mute or black mute).

– Automatic volume levelling (AVL).

– Skip/blank of non-favourite pre-sets.

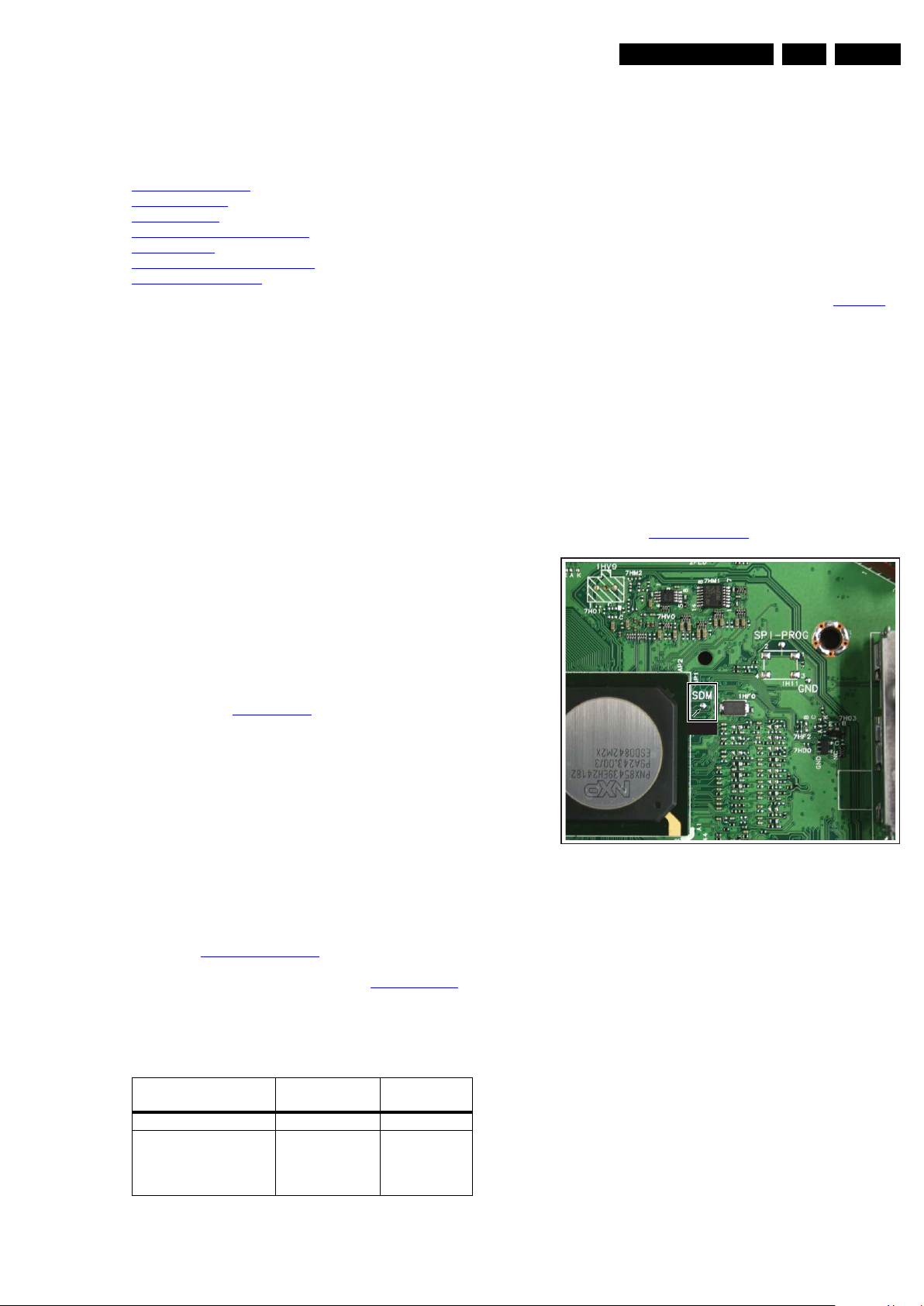

How to Activate SDM

For this chassis there are two kinds of SDM: an analog SDM

and a digital SDM. Tuning will happen according Table 5-1

• Analog SDM: use the standard RC-transmitter and key in

the code “062596”, directly followed by the “MENU” (or

HOME) button.

Note: It is possible that, together with the SDM, the main

menu will appear. To switch it “off”, push the “MENU”(or

HOME) button again.

• Digital SDM: use the standard RC-transmitter and key in

the code “062593”, directly followed by the “MENU” (or

HOME) button.

Note: It is possible that, together with the SDM, the main

menu will appear. To switch it “off”, push the “MENU” (or

HOME) button again.

• Analog SDM can also be activated by grounding for a

moment the solder pad on the SSB, with the indication

“SDM” (see Service mode pad

).

.

Note: For the new model range, a new remote control (RC) is

used with some renamed buttons. This has an impact on the

activation of the Service modes. For instance the old “MENU”

button is now called “HOME” (or is indicated by a “house” icon).

5.2.1 Service Default Mode (SDM)

Purpose

• To create a pre-defined setting, to get the same

measurement results as given in this manual.

• To override SW protections detected by stand-by

processor and make the TV start up to the step just before

protection (a sort of automatic stepwise start-up). See

section “5.3 Stepwise Start-up

• To start the blinking LED procedure where only LAYER 2

errors are displayed. (see also section “5.5 Error Codes

Specifications

Table 5-1 SDM default settings

Region Freq. (MHz)

Europe, AP(PAL/Multi) 475.25 PAL B/G

Europe, AP DVB-T 546.00 PID

• All picture settings at 50% (brightness, colour, contrast).

• All sound settings at 50%, except volume at 25%.

”.

Video: 0B 06 PID

PCR: 0B 06 PID

Audio: 0B 07

Default

system

DVB-T

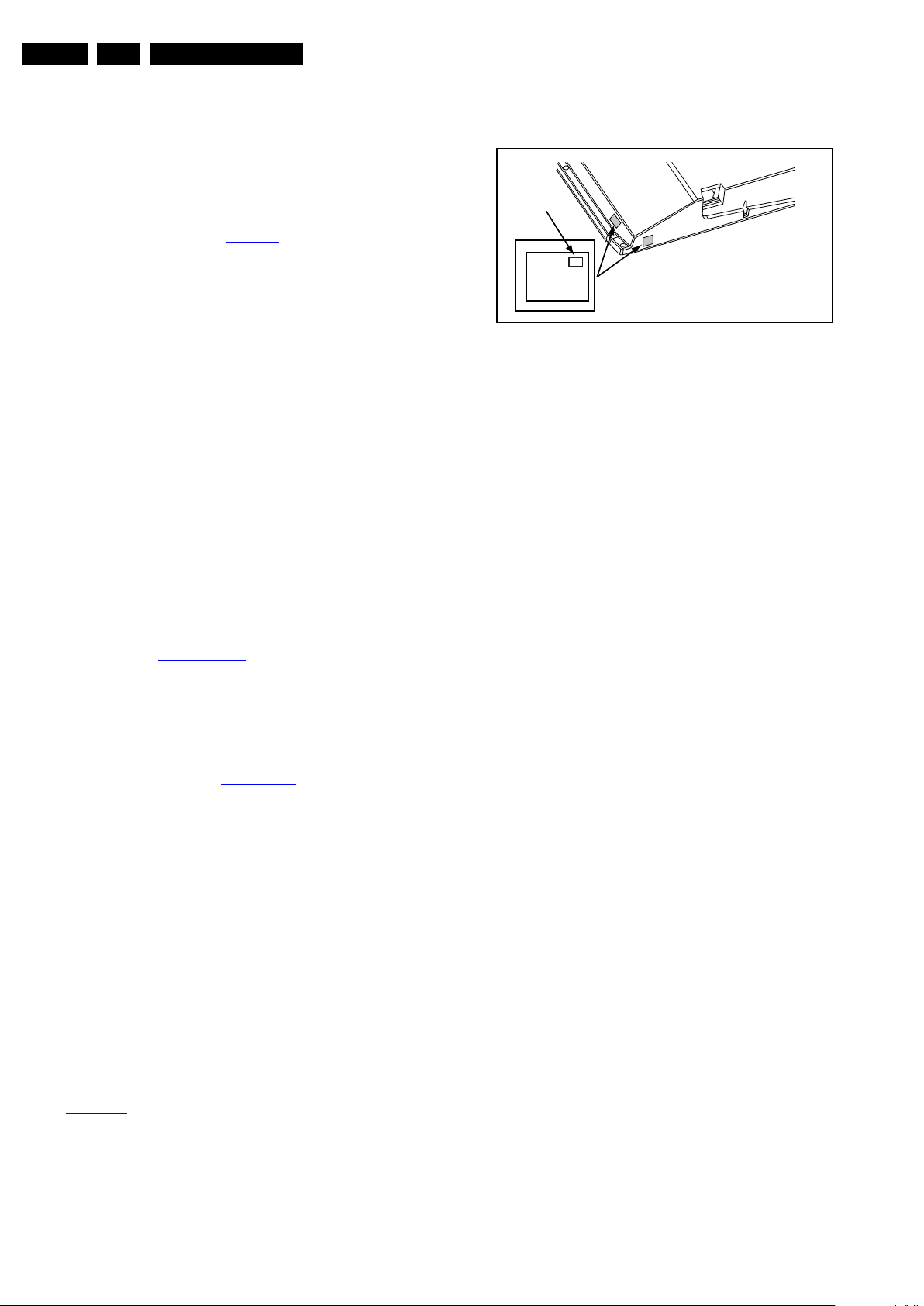

Figure 5-1 Service mode pad

After activating this mode, “SDM” will appear in the upper right

corner of the screen (when a picture is available).

”).

How to Navigate

When the “MENU” (or HOME) button is pressed on the RC

transmitter, the TV set will toggle between the SDM and the

normal user menu.

How to Exit SDM

Use one of the following methods:

• Switch the set to STAND-BY via the RC-transmitter.

• Via a standard customer RC-transmitter: key in “00”sequence.

5.2.2 Service Alignment Mode (SAM)

Purpose

• To perform (software) alignments.

• To change option settings.

• To easily identify the used software version.

2009-May-08

Page 16

EN 16 Q549.2E LA5.

PHILIPS

MODEL:

32PF9968/10

PROD.SERIAL NO:

AG 1A0620 000001

040

39mm

27mm

(CTN Sticker)

Display Option

Code

E_06532_038.eps

240108

Service Modes, Error Codes, and Fault Finding

2009-May-08

• To view operation hours.

• To display (or clear) the error code buffer.

How to Activate SAM

Via a standard RC transmitter: Key in the code “062596”

directly followed by the “INFO” button. After activating SAM

with this method a service warning will appear on the screen,

continue by pressing the “OK” button on the RC.

Contents of SAM (see also Table 6-4

)

• Hardware Info.

– A. SW Version. Displays the software version of the

main software (example: Q5492-1.2.3.4 =

AAAAB_X.Y.W.Z).

• AAAA= the chassis name.

• B= the SW branch version. This is a sequential

number (this is no longer the region indication, as

the software is now multi-region).

• X.Y.W.Z= the software version, where X is the

main version number (different numbers are not

compatible with one another) and Y.W.Z is the sub

version number (a higher number is always

compatible with a lower number).

– B. STBY PROC Version. Displays the software

version of the stand-by processor.

– C. Production Code. Displays the production code of

the TV, this is the serial number as printed on the back

of the TV set. Note that if an NVM is replaced or is

initialized after corruption, this production code has to

be re-written to NVM. ComPair will foresee in a

possibility to do this.

• Operation Hours. Displays the accumulated total of

operation hours (not the stand-by hours). Every time the

TV is switched “on/off”, 0.5 hours is added to this number.

• Errors (followed by maximum 10 errors). The most recent

error is displayed at the upper left (for an error explanation

see section “5.5 Error Codes

”).

• Reset Error Buffer. When “cursor right” (or the “OK

button) is pressed and then the “OK” button is pressed, the

error buffer is reset.

• Alignments. This will activate the “ALIGNMENTS” submenu. See Chapter 6. Alignments.

• Dealer Options. Extra features for the dealers.

• Options. Extra features for Service. For more info

regarding option codes, 6. Alignments

.

Note that if the option code numbers are changed, these

have to be confirmed with pressing the “OK” button before

the options are stored. Otherwise changes will be lost.

• Initialize NVM. The moment the processor recognizes a

corrupted NVM, the “initialize NVM” line will be highlighted.

Now, two things can be done (dependent of the service

instructions at that moment):

– Save the content of the NVM via ComPair for

development analysis, before initializing. This will give

the Service department an extra possibility for

diagnosis (e.g. when Development asks for this).

– Initialize the NVM.

Note: When the NVM is corrupted, or replaced, there is a high

possibility that no picture appears because the display code is

not correct. So, before initializing the NVM via the SAM, a

picture is necessary and therefore the correct display option

has to be entered. Refer to Chapter 6. Alignments

for details.

To adapt this option, it’s advised to use ComPair (the correct

HEX values for the options can be found in Chapter 6.

Alignments) or a method via a standard RC (described below).

Changing the display option via a standard RC: Key in the

code “062598” directly followed by the “MENU” (or HOME)

button and “XXX” (where XXX is the 3 digit decimal display

code as mentioned in Table 6-3

digits, also the leading zero’s. If the above action is successful,

the front LED will go out as an indication that the RC sequence

). Make sure to key in all three

was correct. After the display option is changed in the NVM, the

TV will go to the Stand-by mode. If the NVM was corrupted or

empty before this action, it will be initialized first (loaded with

default values). This initializing can take up to 20 seconds.

Figure 5-2 Location of Display Option Code sticker

• Store - go right. All options and alignments are stored

when pressing “cursor right” (or the “OK” button) and then

the “OK”-button.

• SW Maintenance.

– SW Events. Not useful for Service purposes. In case

of specific software problems, the development

department can ask for this info.

– HW Events. Not useful for Service purposes. In case

of specific software problems, the development

department can ask for this info.

• Operation hours display. Displays the accumulated total

of display operation hours. So, this one keeps up the

lifetime of the display itself, mainly to compensate the

degeneration behaviour.

• Test settings. For development purposes only.

• Development file versions. Not useful for Service

purposes, this information is only used by the development

department.

• Upload to USB. To upload several settings from the TV to

an USB stick, which is connected to the SSB. The items are

“Channel list”, “Personal settings”, “Option codes”,

“Display-related alignments” and “History list”. First a

directory “repair\” has to be created in the root of the

USB stick. To upload the settings select each item

separately, press “cursor right” (or the “OK” button),

confirm with “OK” and wait until “Done” appears. In case

the download to the USB stick was not successful “Failure”

will appear. In this case, check if the USB stick is

connected properly and if the directory “repair” is present in

the root of the USB stick. Now the settings are stored onto

the USB stick and can be used to download onto another

TV or other SSB. Uploading is of course only possible if the

software is running and if a picture is available. This

method is created to be able to save the customer’s TV

settings and to store them into another SSB.

• Download to USB. To download several settings from the

USB stick to the TV, same way of working needs to be

followed as with uploading. To make sure that the

download of the channel list from USB to the TV is

executed properly, it is necessary to restart the TV and

tune to a valid preset if necessary.

Note: The “History list item” can not be downloaded from

USB to the TV. This is a “read-only” item. In case of

specific problems, the development department can ask

for this info.

How to Navigate

• In SAM, the menu items can be selected with the

“CURSOR UP/DOWN” key on the RC-transmitter. The

selected item will be highlighted. When not all menu items

fit on the screen, move the “CURSOR UP/DOWN” key to

display the next/previous menu items.

• With the “CURSOR LEFT/RIGHT” keys, it is possible to:

– (De) activate the selected menu item.

– (De) activate the selected sub menu.

Page 17

Service Modes, Error Codes, and Fault Finding

EN 17Q549.2E LA 5.

• With the “OK” key, it is possible to activate the selected

action.

How to Exit SAM

Use one of the following methods:

• Switch the TV set to STAND-BY via the RC-transmitter.

• Via a standard RC-transmitter, key in “00” sequence, or

select the “BACK” key.

5.2.3 Customer Service Mode (CSM)

Purpose

When a customer is having problems with his TV-set, he can

call his dealer or the Customer Helpdesk. The service

technician can then ask the customer to activate the CSM, in

order to identify the status of the set. Now, the service

technician can judge the severity of the complaint. In many

cases, he can advise the customer how to solve the problem,

or he can decide if it is necessary to visit the customer.

The CSM is a read only mode; therefore, modifications in this

mode are not possible.

When in this chassis CSM is activated, a testpattern will be

displayed during 5 seconds (1 second Blue, 1 second Green

and 1 second Red, then again 1 second Blue and 1 second

Green). This test pattern is generated by the PNX5100. So if

this test pattern is shown, it could be determined that the back

end video chain (PNX5100, LVDS, and display) of the SSB is

working.

When CSM is activated and there is a USB stick connected to

the TV, the software will dump the complete CSM content to the

USB stick. The file (Csm.txt) will be saved in the root of the USB

stick. This info can be handy if no information is displayed.

Also when CSM is activated, the LAYER 1 error is displayed via

blinking LED. Only the latest error is displayed. (see also

section 5.5 Error Codes

How to Activate CSM

Key in the code “123654” via the standard RC transmitter.

Note: Activation of the CSM is only possible if there is no (user)

menu on the screen!

How to Navigate

By means of the “CURSOR-DOWN/UP” knob on the RCtransmitter, can be navigated through the menus.

Contents of CSM

The contents are reduced to 3 pages: General, Software

versions and Quality items. The group names itself are not

shown anywhere in the CSM menu.

).

NVM. ComPair will foresee in a possibility to do this. This

identification number is the 12nc number of the SSB.

• 12NC display. Shows the 12NC of the display.

• 12NC supply. Shows the 12NC of the supply.

• 12NC “fan board”. Shows the 12NC of the “fan board”module (for sets with LED backlight)

• 12NC “LED Dimming Panel”. Shows the 12NC of the

LED dimming Panel (for sets with LED backlight).

Software versions

• Current main SW. Displays the built-in main software

version. In case of field problems related to software,

software can be upgraded. As this software is consumer

upgradeable, it will also be published on the Internet.

Example: Q5492_1.2.3.4

• Standby SW. Displays the built-in stand-by processor

software version. Upgrading this software will be possible

via ComPair or via USB (see section 5.9 Software

Upgrading).

Example: STDBY_88.68.1.2.

• MOP ambient light SW. Displays the MOP ambient light

EPLD SW.

• LED Dimming SW. Displays the LED Dimming EPLD SWversion (for sets with LED backlight).

• Local contrast SW. Displays the MOP local contrast SWversion.

Quality items

• Signal quality. Poor / average /good

• Child lock. Not active / active. This is a combined item for

locks. If any lock (Preset lock, child lock, lock after or

parental lock) is active, the item shall show “active”.

• HDMI HDCP key. Indicates if the HDMI keys (or HDCP

keys) are valid or not. In case these keys are not valid and

the customer wants to make use of the HDMI functionality,

the SSB has to be replaced.

• Ethernet MAC address. Displays the MAC address

present in the SSB.

• Wireless MAC address. Displays the wireless MAC

address to support the Wi-Fi functionality.

• BDS key. Indicates if the “BDS level 1” key is valid or not.

• CI slot present. If the common interface module is

detected the result will be “YES” or “NO”.

• HDMI input format. The detected input format of the

HDMI.

• HDMI audio input stream. The HDMI audio input stream

is displayed: present / not present.

• HDMI video input stream. The HDMI video input stream

is displayed: present / not present.

How to Exit CSM

Press “MENU” (or HOME) / “Back” key on the RC-transmitter.

General

• Set Type. This information is very helpful for a helpdesk/

workshop as reference for further diagnosis. In this way, it

is not necessary for the customer to look at the rear of the

TV-set. Note that if an NVM is replaced or is initialized after

corruption, this set type has to be re-written to NVM.

ComPair will foresee in a possibility to do this.

• Production Code. Displays the production code (the serial

number) of the TV. Note that if an NVM is replaced or is

initialized after corruption, this production code has to be

re-written to NVM. ComPair will foresee a in possibility to

do this.

• Installed date. Indicates the date of the first installation of

the TV. This date is acquired via time extraction.

• Options 1. Gives the option codes of option group 1 as set

in SAM (Service Alignment Mode).

• Options 2. Gives the option codes of option group 2 as set

in SAM (Service Alignment Mode).

• 12NC SSB. Gives an identification of the SSB as stored in

NVM. Note that if an NVM is replaced or is initialized after

corruption, this identification number has to be re-written to

2009-May-08

Page 18

EN 18 Q549.2E LA5.

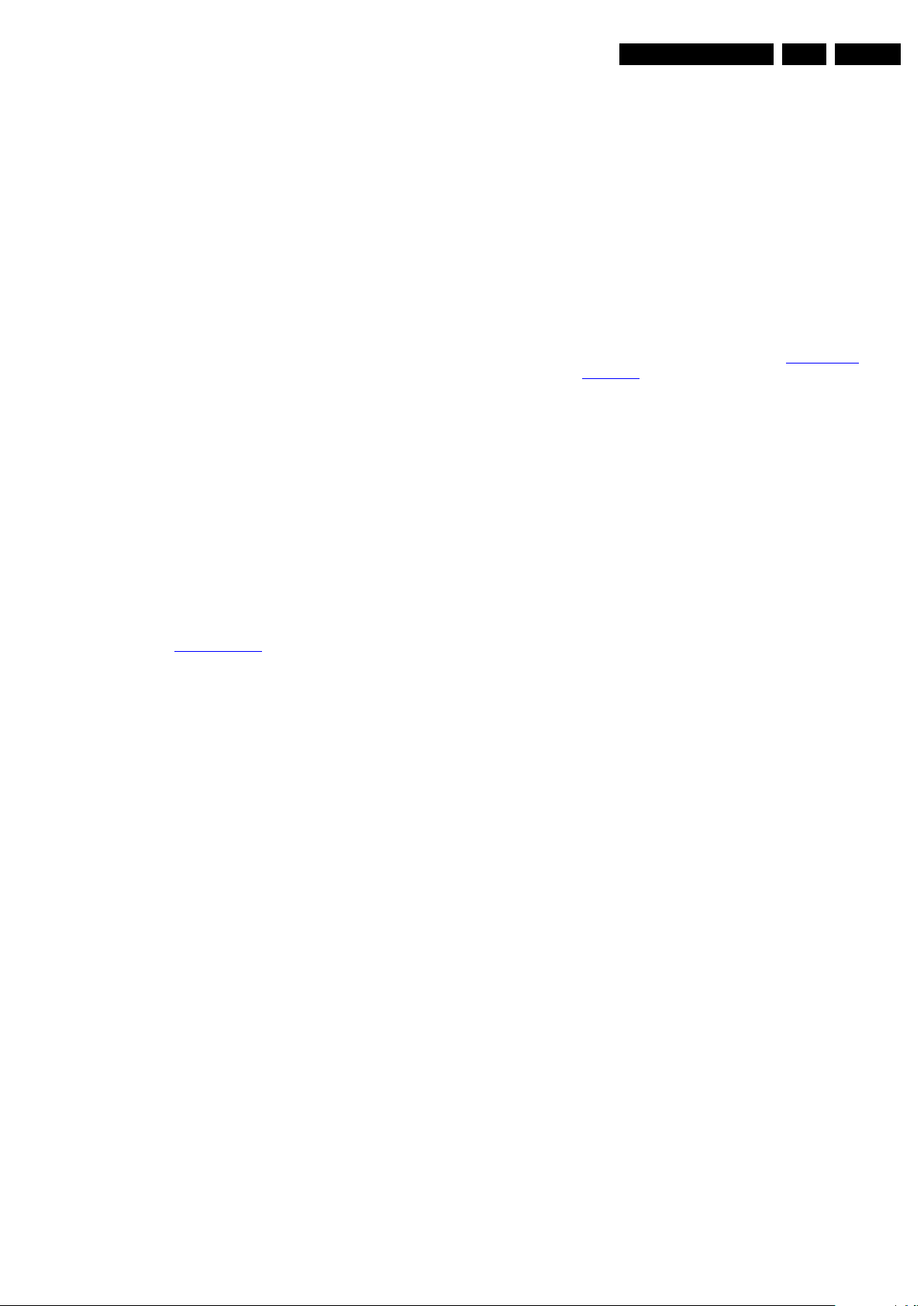

Active

Semi

St by

St by

Mains

on

Mains

off

GoToProtection

-WakeUp requested

-Acquisition needed

-No data Acquisition

required

-tact SW pushed

-last status is hibernate

after mains ON

- St by requested

-tact SW pushed

WakeUp

requested

Protection

WakeUp

requested

(SDM)

GoToProtection

Hibernate

-Tact switch Pushed

-last status is hibernate

after mains ON

Tact switch

pushed

I_17660_124.eps

140308

Service Modes, Error Codes, and Fault Finding

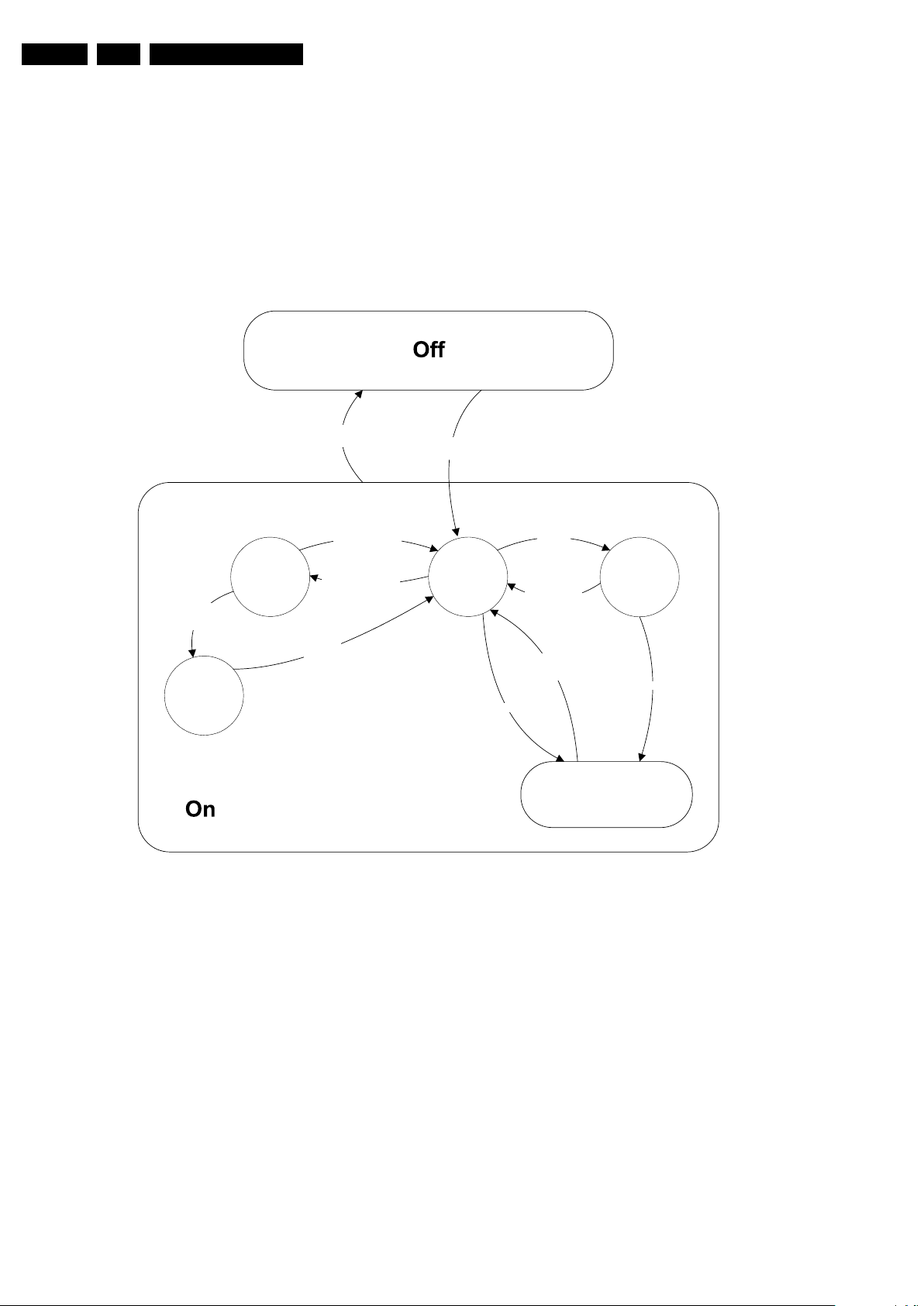

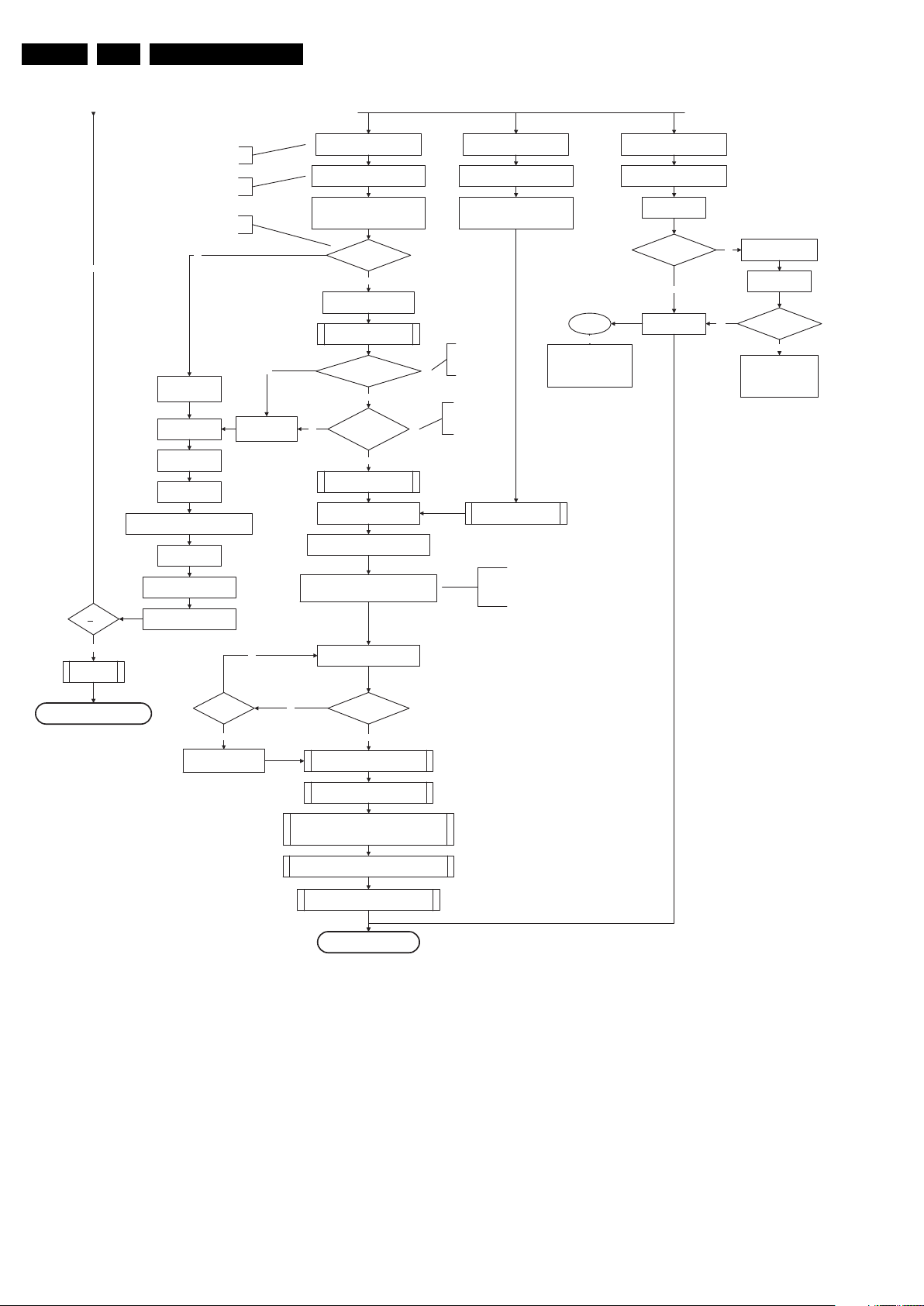

5.3 Stepwise Start-up

When the TV is in a protection state due to an error detected by

stand-by software (error blinking is displayed) and SDM is

activated via shortcutting the pins on the SSB, the TV starts up

until it reaches the situation just before protection. So, this is a

kind of automatic stepwise start-up. In combination with the

start-up diagrams below, you can see which supplies are

present at a certain moment. Important to know is, that if e.g.

the 3V3 detection fails and thus error layer 2 = 18 is blinking

while the TV is restarted via SDM, the Stand-by Processor will

enable the 3V3, but the TV set will not go to protection now.

The TV will stay in this situation until it is reset (Mains/AC

Power supply interrupted). Caution: in case the start-up in this

mode with a faulty FET 7U08 is done, you can destroy all IC’s

supplied by the +3V3, due to overvoltage (12V on 3V3-line). It

is recommended to measure first the FET 7U08 or others

FET’s on shortcircuit before activating SDM via the service

pads.

The abbreviations “SP” and “MP” in the figures stand for:

• SP: protection or error detected by the Stand-by

Processor.

• MP: protection or error detected by the MIPS Main

Processor.

2009-May-08

Figure 5-3 Transition diagram

Page 19

No

EJTAG probe

connected ?

No

Yes

Release AVC system r eset

Feed warm boot script

To I_17660_125b.eps To I_17660_125b.eps

Cold boot?

Yes

No

Set I²C slave address

of Standby µP to (A0h)

An EJTAG probe (e.g. WindPower ICE probe) can

be connected for Linux Kernel debugging

purposes.

This will a llow access to NVM a nd

NAND FLASH and can not be done

earlier because the FLASH needs to

be in Write Protect as long as the

supplies are not available.

Detect EJTAG debug probe

(pulling pin of the probe interface to

ground by inserting EJTAG probe)

Relea se AVC system r eset

Feed cold boot script

Release AVC system r eset

Feed initializing boot script

disable alive mechanism

Initialise I/O pins of the st-by µP:

- Switch reset-AVCLOW (reset state)

- Switch WP-NandFlash LOW (protected)

- Switch reset-system LOW (reset state)

- Switch reset-5100 LOW (reset state)

- Switch reset-Ethernet LOW (reset state)

- Switch reset-ST7100 LOW (reset state)

- keep reset-NVM high, Audio-reset and Audio-Mute-Up HIGH

Off

Standby Supply starts running.

All standby supply voltages become available .

st-by µ P resets

Stand by or

Protection

Mains is app lied

- Switch Audio-Reset high.

It is low in the standby mode if the standby

mode lasted longer than 10s.

start keyboard scanning, RC detection. Wake up reasons are

off.

If the protection state was left by short circuiting the

SDM pins, detection of a protection condition during

startup will stall the startup. Protection conditions in a

playing set will be ignored. The protection mode will

not be entered.

Switch LOW the RESET-NVM line to allow access to NVM. (Add a

2ms delay before trying to address the NVM to allow correct NVM

initialization, this is not issue in this setup, the delay is automatically

covered by the architectural setup)

Release Reset-PNX5100.

PNX5100 will start b ooting.

Wait 10ms (minimum) to allow the bootscript

of the PNX5100 to configure the PCI arbiter

Before PNX8541 boots, the PNX5100 should have

set its PCI arbiter (bootscript command). To allow

this, approx. 1ms is needed. This 1ms is extended

to 10ms to also give some relaxation to the supplies.

Switch HIGH the WP-NandFlash to

allow access to NAND Flash

+12V, +/-12Vs, AL and Bolt-on power

is switched on, followed by the +1V2 DCDC converter

Enable the supply fault detection

algorithm

No

Yes

Detect-1 I/O line

High?

Switch ON Platform and display supply by switching

LOW the Standby line.

This enables the +3V3 and

+5V converter. As a result,

also +5V-tuner, +2V5, +1V8PNX8541 and +1V8-PNX5100

become available.

yes

Enable the DCDC converter for +3V3 and

+5V. (EN ABLE-3V3)

Voltage output error:

Layer1: 2

Layer2: 18

Important remark; the appearance of the +12V

will start the +1V2 DCDC converter automatically

No

Yes

Supply-fault I/O

High?

The supply-fault line is a

combination of the DCDC

converters and the audio

protection line.

1V2 DCDC or class D error:

Layer1: 2

Layer2: 19

Enter protection

No

Detect2 high received

within 1 second?

Power-OK er ror:

Layer1: 3

Layer2: 16

Enter protection

Yes

No

Supply-fault I/O

High?

3V3 / 5V DCDC or class D error:

Layer1: 2

Layer2: 11

Enter protection

Wait 50ms

Enter protection

Delay of 50ms needed because of the latency of the detect-1 circuit.

This delay is also needed for the PNX5100. The reset of the

PNX5100 should only be released 10ms after powering the IC.

Detect2 should be polled on the standard 40ms

interval and startup should be continued when

detect2 becomes high.

Yes

No

Detect -2 I/ O line

High?

Disable 3V3, swit ch standby

line high and wait 4 seconds

Added to make the system more robust to

power dips during startup. At this point the

regular supply fault detection algorithm which

normally detects power dips is not up and

running yet.

I_17660_125a.eps

140308

Service Modes, Error Codes, and Fault Finding

EN 19Q549.2E LA 5.

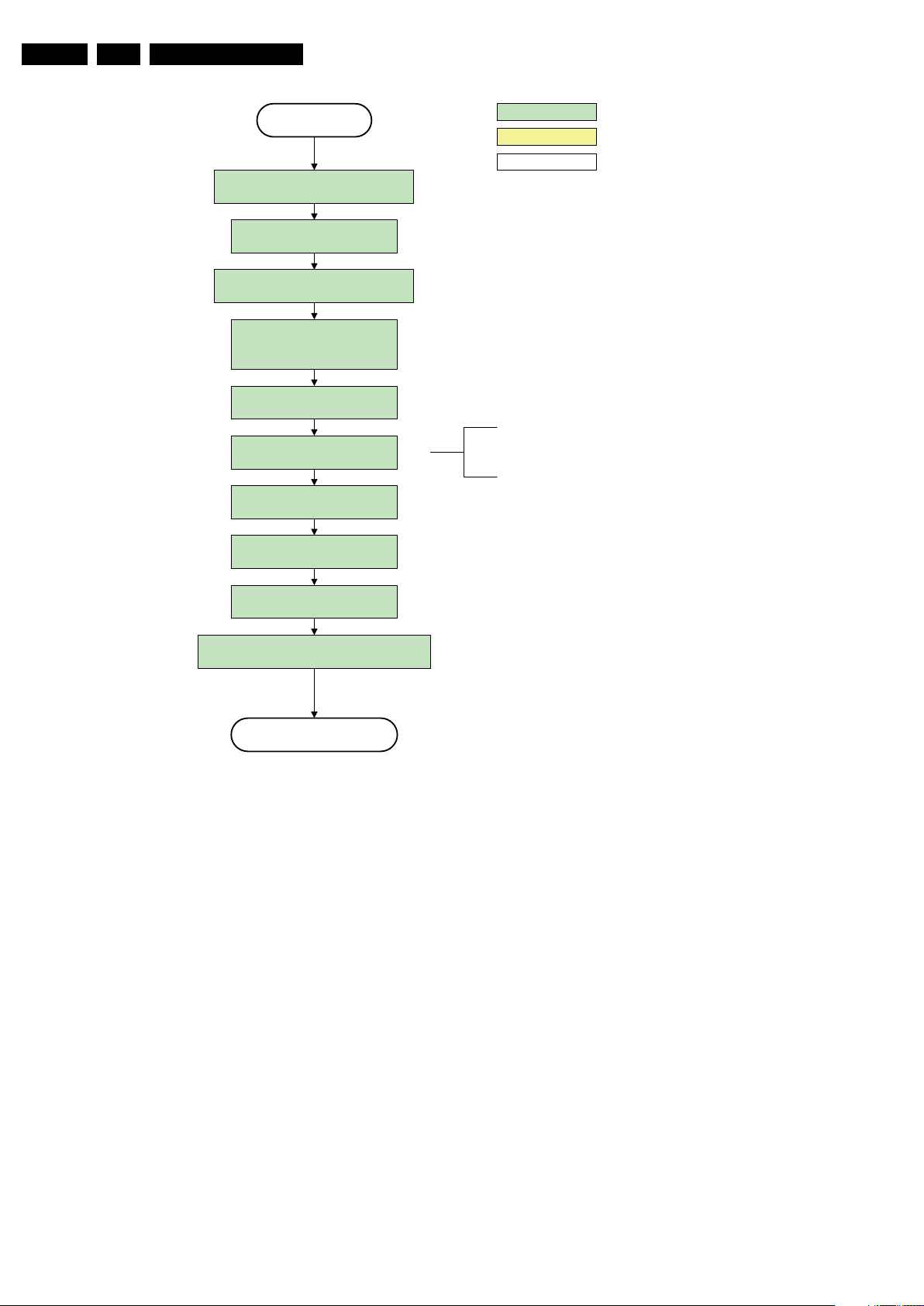

Figure 5-4 “Off” to “Semi Stand-by” flowchart (part 1)

2009-May-08

Page 20

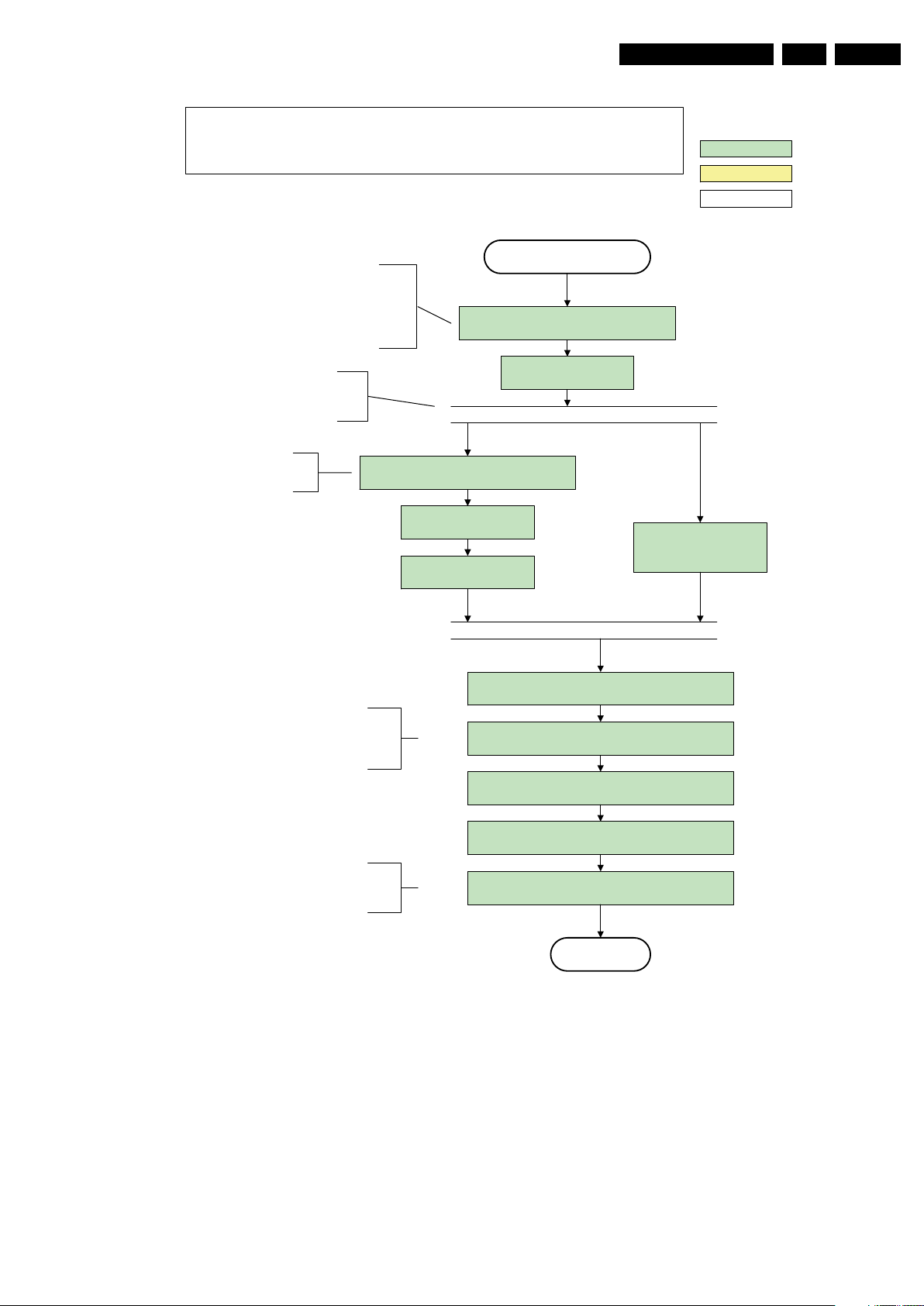

EN 20 Q549.2E LA5.

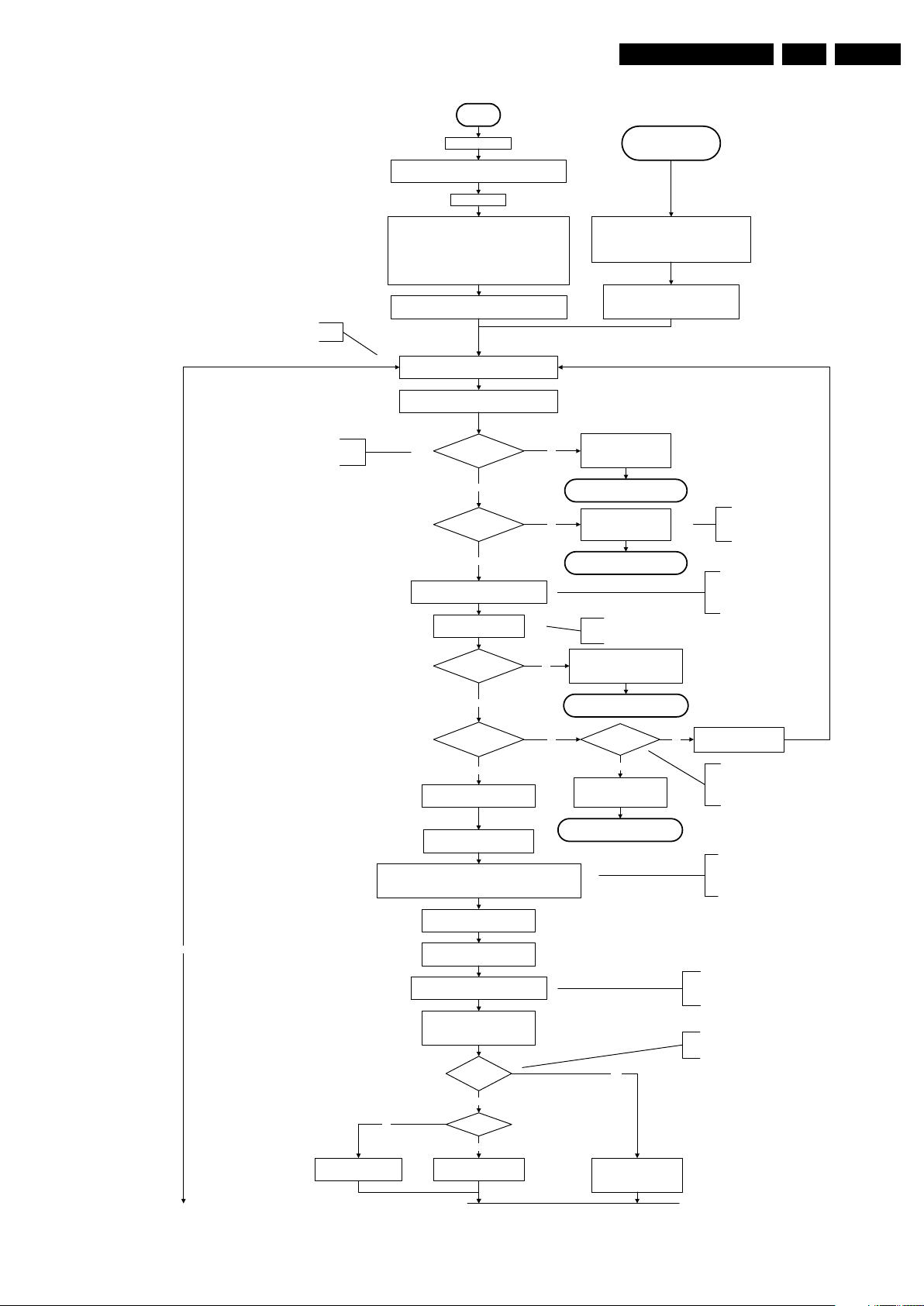

Yes

MIPS reads the wake up reason

from standby µP.

Semi-Standby

initialize tuner, Master IF and channel

decoder

Initialize video processing IC's

Initialize source select ion

initialize Aut oTV

3-th try?

No

Blink Code as

error code

Bootscript ready

in 1250 ms?

Yes

No

Enable Alive check mechanism

Wait until AVC starts to

communicate

SW initializatio n

succeeded

within 20s?

No

Switch Standby

I/O line high.

RPC start (comm. protocol)

Set I²C slave address

of Standby µP to (60h)

Yes

Disable all supply related protections and

switch off the +3V3 +5V DC/DC converter.

switch off the remaining DC/DC

converters

Wait 5ms

Switch AVC PNX85 41

in reset (active low )

Wait 10ms

Switch the NVM reset

line HIGH.

Flash to Ram

image transfer succeeded

within 30s?

No

Yes

Code =

Layer1: 2

Layer2: 53

Code =

Layer1: 2

Layer2: 15

Initialize Ambilight with Lights off.

Timing need to be updated if

more mature info is available.

Timing needs to

be updated if more

matur e info is

available.

Timing needs to be

updated if more

matur e info is

available.

Downloaded

successfully ?

Download firmware into the channel

decoder

Third try? No

No

Yes

Log channel decoder error:

Layer1: 2

Layer2: 37

Yes

Initialize audio

Enter protection

Release reset MPEG4 module:

BOLT-ON-IO: High

MPEG4 module will start booting

autonomously.

Wait 3000 ms

Start alive IIC polling

mechanism

POR polling positive ?

yes

No

Log SW event:

STi7100PorFailure

Wait 200 ms

POR polling positive?yes

No

bootSTi7100PorFailure:

Log HW error

Layer1: 2

Layer2: 38

and generate cold boot

Alive

polling

Log SW event

STi7100AliveFailedError

and generate fast cold reboot

eventually followed by a cold

reboot.

NOK

Reset-system is switched HIGH by the

AVC at the end of the bootscript

AVC releases Reset-Ethernet when the

end of the AVC boot-script is detected

This cannot be done through the bootscript,

the I/O is on the standby µP

Reset- system is connected to USB

From I_17660_125a.eps From I_17660_125a.eps

-reset,

4to1HDMI Mux and channel decoder.

Reset-Audio and Audio-Mute-Up are

switched by MIPS code later on in the

startup process

Reset-syst em is switched HIGH by the

AVC at the end of the bootscript

AVC releases Reset-Ethernet when the

end of the AVC boot-script is detected

Reset-Audio and Audio-Mute-Up are

switched by MIPS code later on in the

startup process

Switch on the display in case of a LED backlight

display by sending the TurnOnDisplay(1) (I²C)

command to the PNX5100

In case of a LED backlight display, a LED DIM panel is

present which is fed by the Vdisplay. To power the LED DIM

Panel, the Vdisplay switch driven by the PNX5100 must be

closed. The display startup sequence is taken care of by the

LED DIM panel.

I_17660_125b.eps

140308

Service Modes, Error Codes, and Fault Finding

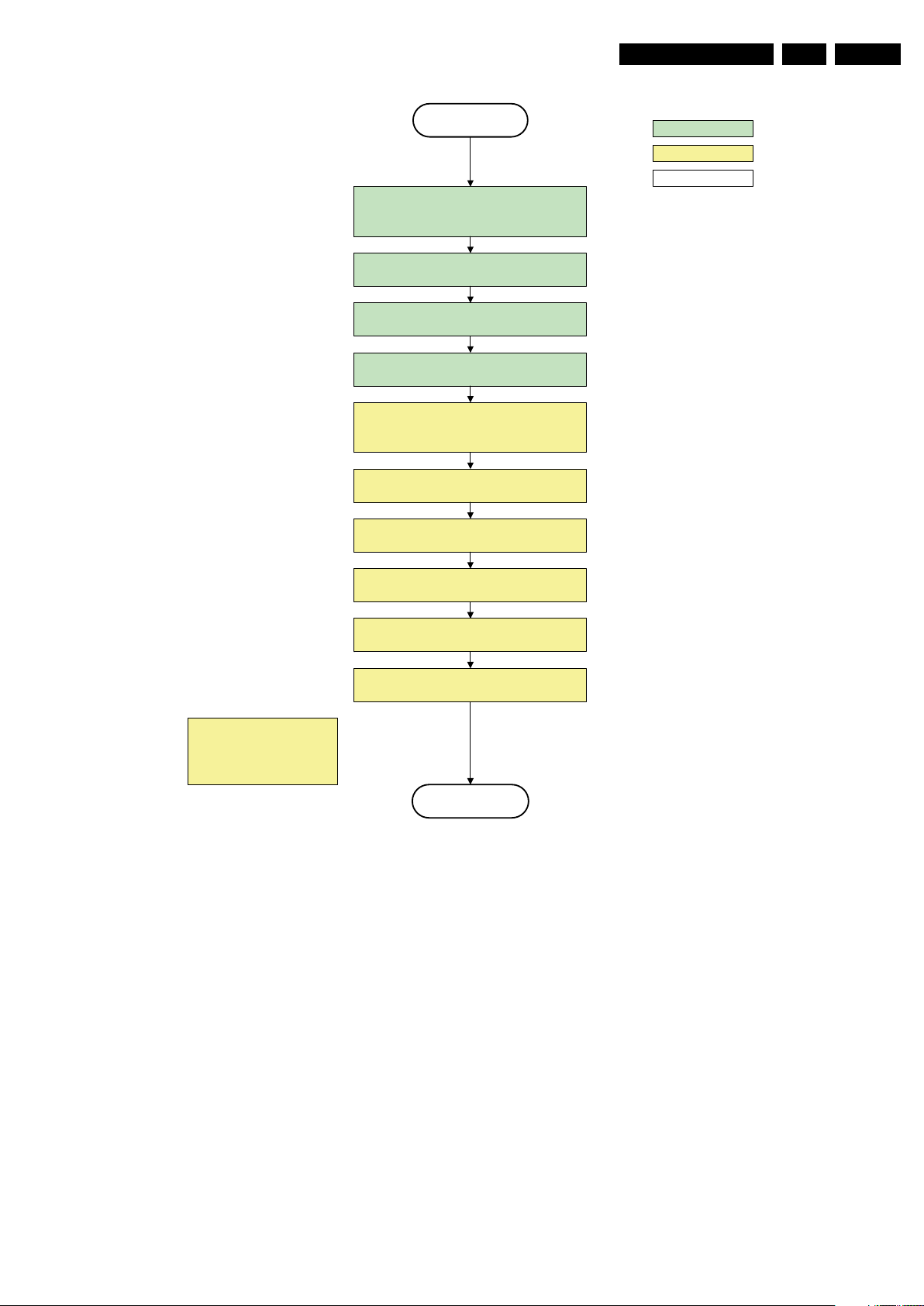

Figure 5-5 “Off” to “Semi Stand-by” flowchart (part 2)

2009-May-08

Page 21

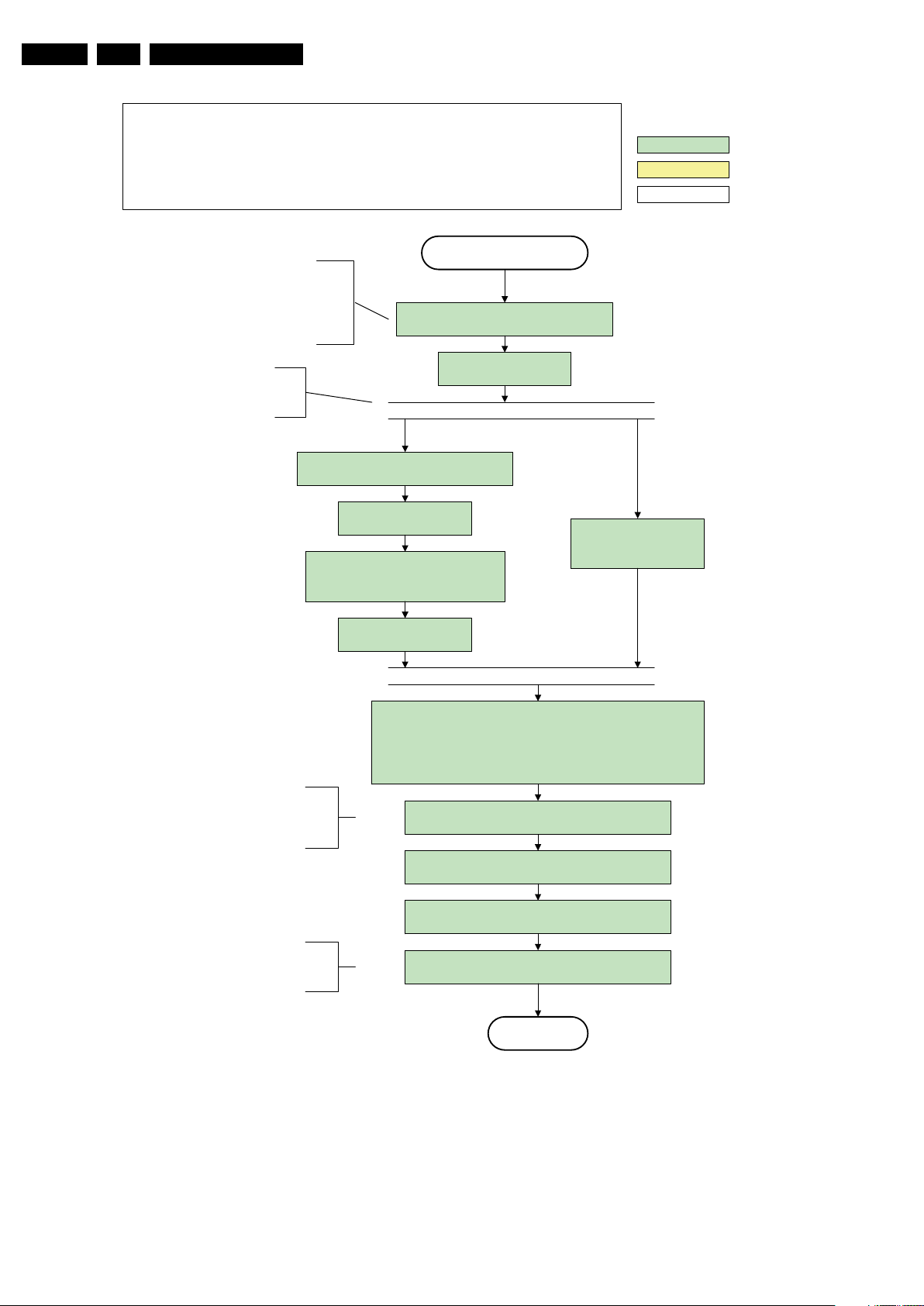

Service Modes, Error Codes, and Fault Finding

Active

Semi Standby

action holder: AVC

autonomous action

action holder: St-by

Initialize audio and video

processing IC's and functions

according needed use case.

Assert RGB video blanking

and audio mute

Wait until previous on-state is left more than 2

seconds ago. (to prevent LCD display problems)

The assumption here is t hat a fast toggle (<2s)

can only happen during ON-> SEMI -> ON. In

these states, the AVC is still active and can

provide the 2s delay. If the transition ON-> SEMI-

>STBY -> SEMI -> ON can be made in less than 2s,

the semi -> stby transition has to be delayed

until the requirement is met.

Switch Audio -Reset low and wait 5ms

Constraints taken into account:

- Display may only be started when valid LVDS output clock can be delivered by the AVC .

- Between 5 and 50 ms after power is supplied, display should receive valid lvds clock .

- minimum wait time to switch on the lamp after power up is 200ms.

unblank the video.

Wait until valid and stable audio and video , corresponding to

the requested output is delivered by the AVC.

The higher level requirement is that audio and

video should be demuted without transient

effects and that the audio should be demuted

maximum 1s before or at the same time as the

unblanking of the video.

Release audio mute and wait 100ms before any other audio

handling is done (e.g. volume change)

CPipe already generates a valid output

clock in t he semi -standby st ate : display

startup can start immediately when leaving

the semi-standby state.

wait 250ms (min. = 200ms)

Switch on LCD backlight

(Lamp-ON)

Switch on the display by sending the

TurnOnDisplay(1) (I²C) command to the PNX5100

The timings to be used in

combination with the PanelON

comman d for th is specific d isplay

Switch on the Ambilight functionality according the last status

settings.

The higher level requirement is that the

ambilig ht fu nctionality m ay not be sw itched on

before the backlight is turned on in case the

set contains a CE IPB inverter supply.

I_17660_126.eps

140308

EN 21Q549.2E LA 5.

Figure 5-6 “Semi Stand-by” to “Active” flowchart

2009-May-08

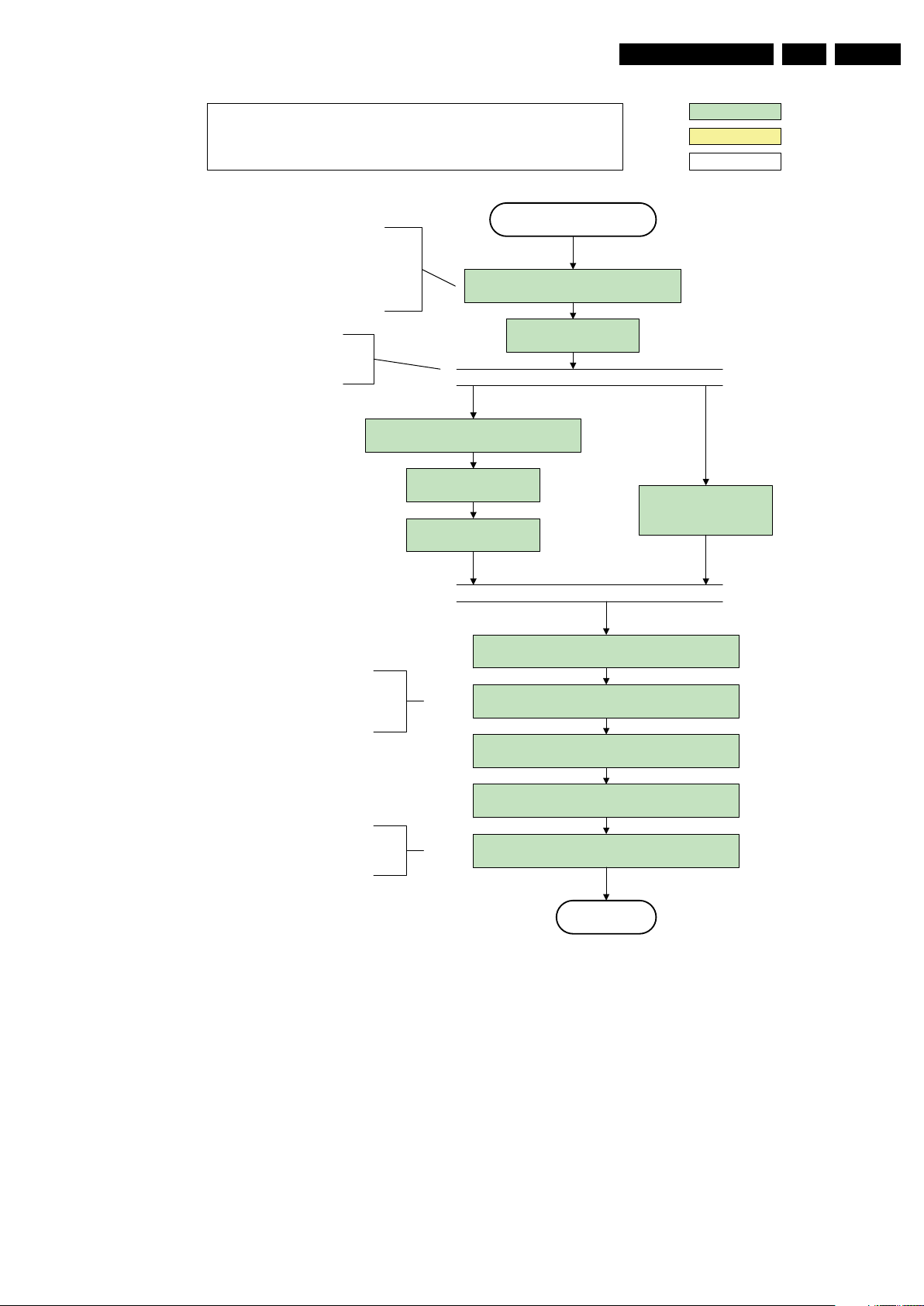

Page 22

EN 22 Q549.2E LA5.

Active

Semi Standby

action holder: AVC

autonomous action

action holder: St-by

Initialize audio and video

processing IC's and functions

according needed use case.

Assert RGB video blanking

and audio mute

Wait until previous on-state is left more than 2

seconds ago. (to prevent LCD display problems)

The assumption here is t hat a fast toggle (<2s)

can only happen during ON->SEMI ->ON. In

these states, the AVC is still active and can

provide t he 2s delay. If the tran sition ON -> SEMI-

->STBY-> SEMI -> ON can be made in less than 2s,

the semi - > stby transition has to be delayed

until the requirement is met.

Switch Audio-Reset low and wait 5ms

Constraints taken into account:

- Display may only be started when valid LVDS output clock can be delivered by the AVC .

- Between 5 and 50 ms after power is supplied, display should receive valid lvds clock .

- minimum wait time to switch on the lamp after power up is 200ms.

- To have a reliable operation of the backlight, the backlight should be driven with a PWM duty cycle of 100%

during the first second. Only after this first one or two seconds, the PWM may be set to the required output level

(Note that the PWM output should be present before the backlight is switched on). To minimize the artefacts, the

picture should only be unblanked after these first seconds.

Restore dimming backlight feature, PWM and BOOST output

and unblank the video.

Wait until valid and stable audio and video , corresponding to the requested

output is delivered by the AVC

AND

[the backlight PWM has been on for 1s (internal inverter LPL displays

OR the backlight PWM has been on for 2s (external inverter LPL displays)] .

The higher level requirement is that audio and

video should be demuted without transient

effects and that the audio should be demuted

maximum 1s before or at the same time as the

unblanking of the video.

Release audio mute and wait 100ms before any other audio

handling is done (e.g. volume change)

CPipe already generates a valid output

clock in t he sem i -standby st ate: display

startup can start immediately when leaving

the semi-standby state.

wait 250ms (min. = 200ms)

Switch on L CD backlig ht

(Lamp-ON)

Switch off the dimming backlight feature, set

the BOOST control to nominal and make sure

PWM output is set to 100%

Switch on the display by sending the

TurnOnDisplay(1) (I²C) command to the PNX5100

Switch on the Ambilight functionality according the last status

settings .

The higher level requirement is that the

ambilig ht functio nality may not be sw itched on

before the backlight is turned on in case the

set contains a CE IPB inverter supply.

I_17660_127.eps

140308

Service Modes, Error Codes, and Fault Finding

2009-May-08

Figure 5-7 “Semi Stand-by” to “Active” flowchart LCD with preheat

Page 23

Service Modes, Error Codes, and Fault Finding

EN 23Q549.2E LA 5.

Constraints taken into account:

- Display may only be started when valid LVDS output clock can be delivered by the AVC.

- Between 5 and 50 ms after power is supplied, display should receive valid lvds clock .

- minimum wait time to switch on the lamp after power up is 200ms.

Semi Standby

The assumption here is that a fast toggle (<2s)

can only happen during ON-> SEMI -> ON. In

these states, the AVC is still active and can

provide the 2s delay. If the t ransition ON -> SEMI-

>STBY->SEMI->ON can be made in less t han 2s,

the semi -> stby transition has to be delayed

CPipe already generates a valid output

clock in t he sem i -standby st ate : display

startup can start immediately when leaving

until the requirement is met.

the semi-standby state.

Switch on the display by sending the OUTPUT-

ENABLE (I²C) command to the LED DIM panel

wait 250ms (min. = 200ms)

Switch on L CD backlig ht

Wait until previous on-state is left more than 2

seconds ago. (to prevent LCD display problems)

Assert RGB video blanking

TBC in def. spec

(Lamp-ON)

and audio mute

action holder: AVC

action holder: St-by

autonomous action

Initialize audio and video

processing IC's and functions

according needed use case.

The higher level requirement is that audio and

video should be demuted without transient

effects and that the audio should be demuted

maximum 1s before or at the same time as the

unblanking of the video.

The higher level requirement is that the

ambilig ht functio nality may not be sw itched on

before the backlight is turned on in case the

set contains a CE IPB inverter supply.

Figure 5-8 “Semi Stand-by” to “Active” flowchart (LED backlight)

Wait until valid and stable audio and video , corresponding to

the requested output is delivered by the AVC.

Switch Audio -Reset low and wait 5ms

Release audio mute and wait 100ms before any other audio

handling is done (e.g. volume change)

unblank the video.

Switch on the Ambilight functionality according the last status

settings .

Active

I_17660_128.eps

140308

2009-May-08

Page 24

EN 24 Q549.2E LA5.

Semi Standby

Active

action holder: AVC

autonomous action

action holder: St-by

Wait 25 0ms ( min. = 2 00ms)

Mute all sound outputs via softmute

Mute all video outputs

switch off LCD backlight

Force ext audio outputs to ground

(I/O: audio reset)

And wait 5ms

Switch off the display by sending the

TurnOnDisplay(0) (I²C) command to the PNX5100

switch o ff Am bilight

Set main amplifier mute (I/O: audio-mute)

Wait 100ms

Wait until Ambilight has faded out

(fixed wait time of x s)

The higher level requirement is that the

backlight may not be switched off before the

ambilight functionality is turned off in case the

set contains a CE IPB inverter supply.

I_17660_129.eps

140308

Service Modes, Error Codes, and Fault Finding

Figure 5-9 “Active” to “Semi Stand-by” flowchart (LCD non DFI)

2009-May-08

Page 25

Service Modes, Error Codes, and Fault Finding

transfer Wake up reasons to the Stand by µP.

Stand by

Semi Stand by

action holder: MIPS

autonomous action

action holder: St-by

Disable all supply related protections and switch off

the DC/DC converters (ENABLE-3V3)

Switch OFF all supplies by swit ching H IGH t he

Standby I/O line

Switch AVC system in re set st ate

Switch reset-PNX5100 LOW

Switch reset-ST7100 LOW

Switch Reset-Ethernet LOW

Important remark:

release reset audio 10 sec after

entering sta ndb y to sa ve power

Wait 5ms

Wait 10ms

Switch the NVM reset line HIGH

Switch het WP-Nandflash LOW

Delay transition until ramping down of ambient light is

finished. *)

If ambientlight functionality was used in semi -standby

(lampadaire mode), switch off ambient light

*) If this is not performed and the set is

switched to standby when the switch off of

the ambilights is still ongoing , the lights will

switch off abruptly when the supply is cut.

Switch Memories to self-refresh (this creates a more

stable condition when switching off the power).

I_17660_130.eps

140308

EN 25Q549.2E LA 5.

Figure 5-10 “Semi Stand-by” to “Stand-by” flowchart

2009-May-08

Page 26

EN 26 Q549.2E LA5.

Protection

action holder: MIPS

autonomous action

action holder: St-by

Redefine wake up reasons for protection

state and transfer to stand-by µP.

Log the appropriate err or and

set stand-by flag in NVM

MP

Ask stand-by µP to enter protection state

Flash the Protection-LED in order to indicate

protection state* (*): This can be the standby LED or the ON LED

depending on the availability in the set

SP

Switch off LCD lamp supply

Wait 250ms (min. = 200ms)

Switch off LVDS signal

Switch off 12V LCD supply within a time frame of

min. 0.5ms to max. 50ms after LVDS switch off.

If needed to speed up this transition,

this block could be omitted . This is

depending on the outcome of the

safety investigations .

Disable all supply related protections and switch off

the +1V8 and the +3V3 DC/DC converter.

Switch OFF all supplies by switching HIGH the

Standby I/O line.

Switch AVC in r eset sta te

Wait 5ms

Wait 10ms

Switch the N VM r eset lin e HI GH.

I_17660_131.eps

140308

Service Modes, Error Codes, and Fault Finding

2009-May-08

Figure 5-11 “To Protection State” flowchart

Page 27

Service Modes, Error Codes, and Fault Finding

EN 27Q549.2E LA 5.

5.4 Service Tools

5.4.1 ComPair

Introduction

ComPair (Computer Aided Repair) is a Service tool for Philips

Consumer Electronics products. and offers the following:

1. ComPair helps to quickly get an understanding on how to

repair the chassis in a short and effective way.

2. ComPair allows very detailed diagnostics and is therefore

capable of accurately indicating problem areas. No

knowledge on I

because ComPair takes care of this.

3. ComPair speeds up the repair time since it can

automatically communicate with the chassis (when the uP

is working) and all repair information is directly available.

4. ComPair features TV software up possibilities.

Specifications

ComPair consists of a Windows based fault finding program

and an interface box between PC and the (defective) product.

The ComPair II interface box is connected to the PC via an

USB cable. For the TV chassis, the ComPair interface box and

the TV communicate via a bi-directional cable via the service

connector(s).

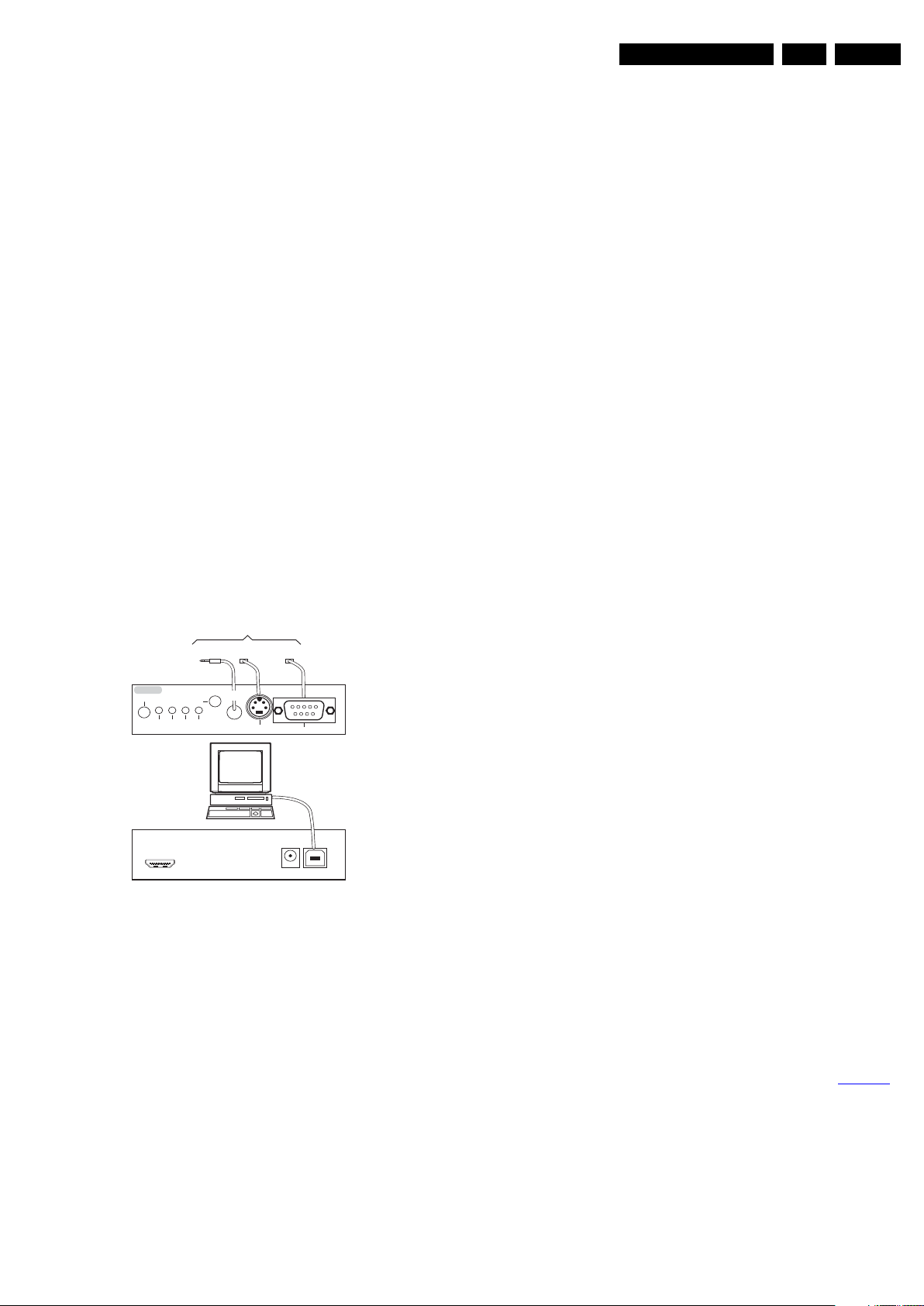

The ComPair fault finding program is able to determine the