Page 1

Colour Television Chassis

I_18020_000.eps

110908

ESSENCEESSENCE

Q529.1E

LC

Contents Page Contents Page

1. Technical Specifications, Connections, and Chassis

Overview 2

2. Safety Instructions, Warnings, and Notes 7

3. Directions for Use 8

4. Mechanical Instructions 9

5. Service Modes, Error Codes, and Fault Finding 24

6. Block Diagrams, Test Point Overview, and

Waveforms

Wiring Diagram Essence 57

Block Diagram Video 58

Block Diagram Audio 59

Block Diagram Control & Clock Signals 60

Test Point Overview SSB 61-66

I2C IC Overview 67

Supply Lines Overview 68

7. Circuit Diagrams and PWB Layouts Drawing PWB

SSB (B01-B09) 69-116 120-129

SSB: SRP List Explanation 117

SSB: SRP List Part 1 118

SSB: SRP List Part 2 119

I/O Panel (G) 130 131

IR & LED Panel (ME TOP) (J) 132 133

LVDS2DP Panel: Connector & Supply (LD1) 134 140-141

LVDS2DP Panel: FPGA: I/O Banks (LD2) 135 140-141

LVDS2DP Panel: Genesis (LD3) 136 140-141

LVDS2DP Panel: Fan Control (LD4) 137 140-141

LVDS2DP Panel: FPGA: Control (LD5) 138 140-141

LVDS2DP: SRP List 139

Monitor Panel: DC/DC (M01A) 142 151-152

Monitor Panel: DC/DC (M01B) 143 151-152

Monitor Panel: Audio (M02A) 144 151-152

Monitor Panel: Audio (M02B) 145 151-152

Monitor Panel: DP-Rx (M03A) 146 151-152

Monitor Panel: DP-Receiver & Power (M03B) 147 151-152

©

Copyright 2008 Koninklijke Philips Electronics N.V.

All rights reserved. No part of this publication may be reproduced, stored in a

retrieval system or transmitted, in any form or by any means, electronic,

mechanical, photocopying, or otherwise without the prior permission of Philips.

Monitor Panel: DP-Rx (M03C)148 151-152

Monitor Panel: DP-Rx (M03D)149 151-152

Monitor: SRP List 150

8. Alignments 153

9. Circuit Descriptions, Abbreviation List, and IC Data

Sheets 170

10. Spare Parts List & CTN Overview 185

11. Revision List 185

Published by EL 0872 BU TV Consumer Care Printed in the Netherlands Subject to modification EN 3122 785 18022

Page 2

EN 2 Q529.1E LC1.

Technical Specifications, Connections, and Chassis Overview

1. Technical Specifications, Connections, and Chassis Overview

Index of this chapter:

1.1 Technical Specifications

1.2 Connections

1.3 Chassis Overview

Notes:

• Figures can deviate due to the different set executions.

• Specifications are indicative (subject to change).

1.1 Technical Specifications

1.1.1 Vision

Display type : LCD

Screen size : 42" (107 cm), 16:9

Resolution (H × V pixels) : 1920 × 1080

Min. light output (cd/m

Min. contrast ratio : 66000:1

Max. response time (ms) : 2

Viewing angle (H × V degrees) : 176 × 176

Tuning system : PLL

TV Colour systems : PAL B/G, D/K, I

Video playback : NTSC, PAL, SECAM

Tuner bands : UHF, VHF, S, Hyper

Supported video formats

- 60 Hz : 480i

- 60 Hz : 480p

- 50 Hz : 576i

- 50 Hz : 576p

- 50, 60 Hz : 720p

- 50, 60 Hz : 1080i

- 24, 25, 30, 50, 60 Hz : 1080p

Supported computer formats:

- 60 Hz : 640 × 480

- 60 Hz : 800 × 600

- 60 Hz : 1024 × 768

- 60 Hz : 1280 × 768

- 60 Hz : 1360 × 768

- 60 Hz : 1920 × 1080i

- 60 Hz : 1920 × 1080p

Presets/channels : automatic channel

Tuner bands : VHF

2

) : 500

: SECAM B/G, D/K, L/L’

: DVB-T

: DVB-C (optional)

: MPEG4 (optional)

: UHF

: S-band

: Hyper-band

management

1.1.4 Miscellaneous

Power supply:

- Mains voltage (V

- Mains frequency (Hz) : 50 / 60

Ambient conditions:

- Temperature range (°C) : +5 to +35

Power consumption (values are indicative)

- Normal operation (W) : ≈248

- Standby (W) : < 0.40

Hub dimensions (W × H × D in mm) : 320 × 84 × 320

Hub weight (kg) : 4.7

Screen dimensions (W × H × D in

mm) : 982 × 662.5 × 49.8

Screen weight (kg) : 16.5

) : 220 - 240 ±10%

AC

: 90% R.H.

1.1.2 Sound

Sound systems : Virtual Dolby Digital

Maximum power (W

1.1.3 Multimedia

Supported formats : Slideshow.alb files

USB input : USB1.1 (12 Mbps)

Network : DLNA PC Network

):2 × 15

RMS

: BBE

: MPEG1

: MPEG2

:MP3

: JPEG

: USB2.0 (480 Mbps)

link

Page 3

Technical Specifications, Connections, and Chassis Overview

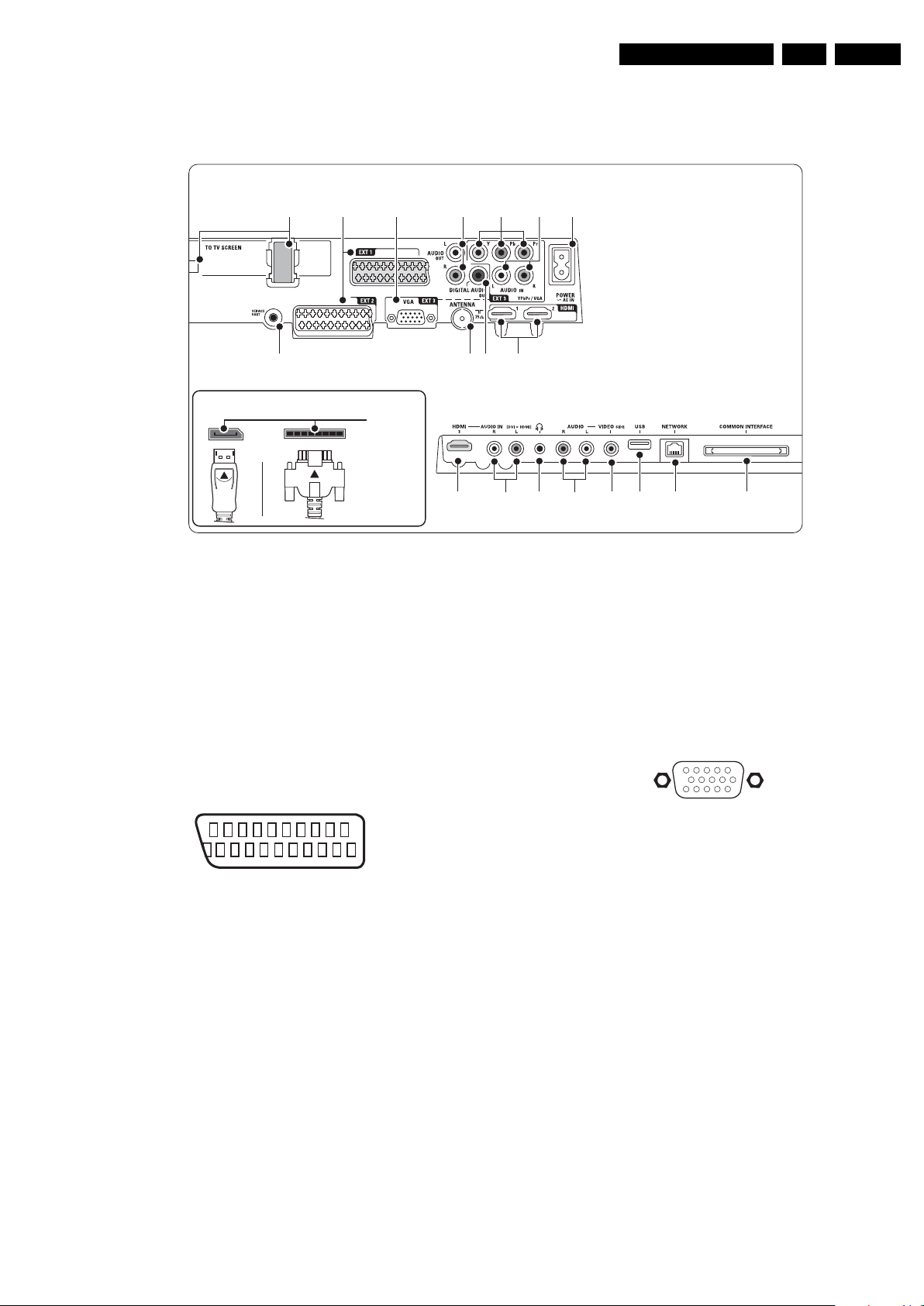

3a1 54 62

11 13 15 16 18

910 8 7

17

3b

12 14

Back connector TV

Back connector HUB

Side connector HUB

I_18020_086.eps

190908

1

1

6

10

11

5

15

E_06532_002.eps

171108

1.2 Connections

EN 3Q529.1E LC 1.

Note: The following connector colour abbreviations are used

(acc. to DIN/IEC 757): Bk= Black, Bu= Blue, Gn= Green,

Gy= Grey, Rd= Red, Wh= White, Ye= Yellow.

1.2.1 Connections

1 - Single cable connectors

Dedicated for Essence

2 - EXT1, EXT2: Video YPbPr - In, CVBS - In/Out, Audio - In/ Out

1 -Audio R 0.5 V

2 -Audio R 0.5 V

3 -Audio L 0.5 V

4 -Ground Audio Gnd H

5 -Ground Blue Gnd H

6 -Audio L 0.5 V

7 -Video Pb 0.7 V

8 -Function Select 0 - 2 V: INT

9 -Ground Gnd H

10 - n.c.

11 - Video Y 1 V

12 - n.c.

13 - Ground Gnd H

14 - Ground Gnd H

15 - Video Pr 0.7 V

20

21

Figure 1-2 SCART connector

E_06532_001.eps

/ 1 kohm k

RMS

/ 10 kohm j

RMS

/ 1 kohm k

RMS

/ 10 kohm j

RMS

/ 75 ohm j

PP

4.5 - 7 V: EXT 16:9

9.5 - 12 V: EXT 4:3 j

/ 75 ohm j

PP

/ 75 ohm j

PP

2

1

050404

Figure 1-1 Connection overview

16 - Status/FBL 0 - 0.4 V: INT

17 - Ground Video Gnd H

18 - Ground FBL Gnd H

19 - Video CVBS 1 V

20 - Video CVBS/Y 1 V

21 - Shield Gnd H

3a - EXT 3 VGA: Video RGB - In

1 -Video Red 0.7 V

2 -Video Green 0.7 V

3 -Video Blue 0.7 V

4-n.c.

5 -Ground Gnd H

6 -Ground Red Gnd H

7 -Ground Green Gnd H

8 -Ground Blue Gnd H

9-+5V

10 - Ground Sync Gnd H

11 - n.c.

12 - DDC_SDA DDC data j

13 - H-sync 0 - 5 V j

14 - V-sync 0 - 5 V j

15 - DDC_SCL DDC clock j

3b - Cinch: Audio - In

Rd - Audio R 0.5 V

Wh - Audio L 0.5 V

4 - Cinch: Audio - Out

Rd - Audio - R 0.5 V

Wh - Audio - L 0.5 V

1 - 3 V: EXT / 75 ohm j

/ 75 ohm k

PP

/ 75 ohm j

PP

Figure 1-3 VGA Connector

PP

PP

PP

DC

+5 V j

RMS

RMS

RMS

RMS

/ 75 Ω j

/ 75 Ω j

/ 75 Ω j

/ 10 kΩ jq

/ 10 kΩ jq

/ 10 kΩ kq

/ 10 kΩ kq

Page 4

EN 4 Q529.1E LC1.

19

1

18 2

E_06532_017.eps

250505

1 2 3 4

E_06532_022.eps

300904

112345678

E_06532_025.eps

210905

Technical Specifications, Connections, and Chassis Overview

5 - Cinch: Video YPbPr - In

Gn - Video Y 1 V

Bu - Video Pb 0.7 V

Rd - Video Pr 0.7 V

/ 75 Ω jq

PP

/ 75 Ω jq

PP

/ 75 Ω jq

PP

7, 11 - HDMI 1, 2, 3 Digital Video, Digital Audio - In

Figure 1-4 HDMI (type A) connector

1 -D2+ Data channel j

2-Shield Gnd H

3 -D2- Data channel j

4 -D1+ Data channel j

5-Shield Gnd H

6 -D1- Data channel j

7 -D0+ Data channel j

8-Shield Gnd H

9 -D0- Data channel j

10 - CLK+ Data channel j

11 - Shield Gnd H

12 - CLK- Data channel j

13 - Easylink Control channel jk

14 - n.c.

15 - DDC_SCL DDC clock j

16 - DDC_SDA DDC data jk

17 - Ground Gnd H

18 - +5V j

19 - HPD Hot Plug Detect j

20 - Ground Gnd H

17 - RJ45: Ethernet

Figure 1-6 Ethernet connector

1 -TD+ Transmit signal k

2 -TD- Transmit signal k

3 -RD+ Receive signal j

4-n.c.

5-n.c.

6 -RD- Receive signal j

7-n.c.

8-n.c.

18 - Common Interface

68p-See diagram B03H jk

8 - Cinch: S/PDIF - Out

Bk - Coaxial 0.4 - 0.6V

/ 75 Ω kq

PP

9 - Aerial - In

- - IEC-type (EU) Coax, 75 Ω D

10 - Service Connector (UART)

1 -Ground Gnd H

2 -UART_TX Transmit k

3 -UART_RX Receive j

12 - Cinch: Audio - In

Rd - Audio - R 0.5 V

Wh - Audio - L 0.5 V

/ 10 kΩ jq

RMS

/ 10 kΩ jq

RMS

13 - Headphone (Output)

Bk - Headphone 32 - 600 Ω / 10 mW ot

14 - Cinch: Audio - In

Rd - Audio - R 0.5 V

Wh - Audio - L 0.5 V

/ 10 kΩ jq

RMS

/ 10 kΩ jq

RMS

15 - Cinch: Video CVBS - In, Audio - In

Ye - Video CVBS 1 V

/ 75 Ω jq

PP

16 - USB2.0

1-+5V k

2 -Data (-) jk

3 -Data (+) jk

4 -Ground Gnd H

Figure 1-5 USB (type A)

Page 5

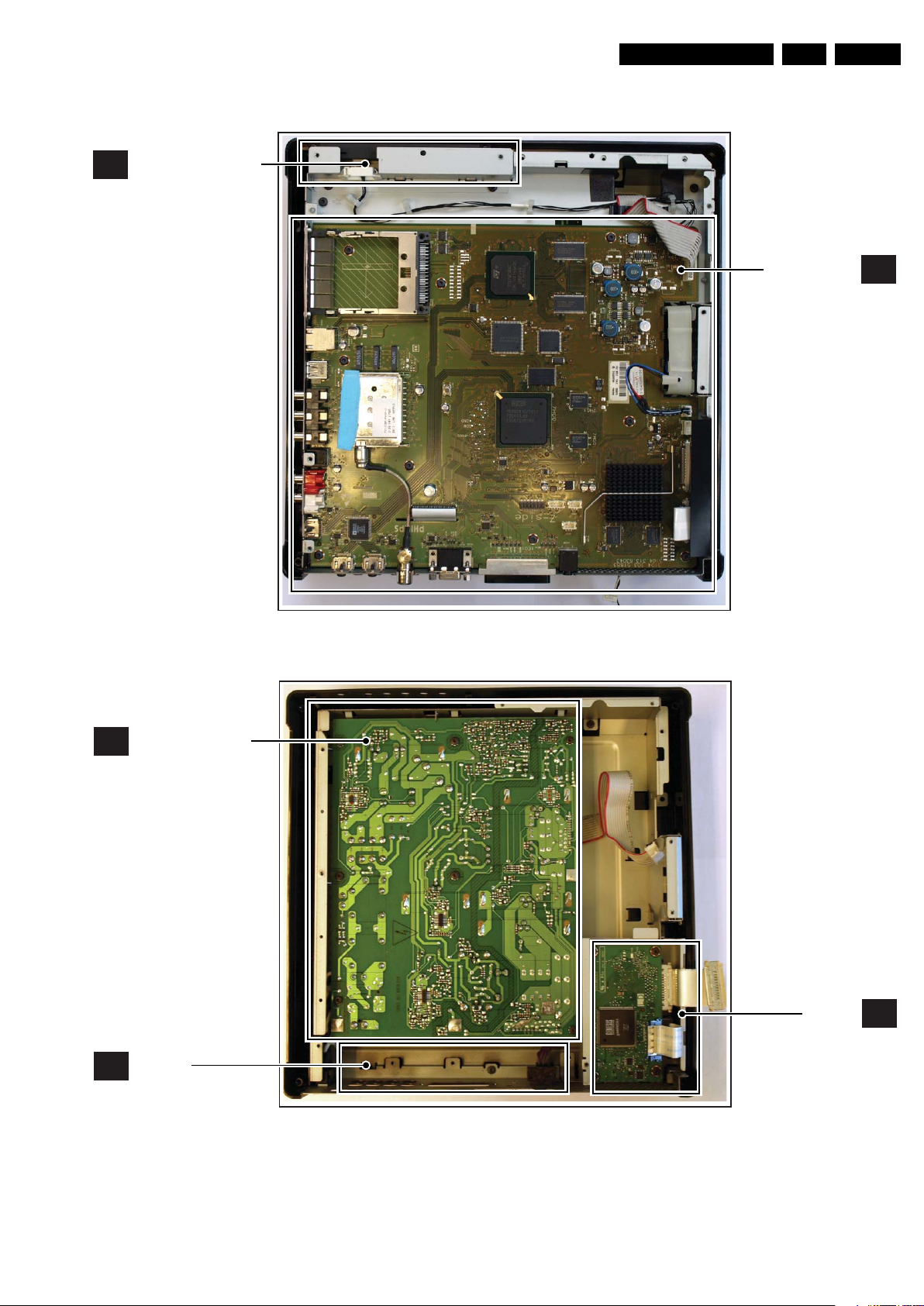

Technical Specifications, Connections, and Chassis Overview

I_18020_088.eps

110908

A

MAIN SUPPLY PANEL

G

I/O PANEL

LD

LV DS2DP

BOARD

1.3 Chassis Overview

KEYBOARD CONTROL

E

PA NE L

EN 5Q529.1E LC 1.

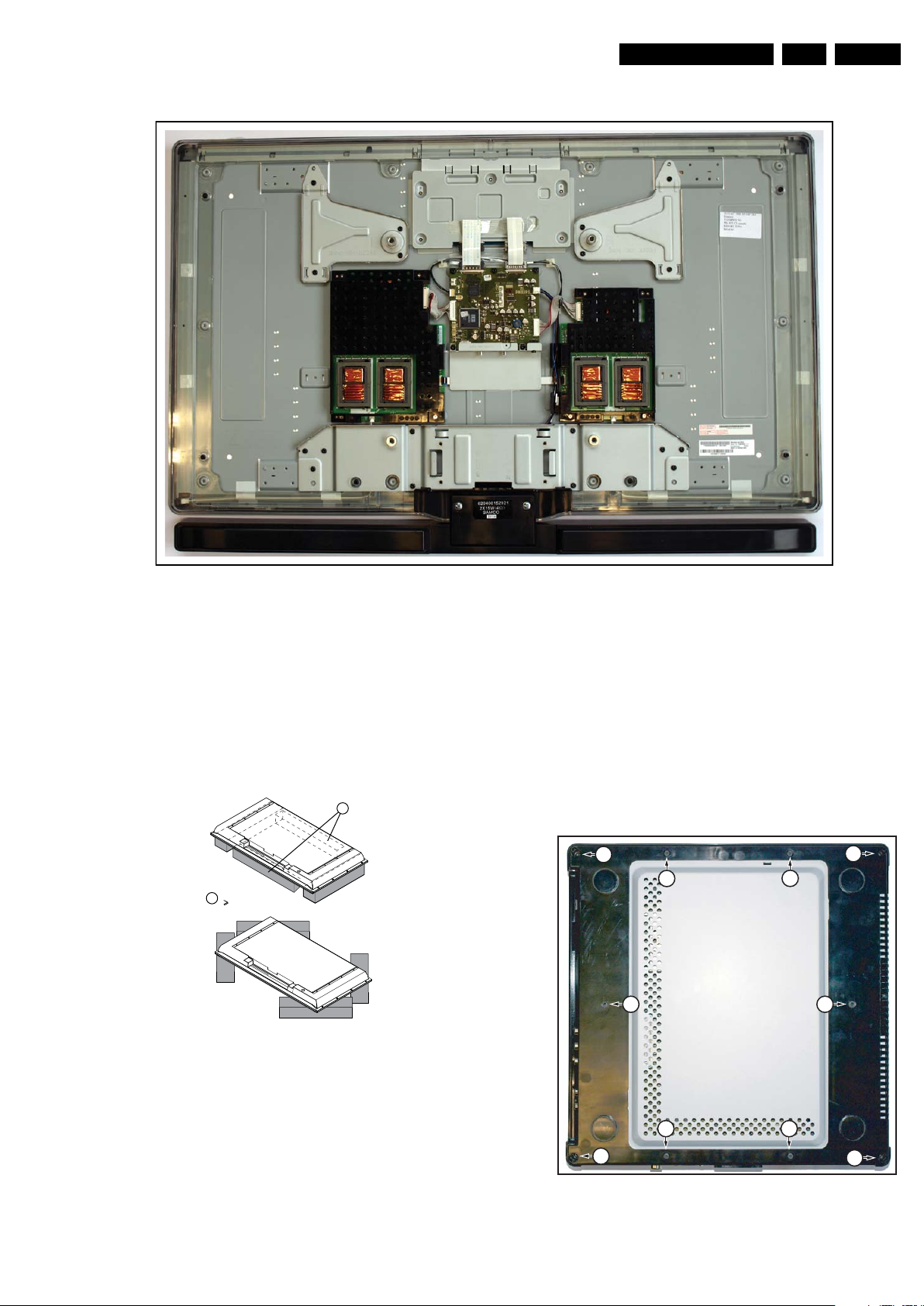

Figure 1-7 PWB/CBA locations Hub -1-

SMALL SIGNAL

BOARD

I_18020_087.eps

B

110908

Figure 1-8 PWB/CBA locations Hub -2-

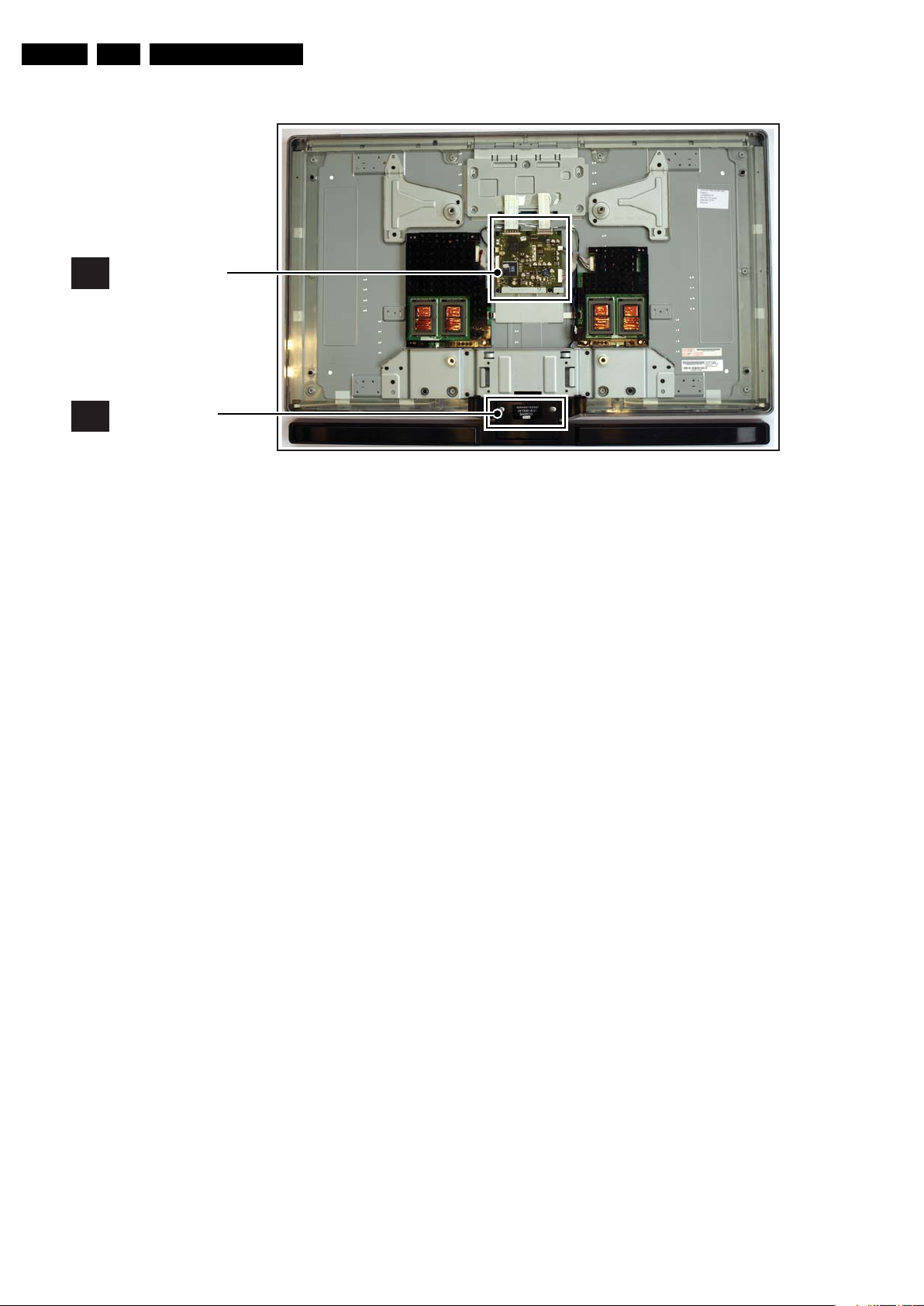

Page 6

EN 6 Q529.1E LC1.

I_18020_089.eps

110908

J

IR & LED PANEL

M

MONITOR BOARD

Technical Specifications, Connections, and Chassis Overview

Figure 1-9 PWB/CBA locations Monitor

Page 7

Safety Instructions, Warnings, and Notes

2. S afety Instructions, Warnings, and Notes

EN 7Q529.1E LC 2.

Index of this chapter:

2.1 Safety Instructions

2.2 Warnings

2.3 Notes

2.1 Safety Instructions

Safety regulations require the following during a repair:

• Connect the set to the Mains/AC Power via an isolation

transformer (> 800 VA).

• Replace safety components, indicated by the symbol h,

only by components identical to the original ones. Any

other component substitution (other than original type) may

increase risk of fire or electrical shock hazard.

Safety regulations require that after a repair, the set must be

returned in its original condition. Pay in particular attention to

the following points:

• Route the wire trees correctly and fix them with the

mounted cable clamps.

• Check the insulation of the Mains/AC Power lead for

external damage.

• Check the strain relief of the Mains/AC Power cord for

proper function.

• Check the electrical DC resistance between the Mains/AC

Power plug and the secondary side (only for sets that have

a Mains/AC Power isolated power supply):

1. Unplug the Mains/AC Power cord and connect a wire

between the two pins of the Mains/AC Power plug.

2. Set the Mains/AC Power switch to the “on” position

(keep the Mains/AC Power cord unplugged!).

3. Measure the resistance value between the pins of the

Mains/AC Power plug and the metal shielding of the

tuner or the aerial connection on the set. The reading

should be between 4.5 MΩ and 12 MΩ.

4. Switch “off” the set, and remove the wire between the

two pins of the Mains/AC Power plug.

• Check the cabinet for defects, to prevent touching of any

inner parts by the customer.

2.2 Warnings

• All ICs and many other semiconductors are susceptible to

electrostatic discharges (ESD w). Careless handling

during repair can reduce life drastically. Make sure that,

during repair, you are connected with the same potential as

the mass of the set by a wristband with resistance. Keep

components and tools also at this same potential.

• Be careful during measurements in the high voltage

section.

• Never replace modules or other components while the unit

is switched “on”.

• When you align the set, use plastic rather than metal tools.

This will prevent any short circuits and the danger of a

circuit becoming unstable.

2.3 Notes

2.3.1 General

• Measure the voltages and waveforms with regard to the

chassis (= tuner) ground (H), or hot ground (I), depending

on the tested area of circuitry. The voltages and waveforms

shown in the diagrams are indicative. Measure them in the

Service Default Mode (see chapter 5) with a colour bar

signal and stereo sound (L: 3 kHz, R: 1 kHz unless stated

otherwise) and picture carrier at 475.25 MHz for PAL, or

61.25 MHz for NTSC (channel 3).

• Where necessary, measure the waveforms and voltages

with (D) and without (E) aerial signal. Measure the

voltages in the power supply section both in normal

operation (G) and in stand-by (F). These values are

indicated by means of the appropriate symbols.

• Manufactured under license from Dolby Laboratories.

“Dolby”, “Pro Logic” and the “double-D symbol”, are

trademarks of Dolby Laboratories.

2.3.2 Schematic Notes

• All resistor values are in ohms, and the value multiplier is

often used to indicate the decimal point location (e.g. 2K2

indicates 2.2 kΩ).

• Resistor values with no multiplier may be indicated with

either an “E” or an “R” (e.g. 220E or 220R indicates 220 Ω).

• All capacitor values are given in micro-farads (μ=× 10

nano-farads (n =× 10

• Capacitor values may also use the value multiplier as the

decimal point indication (e.g. 2p2 indicates 2.2 pF).

• An “asterisk” (*) indicates component usage varies. Refer

to the diversity tables for the correct values.

• The correct component values are listed in the Spare Parts

List. Therefore, always check this list when there is any

doubt.

2.3.3 BGA (Ball Grid Array) ICs

Introduction

For more information on how to handle BGA devices, visit this

URL: www.atyourservice.ce.philips.com (needs subscription,

not available for all regions). After login, select “Magazine”,

then go to “Repair downloads”. Here you will find Information

on how to deal with BGA-ICs.

BGA Temperature Profiles

For BGA-ICs, you must use the correct temperature-profile,

which is coupled to the 12NC. For an overview of these profiles,

visit the website www.atyourservice.ce.philips.com (needs

subscription, but is not available for all regions)

You will find this and more technical information within the

“Magazine”, chapter “Repair downloads”.

For additional questions please contact your local repair help

desk.

2.3.4 Lead-free Soldering

Due to lead-free technology some rules have to be respected

by the workshop during a repair:

• Use only lead-free soldering tin Philips SAC305 with order

code 0622 149 00106. If lead-free solder paste is required,

please contact the manufacturer of your soldering

equipment. In general, use of solder paste within

workshops should be avoided because paste is not easy to

store and to handle.

• Use only adequate solder tools applicable for lead-free

soldering tin. The solder tool must be able:

– To reach a solder-tip temperature of at least 400°C.

– To stabilize the adjusted temperature at the solder-tip.

– To exchange solder-tips for different applications.

• Adjust your solder tool so that a temperature of around

360°C - 380°C is reached and stabilized at the solder joint.

Heating time of the solder-joint should not exceed ~ 4 sec.

Avoid temperatures above 400°C, otherwise wear-out of

tips will increase drastically and flux-fluid will be destroyed.

To avoid wear-out of tips, switch “off” unused equipment or

reduce heat.

• Mix of lead-free soldering tin/parts with leaded soldering

tin/parts is possible but PHILIPS recommends strongly to

-9

), or pico-farads (p =× 10

-12

-6

),

).

Page 8

EN 8 Q529.1E LC3.

E_06532_024.eps

260308

MODEL :

PROD.NO:

~

S

32PF9968/10

MADE IN BELGIUM

220-240V 50/60Hz

128W

AG 1A0617 000001

VHF+S+H+UHF

BJ3.0E LA

Directions for Use

avoid mixed regimes. If this cannot be avoided, carefully

clear the solder-joint from old tin and re-solder with new tin.

2.3.5 Alternative BOM identification

It should be noted that on the European Service website,

“Alternative BOM” is referred to as “Design variant”.

The third digit in the serial number (example:

AG2B0335000001) indicates the number of the alternative

B.O.M. (Bill Of Materials) that has been used for producing the

specific TV set. In general, it is possible that the same TV

model on the market is produced with e.g. two different types

of displays, coming from two different suppliers. This will then

result in sets which have the same CTN (Commercial Type

Number; e.g. 28PW9515/12) but which have a different B.O.M.

number.

By looking at the third digit of the serial number, one can

identify which B.O.M. is used for the TV set he is working with.

If the third digit of the serial number contains the number “1”

(example: AG1B033500001), then the TV set has been

manufactured according to B.O.M. number 1. If the third digit is

a “2” (example: AG2B0335000001), then the set has been

produced according to B.O.M. no. 2. This is important for

ordering the correct spare parts!

For the third digit, the numbers 1...9 and the characters A...Z

can be used, so in total: 9 plus 26= 35 different B.O.M.s can be

indicated by the third digit of the serial number.

Identification: The bottom line of a type plate gives a 14-digit

serial number. Digits 1 and 2 refer to the production center (e.g.

AG is Bruges), digit 3 refers to the B.O.M. code, digit 4 refers

to the Service version change code, digits 5 and 6 refer to the

production year, and digits 7 and 8 refer to production week (in

example below it is 2006 week 17). The 6 last digits contain the

serial number.

Figure 2-1 Serial number (example)

2.3.6 Board Level Repair (BLR) or Component Level Repair (CLR)

If a board is defective, consult your repair procedure to decide

if the board has to be exchanged or if it should be repaired on

component level.

If your repair procedure says the board should be exchanged

completely, do not solder on the defective board. Otherwise, it

cannot be returned to the O.E.M. supplier for back charging!

2.3.7 Practical Service Precautions

• It makes sense to avoid exposure to electrical shock.

While some sources are expected to have a possible

dangerous impact, others of quite high potential are of

limited current and are sometimes held in less regard.

• Always respect voltages. While some may not be

dangerous in themselves, they can cause unexpected

reactions that are best avoided. Before reaching into a

powered TV set, it is best to test the high voltage insulation.

It is easy to do, and is a good service precaution.

3. Directions for Use

Directions for use can be downloaded from the following

websites:

http://www.philips.com/support

http://www.p4c.philips.com

Page 9

4. Mechanical Instructions

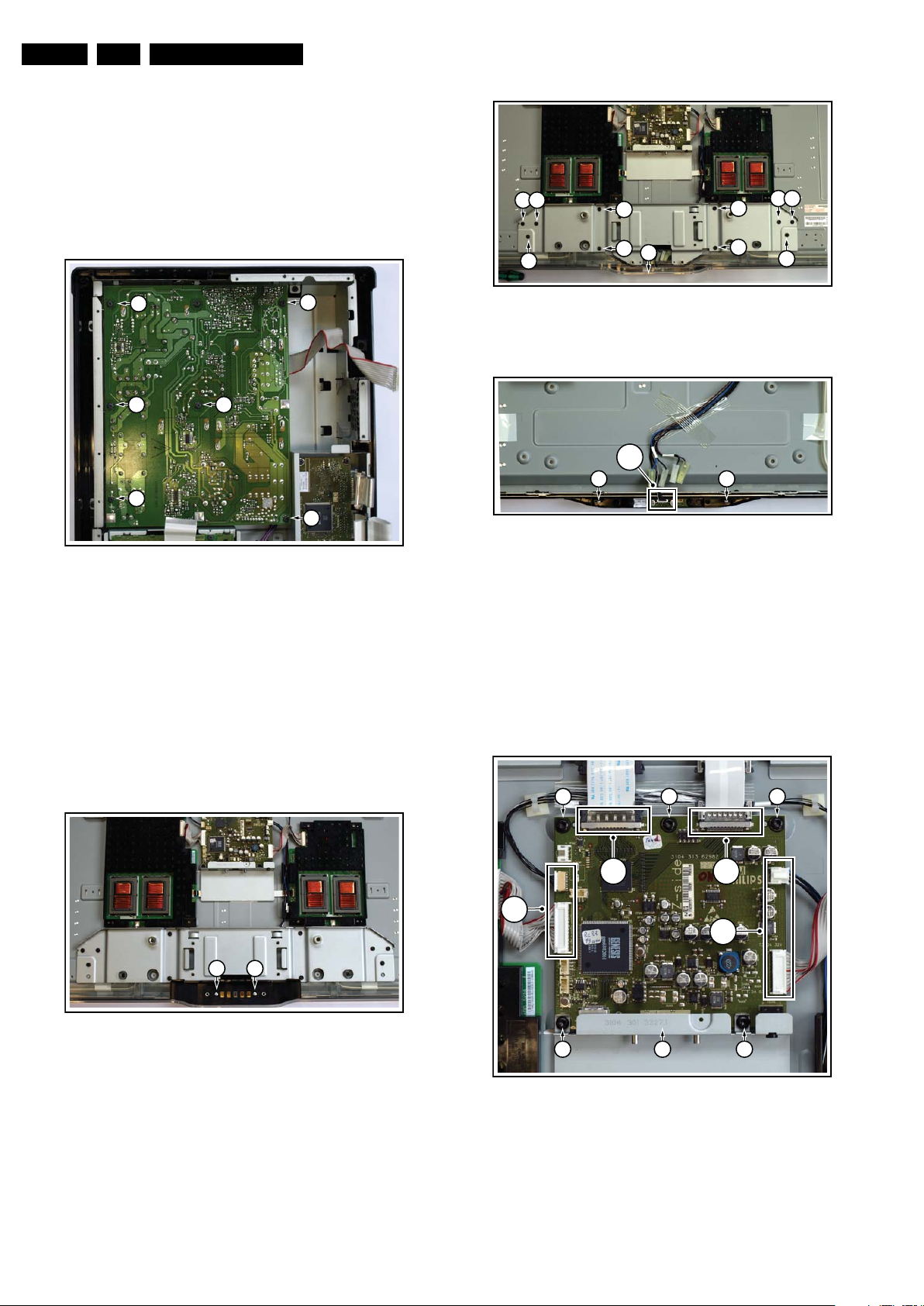

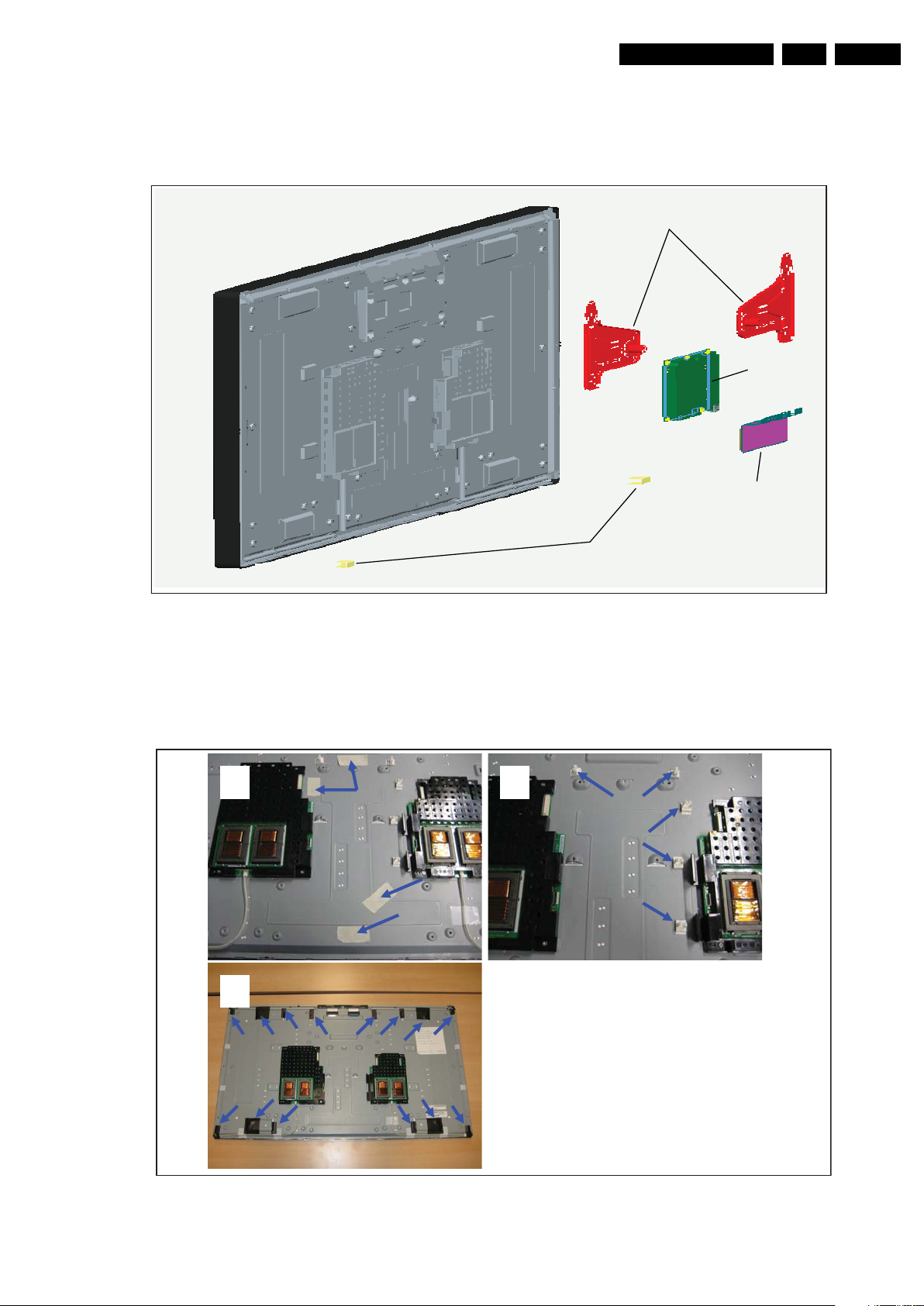

I_18020_090.eps

110908

Index of this chapter:

4.1 Cable Dressing

4.2 Service Positions

4.3 Assy/Panel Removal Hub

4.4 Assy/Panel Removal Monitor

4.5 Set Re-assembly.

Notes:

• Figures below can deviate slightly from the actual situation,

due to the different set executions.

4.1 Cable Dressing

Mechanical Instructions

EN 9Q529.1E LC 4.

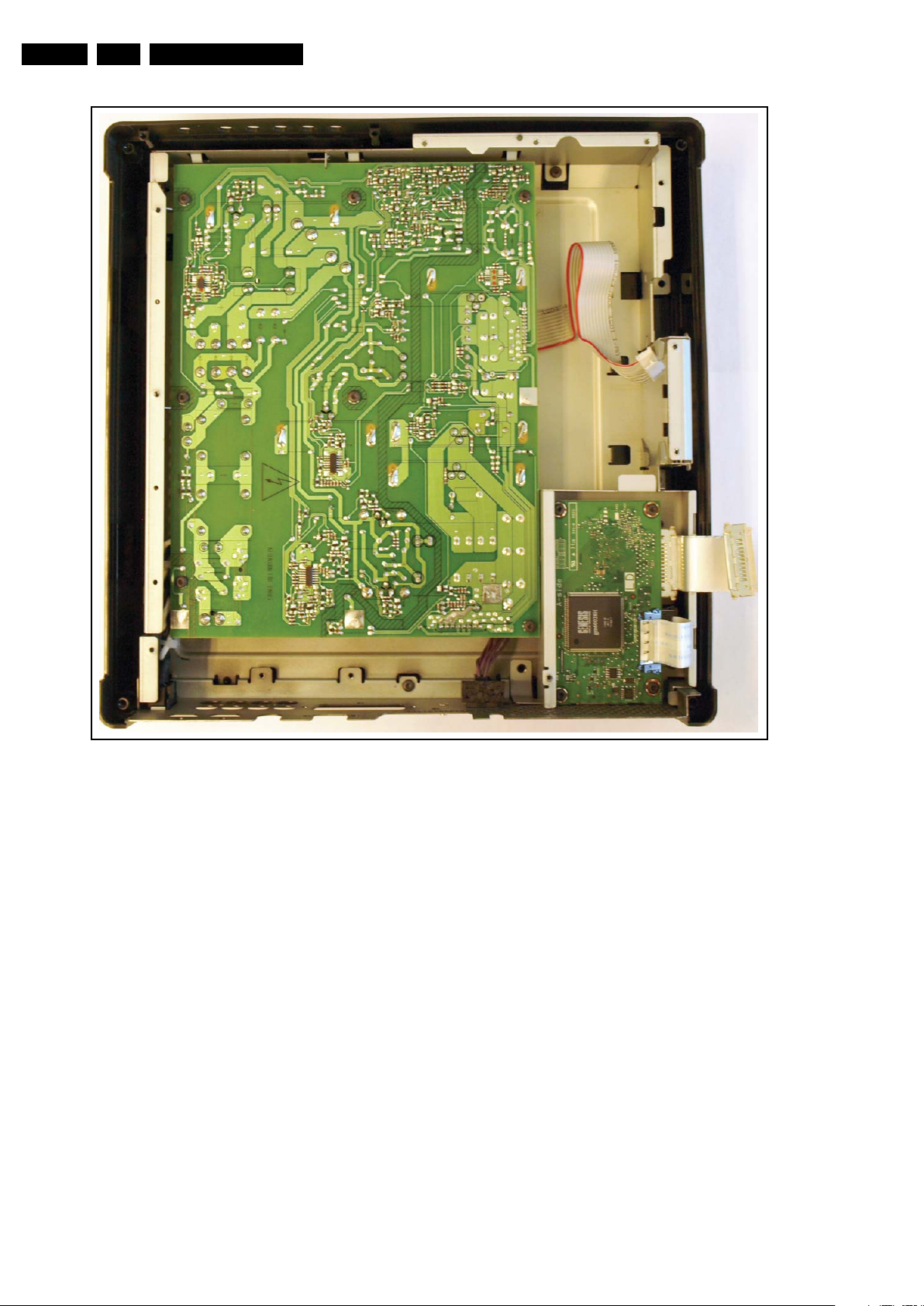

Figure 4-1 Cable dressing hub; bottom view

Page 10

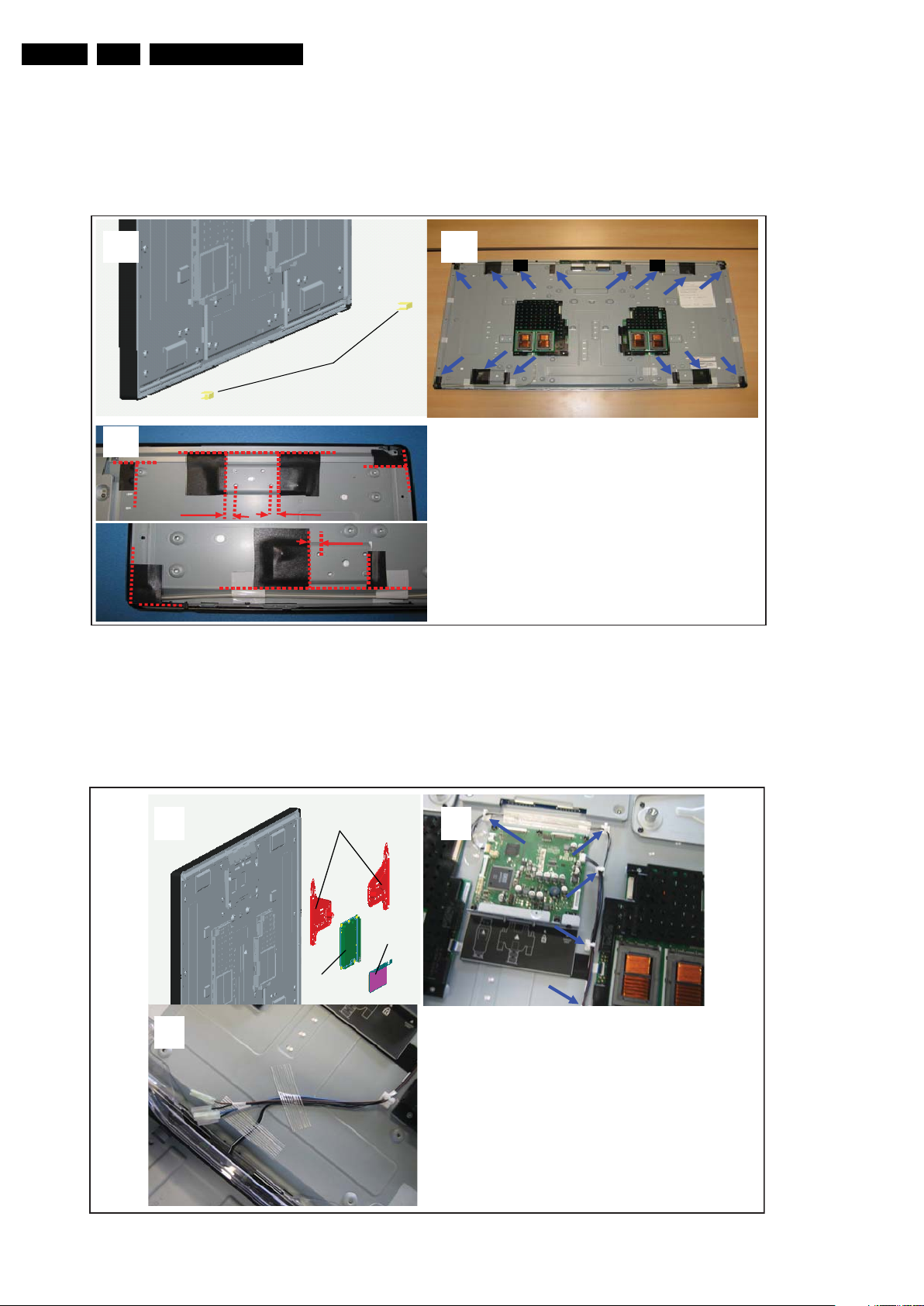

EN 10 Q529.1E LC4.

I_18020_091.eps

110908

Mechanical Instructions

Figure 4-2 Cable dressing hub; bottom view (SSB removed)

Page 11

Mechanical Instructions

I_18020_092.eps

110908

E_06532_018.eps

171106

1

Required for sets

42"

1

I_18020_143.eps

081008

11

1

1

1

1

1

1

1

1

EN 11Q529.1E LC 4.

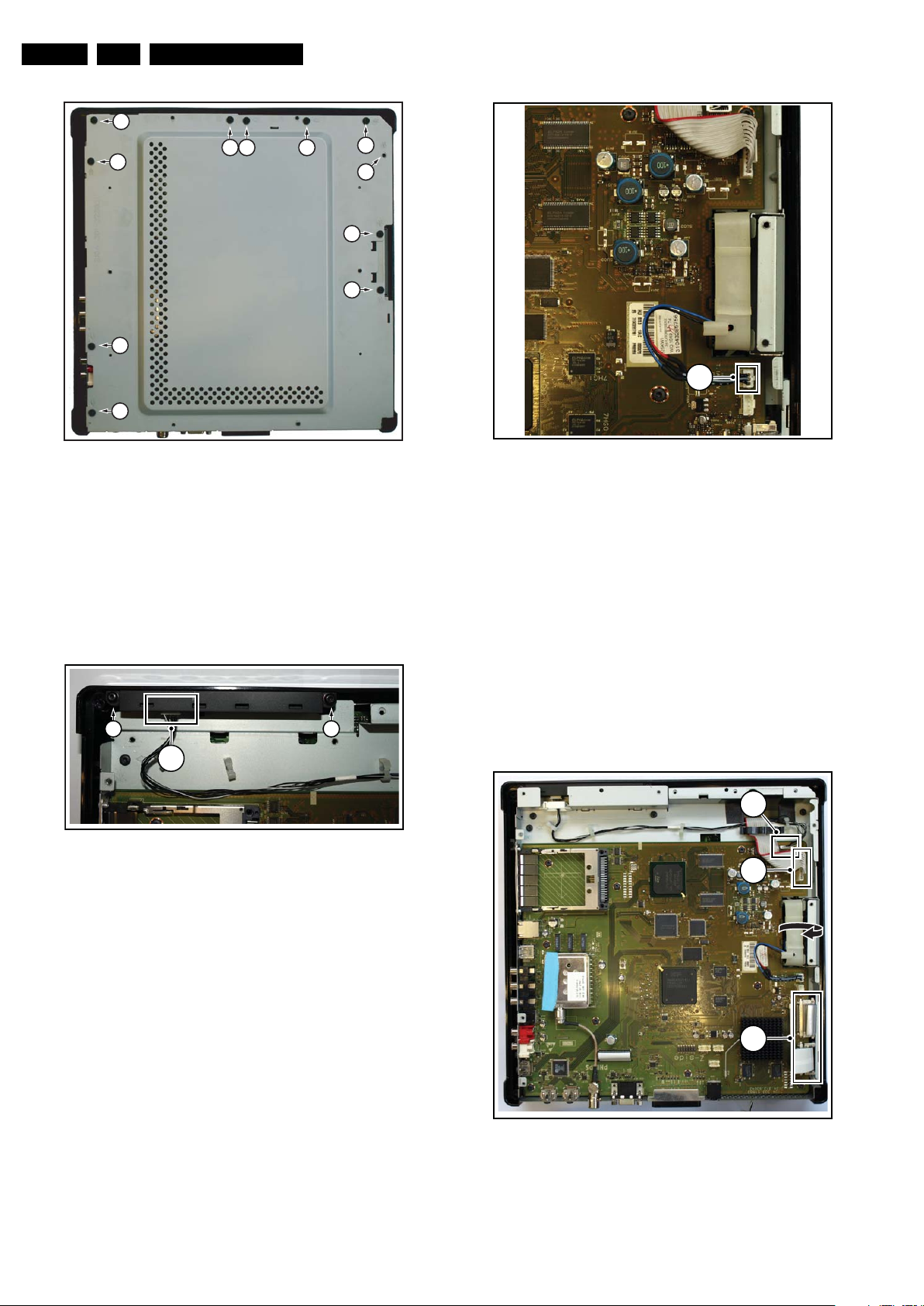

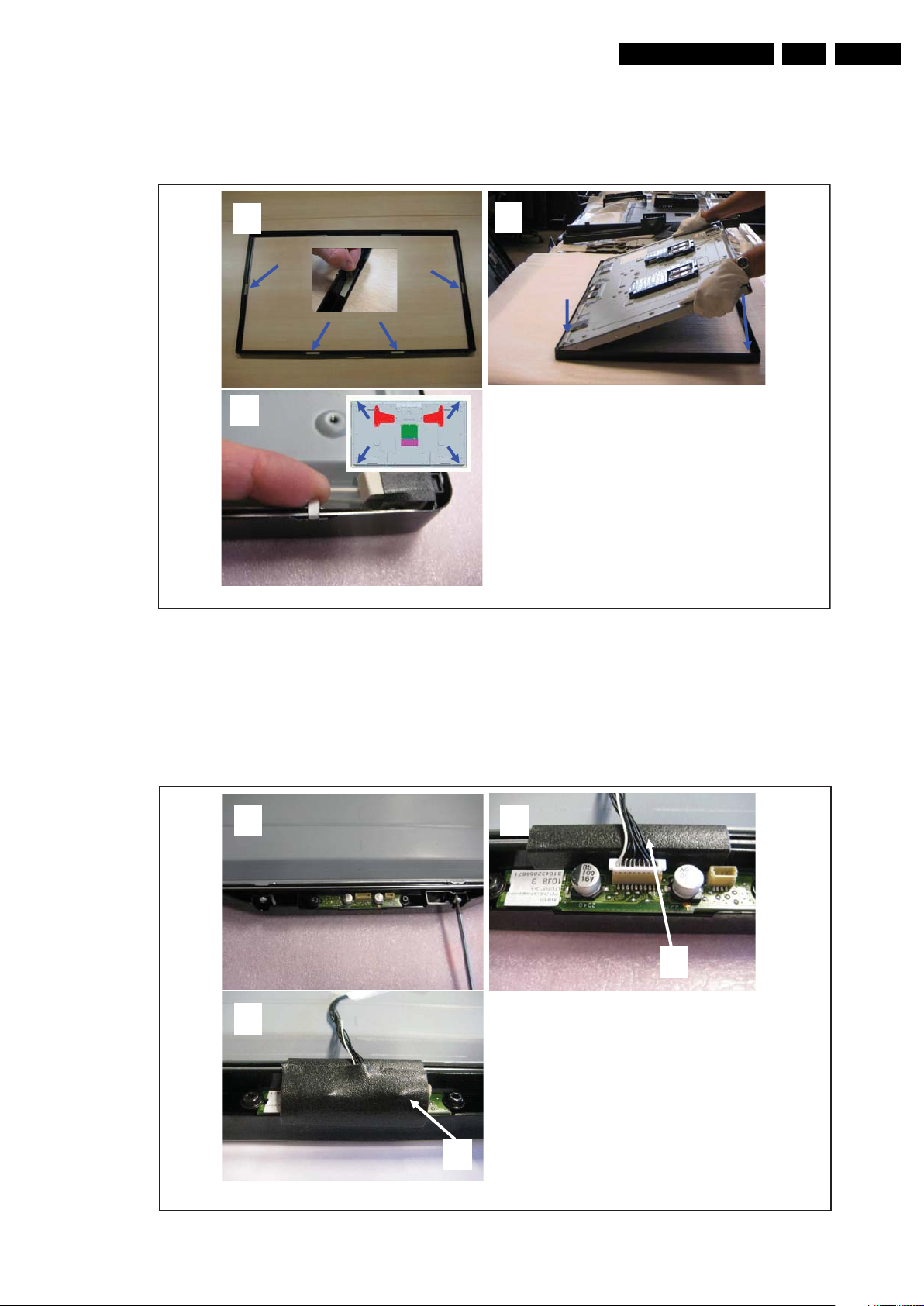

4.2 Service Positions

For easy servicing of the monitor of the set, there are a few

possibilities created:

• The buffers from the packaging.

• Foam bars (created for Service).

4.2.1 Foam Bars

Figure 4-3 Cable dressing monitor

4.3 Assy/Panel Removal Hub

4.3.1 Bottom Cover and -Shield

Warning: Disconnect the mains power cord before removing

the rear cover.

Refer to next figures for details.

1. Place the hub upside-down and remove the bottom cover

by removing the screws [1].

2. Remove the bottom shield by removing the screws [2]

indicated with an arrow.

Figure 4-4 Foam bars

The foam bars (order code 3122 785 90580 for two pieces) can

be used for all types and sizes of Flat TVs. See figure “Foam

bars” for details. Sets with a display of 42" and larger, require

four foam bars [1]. Ensure that the foam bars are always

supporting the cabinet and never only the display.

Caution: Failure to follow these guidelines can seriously

damage the display!

By laying the TV face down on the (ESD protective) foam bars,

a stable situation is created to perform measurements and

alignments. By placing a mirror under the TV, the screen can

be monitored.

Figure 4-5 Bottom Cover and -Shield -1-

Page 12

EN 12 Q529.1E LC4.

I_18020_093.eps

081008

2

2

2

2

2

2

2

2 2 2

2

I_18020_094.eps

190908

2 2

1

I_18020_095.eps

190908

1

I_18020_096.eps

110908

2

3

(2x)

1

Mechanical Instructions

Figure 4-6 Bottom Cover and -Shield -2-

4.3.2 Key Board

Refer to next figure for details.

1. Unplug the key board connector [1] from the IR & LED

board.

2. Remove the screws [2].

3. Lift the unit and take it out of the set.

When defective, replace the whole unit.

Figure 4-7 Keyboard Control Panel

4.3.3 Fan

Figure 4-8 Fan

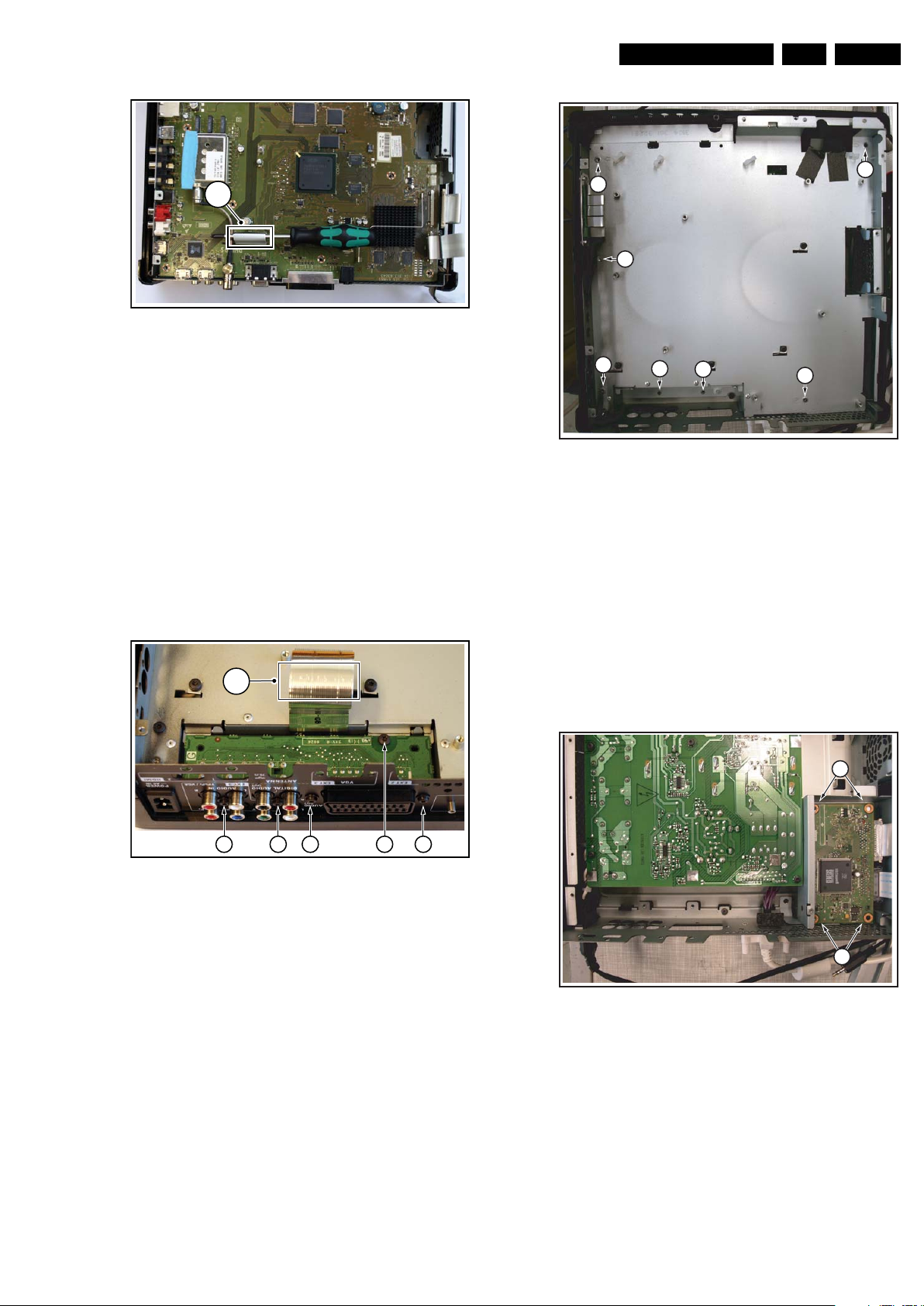

4.3.4 Small Signal Board (SSB)

Refer to next figures or details.

1. Remove fan.

2. Unplug keyboard cable [1] on SSB.

3. Unplug flat cable [2] on SSB.

4. Unplug two LVDS connectors [3] on SSB. These are very

fragile connectors!

5. Lift the flatcable gently with a screwdriver [4] that leads to

the underlaying I/O Panel.

6. Remove three screws near side I/O Panel.

7. Remove four screws near back I/O Panel (including the two

screws of the VGA connector).

8. Remove all remaining screws that secure the SSB.

9. Slide the SSB sidewards out of the hub.

Refer to next figure for details.

1. Unplug connector [1].

2. Lift the fan from the set. During replacement, ensure you

replace it at its original position.

When defective, replace the unit.

Figure 4-9 Small Signal Board -1-

Page 13

Figure 4-10 Small Signal Board -2-

I_18020_097.eps

110908

4

I_18020_119.eps

151008

1 1 2 23

4

I_18020_144.eps

151008

5

5

5

5

5

5

5

I_18020_098.eps

151008

1

1

4.3.5 Subframe underneath SSB

Refer to next figures for details.

1. Remove keyboard, fan and SSB.

2. Remove two screws [1] on Additional I/O Panel (near cinch

plugs).

3. Remove two screw [2] on Additional I/O Panel (near

SCART plug).

4. Remove screw [3].

5. Unclamp flat cable coming from Power Supply Unit [4].

6. Take the board out.

7. Remove screws on the subframe indicated with an arrow

[5].

8. Lift the subframe on the right side, then lift the subframe

forwards, then take the subframe out of the hub.

Mechanical Instructions

4.3.6 Additional I/O Panel

Refer to section “Subframe underneath SSB”.

When defective, replace the whole unit.

4.3.7 Display Port Panel Hub

EN 13Q529.1E LC 4.

Figure 4-12 Subframe -2-

Refer to next figure for details.

1. Remove screws [1].

2. Unplug the other connectors.

3. Remove all fixation screws.

4. Take the board out.

Figure 4-11 Subframe -1-

Figure 4-13 Display Port Panel Hub

Page 14

EN 14 Q529.1E LC4.

I_18020_100.eps

110908

1

11

1

1

1

I_18020_101.eps

110908

1 1

I_18020_102.eps

110908

1

2

1

1

111

1

1

1

1

I_18020_103.eps

110908

4 4

3

I_18020_104.eps

110908

2 2

5 55

1

(2x)

1

(2x)

3 34

4.3.8 Power Supply Unit

Refer to next figure for details.

1. Remove the fixation screws [1].

2. Lift the board.

3. Unplug the connector to the mains inlet.

4. Unplug the connector from the supply connector to the

screen.

5. Take the supply out.

When defective, replace the whole unit.

Mechanical Instructions

Figure 4-16 IR & LED Panel -1-

Figure 4-14 Power Supply Unit

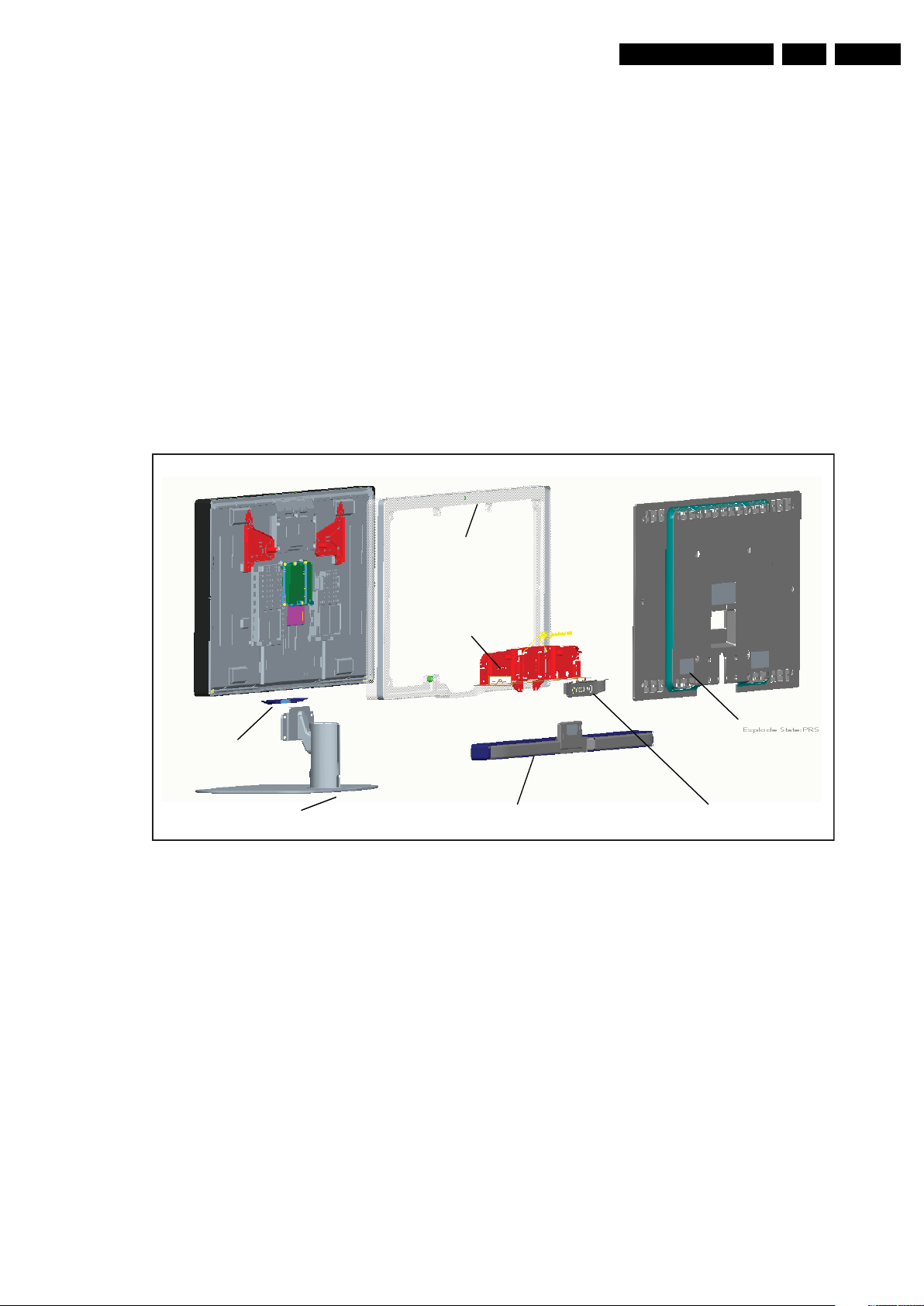

4.4 Assy/Panel Removal Monitor

4.4.1 Sound Interface

Refer to next figure for details.

1. Remove stand (four screws).

2. Lift set from stand.

3. Remove soundbar.

4. Remove sound interface by removing the screws [1].

When defective, replace the whole module.

Figure 4-17 IR & LED Panel -2-

4.4.3 Display Port Panel

Refer to next figure for details.

1. Unplug connectors [1].

2. Unplug LVDS connectors [2]. Be careful, as these are very

fragile connectors.

3. Remove screws [3] and subframe [4].

4. Remove screws [5].

When defective, replace the whole unit.

4.4.2 IR & LED Board

Refer to next figures for details.

1. Remove lower part of VESA stand [1].

2. Remove flare [2] (six screws).

3. Unplug connector [3].

4. Remove screws [4].

When defective, replace the whole unit.

Figure 4-15 Sound Interface

Figure 4-18 Display Port Panel Monitor

Page 15

Mechanical Instructions

Stand

Back Cover

Soundbar

Stand

Bracket

Flare

Sound Interface

Leading Edge

I_18020_105.eps

151008

EN 15Q529.1E LC 4.

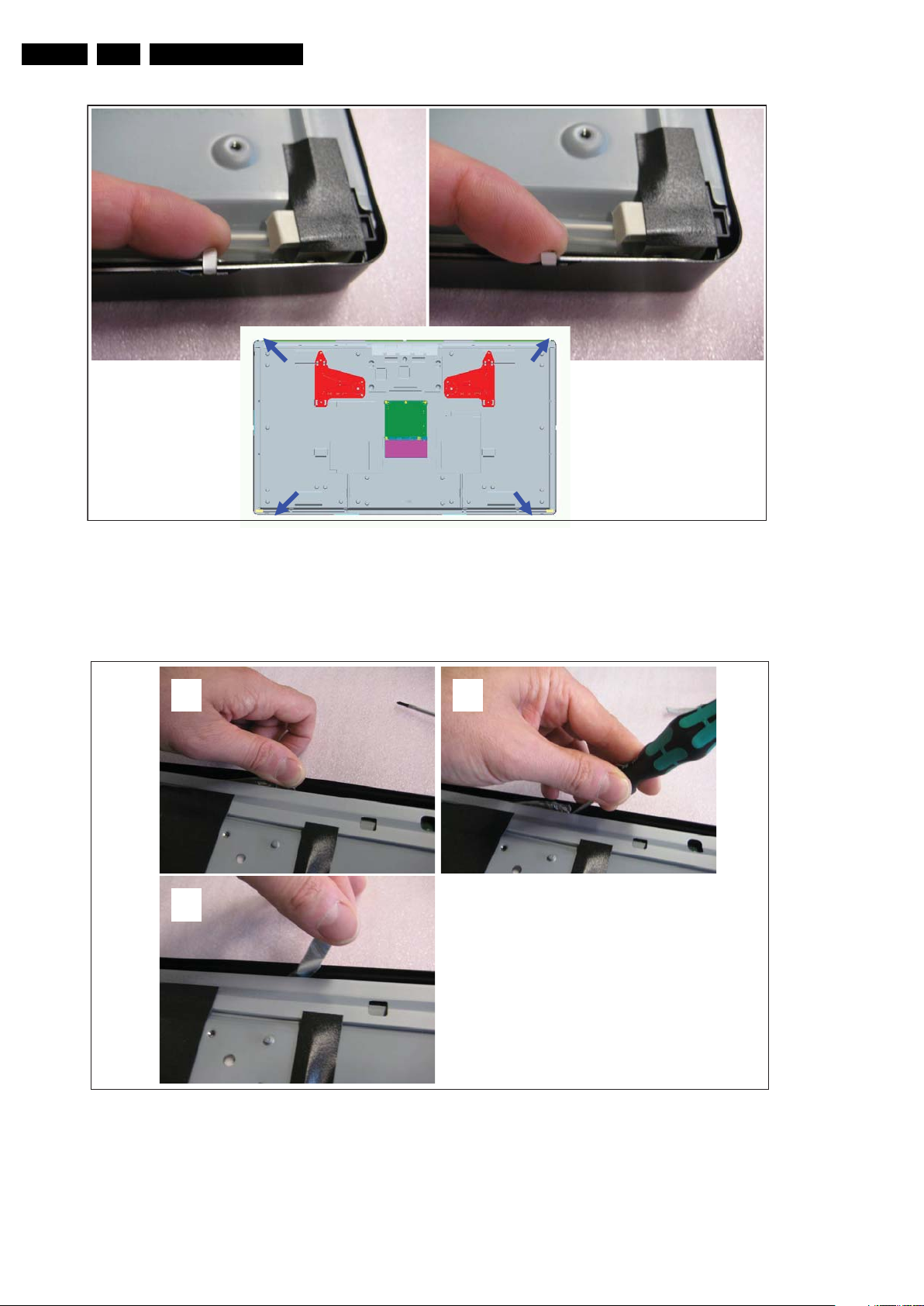

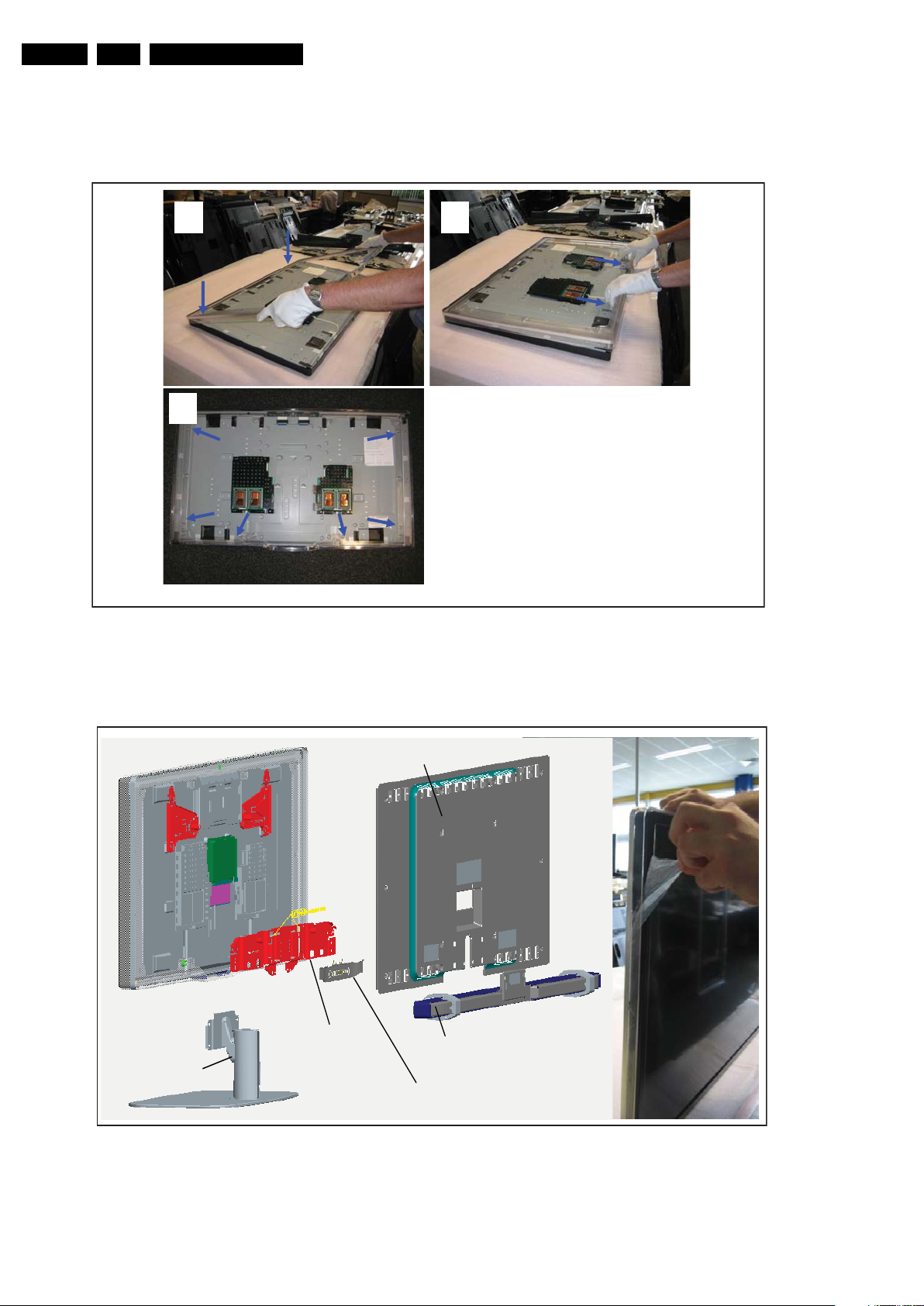

4.4.4 LCD Panel

SPECIAL NOTICE

The dis-assembly, re-assembly and/or exchange of the

LCD Panel is an elaborate process. Reason for this is the

mounting method of the Panel in the cabinet. Due to physical

restraints, no screws could be used, but instead adhesive

foams and -tapes are used.

Use gloves where indicated to avoid personal injury and

pollution of the LCD Panel (dust and/or fingerprints).

Exactly follow the instructions to avoid warranty issues,

especially when a defective LCD Panel has to be returned to

the supplier.

Step A. to F. describe the removal of the LCD Panel of the

cabinet.

Step K. to N. describe the mounting of the LCD Panel back into

the cabinet.

Step G. to J. describe which additional actions have to be taken

in the event the original LCD Panel has to be replaced.

Additional Spare Parts are needed when remounting the (new)

LCD Panel in the cabinet. These spare parts can be ordered as

one Service Kit using ordering code 3122 785 91150. The kit

contains the following items:

• 5 x Foam L × W × T = 20 × 43 × 0.5 mm.

• 6 x Foam L × W × T = 70 × 50 × 0.5 mm.

• 4 x Foam L × W × T = 30 × 43 × 0.5 mm.

• 1 x Foam L × W × T = 55 × 20 × 0.8 mm.

• 5 x Cable clamp (wire saddle) 11.2 mm.

LCD Panel Removal

A. Refer to next figure for details.

1. Remove stand.

2. Remove soundbar.

3. Remove backcover.

4. Remove sound interface.

5. Remove flare.

6. Remove stand bracket.

7. Remove leading edge.

Figure 4-19 LCD Panel -1-

Page 16

EN 16 Q529.1E LC4.

I_18020_106.eps

110908

1

3

2

I_18020_107.eps

180908

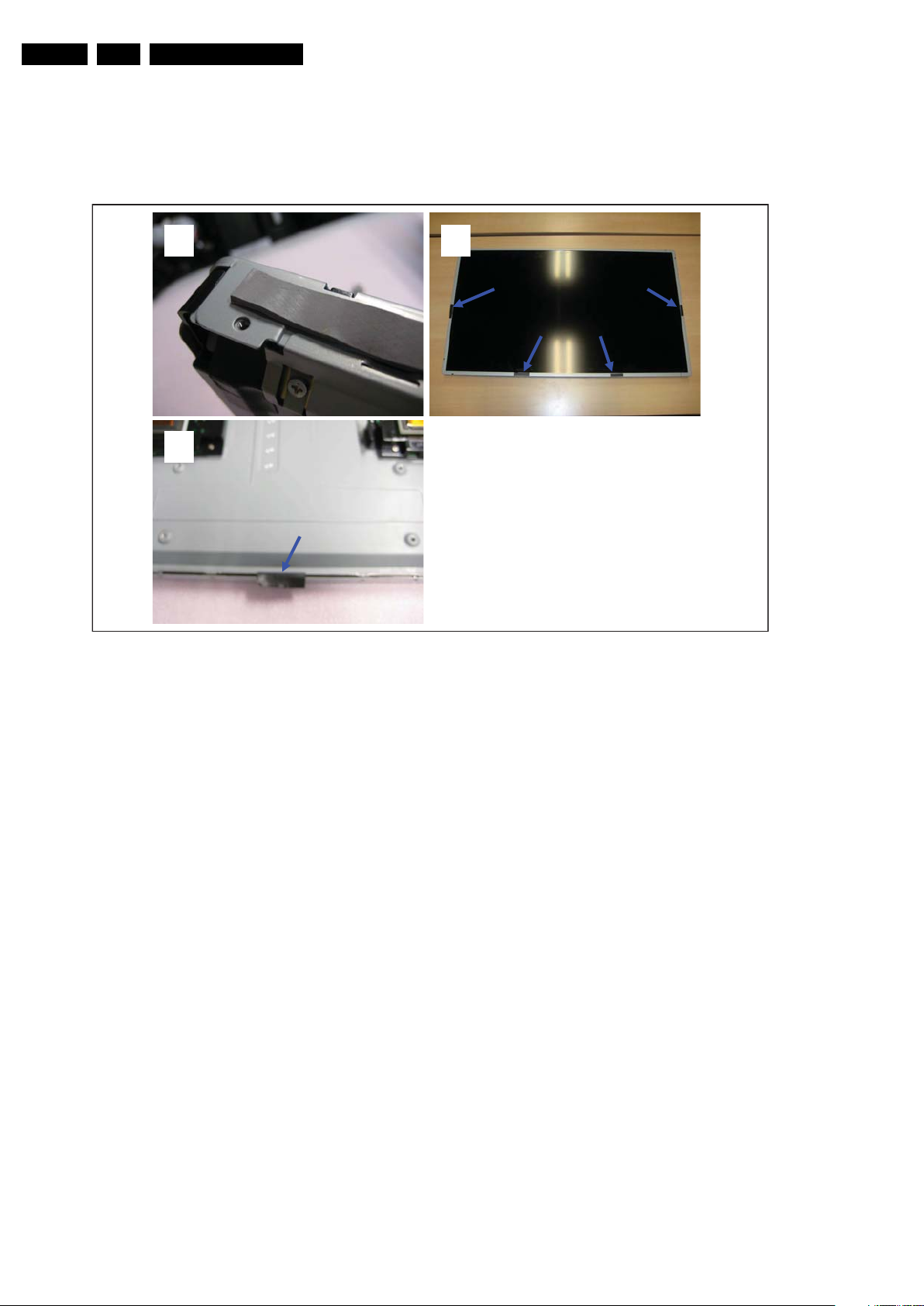

B. Bend metal lips in each corner of Front open.

Mechanical Instructions

Figure 4-20 LCD Panel -2-

C. Remove thermal foams (3x) between LCD-panel and upper

wall of metal Front.

1. Pull the upper bend open.

2. Move out the thermal foam with e.g. a screwdriver.

3. Pull out the thermal foam.

Figure 4-21 LCD Panel -3-

Page 17

Mechanical Instructions

1

3

2

I_18020_108.eps

110908

1

3

2

I_18020_109.eps

180908

D. Release two side walls of metal Front (use gloves).

1. Place thumb against each upper corner of the metal Front.

2. Place fingers against LCD Panel.

3. Push out LCD Panel in each corner until tape in middle of

side wall releases.

EN 17Q529.1E LC 4.

Figure 4-22 LCD Panel -4-

E. Release bottom wall of metal Front (use gloves).

1. Place hands in top/middle of metal Front and LCD Panel.

2. Pull metal Front and LCD Panel further apart until 2 tapes

in bottom wall release.

3. Take out LCD Panel.

Figure 4-23 LCD Panel -5-

Page 18

EN 18 Q529.1E LC4.

1

3

2

I_18020_110.eps

110908

F. Removing tapes/foams from LCD Panel (use “Label Off 50”;

“Intronics L50/200”).

1. Remove remains of thermal foam on top of LCD Panel.

2. Remove remains of double-sided tapes (4x) on front of

LCD Panel.

3. Remove protective foam on bottom of LCD Panel.

Mechanical Instructions

For re-assembly instructions, proceed with step K.

Figure 4-24 LCD Panel -6-

Page 19

Mechanical Instructions

Vesa Brackets

Connector

Plate

PCB

Isolator

Plates

I_18020_111.eps

151008

1

3

2

I_18020_112.eps

120908

LCD Panel Replacement

Instructions G to J apply if you have to replace the LCD

Panel.

G. Remove VESA brackets, PCB connector plate, wiring, and

isolator plates.

EN 19Q529.1E LC 4.

Figure 4-25 LCD Panel -7-

H. Remove all remaining tapes/foams/cable clamps.

1. Remove remaining tapes for wiring.

2. Remove cable clamps (five times).

3. Remove all backlight blocking foams.

4. Remove all glue remains with “Label Off 50”.

Figure 4-26 LCD Panel -8-

Page 20

EN 20 Q529.1E LC4.

1 2

Isolator

Plates

3

10±5 10±5

3

10±5

AB

C

A

B

C

B

A

B

BBBC

C

B

A

A

B

C

C

A

I_18020_113.eps

171008

1

3

2

Vesa Brackets

Connector

Plate

PCB

I_18020_114.eps

180908

I. Prepare new LCD Panel.

1. Take new LCD Panel and place two isolator plates.

2. Glue new foams on LCD Panel with the following

specifications:

- four times foam L × W × T = 20 × 43 × 0.5 mm [A].

- six times foam L × W × T = 70 × 50 × 0.5 mm [B].

- four times foam L × W × T = 30 × 43 × 0.5 mm [C].

3. Figure [3] show the upper- and lower foams.

Mechanical Instructions

Figure 4-27 LCD Panel -9-

J. Assemble VESA brackets, PCB, connector plate, and wiring.

1. Assemble VESA brackets, PCB and connector plate.

2. Assemble cable clamps:

- five times cable clamp 11.2 mm.

3. Assemble wiring.

Figure 4-28 LCD Panel -10-

Page 21

Mechanical Instructions

1

3

2

1

2

3

2

I_18020_115.eps

171008

1

3

2

A

B

I_18020_116.eps

180908

K. Assemble metal Front and LCD Panel (use gloves).

1. Take a new metal Front and remove liners of double-sided

tapes (four times).

2. Insert LCD Panel as shown in picture: first top side, then

cantilever down.

3. Bend down metal lips in each corner (4 times).

EN 21Q529.1E LC 4.

Figure 4-29 LCD Panel -11-

L. Assemble Leading Edge.

1. Assemble Leading Edge on Front.

2. Glue protective foam across edge of metal Front and LCD

Panel with the following specifications:

1 time foam L × W × T = 55 × 20 × 0.8 mm [A].

3. Glue light-blocking foam upon LED-PCB with the following

specifications:

1 time foam L × W × T = 20 × 43 × 0.5 mm [B].

Figure 4-30 LCD Panel -12-

Page 22

EN 22 Q529.1E LC4.

Stand

Back Cover

Soundbar

Stand

Bracket

Sound Interface

I_18020_118.eps

180908

M. Assemble Flare.

1. Place flare upon LCD Panel as shown in picture: first on top

side.

2. Cantilever flare down while pulling it slightly open (to avoid

scratches from metal Front).

3. Fix flare on Panel (six screws).

Mechanical Instructions

1

1

1

3

3

Figure 4-31 LCD Panel -13-

N. Assemble Stand Bracket, Sound Interface, Back Cover,

Soundbar and Stand.

1. Remove protective foils on both sides of Flare.

2

I_18020_117.eps

171008

Figure 4-32 LCD Panel -14-

Page 23

4.5 Set Re-assembly

To re-assemble the whole set, execute all processes in reverse

order, except for the Monitor. To re-assembly the Monitor,

follow the instructions in the applicable section of this Manual.

Notes:

• While re-assembling, make sure that all cables are placed

and connected in their original position. See figure “Cable

dressing”.

• Pay special attention not to damage the EMC foams on the

SSB shields. Ensure that EMC foams are mounted

correctly.

Mechanical Instructions

EN 23Q529.1E LC 4.

Page 24

EN 24 Q529.1E LC5.

I_18020_146.eps

190908

1

SDM1SDM

1

SDM2SPI-P

Service Modes, Error Codes, and Fault Finding

5. S ervice Modes, Error Codes, and Fault Finding

Index of this chapter:

5.1 Test Points

5.2 Service Modes

5.3 Stepwise Start-up

5.4 Service Tools

5.5 Error Codes

5.6 The Blinking LED Procedure

5.7 Protections

5.8 Fault Finding and Repair Tips

5.9 Software Upgrading

5.1 Test Points

As most signals are digital, it will be difficult to measure

waveforms with a standard oscilloscope. However, several key

ICs are capable of generating test patterns, which can be

controlled via ComPair. In this way it is possible to determine

which part is defective.

Perform measurements under the following conditions:

• Service Default Mode.

• Video: Colour bar signal.

• Audio: 3 kHz left, 1 kHz right.

5.2 Service Modes

Service Default mode (SDM) and Service Alignment Mode

(SAM) offers several features for the service technician, while

the Customer Service Mode (CSM) is used for communication

between the call centre and the customer.

This chassis also offers the option of using ComPair, a

hardware interface between a computer and the TV chassis. It

offers the abilities of structured troubleshooting, error code

reading, and software version read-out for all chassis.

(see also section “5.4.1 ComPair”).

– Skip/blank of non-favourite pre-sets.

How to Activate SDM

For this chassis there are two kinds of SDM: an analog SDM

and a digital SDM. Tuning will happen according table “SDM

Default Settings”.

• Analog SDM: use the standard RC-transmitter and key in

the code “062596”, directly followed by the “MENU” button.

Note: It is possible that, together with the SDM, the main

menu will appear. To switch it “off”, push the “MENU”

button again.

• Digital SDM: use the standard RC-transmitter and key in

the code “062593”, directly followed by the “MENU” button.

Note: It is possible that, together with the SDM, the main

menu will appear. To switch it “off”, push the “MENU”

button again.

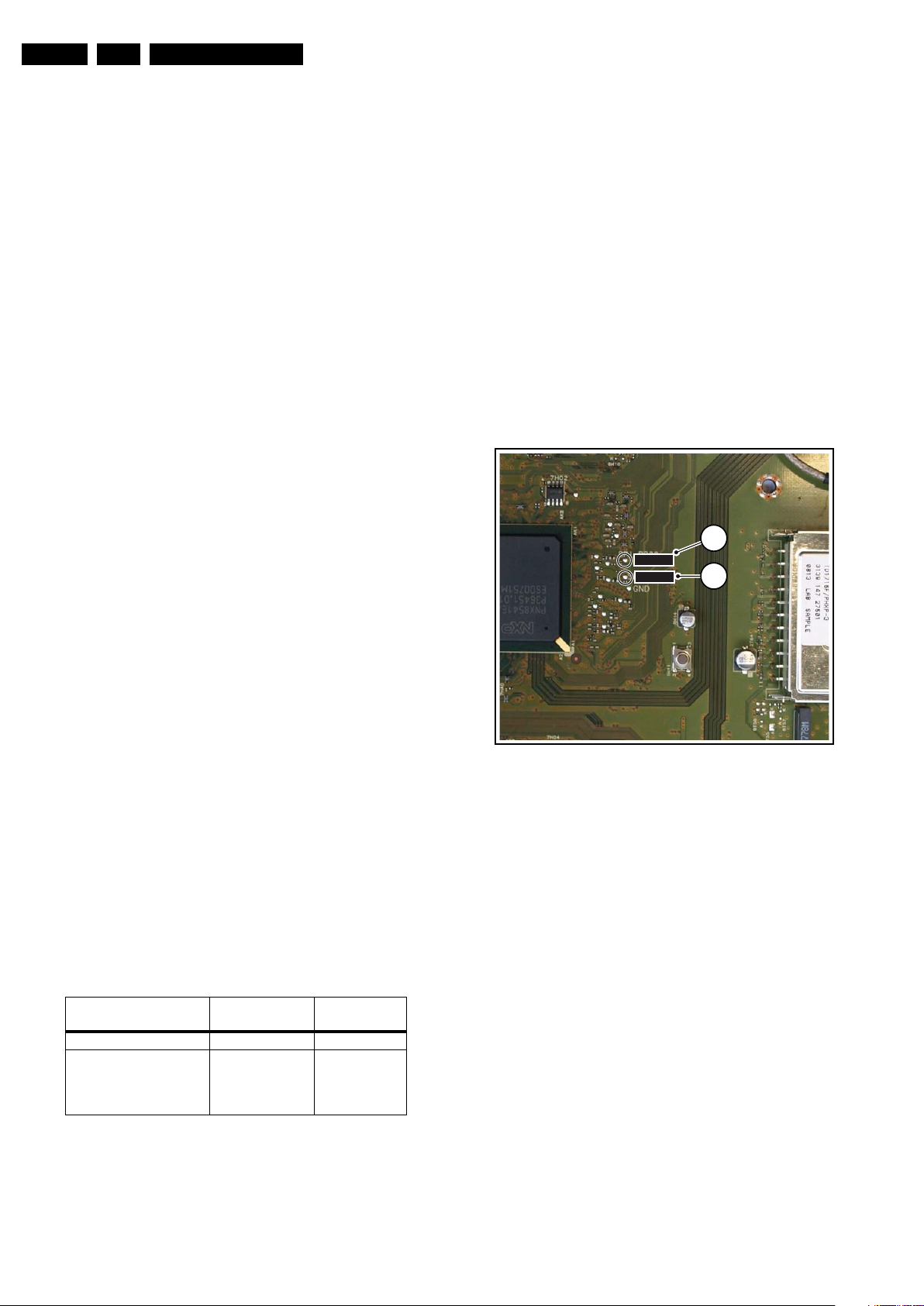

• Analog SDM can also be activated by connecting for a

moment the solder pad (see figure “Service mode pads”)

on the SSB with the indication “SDM” [1], to GND.

5.2.1 Service Default Mode (SDM)

Purpose

• To create a pre-defined setting, to get the same

measurement results as given in this manual.

• To override SW protections detected by stand-by

processor and make the TV start up to the step just before

protection (a sort of automatic stepwise start up). See

section “5.3 Stepwise Start-up”.

• To start the blinking LED procedure where only layer 2

errors are displayed. (see also section “5.5 Error Codes”)

Specifications

Table 5-1 SDM default settings

Region Freq. (MHz)

Europe, AP(PAL/Multi) 475.25 PAL B/G

Europe, AP DVB-T 546.00 PID

• All picture settings at 50% (brightness, colour, contrast).

• All sound settings at 50%, except volume at 25%.

• All service-unfriendly modes (if present) are disabled, like:

– (Sleep) timer.

– Child/parental lock.

– Picture mute (blue mute or black mute).

– Automatic volume levelling (AVL).

Video: 0B 06 PID

PCR: 0B 06 PID

Audio: 0B 07

Default

system

DVB-T

Figure 5-1 Service mode pads

After activating this mode, “SDM” will appear in the upper right

corner of the screen (when a picture is available).

How to Navigate

When the “MENU” button is pressed on the RC transmitter, the

set will toggle between the SDM and the normal user menu

(with the SDM mode still active in the background).

How to Exit SDM

Use one of the following methods:

• Switch the set to STAND-BY via the RC-transmitter.

• Via a standard customer RC-transmitter: key in “00”sequence.

5.2.2 Service Alignment Mode (SAM)

Purpose

• To perform (software) alignments.

• To change option settings.

• To easily identify the used software version.

• To view operation hours.

• To display (or clear) the error code buffer.

How to Activate SAM

Via a standard RC transmitter: key in the code “062596”

directly followed by the “INFO” button. After activating SAM

Page 25

PHILIPS

MODEL:

32PF9968/10

PROD.SERIAL NO:

AG 1A0620 000001

040

39mm

27mm

(CTN Sticker)

Display Option

Code

E_06532_038.eps

240108

Service Modes, Error Codes, and Fault Finding

EN 25Q529.1E LC 5.

with this method a service warning will appear on the screen,

continue by pressing the red button on the RC.

Contents of SAM:

• Hardware Info.

– A. SW Version. Displays the software version of the

main software (example: Q591E-1.2.3.4 =

AAAAB_X.Y.W.Z).

• AAAA= the chassis name.

• B= the region: A= AP, E= EU, L= Latam, U = US.

For AP sets it is possible that the Europe software

version is used.

• X.Y.W.Z= the software version, where X is the

main version number (different numbers are not

compatible with one another) and Y.W.Z is the sub

version number (a higher number is always

compatible with a lower number).

– B. SBY PROC Version. Displays the software version

of the stand-by processor.

– C. Production Code. Displays the production code of

the TV, this is the serial number as printed on the back

of the TV set. Note that if an NVM is replaced or is

initialized after corruption, this production code has to

be re-written to NVM. ComPair will foresee in a

possibility to do this.

• Operation Hours. Displays the accumulated total of

operation hours (not the stand-by hours). Every time the

TV is switched “on/off”, 0.5 hours is added to this number.

• Errors (followed by maximum 10 errors). The most recent

error is displayed at the upper left (for an error explanation

see section “5.5 Error Codes”).

• Reset Error Buffer. When “cursor right” (or the “OK

button) is pressed followed by another “OK” button touch,

the error buffer is reset.

• Alignments. This will activate the “ALIGNMENTS” submenu.

• Dealer Options. Extra features for the dealers.

• Options. Extra features for Service. For more info

regarding option codes, see chapter 8 “Alignments”.

Note that if the option code numbers are changed, these

have to be confirmed with pressing the “OK” button before

the options are stored. Otherwise changes will be lost.

• Initialize NVM. The moment the processor recognizes a

corrupted NVM, the “initialize NVM” line will be highlighted.

Now, two things can be done (dependent of the service

instructions at that moment):

– Save the content of the NVM via ComPair for

development analysis, before initializing. This will give

the Service department an extra possibility for

diagnosis (e.g. when Development asks for this).

– Initialize the NVM.

Note: When the NVM is corrupted, or replaced, there is a high

possibility that no picture appears because the display code is

not correct. So, before initializing the NVM via the SAM, a

picture is necessary and therefore the correct display option

has to be entered. Refer to chapter 8 “Alignments” for details.

To adapt this option, it’s advised to use ComPair (the correct

HEX values for the options can be found in chapter 8

“Alignments”) or a method via a standard RC (described

below).

Changing the display option via a standard RC

: Key in the

code “062598” directly followed by the “MENU” button and

“XXX” (where XXX is the 3 digit decimal display code as

mentioned in table “Option code overview” in chapter 8

“Alignments”. Remark : there is only one display option code

here “168” used for this chassis). If the above action is

successful, the front LED will go out as an indication that the

RC sequence was correct. After the display option is changed

in the NVM, the TV will go to the Stand-by mode. If the NVM

Figure 5-2 Location of Display Option Code sticker

• Store - go right. All options and alignments are stored

when pressing “cursor right” (or the “OK” button) and then

the “OK”-button.

• SW Maintenance.

– SW Events. Not useful for Service purposes. In case

of specific software problems, the development

department can ask for this info.

– HW Events. Not useful for Service purposes. In case

of specific software problems, the development

department can ask for this info.

• Test settings. For development purposes only.

• Upload to USB. To upload several settings from the TV to

an USB stick, which is connected to the SSB. The items are

“Channel list”, “Personal settings”, “Option codes”,

“Display-related alignments” and “History list”. First a

directory “repair\” has to be created in the root of the USB

stick. To upload the settings select each item separately,

press “cursor right” (or the “OK” button), confirm with “OK”

and wait until “Done” appears. In case the download to the

USB stick was not successful “Failure” will appear. In this

case, check if the USB stick is connected properly and if

the directory “repair” is present in the root of the USB stick.

Now the settings are stored onto the USB stick and can be

used to download onto another TV or other SSB.

Uploading is of course only possible if the software is

running and if a picture is available. This method is created

to be able to save the customer’s TV settings and to store

them into another SSB.

• Download to USB. To download several settings from the

USB stick to the TV. Same way of working as with

uploading. To make sure that the download of the channel

list from USB to the TV is executed properly, it is necessary

to restart the TV and tune to a valid preset if necessary.

Note: The “History list item” can not be downloaded from

USB to the TV. This is a “read-only” item. In case of

specific problems, the development department can ask

for this info.

• Development file versions. Not useful for Service

purposes, this information is only used by the development

department.

How to Navigate

• In SAM, the menu items can be selected with the

“CURSOR UP/DOWN” key (or the scroll wheel) on the RCtransmitter. The selected item will be highlighted. When not

all menu items fit on the screen, move the “CURSOR UP/

DOWN” key to display the next/previous menu items.

• With the “CURSOR LEFT/RIGHT” keys (or the scroll

wheel), it is possible to:

– (De) activate the selected menu item.

– (De) activate the selected sub menu.

• With the “OK” key, it is possible to activate the selected

action.

was corrupted or empty before this action, it will be initialized

first (loaded with default values). This initializing can take up to

20 seconds.

How to Exit SAM

Use one of the following methods:

• Press the “MENU” button on the RC-transmitter.

Page 26

EN 26 Q529.1E LC5.

Service Modes, Error Codes, and Fault Finding

• Switch the set to STAND-BY via the RC-transmitter.

5.2.3 Customer Service Mode (CSM)

Purpose

When a customer is having problems with his TV-set, he can

call his dealer or the Customer Helpdesk. The service

technician can then ask the customer to activate the CSM, in

order to identify the status of the set. Now, the service

technician can judge the severity of the complaint. In many

cases, he can advise the customer how to solve the problem,

or he can decide if it is necessary to visit the customer.

The CSM is a read only mode; therefore, modifications in this

mode are not possible.

When in this chassis CSM is activated, a test pattern will be

displayed during 5 seconds (1 second Blue, 1 second Green

and 1 second Red, then again 1 second Blue and 1 second

Green). This test pattern is generated by the PNX5100. So if

this test pattern is shown, it could be determined that the back

end video chain (PNX5100, LVDS, and display) of the SSB is

working.

New in this chassis are two test patterns with fixed colours:

• When the Green key is pushed while in CSM (toggle

function) : a fixed testpattern by the “FPGA transmitter”

device located on the LVDS panel will be generated. The

selftest of this device is confirmed positive with a fully

Green picture displayed on the screen.

• When the Yellow key is pushed while in CSM (toggle

function) : a fixed testpattern by the “FPGA receiver”

device located on the monitor will be generated. The

selftest of this device is confirmed positive with a fully

Yellow picture displayed on the screen.

When CSM is activated and there is a USB stick connected to

the TV, the software will dump the complete CSM content to the

USB stick. The file (CSM.txt) will be saved in the root of the

USB stick. This info can be handy if no information is displayed.

Also when CSM is activated, the layer 1 error is displayed via

blinking LED on the HUB. Only the latest error is displayed.

(see also section “5.5 Error Codes”).

How to Activate CSM

Key in the code “123654” via the standard RC transmitter.

Note: Activation of the CSM is only possible if there is no (user)

menu on the screen!

How to Navigate

By means of the “CURSOR-DOWN/UP” knob (or the scroll

wheel) on the RC-transmitter, can be navigated through the

menus.

Contents of CSM

The contents are reduced to 4 pages: General, Software

versions/General, Quality items and Addtitional Info. The group

names itself are not shown anywhere in the CSM menu.

General

• Set Type. This information is very helpful for a helpdesk/

workshop as reference for further diagnosis. In this way, it

is not necessary for the customer to look at the rear of the

TV-set. Note that if an NVM is replaced or is initialized after

corruption, this set type has to be re-written to NVM.

ComPair will foresee in a possibility to do this.

• Production Code. Displays the production code (the serial

number) of the TV. Note that if an NVM is replaced or is

initialized after corruption, this production code has to be

re-written to NVM. ComPair will foresee a in possibility to

do this.

• Installed date. Indicates the date of the first installation of

the TV. This date is acquired via time extraction.

• Options 1. Gives the option codes of option group 1 as set

in SAM (Service Alignment Mode).

• Options 2. Gives the option codes of option group 2 as set

in SAM (Service Alignment Mode).

• 12NC SSB. Gives an identification of the SSB as stored in

NVM. Note that if an NVM is replaced or is initialized after

corruption, this identification number has to be re-written to

NVM. ComPair will foresee in a possibility to do this. This

identification number is the 12nc number of the SSB.

Remark: the content here can also be a part of the 12NC

SSB in combination with the serial number.

• 12NC display. Shows the 12NC of the display

• 12NC supply. Shows the 12NC of the supply.

• 12NC “bolt-on”. Shows the 12NC of the “BOLT-ON”module.

• 12NC LED dimming panel. Shows the 12NC of the LED

dimming panel.

Software versions/General

• Current main SW. Displays the built-in main software

version. In case of field problems related to software,

software can be upgraded. As this software is consumer

upgradeable, it will also be published on the Internet.

Example: Q591E_1.2.3.4

• Standby SW. Displays the built-in stand-by processor

software version. Upgrading this software will be possible

via ComPair or via USB (see chapter Software upgrade).

Example: STDBY_3.0.1.2.

• MOP ambient light SW. Displays the MOP ambient light

EPLD SW.

• MPEG4 software. Displays the MPEG4 software (optional

for sets with MPEG4).

• PNX5100 boot NVM. Displays the SW-version that is used

in the PNX5100 boot NVM.

• LED dimming SW. Displays the SW-version for the LED

dimming panel.

• MPEG4 (blue to toggle). Displays the activation of

MPEG4 reception functionality (on/off).

Quality items

• Signal quality. Bad / average /good

• Child lock. Not active / active. This is a combined item for

locks. If any lock (Preset lock, child lock, lock after or

parental lock) is active, the item shall show “active”.

• Table channel changed. This item is for development

purpose.

• Key missing. This is a combined item for keys. The keys

have a separate bit and the sum is displayed in decimal

value.

– HDMI key valid = 001

– MAC key valid = 010

Important remark here : due to a software bug, the

MAC key is missing and not valid when “2” is displayed

in CSM.So, if for instance the HDMI and MAC keys are

both valid, the decimal value in CSM “1” is displayed

and not “3”.

– BDS key valid = 100

If 3 keys are valid the value: “5” is displayed (should be

“7” but due to the software bug it is not).

For value:

“0” in CSM: MAC stored, HDCP invalid.

“1” in CSM: MAC stored, HDCP valid.

“2” in CSM: no MAC, HDCP invalid.

“3” in CSM: no MAC, HDCP valid.

• CI slot present. If the common interface module is

detected the result will be “YES”, else “NO”.

• HDMI input format. The detected input format of the

HDMI.

• HDMI audio input stream. The HDMI audio input stream

is displayed: present / not present.

• HDMI video input stream. The HDMI video input stream

is displayed: present / not present.

Page 27

Service Modes, Error Codes, and Fault Finding

Active

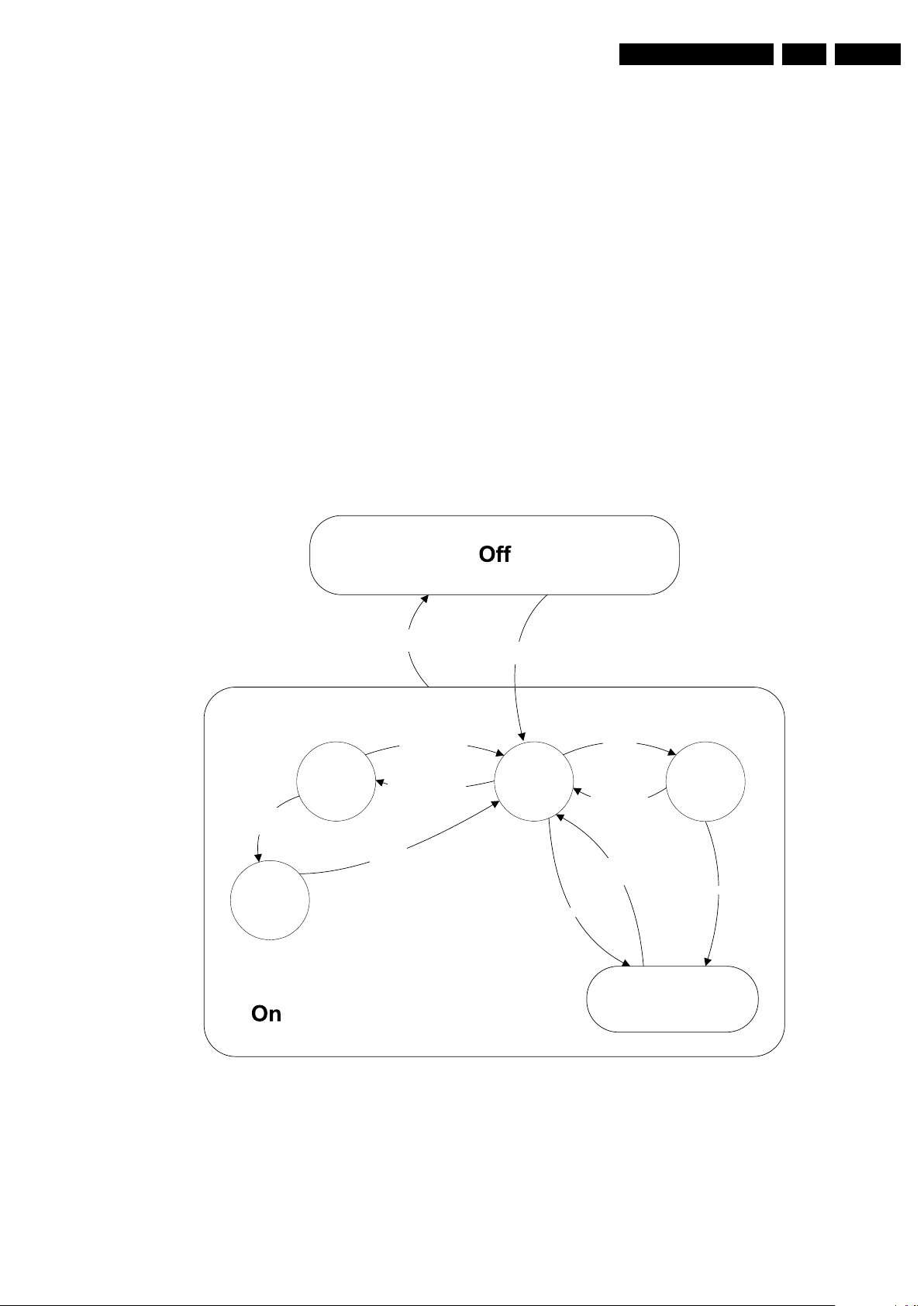

Semi

St by

St by

Mains

on

Mains

off

GoToProtection

-WakeUp requested

-Acquisition needed

-No data Acquisition

required

-tact SW pushed

-last status is hibernate

after mains ON

- St by requested

-tact SW pushed

WakeUp

requested

Protection

WakeUp

requested

(SDM)

GoToProtection

Hibernate

-Tact switch Pushed

-last status is hibernate

after mains ON

Tact switch

pushed

I_17660_124.eps

140308

EN 27Q529.1E LC 5.

Additional Info

• 12NC LVDS2DP board. Displays the 12NC of the built-in

LVDS-to-DisplayPort software.

• 12NC monitor board. Displays the 12NC of the monitor

board.

• SW version DPTX. Displays the built-in DisplayPort TX

software version.

• SW version DPRX. Displays the built-in DisplayPort RX

software version.

• SW version FPGA e-box. Displays the built-in FPGA ebox (HUB) software version.

• SW version FPGA monitor. Displays the built-in FPGA

monitor software version.

• SW version microP monitor. Displays the built-in monitor

microprocessor software version.

• SW version NVM monitor. Displays the built-in monitor

NVM software version.

How to Exit CSM

Press “MENU” on the RC-transmitter.

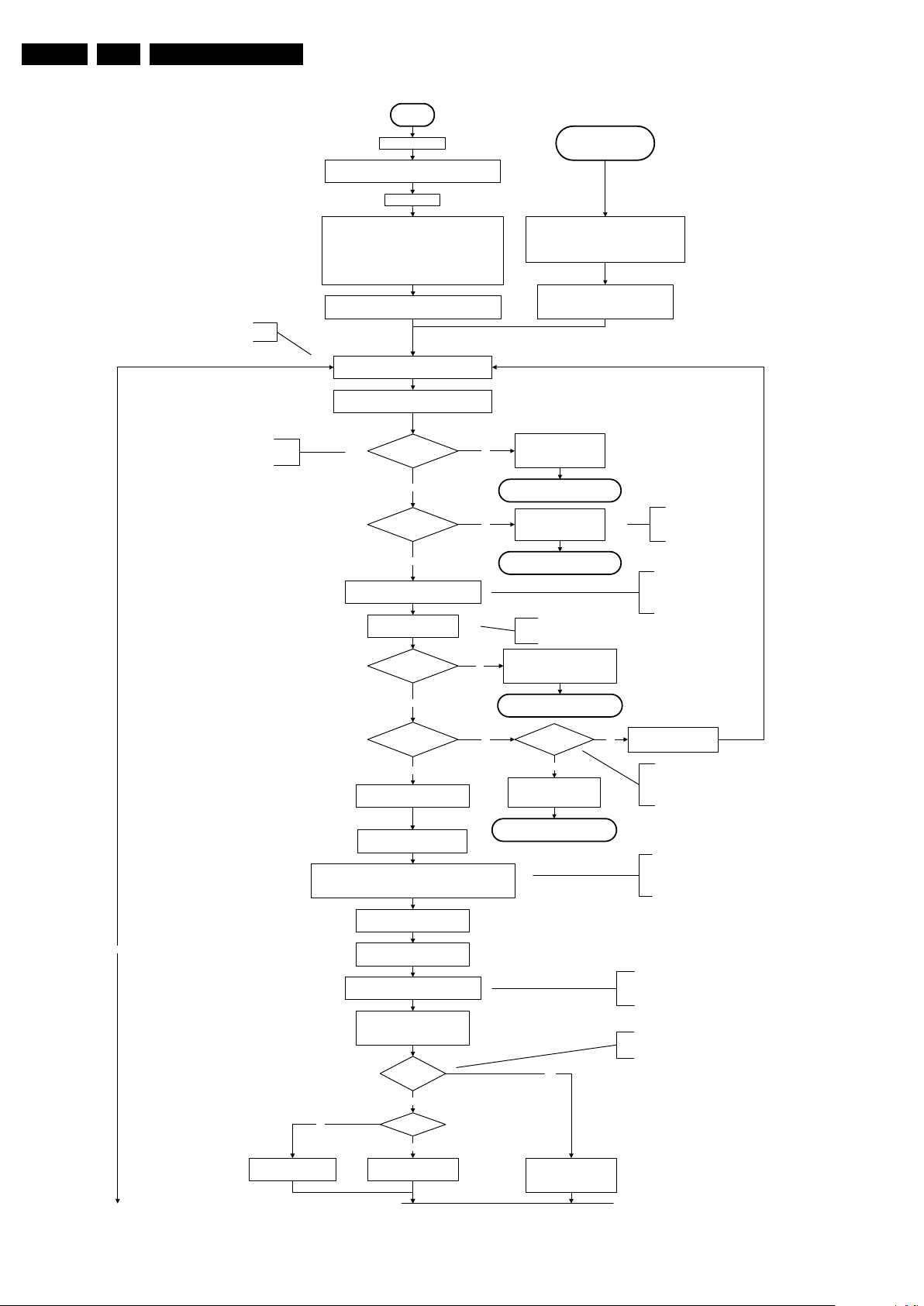

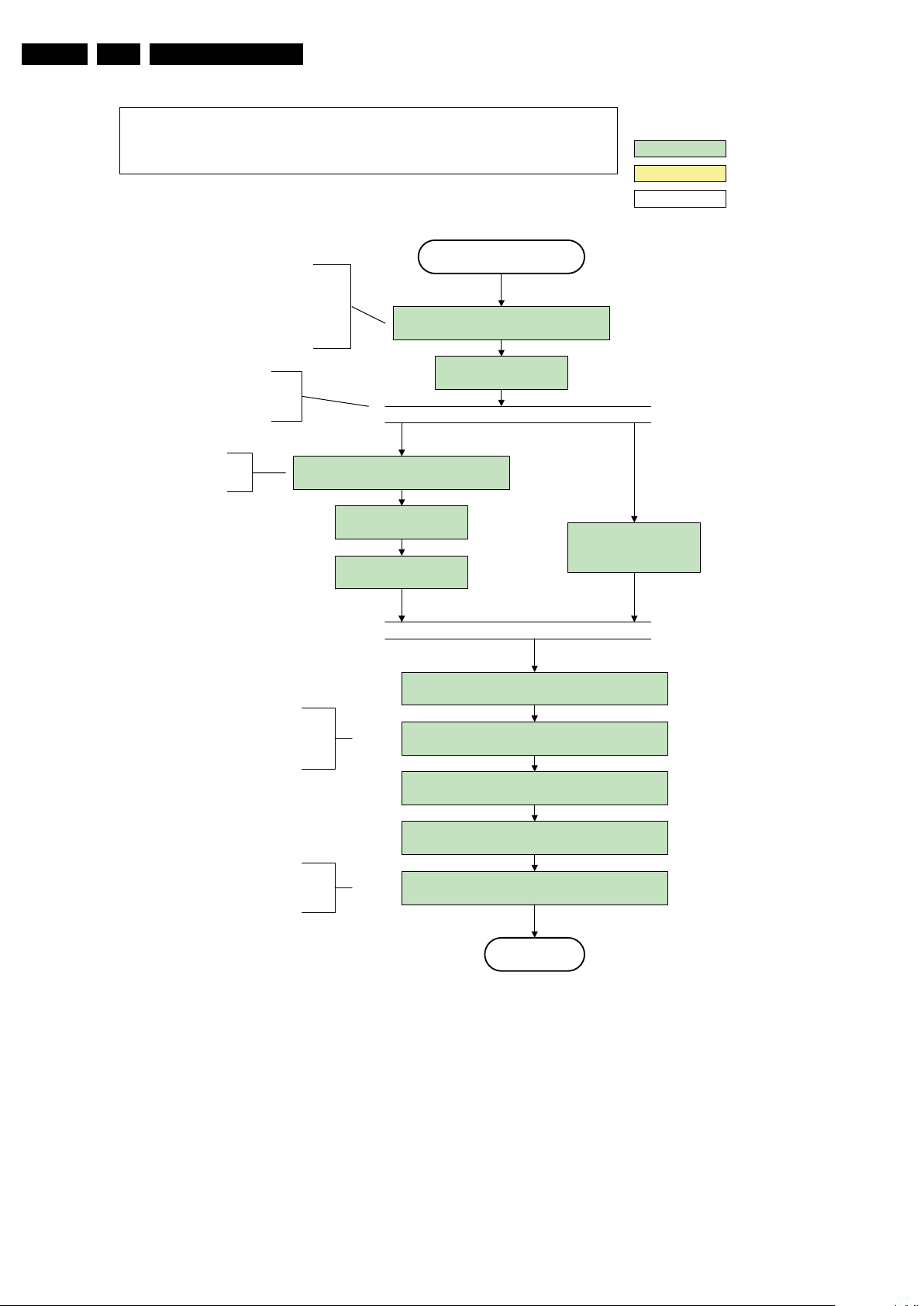

5.3 Stepwise Start-up

When the TV is in a protection state due to an error detected by

stand-by software (error blinking is displayed) and SDM is

activated via shortcutting the pins on the SSB, the TV starts up

until it reaches the situation just before protection. So, this is a

kind of automatic stepwise start-up. In combination with the

start-up diagrams below, you can see which supplies are

present at a certain moment. Important to know is, that if e.g.

the 3V3 detection fails and thus error layer 2 = 18 is blinking

while the TV is restarted via SDM, the Stand-by Processor will

enable the 3V3, but the TV set will not go to protection now.

The TV will stay in this situation until it is reset (Mains/AC

Power supply interrupted). Caution: in case the start up in this

mode with a faulty FET 7U08 is done, you can destroy all IC’s

supplied by the +3V3, due to overvoltage (12V on 3V3-line). It

is recommended to measure first the FET 7U08 or other FET’s

on shortcircuit before activating SDM via the service pads.

The abbreviations “SP” and “MP” in the figures stand for:

• SP: protection or error detected by the Stand-by

Processor.

• MP: protection or error detected by the MIPS Main

Processor.

Figure 5-3 Transition diagram

Page 28

EN 28 Q529.1E LC5.

No

EJTAG probe

connected ?

No

Yes

Release AVC system r eset

Feed warm boot script

To I_17660_125b.eps To I_17660_125b.eps

Cold boot?

Yes

No

Set I²C slave address

of Standby µP to (A0h)

An EJTAG probe (e.g. WindPower ICE probe) can

be connected for Linux Kernel debugging

purposes.

This will a llow access to NVM a nd

NAND FLASH and can not be done

earlier because the FLASH needs to

be in Write Protect as long as the

supplies are not available.

Detect EJTAG debug probe

(pulling pin of the probe interface to

ground by inserting EJTAG probe)

Relea se AVC system r eset

Feed cold boot script

Release AVC system r eset

Feed initializing boot script

disable alive mechanism

Initialise I/O pins of the st-by µP:

- Switch reset-AVCLOW (reset state)

- Switch WP-NandFlash LOW (protected)

- Switch reset-system LOW (reset state)

- Switch reset-5100 LOW (reset state)

- Switch reset-Ethernet LOW (reset state)

- Switch reset-ST7100 LOW (reset state)

- keep reset-NVM high, Audio-reset and Audio-Mute-Up HIGH

Off

Standby Supply starts running.

All standby supply voltages become available .

st-by µ P resets

Stand by or

Protection

Mains is app lied

- Switch Audio-Reset high.

It is low in the standby mode if the standby

mode lasted longer than 10s.

start keyboard scanning, RC detection. Wake up reasons are

off.

If the protection state was left by short circuiting the

SDM pins, detection of a protection condition during

startup will stall the startup. Protection conditions in a

playing set will be ignored. The protection mode will

not be entered.

Switch LOW the RESET-NVM line to allow access to NVM. (Add a

2ms delay before trying to address the NVM to allow correct NVM

initialization, this is not issue in this setup, the delay is automatically

covered by the architectural setup)

Release Reset-PNX5100.

PNX5100 will start b ooting.

Wait 10ms (minimum) to allow the bootscript

of the PNX5100 to configure the PCI arbiter

Before PNX8541 boots, the PNX5100 should have

set its PCI arbiter (bootscript command). To allow

this, approx. 1ms is needed. This 1ms is extended

to 10ms to also give some relaxation to the supplies.

Switch HIGH the WP-NandFlash to

allow access to NAND Flash

+12V, +/-12Vs, AL and Bolt-on power

is switched on, followed by the +1V2 DCDC converter

Enable the supply fault detection

algorithm

No

Yes

Detect-1 I/O line

High?

Switch ON Platform and display supply by switching

LOW the Standby line.

This enables the +3V3 and

+5V converter. As a result,

also +5V-tuner, +2V5, +1V8PNX8541 and +1V8-PNX5100

become available.

yes

Enable the DCDC converter for +3V3 and

+5V. (EN ABLE-3V3)

Voltage output error:

Layer1: 2

Layer2: 18

Important remark; the appearance of the +12V

will start the +1V2 DCDC converter automatically

No

Yes

Supply-fault I/O

High?

The supply-fault line is a

combination of the DCDC

converters and the audio

protection line.

1V2 DCDC or class D error:

Layer1: 2

Layer2: 19

Enter protection

No

Detect2 high received

within 1 second?

Power-OK er ror:

Layer1: 3

Layer2: 16

Enter protection

Yes

No

Supply-fault I/O

High?

3V3 / 5V DCDC or class D error:

Layer1: 2

Layer2: 11

Enter protection

Wait 50ms

Enter protection

Delay of 50ms needed because of the latency of the detect-1 circuit.

This delay is also needed for the PNX5100. The reset of the

PNX5100 should only be released 10ms after powering the IC.

Detect2 should be polled on the standard 40ms

interval and startup should be continued when

detect2 becomes high.

Yes

No

Detect -2 I/ O line

High?

Disable 3V3, switch standby

line high and wait 4 seconds

Added to make the system more robust to

power dips during startup. At this point the

regular supply fault detection algorithm which

normally detects power dips is not up and

running yet.

I_17660_125a.eps

140308

Service Modes, Error Codes, and Fault Finding

Figure 5-4 “Off” to “Semi Stand-by” flowchart (part 1)

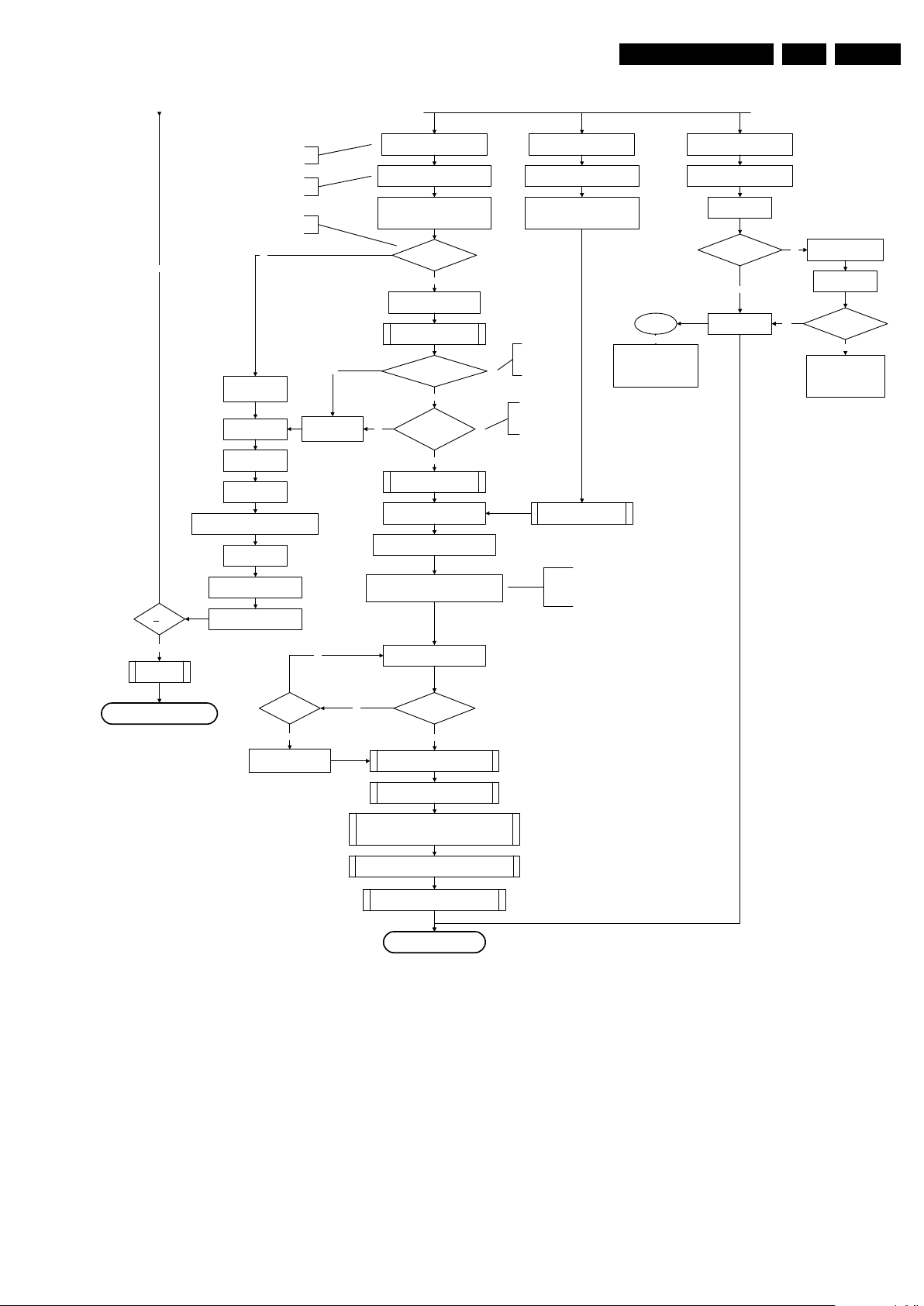

Page 29

Service Modes, Error Codes, and Fault Finding

Yes

MIPS reads the wake up reason

from standby µP.

Semi-Standby

initialize tuner, Master IF and channel

decoder

Initialize video processing IC's

Initiali ze source sele ction

initialize AutoTV by triggering CHS AutoTV Init interface

3-th try?

No

Blink Code as

error code

Bootscript ready

in 1250 ms?

Yes

No

Enable Alive check mechanism

Wait until AVC starts to

communicate

SW initializatio n

succeeded

within 20s?

No

Switch Standby

I/O line high.

RPC start (comm. protocol)

Set I²C slave address

of Standby µP to (60h)

Yes

Disable all supply related protections and

switch off the +3V3 +5V DC/DC converter.

switch off the remaining DC/DC

converters

Wait 5ms

Switch AVC PNX85 41

in reset (active low )

Wait 10ms

Switch the NVM reset

line HIGH.

Flash to Ram

image transfer succeeded

within 30s?

No

Yes

Code =

Layer1: 2

Layer2: 53

Code =

Layer1: 2

Layer2: 15

Initialize Ambilight with Lights off.

Timing need to be updated if

more mature info is available.

Timing needs to

be updated if more

mature info is

available.

Timing needs to be

updated if more

matur e info is

available.

Downloaded

successfully ?

Download firmware into the channel

decoder

Third try? No

No

Yes

Log channel decoder error:

Layer1: 2

Layer2: 37

Yes

Initialize audio

Enter protection

Release reset MPEG4 module:

BOLT-ON-IO: High

MPEG4 module will start booting

autonomously.

Wait 3000 ms

Start alive IIC polling

mechanism

POR polling positive?

yes

No

Log SW event:

STi7100PorFailure

Wait 200 ms

POR polling positive?yes

No

bootSTi7100PorFailure:

Log HW error

Layer1: 2

Layer2: 38

and generate cold boot

Alive

polling

Log SW event

STi7100AliveFailedError

and generate fast cold reboot

eventually followed by a cold

reboot.

NOK

Reset-system is switched HIGH by the

AVC at the end of the bootscript

AVC releases Reset-Ethernet when the

end of the AVC boot-script is detected

This cannot be done through the bootscript,

the I/O is on the standby µP

Reset- system is connected to USB

From I_17660_125a.eps From I_17660_125a.eps

-reset,

4to1HDMI Mux and channel decoder.

Reset-Audio and Audio-Mute-Up are

switched by MIPS code later on in the

startup process

Reset-syst em is switched HIGH by the

AVC at the end of the bootscript

AVC releases Reset-Ethernet when the

end of the AVC boot-script is detected

Reset-Audio and Audio-Mute-Up are

switched by MIPS code later on in the

startup process

Switch on the display in case of a LED backlight

display by sending the TurnOnDisplay(1) (I²C)

command to the PNX5100

In case of a LED backlight display, a LED DIM panel is

present which is fed by the Vdisplay. To power the LED DIM

Panel, the Vdisplay switch driven by the PNX5100 must be

closed. The display startup sequence is taken care of by the

LED DIM panel.

I_17660_125b.eps

140308

EN 29Q529.1E LC 5.

Figure 5-5 “Off” to “Semi Stand-by” flowchart (part 2)

Page 30

EN 30 Q529.1E LC5.

Service Modes, Error Codes, and Fault Finding

Constraints taken into account:

- Display may only be started when valid LVDS output clock can be delivered by the AVC .

- Between 5 and 50 ms after power is supplied, display should receive valid lvds clock .

- minimum wait time to switch on the lamp after power up is 200ms.

action holder: AVC

action holder: St-by

autonomous action

The assumption here is that a f ast toggle (<2s)

can only happen during ON-> SEMI -> ON. In

these states, the AVC is still act ive and can

provide the 2s delay. If the transitio n ON-> SEMI-

>STBY -> SEMI -> ON can be made in less than 2s,

the semi -> stby transition has to be delayed

CPipe already generates a valid output

clock in t he semi -standb y state : display

startup can start immediately when leaving

The timings to be used in

combination with the PanelON

comman d for t his specific display

The higher level requirement is that audio and

video should be demuted without transient

effects and that the audio should be demuted

maximum 1s before or at the same time as the

until the requirement is met.

the semi-standby state.

TurnOnDisplay(1) (I²C) command to the PNX5100

unblanking of the video.

Semi Standby

Wait until previous on-state is left more than 2

seconds ago. (to prevent LCD display problems)

Assert RGB video blanking

Switch on the display by sending the

wait 250ms (min. = 200ms)

Switch on LCD backlight

(Lamp-ON)

Wait until valid and stable audio and video , corresponding to

the requested output is delivered by the AVC.

Switch Audio -Reset low and wait 5ms

Release audio mute and wait 100ms before any other audio

handling is done (e.g. volume change)

and audio mute

Initialize audio and video

processing IC's and functions

according needed use case.

The higher level requirement is that the

ambilig ht functionality may not be switched on

before the backlight is turned on in case the

set contains a CE IPB inverter supply.

Figure 5-6 “Semi Stand-by” to “Active” flowchart

unblank the video.

Switch on the Ambilight functionality according the last status

settings.

Active

I_17660_126.eps

140308

Page 31

Service Modes, Error Codes, and Fault Finding

Active

Semi Standby

action holder: AVC

autonomous action

action holder: St-by

Initialize audio and video

processing IC's and functions

according needed use case.

Assert RGB video blanking

and audio mute

Wait until previous on-state is left more than 2

seconds ago. (to prevent LCD display problems)

The assumption here is that a f ast toggle (<2s)

can only happen during ON->SEMI ->ON. In

these states, the AVC is still act ive and can

provide t he 2s delay. If the t ransition ON -> SEMI-

->STBY-> SEMI -> ON can be made in less than 2s,

the semi - > stby transition has to be delayed

until the requirement is met.

Switch Audio-Reset low and wait 5ms

Constraints taken into account:

- Display may only be started when valid LVDS output clock can be delivered by the AVC .

- Between 5 and 50 ms after power is supplied, display should receive valid lvds clock .

- minimum wait time to switch on the lamp after power up is 200ms.

- To have a reliable operation of the backlight, the backlight should be driven with a PWM duty cycle of 100%

during the first second. Only after this first one or two seconds, the PWM may be set to the required output level

(Note that the PWM output should be present before the backlight is switched on). To minimize the artefacts, the

picture should only be unblanked after these first seconds.

Restore dimming backlight feature, PWM and BOOST output

and unblank the video.

Wait until valid and stable audio and video, corresponding to the requested

output is delivered by the AVC

AND

[the backlight PWM has been on for 1s (internal inverter LPL displays

OR the backlight PWM has been on for 2s (external inverter LPL displays)] .

The higher level requirement is that audio and

video should be demuted without transient

effects and that the audio should be demuted

maximum 1s before or at the same time as the

unblanking of the video.

Release audio mute and wait 100ms before any other audio

handling is done (e.g. volume change)

CPipe already generates a valid output

clock in t he semi -standby state: d isplay

startup can start immediately when leaving

the semi-standby state.

wait 250ms (min. = 200ms)

Switch on LCD backlight

(Lamp-ON)

Switch off the dimming backlight feature, set

the BOOST control to nominal and make sure

PWM output is set to 100%

Switch on the display by sending the

TurnOnDisplay(1) (I²C) command to the PNX5100

Switch on the Ambilight functionality according the last status

settings.

The higher level requirement is that the

ambilig ht functionality may n ot be swit ched on

before the backlight is turned on in case the

set contains a CE IPB inverter supply.

I_17660_127.eps

140308

EN 31Q529.1E LC 5.

Figure 5-7 “Semi Stand-by” to “Active” flowchart LCD with preheat

Page 32

EN 32 Q529.1E LC5.

Active

Semi Standby

action holder: AVC

autonomous action

action holder: St-by

Initialize audio and video

processing IC's and functions

according needed use case.

Assert RGB video blanking

and audio mute

Wait until previous on-state is left more than 2

seconds ago. (to prevent LCD display problems)

The assumption here is that a f ast toggle (<2s)

can only happen during ON-> SEMI -> ON. In

these states, the AVC is still active an d can

provide the 2s delay. If the transition ON -> SEMI-

>STBY->SEMI->ON can be made in less than 2s,

the semi -> stby transition has to be delayed

until the requirement is met.

Switch Audio -Reset low and wait 5ms

Constraints taken into account:

- Display may only be started when valid LVDS output clock can be delivered by the AVC.

- Between 5 and 50 ms after power is supplied, display should receive valid lvds clock .

- minimum wait time to switch on the lamp after power up is 200ms.

unblank the video.

Wait until valid and stable audio and video , corresponding to

the requested output is delivered by the AVC.

The higher level requirement is that audio and

video should be demuted without transient

effects and that the audio should be demuted

maximum 1s before or at the same time as the

unblanking of the video.

Release audio mute and wait 100ms before any other audio

handling is done (e.g. volume change)

CPipe already generates a valid output

clock in t he semi -standby state : display

startup can start immediately when leaving

the semi-standby state.

wait 250ms (min. = 200ms)

TBC in def. spec

Switch on LCD backlight

(Lamp-ON)

Switch on the display by sending the OUTPUTENABLE (I²C) command to the LED DIM panel

Switch on the Ambilight functionality according the last status

settings.

The higher level requirement is that the

ambilig ht functionality may n ot be swit ched on

before the backlight is turned on in case the

set contains a CE IPB inverter supply.

I_17660_128.eps

140308

Service Modes, Error Codes, and Fault Finding

Figure 5-8 “Semi Stand-by” to “Active” flowchart (LED backlight)

Page 33

Service Modes, Error Codes, and Fault Finding

Semi Standby

Active

action holder: AVC

autonomous action

action holder: St-by

Wait 25 0ms (min. = 200ms)

Mute all sound outputs via softmute

Mute all video outputs

switch off LCD backlight

Force ext audio outputs to ground

(I/O: audio reset)

And wait 5ms

Switch off the display by sending the

TurnOnDisplay(0) (I²C) command to the PNX5100

switch o ff Ambilight

Set main amplifier mute (I/O: audio-mute)

Wait 100ms

Wait until Ambilight has faded out

(fixed wait time of x s)

The higher level requirement is that the

backlight may not be switched off before the

ambilight functionality is turned off in case the

set contains a CE IPB inverter supply.

I_17660_129.eps

140308

EN 33Q529.1E LC 5.

Figure 5-9 “Active” to “Semi Stand-by” flowchart (LCD non DFI)

Page 34

EN 34 Q529.1E LC5.

transfer Wake up reasons to the Stand by µP.

Stand by

Semi Stand by

action holder: MIPS

autonomous action

action holder: St-by

Disable all supply related protections and switch off

the DC/DC converters (ENABLE-3V3)

Switch OFF all supplies by switching HIGH the

Standby I/O line

Switch AVC system in reset state

Switch reset-PNX5100 LOW

Switch reset-ST7100 LOW

Switch Reset-Ethernet LOW

Important remark:

release reset audio 10 sec after

entering st andby to save pow er

Wait 5ms

Wait 10ms

Switch the NVM reset line HIGH

Switch het WP-Nandflash LOW

Delay transition until ramping down of ambient light is

finished. *)

If ambientlight functionality was used in semi -standby

(lampadaire mode), switch off ambient light

*) If this is not performed and the set is

switched to standby when the switch off of

the ambilights is still ongoing , the lights will

switch off abruptly when the supply is cut.

Switch Memories to self-refresh (this creates a more

stable condition when switching off the power).

I_17660_130.eps

140308

Service Modes, Error Codes, and Fault Finding

Figure 5-10 “Semi Stand-by” to “Stand-by” flowchart

Page 35

Service Modes, Error Codes, and Fault Finding

Protection

action holder: MIPS

autonomous action

action holder: St-by

Redefine wake up reasons for protection

state and transfer to stand-by µP.

Log the appropriate err or and

set stand-by flag in NVM

MP

Ask stand-by µP to enter protection state

Flash the Protection-LED in order to indicate

protection state* (*): This can be the standby LED or the ON LED

depending on the availability in the set

SP

Switch off LCD lamp supply

Wait 250ms (min. = 200ms)

Switch off LVDS signal

Switch off 12V LCD supply within a time frame of

min. 0.5ms to max. 50ms after LVDS switch off.

If needed to speed up this transition,

this block could be omitted . This is

depending on the outcome of the

safety investiga tions .

Disable all supply related protections and switch off

the +1V8 and the +3V3 DC/DC converter.

Switch OFF all supplies by switching HIGH the

Standby I/O line.

Switch AVC in r eset state

Wait 5ms

Wait 10ms

Switch the NVM r eset line H IGH.

I_17660_131.eps

140308

EN 35Q529.1E LC 5.

Figure 5-11 “To Protection State” flowchart

5.4 Service Tools

5.4.1 ComPair

Introduction

ComPair (Computer Aided Repair) is a Service tool for Philips

Consumer Electronics products. and offers the following:

1. ComPair helps to quickly get an understanding on how to

repair the chassis in a short and effective way.

2. ComPair allows very detailed diagnostics and is therefore

capable of accurately indicating problem areas. No

knowledge on I

because ComPair takes care of this.

2

C or UART commands is necessary,

3. ComPair speeds up the repair time since it can

automatically communicate with the chassis (when the uP

is working) and all repair information is directly available.

4. ComPair features TV software up possibilities.

Specifications

ComPair consists of a Windows based fault finding program

and an interface box between PC and the (defective) product.

The ComPair II interface box is connected to the PC via an

USB cable. For the TV chassis, the ComPair interface box and

the TV communicate via a bi-directional cable via the service

connector(s).

The ComPair fault finding program is able to determine the

problem of the defective television, by a combination of

automatic diagnostics and an interactive question/answer

procedure.

Page 36

EN 36 Q529.1E LC5.

E_06532_036.eps

150208

TO

UART SERVICE

CONNECTOR

TO

UART SERVICE

CONNECTOR

TO

I2C SERVICE

CONNECTOR

TO TV

PC

HDMI

I

2

C only

Optional power

5V DC

ComPair II Developed by Philips Brugge

RC out

RC in

Optional

Switch