Philips plc18v8z DATASHEETS

INTEGRATED CIRCUITS

PLC18V8Z

Zero standby power

CMOS versatile PAL devices

Product specification

Replaces data sheet PLC18V8Z35/PLC18V8ZI of Dec 19 1995,

and data sheet PLC18V8Z25/PLC18V8ZI of Dec 19, 1995

1997 Aug 08

Philips Semiconductors Product specification

Zero standby power

CMOS versatile PAL devices

DESCRIPTION

The PLC18V8Z is a universal PAL device featuring high

performance and virtually zero-standby power for power sensitive

applications. They are reliable, user-configurable substitutes for

discrete TTL/CMOS logic. While compatible with TTL and HCT

logic, the PLC18V8Z can also replace HC logic over the V

of 4.5 to 5.5V .

The PLC18V8Z is a two-level logic element comprised of 10 inputs,

74 AND gates (product terms) and 8 output Macro cells.

Each output features an “Output Macro Cell” which can be

individually configured as a dedicated input, a combinatorial output,

or a registered output with internal feedback. As a result, the

PLC18V8Z is capable of emulating all common 20-pin PAL devices

to reduce documentation, inventory, and manufacturing costs.

A power-up reset function and a Register Preload function have

been incorporated in the PLC18V8Z architecture to facilitate state

machine design and testing.

With a standby current of less than 100µA and active power

consumption of 1.5mA/MHz, the PLC18V8Z is ideally suited for

power sensitive applications in battery operated/backed portable

instruments and computers.

The PLC18V8Z is also processed to industrial requirements for

operation over an extended temperature range of -40°C to +85°C

and supply voltage of 4.5V to 5.5V .

Ordering information can be found on the following page.

FEA TURES

•20-pin Universal Programmable Array Logic

•Virtually Zero-Standby-power

– 20µA (typical)

•Available in DIP, PLCC, SOL (Small Outline), SSOP (Shrink Small

Outline), and TSSOP (Thin Shrink Small Outline) packages

•Functional replacement for Series 20 PAL devices

= 24mA

– I

OL

•Up to 18 inputs and 8 input/output macro cells

•Programmable output polarity

•Power-up reset on all registers

•Register Preload capability

•Synchronous Preset/Asynchronous Reset

•Security fuse to prevent duplication of proprietary designs

•Also available in 3V operation–the P3C18V8Z

APPLICATIONS

•Battery powered instruments

•Laptop and pocket computers

CC

range

•Industrial control

•Medical Instruments

•Portable communications equipment

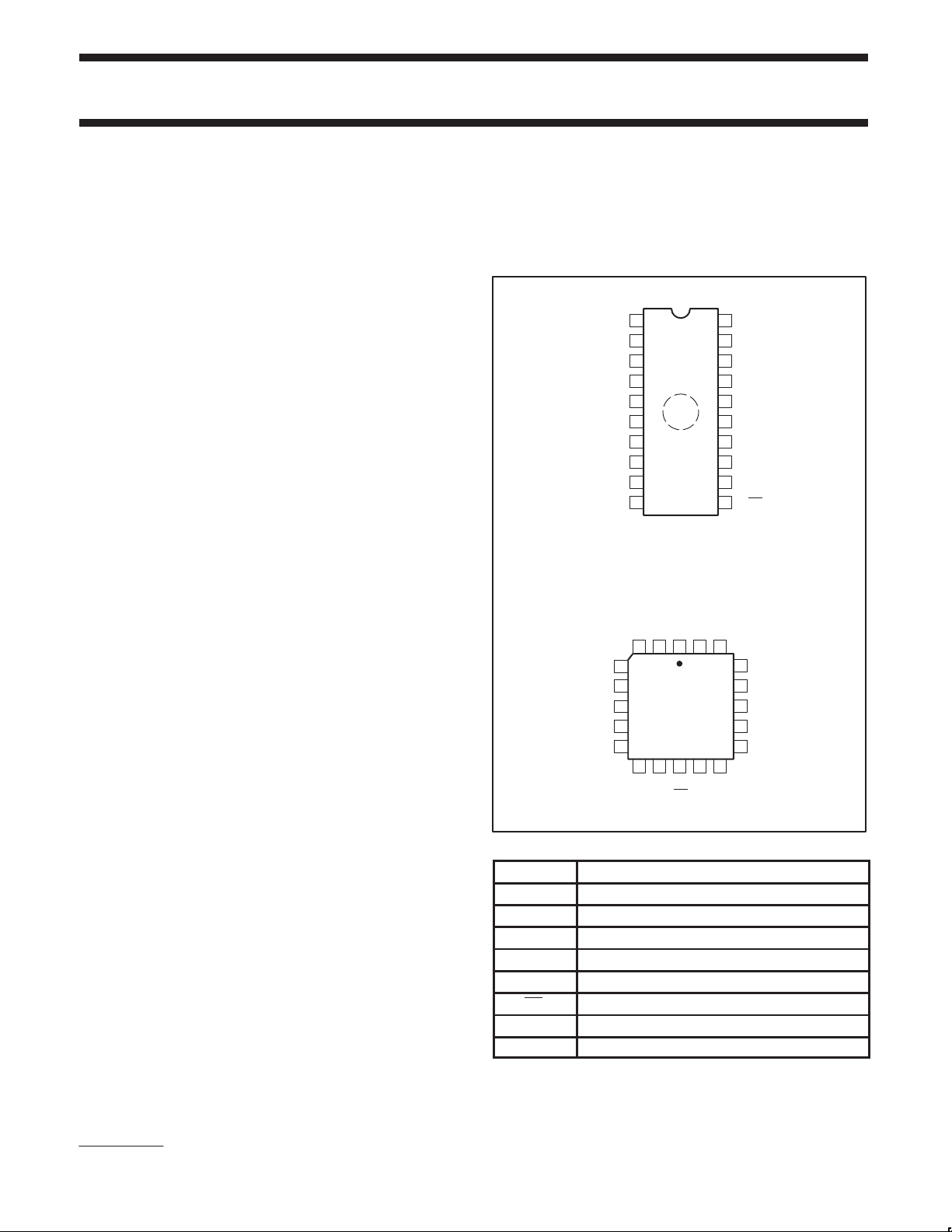

PIN CONFIGURATIONS

D, DB, DH, N, Packages

1

I0/CLK

2

I1

3

I2

4

I3

5

I4

6

I5

7

I6

8

I7

9

I8 F0

10 11

GND

D = Plasitc Small Outline Large Package (300mil-wide)

DB = Plastic Shrink Small Outline Package (5.3mm wide)

DH = Plastic Thin Shrink Small Outline Package (4.4mm wide)

N = Plastic Dual In-Line Package (DIP) (300mil-wide)

A Package

CLK

I1I2

I3

4

I4

5

6

I5

7

I6

I7

8

910111213

GND

I8

A = Plastic Leaded Chip Carrier

PIN DESCRIPTIONS

I Dedicated Input

B Bidirectional input/output

O Dedicated output

D Registered output (D-type flip-flop)

F Output/Input Macrocell

CLK Clock Input

OE Output Enable

V

CC

GND Ground

Supply Voltage

I0/

I9/

OE

123

V

CC

F0 F1

20

19

18

17

16

15

14

13

12

F7

1920

PLC18V8Z

V

CC

F7

F6

F5

F4

F3

F2

F1

I9/OE

F6

18

17

F5

16

F4

15

F3

F2

14

SP00544

PAL is a registered trademark of Advanced Micro Devices, Inc.

1997 Aug 08 853–2016 18258

2

Philips Semiconductors Product specification

T

T

Zero standby power

CMOS versatile PAL devices

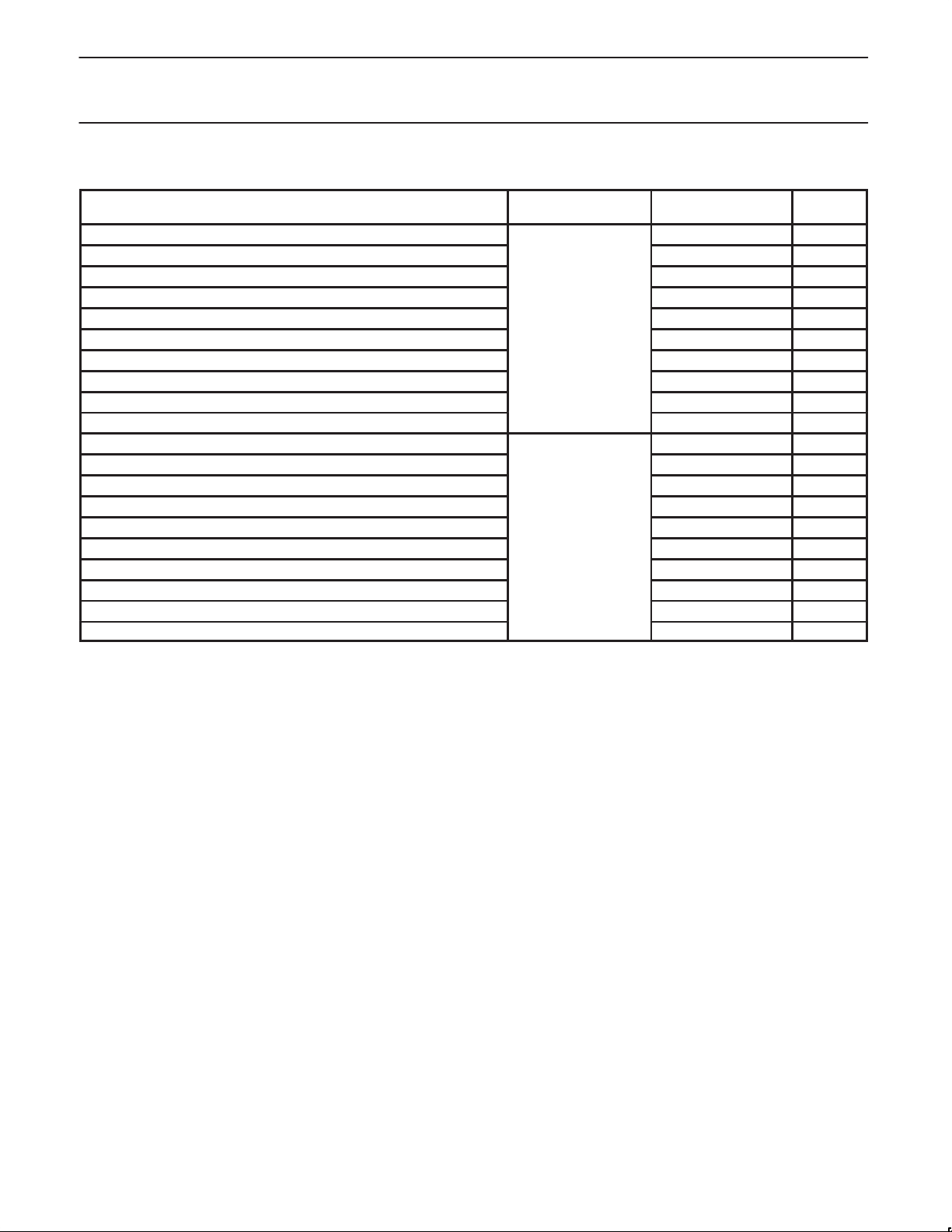

ORDERING INFORMATION

DESCRIPTION

20-Pin (300mil-wide) Plastic Dual In-Line Package, 25ns t

20-Pin (350mil square) Plastic Leaded Chip Carrier Package PLC18V8Z25A SOT380-1

20-Pin (300mil-wide) Plastic Small Outline Large Package PLC18V8Z25D SOT163-1

20-Pin (5.3mm-wide) Plastic Shrink Small Outline Package PLC18V8Z25DB SOT339-1

20-Pin (4.4mm-wide) Plastic Thin Shrink Small Outline Package

20–Pin (300mil–wide) Plastic Dual In–Line Package. 35ns t

20–Pin (350mil square) Plastic Leaded Chip Carrier Package PLC18V8Z35A SOT380–1

20–Pin (300mil square) Plastic Small Outline Large Package Package PLC18V8Z35D SOT163–1

20–Pin (5.3mm–wide) Plastic Shrink Small Outline Package PLC18V8Z35DB SOT339–1

20–Pin (4.4mm–wide) Plastic Thin shrink Small Outline Package PLC18V8Z35DH SOT260–1

20-Pin (300mil-wide) Plastic Dual In-Line Package 25ns t

20-Pin (350mil square) Plastic Leaded Chip Carrier Package PLC18V8ZIAA SOT380-1

20-Pin (300mil-wide) Plastic Small Outline Large Package PLC18V8ZIAD SOT163-1

20-Pin (5.3mm-wide) Plastic Shrink Small Outline Package PLC18V8ZIADB SOT339-1

20-Pin (4.4mm-wide) Plastic Thin Shrink Small Outline Package

20–Pin (300mil–wide) Plastic Dual In–Line Package, 40ns t

20–Pin (350mil square) Plastic Leaded chip Carrier Package PLC18V8ZIA SOT380–1

20–Pin (300mil square) Plastic Small Outline Large Package PLC18V8ZZID SOT163–1

20–Pin (5.3mm–wide) Plastic Shrink Small Outline Package PLC18V8ZIDB SOT339–1

20–Pin (4.4mm–wide) Plastic Thin Shrink Small Outline Package PLC18V8ZIDH SOT360–1

PD

PD

PD

PD

TEMPERATURE

RANGE

Commercial

p

emperature Range

± 5% Power Supplies

Industrial

p

emperature Range

± 10% Power Supplies

ORDER CODE

PLC18V8Z25N SOT146-1

PLC18V8Z25DH SOT360-1

PLC18V8Z35N SOT146–1

PLC18V8ZIAN SOT146-1

PLC18V8ZIADH SOT360-1

PLC18V8ZIN SOT146–1

PLC18V8Z

DRAWING

NUMBER

1997 Aug 08

3

Philips Semiconductors Product specification

Zero standby power

CMOS versatile PAL devices

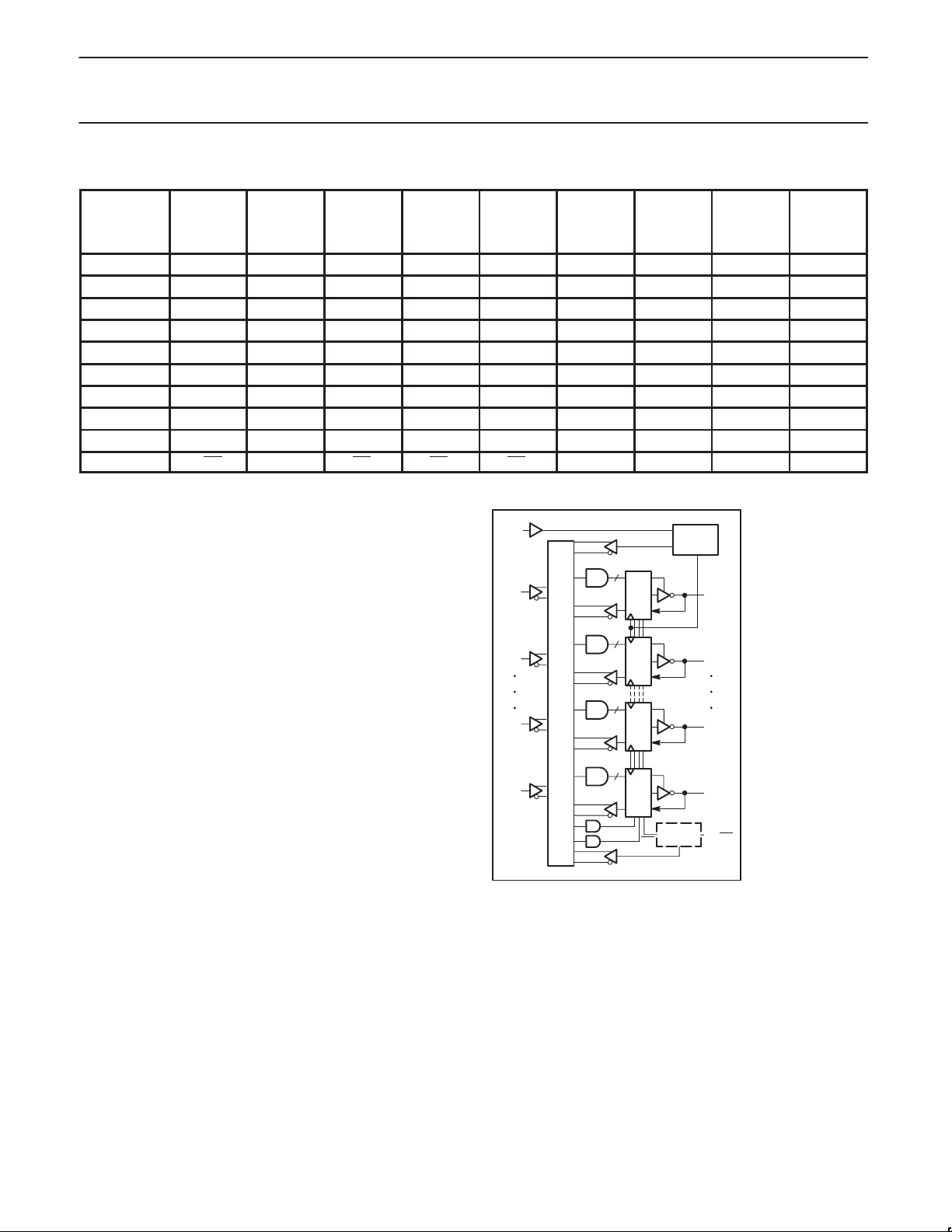

PAL DEVICE TO PLC18V8Z OUTPUT PIN CONFIGURATION CROSS REFERENCE

16L8

PIN

NO.

PLC

18V8Z

16H8

16P8

16R4

16RP4

16R6

16RP6

16R8

16RP8

16P8

1 I0/CLK I CLK CLK CLK I I I I

19 F7 B B B D I I I O

18 F6 B B D D I I O O

17 F5 B D D D I O O O

16 F4 B D D D O O O O

15 F3 B D D D O O O O

14 F2 B D D D I O O O

13 F1 B B D D I I O O

12 F0 B B B D I I I O

11 I9/OE I OE OE OE I I I I

The Philips Semiconductors’ state-of-the-art Floating-Gate CMOS

EPROM process yields bipolar equivalent performance at less than

one-quarter the power consumption. The erasable nature of the

EPROM process enables Philips Semiconductors to functionally test

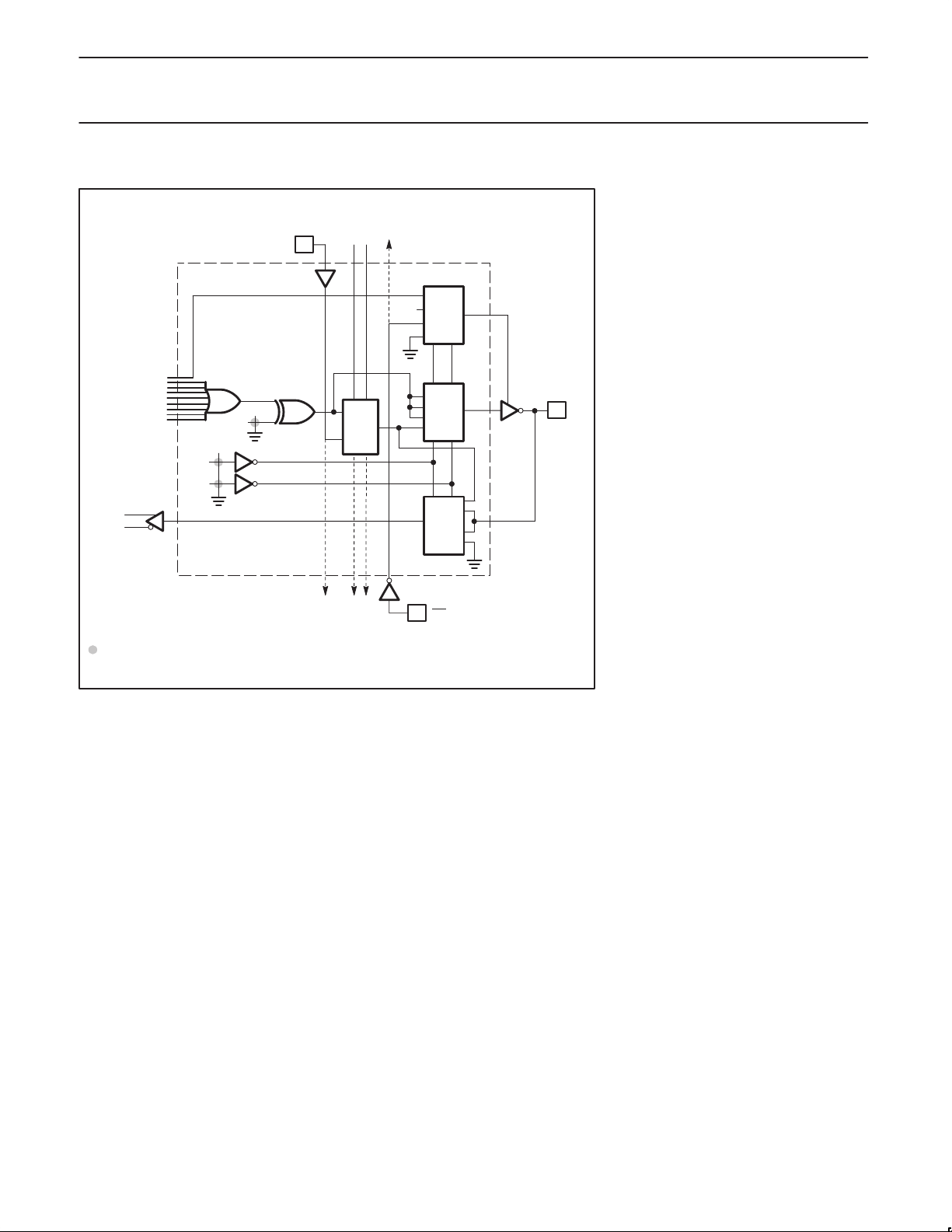

FUNCTIONAL DIAGRAM

I0/

CLK

the devices prior to shipment to the customer. Additionally, this

allows Philips Semiconductors to extensively stress test, as well as

ensure the threshold voltage of each individual EPROM cell. 100%

programming yield is subsequently guaranteed.

I

1

I

2

16L2

16H2

16P2

14L4

14H4

14P4

CONFIG.

I

0

CELL

9

OMC

9

CLK

OMC

12L6

12H6

12P6

F

7

F

6

PLC18V8Z

10L8

10H8

10P8

9

I

7

36 ROWS X 72 COLUMNS

PROGRAMMABLE AND ARRAY

I

8

SP

AR

OMC

9

OMC

CONFIG.

OE

CELL

I

9

SP00013

F

1

F

0

I9/OE

1997 Aug 08

4

Philips Semiconductors Product specification

Zero standby power

CMOS versatile PAL devices

LOGIC DIAGRAM

0 4 8 12162024283235

1

I0/CLK

2

I1

3

I2

4

I3

DIR

DIR

DIR

DIR

PLC18V8Z

CLK

SP

AC1

AC2

AR

CLK OE

SP

AC1

AC2

AR

CLK OE

SP

AC1

AC2

AR

CLK OE

SP

19

F7

18

F6

17

F5

5

I4

6

I5

7

I6

8

I7

9

I8

SP

AR

226

117

7

I

I

F

F

NOTES:

In the unprogrammed or virgin state:

All cells are in a conductive state.

All AND gate locations are pulled to a logic “0” (Low).

Output polarity is inverting.

6

I

I

I

F

F

335

I

16

15

14

13

12

11

F4

F3

F2

F1

F0

I9/OE

SP00012

AC1

AC2

AR

CELL

CLK OE

SP

AC1

AC2

AR

CLK OE

SP

AC1

AC2

AR

CLK OE

SP

AC1

AC2

AR

CLK OE

SP

AC1

AC2

AR

CLK OE

DIR

DIR

DIR

DIR

009

III

9

I

880

771

662

5

F

F

I

I

I

I

F

F

F

F

Pins 1 and 11 are configured as Inputs 0 and 9, respectively, via the configuration cell. The clock and OE

functions are disabled.

All output macro cells (OMC) are configured as bidirectional I/O, with the outputs disabled via the direction term.

Denotes a programmable cell location.

553

444

4

2

3

I

I

I

I

F

F

F

F

0

1

I

I

F

F

CONFIG.

1997 Aug 08

5

Philips Semiconductors Product specification

Zero standby power

CMOS versatile PAL devices

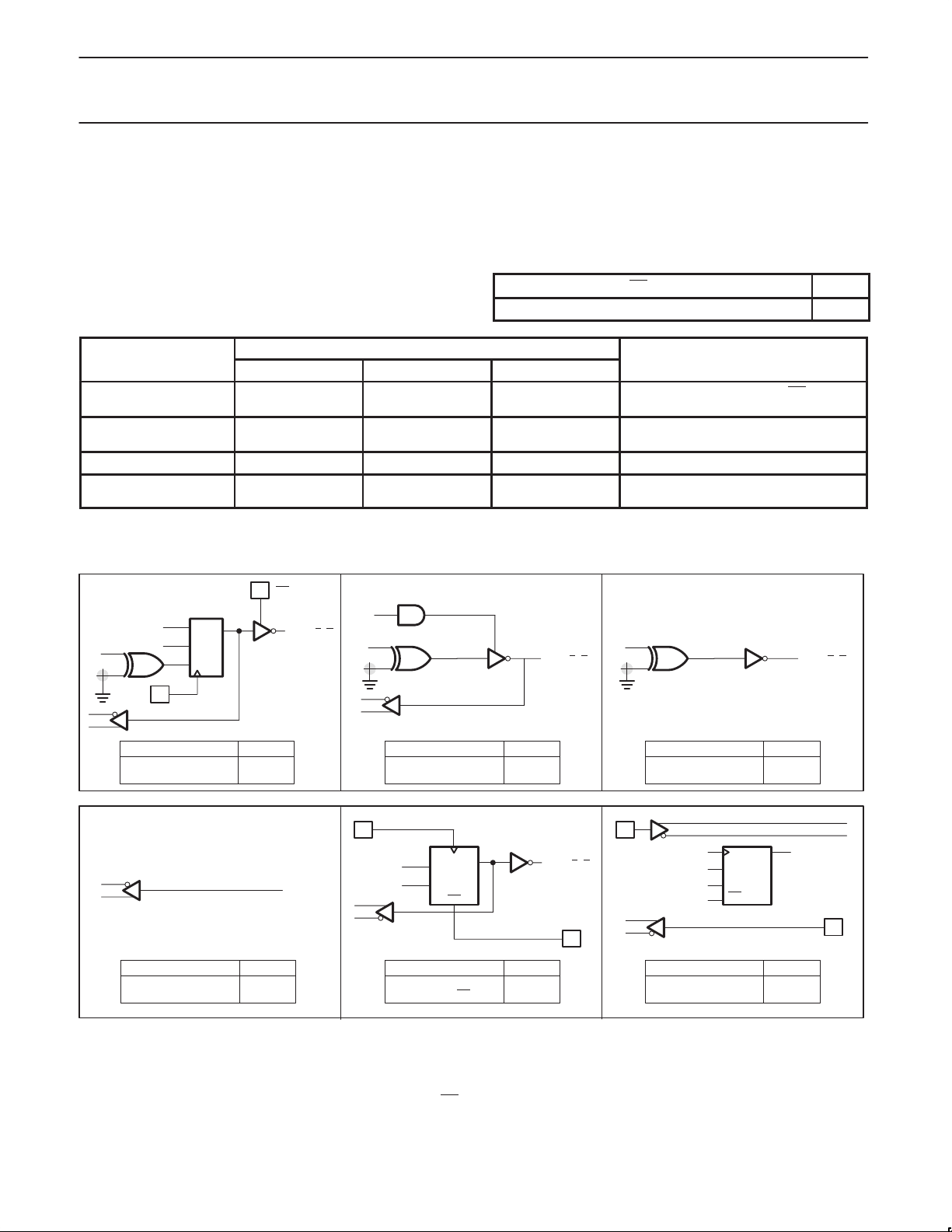

OUTPUT MACRO CELL (OMC)

1

DIRECTION CONTROL TERM

FROM

AND

ARRAY

{

AC1

AC2

n

n

S

X

(n)

OUTPUT

POLARITY

CONTROL

FROM AND

ARRAY

SP

AR

D

Q

CLK

TO ALL OMCs

11

V

01

CC

MUX

00

10

01

OUT

10

MUX

11

00

F

MUX

OE

PLC18V8Z

F

00

10

11

01

NOTE:

Denotes a programmable cell location.

TO ALL OMCs

11

OE

THE OUTPUT MACRO CELL (OMC)

The PLC18V8Z series devices have 8 individually programmable

Output Macro Cells. The 72 AND inputs (or product terms) from the

programmable AND array are connected to the 8 OMCs in groups of

9. Eight of the AND terms are dedicated to logic functions; the ninth

is for asynchronous direction control, which enables/disables the

respective bidirectional I/O pin. Two product terms are dedicated for

the Synchronous Preset and Asynchronous Reset functions.

Each OMC can be independently programmed via 16 architecture

control bits, AC1

each OMC has a programmable output polarity control bit (Xn). By

configuring the pair of architecture control bits according to the

configuration cell table, 4 different configurations may be

implemented. Note that the configuration cell is automatically

programmed based on the OMC configuration.

and AC2n (one pair per macro cell). Similarly,

n

SP00014

DESIGN SECURITY

The PLC18V8Z series devices have a programmable security fuse

that controls the access to the data programmed in the device. By

using this programmable feature, proprietary designs implemented

in the device cannot be copied or retrieved.

1997 Aug 08

6

Philips Semiconductors Product specification

Zero standby power

CMOS versatile PAL devices

CONFIGURATION CELL

A single configuration cell controls the functions of Pins 1 and 11.

Refer to Functional Diagram. When the configuration cell is

programmed, Pin 1 is a dedicated clock and Pin 11 is dedicated for

output enable. When the configuration cell is unprogrammed, Pins 1

and 11 are both dedicated inputs. Note that the output enable for all

registered OMCs is common—from Pin 11 only. Output enable

control of the bidirectional I/O OMCs is provided from the AND array

via the direction product term.

CONTROL CELL CONFIGURATIONS

FUNCTION AC1

1

Registered mode Programmed Programmed Programmed

Bidirectional I/O mode

1

Unprogrammed Unprogrammed Unprogrammed

Fixed input mode Unprogrammed Programmed Unprogrammed Pins 1 and 11 are dedicated inputs.

Fixed output mode Programmed Unprogrammed Unprogrammed

NOTE:

1. This is the virgin state as shipped from the factory.

AC2

N

If any one OMC is configured as registered, the configuration cell

will be automatically configured (via the design software) to ensure

that the clock and output enable functions are enabled on Pins 1

and 11, respectively. If none of the OMCs are registered, the

configuration cell will be programmed such that Pins 1 and 11 are

dedicated inputs. The programming codes are as follows:

Pin 1 = CLK, Pin 11 = OE

Pin 1 and Pin 11 = Input H

CONFIG. CELL COMMENTS

Dedicated clock from Pin 1. OE Control

for all registerd OMCs from Pin 11 only.

Pins 1 and 11 are dedicated inputs.

3-State control from AND array only.

Pins 1 and 11 are dedicated inputs. The

feedback path (via F

PLC18V8Z

) is disabled.

MUX

L

ARCHITECTURE CONTROL—AC1 and AC2

11

OE

DIR

SP

S

AR

1

OMC CONFIGURATION

REGISTERED (D–TYPE)

FIXED INPUT

NOTES:

A factory shipped unprogrammed device is configured such that:

1. This is the initial unprogrammed state. All cells are in a conductive state.

2. All AND gates are pulled to a logic “0” (Low).

3. Output polarity is inverting.

4. Pins 1 and 11 are configured as inputs 0 and 9. The clock and OE

5. All Output Macro Cells (OMCs) are configured as bidirectional I/O, with the outputs disabled via the direction term.

6. This configuration cannot be used if any OMCs are configured as registered (Code = D).

CLK

Q

CODE

D

I

F(D), F

F (I)

(D)

S

OMC CONFIGURATION CODE

BIDIRECTIONAL I/O

(COMBINATORIAL)

1

SP

AR

CONFIGURATION CELLCODEOMC CONFIGURATION

PIN 1 = CLK

PIN 11 = OE

CLK

OE

1

Q

F(B), F (B)

CODE

B

F(D), F (D)

11

L

S

OMC CONFIGURATION

1

FIXED OUTPUT

NC

SP

AR

NC

PIN 1 = INPUT

PIN 11 = INPUT

functions are disabled.

CLK Q

OE

(O)

F(O), F

O

11

CODECONFIGURATION CELLCODE

6

H

SP00015

1997 Aug 08

7

Loading...

Loading...