Philips PDIUSBH1 Service Manual

PDIUSBH11

Universal Serial Bus hub

Preliminary specification 1996 Nov 12

INTEGRATED CIRCUITS

Philips Semiconductors Preliminary specification

PDIUSBH11Universal Serial Bus hub

2

1996 Nov 12

FEATURES

•Complies with the Universal Serial Bus specification Rev. 1.0

•Four downstream ports with per packet connectivity

•Embedded function with two endpoints (control and interrupt)

•Integrated FIFO memory for hub and embedded function

•Automatic protocol handling

•Versatile I

2

C interface

•Compliant with USB Human Interface and Display Device Class

•Single 3.3V supply and SDIP32 package

DESCRIPTION

The Philips Semiconductors Universal Serial Bus (USB) hub is

designed to provide USB expandability in a PC system and

plug-and-play control of the embedded function, for example,

monitor. The PDIUSBH11 is used in a microcontroller based system

and communicates with the system microcontroller over the I

2

C

serial bus.

This modular approach to implementing a hub and embedded

function allows the designer to either use a low cost dedicated

microcontroller or adapt the existing system microcontroller. The

PDIUSBH11 conforms to the USB specification 1.0 and the I

2

C

serial interface specification.

Since the device is a compound USB device (hub function plus

embedded function), the embedded function appears as PORT1 to

the host system. The four expansion ports are numbered 2 through

5.

ORDERING INFORMATION

PACKAGES TEMPERATURE RANGE OUTSIDE NORTH AMERICA NORTH AMERICA PKG. DWG. #

32-pin plastic SO 0°C to +70°C PDIUSBH11 D PDIUSBH11 D SOT287–1

32-pin plastic SDIP 0°C to +70°C PDIUSBH11 NB PDIUSBH11 NB SOT232–1

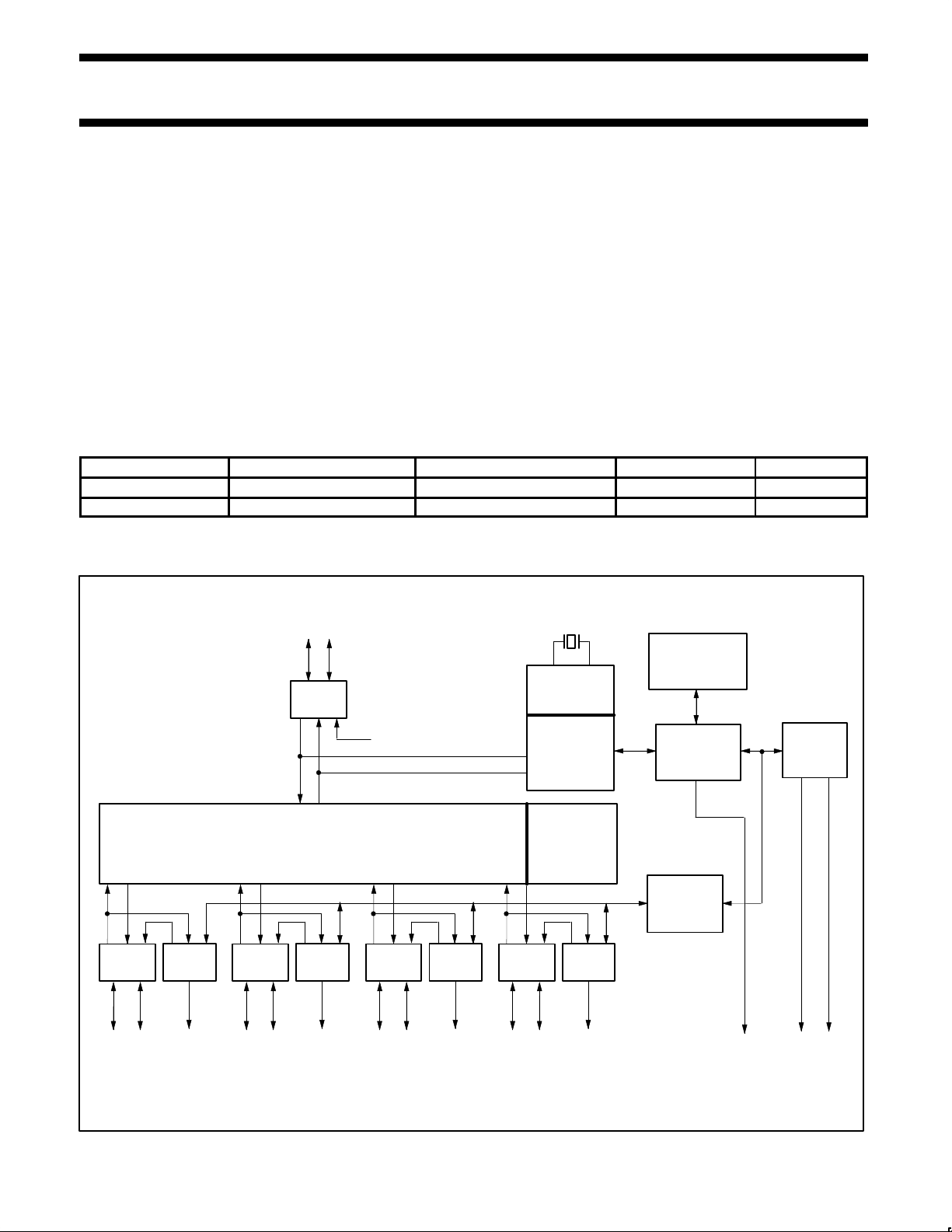

BLOCK DIAGRAM

ANALOG

TX/R

X

PORT

CONTROL

ANALOG

TX/R

X

PORT

CONTROL

ANALOG

TX/R

X

PORT

CONTROL

ANALOG

TX/R

X

PORT

CONTROL

GENERAL

PORT

CONTROLLER

HUB

REPEATER

END OF

FRAME

TIMERS

ANALOG

T

X/RX

PHILIPS

SIE

INTEGRATED

RAM

BIT CLOCK

RECOVERY

MEMORY

MANAGEMENT

UNIT

I

2

C

SLAVE

INTERFACE

48 MHz

FULL SPEED

INTERRUPT SDA SCL

LED

ENABLE

D–D+

LED

ENABLE

D–D+

LED

ENABLE

D–D+

LED

ENABLE

D–D+

DOWNSTREAM

PORT 2

DOWNSTREAM

PORT 3

DOWNSTREAM

PORT 4

DOWNSTREAM

PORT 5

D+

D–

UPSTREAM

PORT

SV00226

NOTE:

1. This is a conceptual block diagram and does not include each individual signal.

Philips Semiconductors Preliminary specification

PDIUSBH11Universal Serial Bus hub

1996 Nov 12

3

Analog Transceivers

These transceivers interface directly to the USB cables through

some termination resistors. They are capable of transmitting and

receiving serial data at both “full speed” (12 Mbit/s) and “low speed”

(1.5 Mbit/s) data rates.

Hub Repeater

The hub repeater is responsible for managing connectivity on a per

packet basis. It implements packet signaling connectivity and

resume connectivity.

Low speed devices can be connected to downstream ports since the

repeater will not propagate upstream packets to downstream ports,

to which low speed devices are connected, unless they are

preceded by a PREAMBLE PID.

End of Frame Timers

This block contains the specified EOF1 and EOF2 timers which are

used to detect loss–of–activity and babble error conditions in the

hub repeater. The timers also maintain the low–speed keep–alive

strobe which is sent at the beginning of a frame.

General and Individual Port Controller

The general and individual port controllers together provide status

and control of individual downstream ports. Via the I

2

C–interface a

microcontroller can access the downstream ports and request or

change the status of each individual port.

Any change in the status or settings of the individual port will result

in an interrupt request. Via an interrupt register, the servicing

microcontroller can look up the downstream port which generated

the interrupt and request its new status. Any port status change can

then be reported to the host via the hub status change (interrupt)

endpoint.

Bit Clock Recovery

The bit clock recovery circuit recovers the clock from the incoming

USB data stream using (4X) over–sampling principle. It is able to

track jitter and frequency drift specified by the USB spec.

Philips Serial Interface Engine (PSIE)

The Philips SIE implements the full USB protocol layer. It is

completely hardwired for speed and needs no firmware intervention.

The functions of this block include: synchronisation pattern

recognition, parallel / serial conversion, bit stuffing / destuffing, CRC

checking / generation, PID verification / generation, address

recognition, handshake evaluation / generation.

Memory Management Unit (MMU) and Integrated RAM

The MMU and the integrated RAM is used to handle the large

difference in data–rate between USB, running in burst of 12 Mbit/s

and the I

2

C interface to the microcontroller, running at 100 kbit/s.

This allows the microcontroller to read and write USB packets at its

own (low) speed through I

2

C.

I

2

C Slave Interface

This block implements the necessary I

2

C interface protocol. A slave

I

2

C allows for simple micro–coding. An interrupt is used to alert the

microcontroller whenever the PDIUSBH11 needs attention. As a

slave I

2

C device, the PDIUSBH11 I2C clock: SCL is an input and is

controlled by the microcontroller.

Philips Semiconductors Preliminary specification

PDIUSBH11Universal Serial Bus hub

1996 Nov 12

4

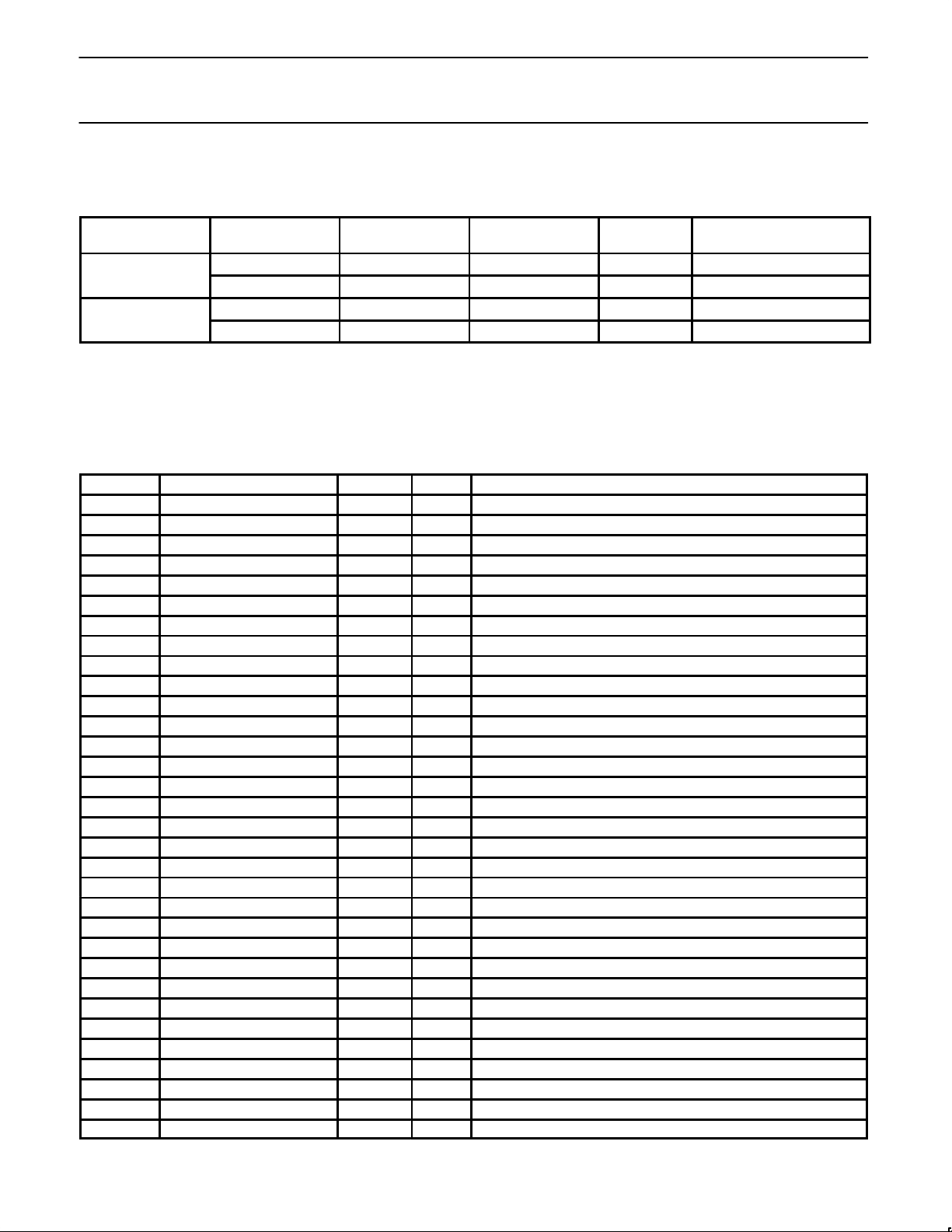

ENDPOINT DESCRIPTIONS

The following table summarizes the endpoints supported by the PDIUSBH11.

FUNCTION

ENDPOINT

NUMBER

ENDPOINT TYPE TRANSFER TYPE DIRECTION

MAXIMUM PACKET SIZE

(bytes)

0 Default Control IN, OUT 8

HUB

1 Status change Interrupt IN 1

0 Default Control IN, OUT 8

1 Interrupt Interrupt IN 8

PIN DESCRIPTION

The PDIUSBH11 has two modes of operation. The first mode

(Mode 0) enables the pins DNx_EN_N to power a LED indicating

the port is enabled. The second mode (Mode 1) utilizes the LED

enable pins as per port overcurrent condition pins.

The voltage level at power up on the TEST1 and TEST2 pins

determine the PDIUSBH11 mode of operation. When both of the

pins are connected to Ground, Mode 0 is enabled. When pins

TEST1 and TEST2 are connected to Vcc, Mode 1 is enabled. Note

that in Mode 1 the pin DN2_EN_N remains an LED enable pin. Pin

TEST3 should always be connected to Ground at all times.

PIN DESCRIPTION (MODE 0)

PIN NO PIN SYMBOL I/O DRIVE NAME AND FUNCTION

1 TEST1 I Connect to Ground

2 TEST2 I Connect to Ground

3 TEST3 I Connect to Ground

4 RESET_N I ST Power-on reset

5 GND POWER Ground reference

6 XTAL1 I Crystal connection 1 (48MHz)

7 XTAL2 O Crystal connection 2 (48MHz)

8 CLK12MHZ O 2mA 12MHz output clock for external devices

9 V

CC

POWER Voltage supply 3.3V 0.3V

10 OCURRENT_N I ST Over-current notice to the device

11 SWITCH_N O OD8 Enables power to downstream ports

12 SUSPEND O 4mA Device is in suspended state

13 DN2_EN_N O OD8 Downstream port 2 LED enable indicator

14 DN3_EN_N O OD8 Downstream port 3 LED enable indicator

15 DN4_EN_N O OD8 Downstream port 4 LED enable indicator

16 DN5_EN_N O OD8 Downstream port 5 LED enable indicator

17 INT_N O OD4 Connect to microcontroller interrupt

18 SDA I/O OD4 I2C bi-directional data

19 SCL I/O OD4 I2C bit-clock

20 GND POWER Ground reference

21 DN5_DP AI/O Downstream port 5 D+ connection

22 DN5_DM AI/O Downstream port 5 D– connection

23 DN4_DP AI/O Downstream port 4 D+ connection

24 DN4_DM AI/O Downstream port 4 D– connection

25 DN3_DP AI/O Downstream port 3 D+ connection

26 DN3_DM AI/O Downstream port 3 D– connection

27 DN2_DP AI/O Downstream port 2 D+ connection

28 DN2_DM AI/O Downstream port 2 D– connection

29 AGND POWER Analog Ground reference

30 AV

CC

POWER Analog voltage supply 3.3V 0.3V

31 UP_DP AI/O Upstream D+ connection

32 UP_DM AI/O Upstream D– connection

EMBEDDED

Philips Semiconductors Preliminary specification

PDIUSBH11Universal Serial Bus hub

1996 Nov 12

5

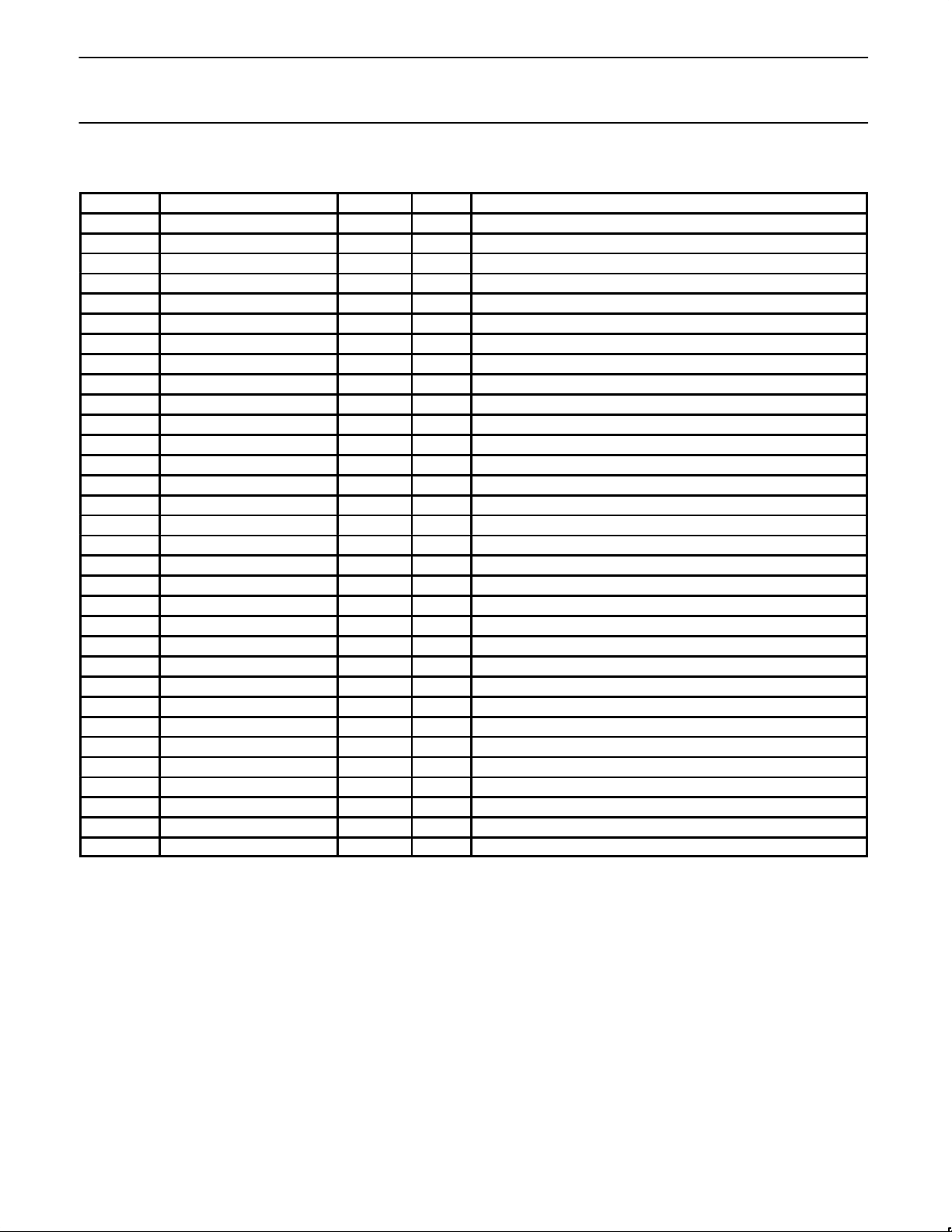

PIN DESCRIPTION (MODE 1)

PIN NO PIN SYMBOL I/O DRIVE NAME AND FUNCTION

1 TEST1 I Connect to V

CC

2 TEST2 I Connect to V

CC

3 TEST3 I Connect to Ground

4 RESET_N I ST Power-on reset

5 GND POWER Ground reference

6 XTAL1 I Crystal connection 1 (48MHz)

7 XTAL2 O Crystal connection 2 (48MHz)

8 CLK12MHZ O 2mA 12MHz output clock for external devices

9 V

CC

POWER Voltage supply 3.3V 0.3V

10 OCURRENT2_N I ST Downstream port 2 over-current notice

11 SWITCH_N O OD8 Enables power to downstream ports

12 SUSPEND O 4mA Device is in suspended state

13 DN2_EN_N O OD8 Downstream port 2 LED enable indicator

14 OCURRENT3_N I ST Downstream port 3 over-current notice

15 OCURRENT4_N I ST Downstream port 4 over-current notice

16 OCURRENT5_N I ST Downstream port 5 over-current notice

17 INT_N O OD4 Connect to microcontroller interrupt

18 SDA I/O OD4 I2C bi-directional data

19 SCL I/O OD4 I2C bit-clock

20 GND POWER Ground reference

21 DN5_DP AI/O Downstream port 5 D+ connection

22 DN5_DM AI/O Downstream port 5 D– connection

23 DN4_DP AI/O Downstream port 4 D+ connection

24 DN4_DM AI/O Downstream port 4 D– connection

25 DN3_DP AI/O Downstream port 3 D+ connection

26 DN3_DM AI/O Downstream port 3 D– connection

27 DN2_DP AI/O Downstream port 2 D+ connection

28 DN2_DM AI/O Downstream port 2 D– connection

29 AGND POWER Analog Ground reference

30 AV

CC

POWER Analog voltage supply 3.3V 0.3V

31 UP_DP AI/O Upstream D+ connection

32 UP_DM AI/O Upstream D– connection

NOTES:

1. Signals ending in _N indicate active low signals.

ST: Schmitt Trigger

OD4, OD8: Open Drain with 4 or 8 mA drive

AI/O: Analog I/O

Loading...

Loading...