Philips pdi1394p11 DATASHEETS

INTEGRATED CIRCUITS

PDI1394P11

3-port physical layer interface

Product specification

Supersedes data of 1998 Sep 24

1999 Apr 09

Philips Semiconductors Product specification

PDI1394P1 13-port physical layer interface

1.0 FEA TURES

•3 cable interface ports

•Supports 100Mb/s and 200Mb/s transfers

•Interfaces to any 1394 standard Link Layer Controller

•5V tolerant I/Os with Bus Holders

•Single 3.3V supply voltage

•Arbitrated (short) Bus Reset (1394a feature)

2.0 DESCRIPTION

The Philips Semiconductors PDI1394P11 is an IEEE1394-1995

compliant Physical Layer interface. The PDI1394P11 provides the

analog physical layer functions needed to implement a three port

node in a cable-based IEEE 1394–1995 network. Additionally, the

device manages bus initialization and arbitration cycles, as well as

transmission and reception of data bits. The Link Layer Controller

interface is compatible with both 3V and 5V Link Controllers. While

providing a maximum transmission data rate of 200 Mb/s, the

PDI1394P1 1 is compatible with current 100 Mb/s Physical Layer

ICs. The PDI1394P11 is available in the LQFP64 package.

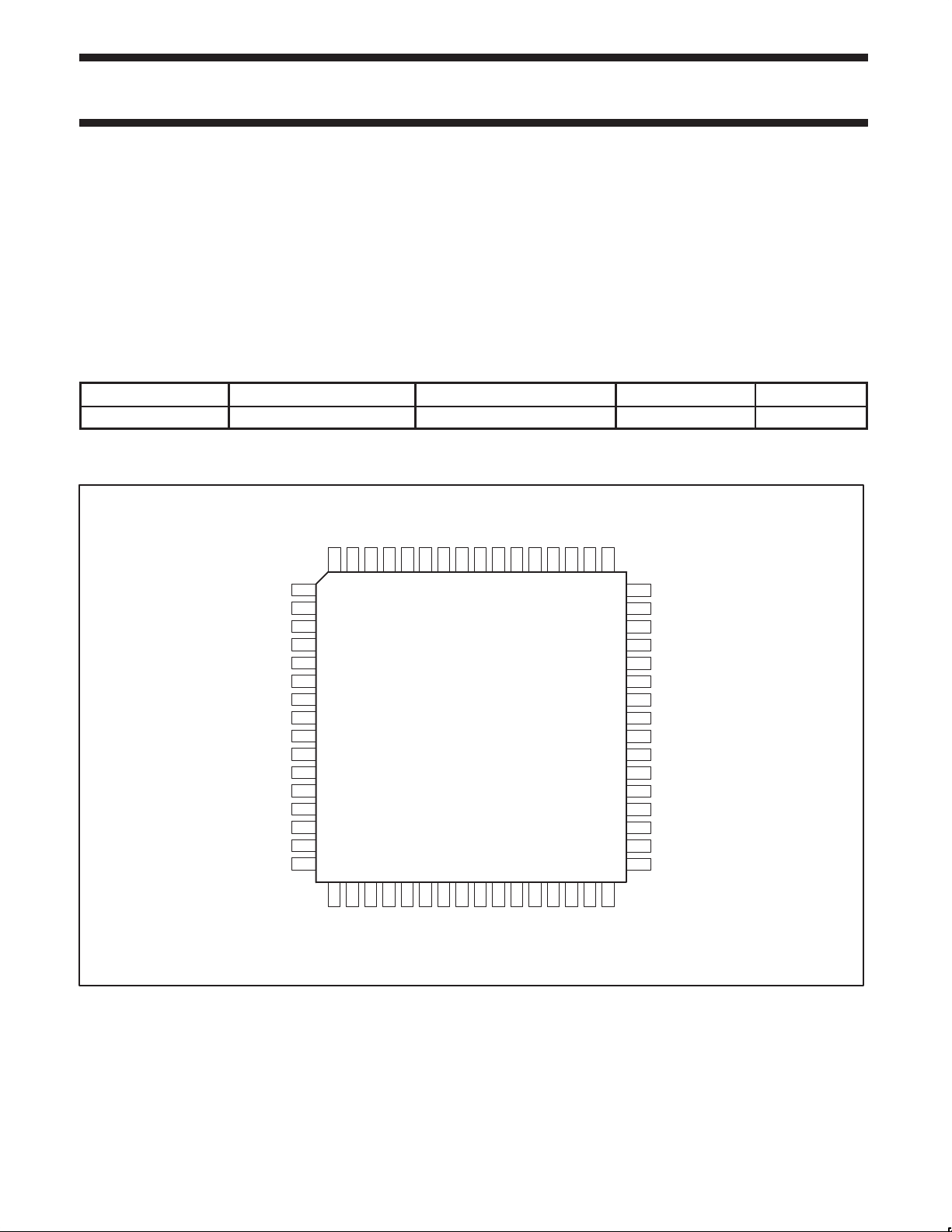

3.0 ORDERING INFORMATION

PACKAGE TEMPERATURE RANGE OUTSIDE NORTH AMERICA NORTH AMERICA PKG. DWG. #

64-pin plastic LQFP 0°C to +70°C PDI1394P11 BD PDI1394P11 BD SOT314-2

4.0 PIN CONFIGURATION

PLLGND

PLLGND

AVDD

AGND

AGND

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

TPBIAS3

TPBIAS2

TPBIAS1

TPA1+

TPA1–

TPB1+

TPB1–

AGND

TPA2+

TPA2–

TPB2+

TPB2–

TPA3+

TPA3–

TPB3+

TPB3–

RESET–

LPS

LREQ

DVDD

DVDD

DVDD

PD

DGND

SYSCLK

DGND

CTL0

CTL1

DGND

DGND

ISO–

AGNDR1R0

646362616059585756555453525150

1

2

3

4

5

6

7

8

9

10

11

12

13

D0

14

D1

15

D2

16

D3

XO

XI

PLLVDD

PDI1394P11

AVDD

FILTER

171819202122232425262728293031

PC2

CPS

AVDD

DVDD

DGND

DVDD

TESTM2

TESTM1

DGND

1999 Apr 09 853–2150 21222

AVDD

AGND

2

PC1

C/LKON

PC0

CNA

32

AGND

SV00229

Philips Semiconductors Product specification

PDI1394P113-port physical layer interface

5.0 PIN DESCRIPTION

PIN NUMBER PIN SYMBOL I/O NAME AND FUNCTION

1 RESET– I* Power up reset, active LOW

2 LPS I* Link Layer Controller (LLC) power status

3 LREQ I* Link request from controller

4 DVDD I* Should be connected to the LLC VDD supply when a 5V LLC is connected to the

5, 6, 19, 20 DVDDD I Digital circuit power

7 PD I* Device power down input

8, 10, 17, 18, 63, 64 DGND – Digital circuit ground

9 SYSCLK O* 49.152 MHz clock to link controller

11, 12 CTL[0:1] I/O* Link interface bi-directional control signals

13, 14, 15, 16 D[0:3] I/O* Link interface bi-directional data signals

22, 21 TESTM[1:2] I* Test/Mode Control pins

23 CPS I Cable power status

24, 25, 51, 55 AVDD – Analog circuit power

26, 32, 41, 49, 50, 61 AGND – Analog circuit ground

27 C/LKON I/O* Bus/Isochronous Resource Manager capable input, or LINK-ON signal output

30, 29, 28 PC[0:2] I* Power class bits 0 through 2 inputs

31 CNA O* Cable Not Active output

36, 40, 45 TPA[1:3]+ I/O Port n cable pair A, positive signal

35, 39, 44 TPA[1:3]– I/O Port n cable pair A, negative signal

34, 38, 43 TPB[1:3]+ I/O Port n cable pair B, positive signal

33, 37, 42 TPB[1:3]– I/O Port n cable pair B, negative signal

46, 47, 48 TPBIAS[1:3] O Cable termination voltage supplies

52, 53 PLLGND – PLL circuit ground

54 FILTER I/O PLL external filter capacitor

56 XI I Crystal oscillator connection

57 XO O Crystal oscillator connection

58 PLLVDD – PLL circuit power

59, 60 R[0:1] – External current setting resistor

62 ISO– I* Link interface isolation status input

NOTE:

* Indicates 5V tolerant structure.

Phy, and should be connected to the Phy DVDD when a 3V LLC is used.

11 =1394–1995 mode

10 = 1394a mode

00/01 = Reserved

1999 Apr 09

3

Philips Semiconductors Product specification

PDI1394P113-port physical layer interface

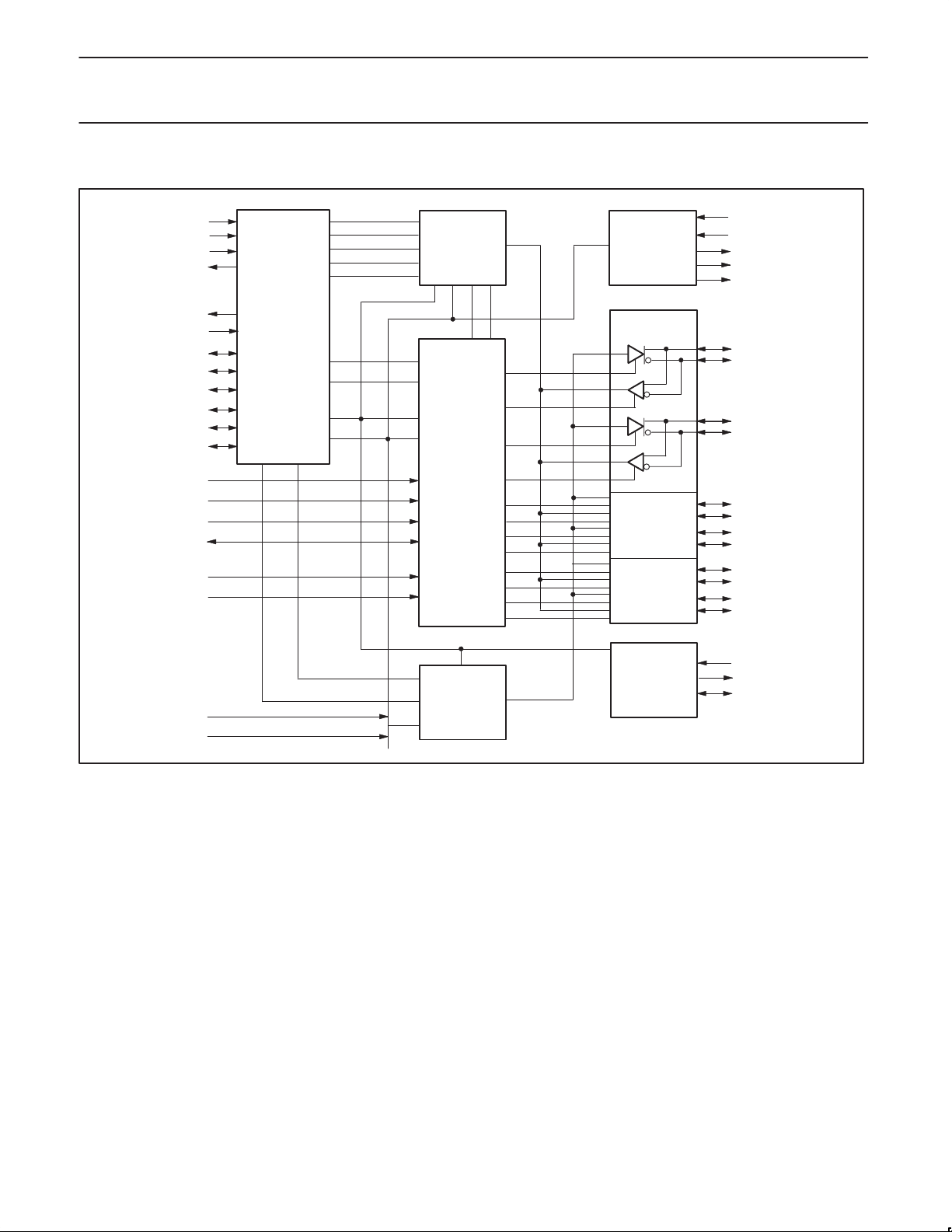

6.0 BLOCK DIAGRAM

CPS

LPS

ISO–

CNA

SYSCLK

LREQ

CTL0

CTL1

PC0

PC1

PC2

C/LKON

TESTM1

TESTM2

RESET–

D0

D1

D2

D3

PD

LINK

INTERFACE

RECEIVED

DATA

DECODER/

TIMER

ARBITRATION

AND CONTROL

STATE

MACHINE

LOGIC

TRANSMIT

DATA

ENCODER

BIAS

VOLTAGE AND

CURRENT

GENERATOR

PORT 1

PORT 2

PORT 3

CRYSTAL

OSCILLATOR

PLL SYSTEM

& TRANSMIT

CLOCK

GENERATOR

R0

R1

TPBIAS1

TPBIAS2

TPBIAS3

TPA1+

TPA1–

TPB1+

TPB1–

TPA2+

TPA2–

TPB2+

TPB2–

TPA3+

TPA3–

TPB3+

TPB3–

XI

XO

FILTER

SV00228

7.0 FUNCTIONAL SPECIFICA TION

The PDI1394P11 is an IEEE1394–1995 High Performance Serial

Bus Specification compliant physical layer interface device. It

provides an interface between an attached link layer controller and

three 1394 cable interface ports. In addition to the interface function,

the PDI1394P11 performs bus initialization and arbitration functions

as well as monitoring line conditions and connection status.

7.1 Clocking

The PDI1394P1 1 utilizes a stable internal reference clock of

196.608 MHz. The reference clock is generated using an external

24.576 MHz crystal and an internal Phase Locked Loop (PLL). The

PLL clock is divided down to 49.152 MHz and 98.304 MHz clock

signals. The 49.152 MHz clock is used for internal logic and

provided as an output to clock a link layer controller. The 196.608

MHz and 98.304 MHz clocks are used for synchronization of the

transmitted strobe and data information.

7.2 Port Interfaces

The PDI1394P1 1 provides the transceiver functions needed to

implement a three port node in a cable-based 1394 network. Each

cable port incorporates two differential line transceivers. In addition

to transmission and reception of packet data, the line transceivers

1999 Apr 09

monitor conditions on the cable to determine connection status, data

speed, and bus arbitration states.

The PDI1394P1 1 receives data to be transmitted over the bus from

two or four parallel data paths to the Link Controller, D[0:3]. These

data paths are latched and synchronized with the 49.152 MHz clock.

The parallel bit paths are combined serially, encoded and

transmitted at either 98.304 Mb/s or 196.608 Mb/s, depending

whether the transaction is a 100 Mb/s or 200 Mb/s transfer,

respectively. The transmitted data is encoded as data-strobe

information, with the data information being transmitted on the TPB

cable pairs and the strobe information transmitted on the TPA cable

pairs.

During packet reception the TPA and TPB transmitters of the

receiving cable port are disabled, and the receivers for that port are

enabled. The encoded data information is received on the TPA cable

pair and the strobe information is received on the TPB cable pair.

The combination of the data and strobe signals is decoded to

recover the receive clock signal and the serial data stream. The

serial data stream is converted to two or four parallel bit streams,

resynchronized to the internal 49.152 MHz clock and sent to the

4

Philips Semiconductors Product specification

SYMBOL

PARAMETER

CONDITION

UNIT

V

Common mode voltage

V

V

Common mode voltage

V

Receive input jitter

Receive input ske

IOL/I

Output current, IOL/I

mA

PDI1394P113-port physical layer interface

associated link controller. The received data is also transmitted out

the other active cable ports.

The cable status, bus initialization and arbitration states are

monitored through the cable interface using differential comparators.

The outputs of these comparators are used by internal logic to

determine cable and arbitration status. The TPA channel monitors

the incoming cable common-mode voltage value during arbitration to

determine the speed of the next packet transmission. The TPB

channel monitors the incoming cable common-mode voltage for the

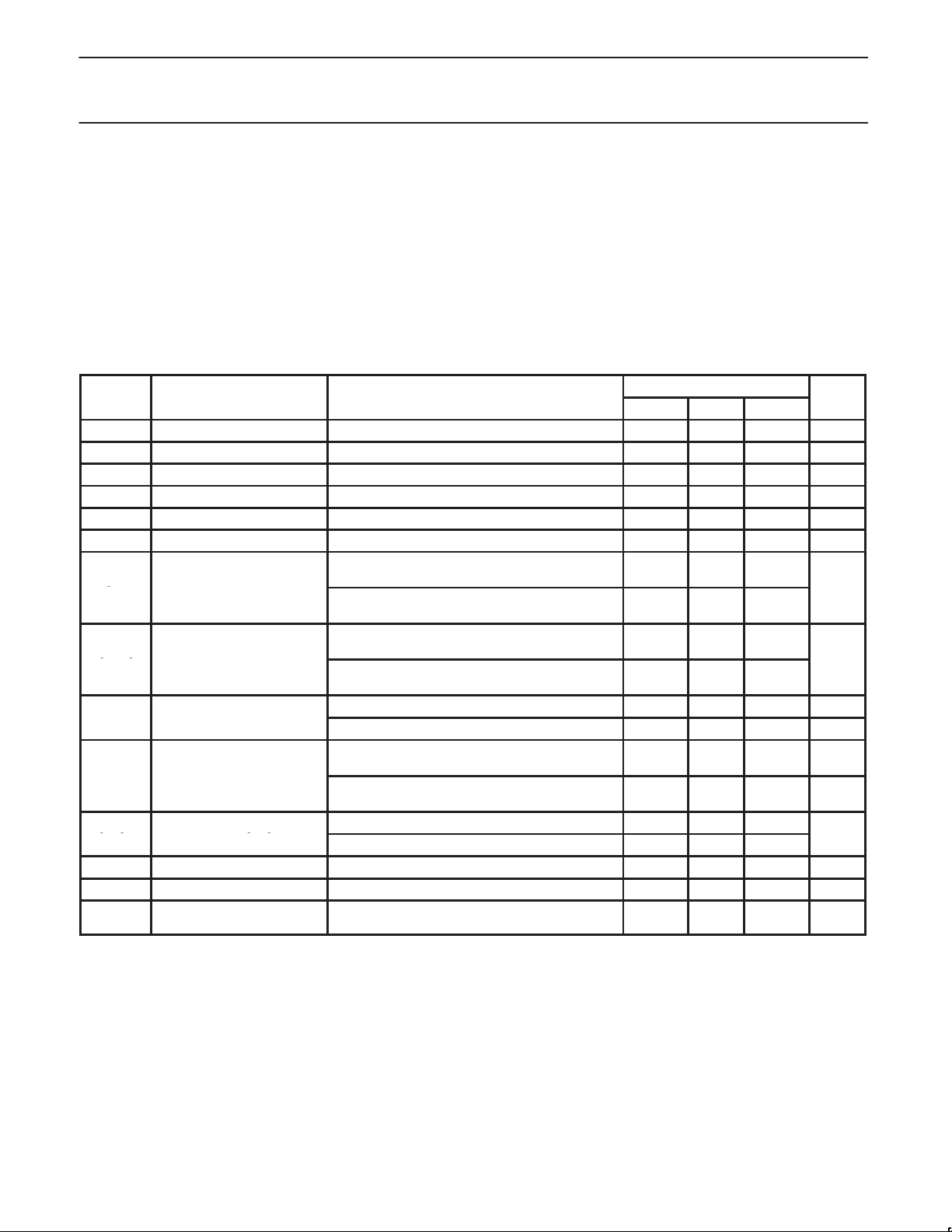

8.0 RECOMMENDED OPERATING CONDITIONS

V

V

V

V

ID–100

V

ID–200

V

ID–ARB

IC–100

IC–200SP

I

f

XTAL

T

amb

DC supply voltage Source/non-source power node 3.0 3.3 3.6 V

DD

High level input voltage CMOS inputs 2.0 5.5 V

IH

Low level input voltage CMOS inputs 0.8 V

IL

Differential input voltage Cable inputs, 100Mbit operation 142 260 mV

Differential input voltage Cable inputs, 200Mbit operation 132 260 mV

Differential input voltage Cable inputs, during arbitration 171 262 mV

TPB cable inputs, 100Mbit or speed signaling OFF,

source power node

TPB cable inputs, 100Mbit or speed signaling OFF,

non–source power node

TPB cable inputs, 200Mbit or speed signaling,

source power node

TPB cable inputs, 200Mbit or speed signaling,

non–source power node

p

TPA, TPB cable inputs, 100Mbit operation ±1.08 ns

TPA, TPB cable inputs, 200Mbit operation ±0.5 ns

Between TPA and TPB cable inputs, 100Mbit

p

w

operation

Between TPA and TPB cable inputs, 200Mbit

operation

OH

O

p

OH

Output current TPBIAS outputs –3 1.3 mA

SYSCLK –16 16

Control, Data, CNA, C/LKON –12 12

Crystal frequency Parallel resonant fundamental mode crystal 24.5735 24.576 24.5785 MHz

Operating ambient

temperature range in free air

presence of the remotely supplied twisted-pair bias voltage,

indicating the cable connection status.

The PDI1394P1 1 provides a nominal 1.85 V for driver load

termination. This bias voltage, when seen through a cable by a

remote receiver, is used to sense the presence of an active

connection. The value of this bias voltage has been chosen to allow

inter-operability between transceiver chips operating from either 5 V

nominal supplies, or 3.3 V nominal supplies. This bias voltage

source should be stabilized by using an external filter capacitor.

LIMITS

MIN TYP MAX

1.165 2.515

1.165 2.015

0.935 2.515

0.935 2.015

±0.8 ns

±0.55 ns

0 +70 °C

1999 Apr 09

5

Philips Semiconductors Product specification

SYMBOL

PARAMETER

CONDITION

UNIT

SYMBOL

PARAMETER

TEST CONDITION

UNIT

SYMBOL

PARAMETER

TEST CONDITION

UNIT

ZIDDifferential input impedance

Driver disabled

ZICCommon mode input impedance

Driver disabled

PDI1394P113-port physical layer interface

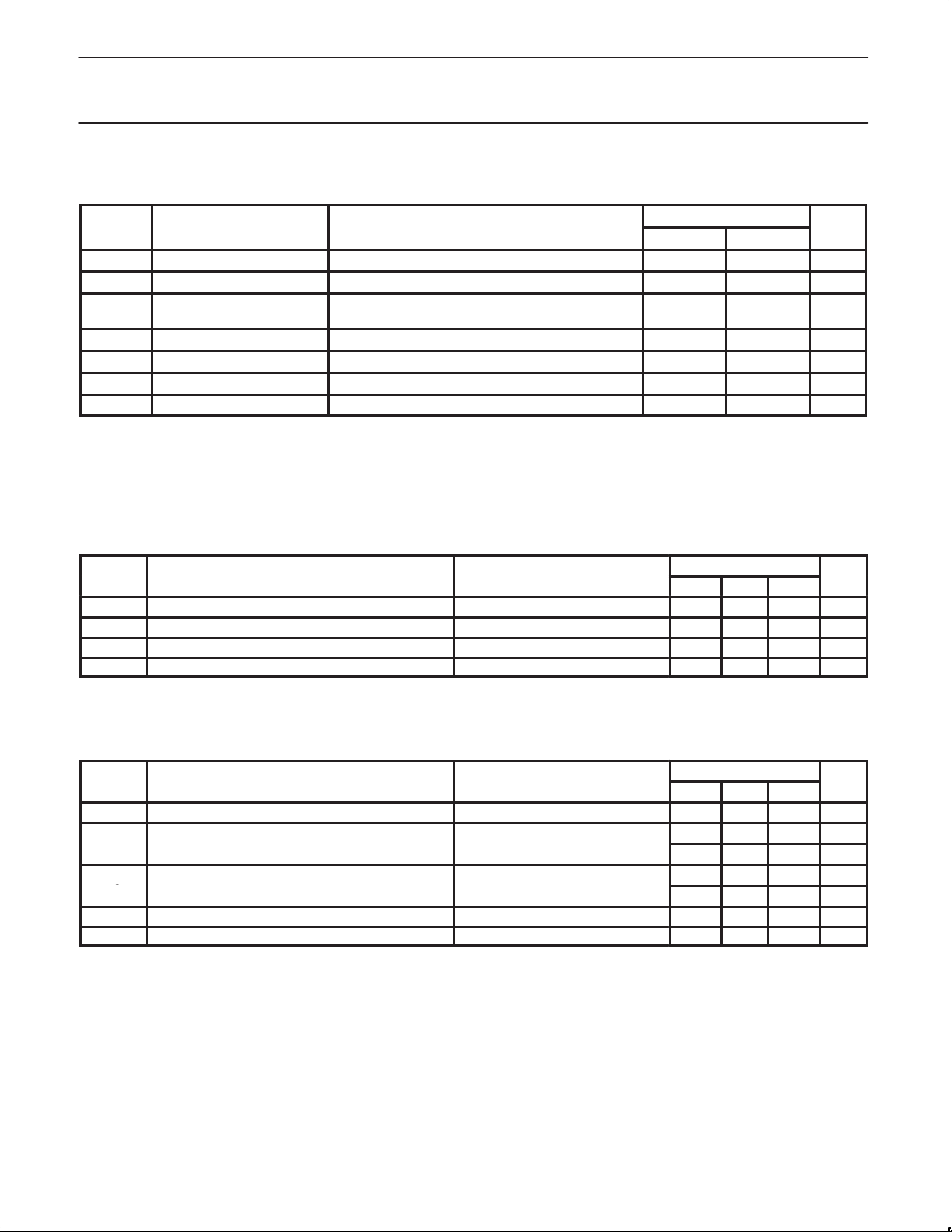

9.0 ABSOLUTE MAXIMUM RATINGS

1, 2

In accordance with the Absolute Maximum Rating System (IEC 134). Voltages are referenced to GND (ground = 0V).

LIMITS

MIN MAX

V

V

V

V

I

I

OK

T

DC supply voltage –0.3 4.6 V

DD

DC input voltage

I

DC input voltage

I,5t

DC output voltage

O

DC input diode current VI < 0 – –50 mA

IK

DC output diode current VO < 0 or VO > V

Storage temperature range –65 +150 °C

stg

3

3

Inputs CPS, TPAn, TPBn, FILTER, XI –0.5 VDD+0.5 V

5V tolerant digital inputs RESET–, LPS, LREQ, PD,

CTL[0:1], D[0:3], TESTM[2:1], C/LKON, PC[0:2], ISO–

–0.5 5.5 V

–0.5 VDD+0.5 V

DD

– ±50 mA

NOTES:

1. Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the

device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to

absolute-maximum-rated conditions for extended periods may affect device reliability .

2. The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction

temperatures which are detrimental to reliability. The maximum junction temperature of this integrated circuit should not exceed 150°C.

3. The input and output voltage ratings may be exceeded if the input and output clamp current ratings are observed.

10.0 CABLE DRIVER

LIMITS

MIN TYP MAX

V

I

O(diff)

I

V

OFF

NOTES:

1. Limits defined as algebraic sum of TPA+ and TPA– driver currents. Limits also apply to TPB+ and TPB– algebraic sum of driver currents.

2. Limits defined as one half of the algebraic sum of currents flowing into TPB+ and TPB–.

Differential output voltage

OD

56 load

Difference current, TPA+, TPA–, TPB+, TPB– Driver enabled, speed signaling OFF –1.05

Common mode speed signaling current, TPB+, TPB– 200Mbit speed signaling enabled +2.53

SP

172 265 mV

1

2

OFF state common mode voltage Drivers disabled 20 mV

1

1.05

mA

+4.842mA

11.0 CABLE RECEIVER

I

IC

V

TH

V

TH

1999 Apr 09

LIMITS

MIN TYP MAX

Common mode input current Driver disabled –20 20 µA

p

p

p

p

15

20 kΩ

24 pF

kΩ

6 pF

Receiver input threshold voltage –60 60 mV

Cable bias detect threshold, TPBn cable inputs Driver disabled 0.6 1.0 V

6

Loading...

Loading...