PCK2011

Direct RAMbus Clock Generator

Preliminary specification 1999 Jan 19

INTEGRATED CIRCUITS

Philips Semiconductors Preliminary specification

PCK201 1Direct Rambus Clock Generator

2

1999 Jan 19

Overview

The Direct Rambus Clock Generator (DRCG) provides the Channel

clock signals for a Direct Rambus memory subsystem. It includes

signals to synchronize the Direct Rambus Channel clock to an

external system clock. Contained in a 24-pin SSOP package, the

DRCG provides an off-the-shelf solution for a broad range of Direct

Rambus memory applications.

Features

•High Speed Clock Support

Provides a 400MHz differential clock source for Direct Rambus

memory systems for an 800MHz data transfer rate.

• Synchronization Flexibility

The DRCG includes signals to synchronize the clock domains of

the Rambus Channel with an external system or processor

clock.

• Power Management Support

The DRCG is able to turn off the Rambus Channel clock to

minimize power for mobile and other power-sensitive applications:

- In the “clock off” mode, the DRCG remains on while the output

is disabled, allowing fast transitions between the clock-off and

clock-on states. This mode could be used in conjunction with

the Nap mode of the RDRAMs and Rambus ASIC Cell (RAC).

- In the “power down” mode, the DRCG is completely powered

down for minimum power dissipation. This mode is used in

conjunction with the power down modes of the RDRAMs and

RAC.

•Supports Independent Channel Clocking

The DRCG supports systems that do not require synchronization

of the Rambus clock to another system clock.

•Works with Philips PCK2010 to support Intel CK98 Clock

Synthesizer/Driver specification.

PIN CONFIGURATION

1

2

3

4

5

6

7

8

9

10

11

12 13

14

15

16

17

18

19

20

21

22

23

24

VDDLR

S0

REFCLK S1

VDDP VDDO

GNDP GNDO

GNDl CLK

PCLKM N/C

SYNCLKN CLKB

GNDC

VDDO

VDDC

GNDO

VDDIPD MULT0

STOPB MULT1

S2

SW00289

PWRDNB

Related Documentation

Direct Rambus RAC Overview

Direct Rambus Memory Controller Guide

Pin-outs

The DRCG is packaged in a 24-pin 150 mil SSOP. The pin

configuration shows the preliminary pin-out. Table 1 describes the

function and connection of each pin.

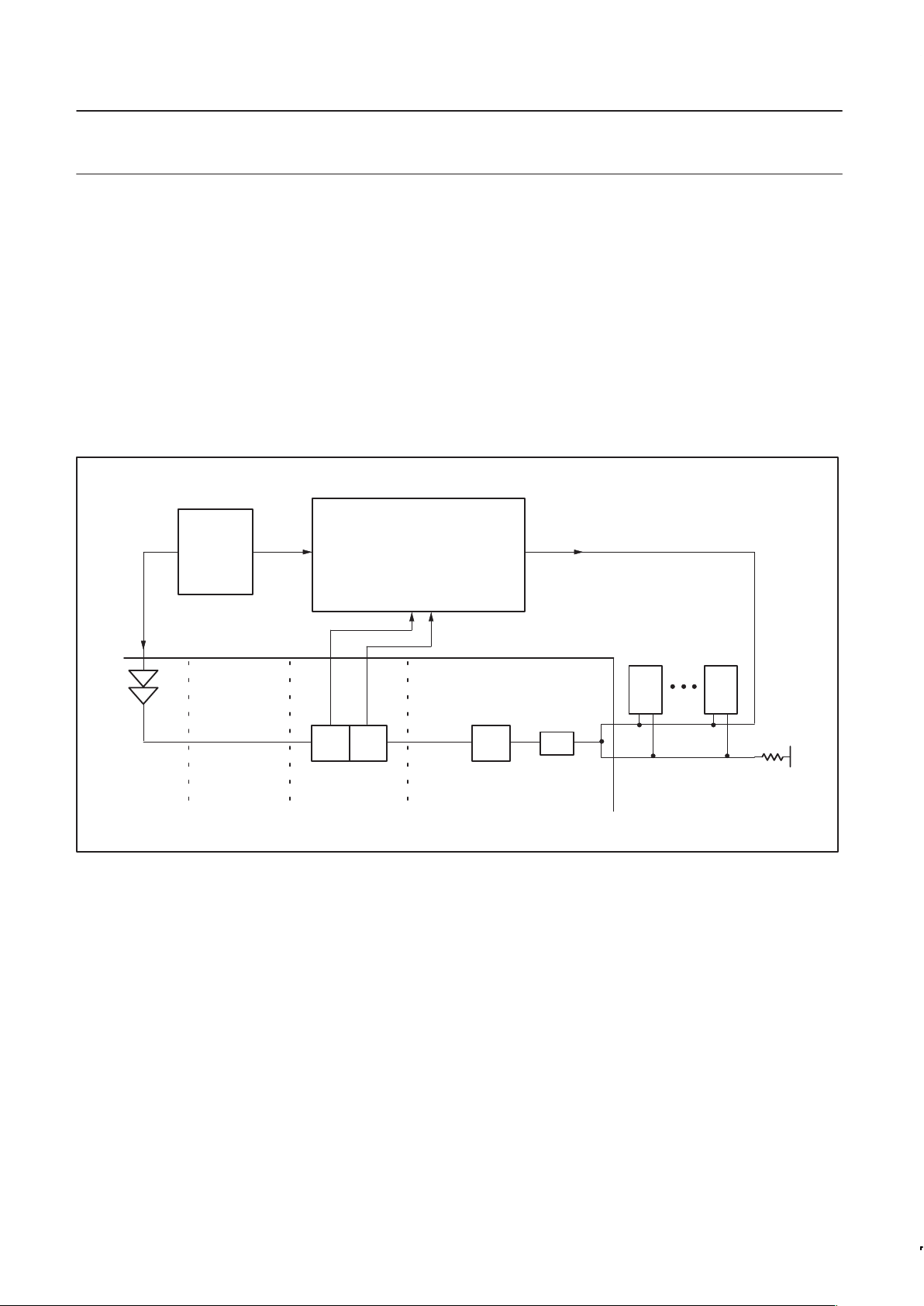

Example System Clock Configuration

Figure 2 shows the clocking configuration for an example Direct

Rambus subsystem. The configuration shows the interconnection of

the system clock source, the Direct Rambus Clock Generator

(DRCG), and the clock signals of a memory controller ASIC. The

ASIC contains the RAC, the Rambus Memory Controller protocol

engine (RMC), and logic to support synchronizing the Channel clock

with the controller clock. (This diagram represents the differential

clocks as a single Busclk wire.)

ORDERING INFORMATION

PACKAGES TEMPERATURE RANGE OUTSIDE NORTH AMERICA NORTH AMERICA DRAWING NUMBER

24-Pin Plastic SSOP 0°C to +70°C PCK2011 DL PCK2011 DL SOT340-1

Philips Semiconductors Preliminary specification

PCK201 1Direct Rambus Clock Generator

1999 Jan 19

3

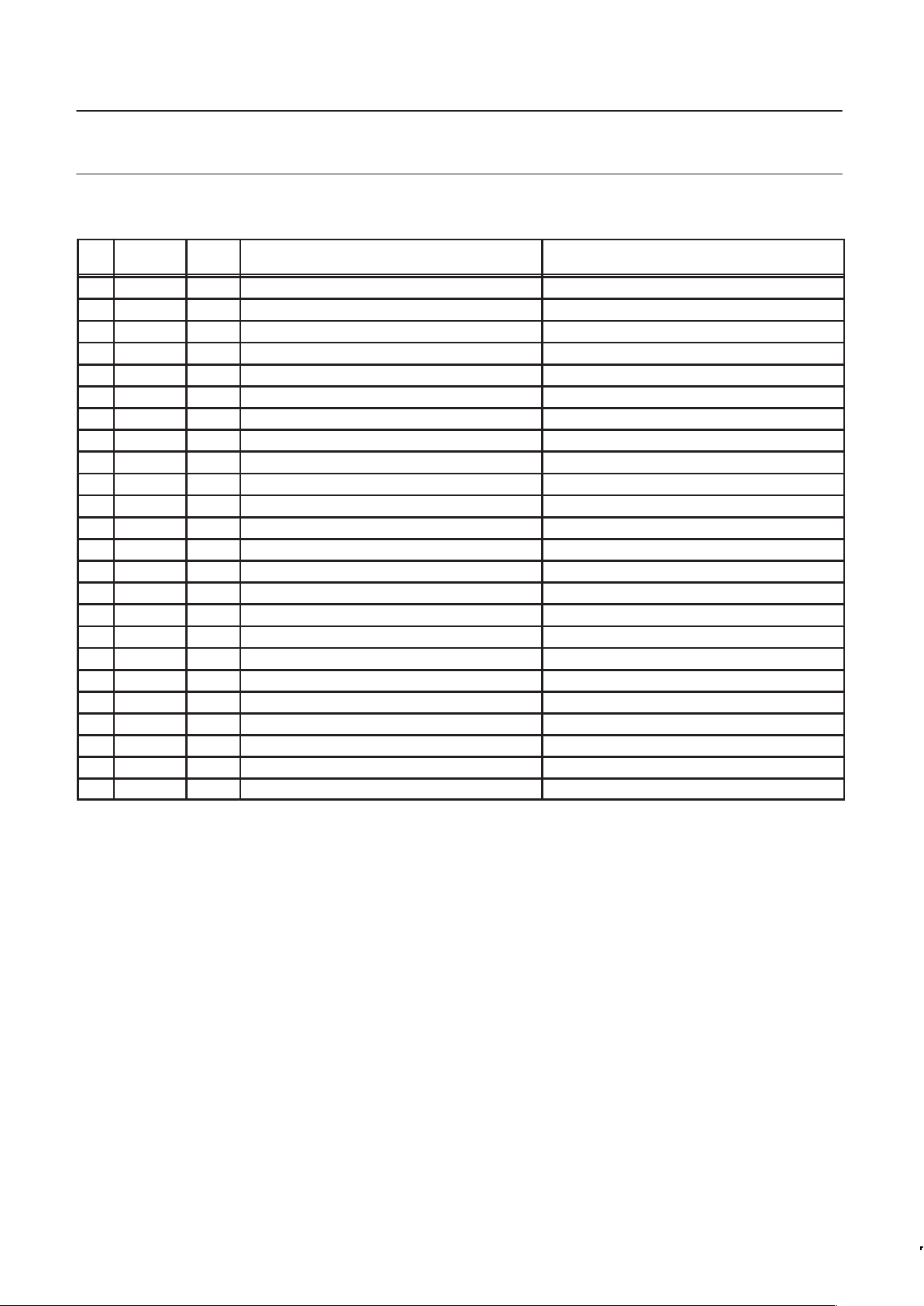

T able 1. PIN DESCRIPTION

Pin#Name Type Function Notes

1 VDDLR RefV Reference for REFCLK Connect to CK133

2 REFCLK In Reference clock Connect to CK133

3 VDDP Pwr VDD for PLL 3.3V Supply

4 GNDP GND GND for PLL Ground

5 GNDl GND GND for control inputs Ground

6 PCLKM In Phase Detector Input Connect to Controller

7 SYNCLKN In Phase Detector Input Connect to Controller

8 GNDC GND GND for Phase Aligner Ground

9 VDDC Pwr VDD for Phase Aligner 3.3V Supply

10 VDDLPD RefV Reference for P.D. Inputs Connect to Controller

11 STOPB In Active Low Output Disable Connect to Controller

12 PWRDnB In Active Low power down 3.3V CMOS

13 S2 In Mode control input 3.3V CMOS

14 MULT1 In PLL multiplier select 3.3V CMOS

15 MULT0 In PLL multiplier select 3.3V CMOS

16 VDDO Pwr VDD for clock outputs 3.3V Supply

17 GNDO GND GND for clock outputs Ground

18 CLKB Out Output Clock (complement) Connect to Rambus Channel

19 N/C N/C Not used Not connected (floating)

20 CLK Out Output Clock Connect to Rambus Channel

21 GNDO GND GND for clock outputs Ground

22 VDDO Pwr VDD for clock outputs 3.3V Supply

23 S1 In Mode Control 3.3V CMOS

24 S0 In Mode Control 3.3V CMOS

Philips Semiconductors Preliminary specification

PCK201 1Direct Rambus Clock Generator

1999 Jan 19

4

This configuration achieves frequency-lock between the controller

and Rambus Channel clocks (PCLK and SYNCLK). These clock

signals are matched and phase-aligned at the RMC/RAC boundary

in order to allow data transfers to occur across this boundary without

additional latency.

The main clock source drives the system clock (PCLK) to the ASIC,

and also drives the reference clock (REFCLK) to the DRCG.

REFCLK may or may not be the same frequency as PCLK. A PLL

inside the DRCG multiplies REFCLK to generate the desired

frequency for BUSCLK. BUSCLK is driven on the Rambus Channel

through a terminated transmission line. At the mid-point of the

Channel, the RAC senses BUSCLK using its own DLL for clock

alignment, followed by a fixed divide-by- 4 circuit that generates

SYNCLK.

Pclk is the clock used in the Rambus memory controller (RMC) in

the ASIC. SYNCLK is the clock used at the ASIC interface of the

RAC. The DRCG together with the Gear Ratio Logic enables the

controller to exchange data directly from the PCLK domain to the

SYNCLK domain without incurring additional latency for

synchronization. In general, PCLK and SYNCLK can run at different

frequencies, so the Gear Ratio Logic must select the appropriate M

and N dividers such that the frequencies of PCLK/M and SYNCLK/N

are equal. In one example, PCLK=133MHz and SYNCLK=100MHz,

and M=4 while N=3, giving PCLK/M = SYNCLK/N = 33MHz. Figure

4 shows an example of the clock waveforms generated with the

Gear Ratio Logic.

PCK2010

Direct Rambus

Clock Generator

(DRCG)

Gear Ratio-

Logic

/4

DLL

MN

BUSCLK

REFCLK

RMC

PCLK

SYNCLK

RAC

RDRAMs

CONTROLLER

SynClk/N

Pclk/M

SW00290

Figure 1. System Clock Architecture

The ASIC drives the output clocks, Pclk and SynClk/N from the

Gear Ratio Logic to the DRCG Phase Detector inputs. The routing

of the Pclk/M and SynClk/N signal traces must be matched in

impedance and propagation delay on the ASIC as well as on the

board. These signals are not part of the Rambus Channel and their

routing must be matched by board designers.

After comparing the phases of Pclk/M and SynClk/N, the DRCG

Phase Detector drives a phase aligner that adjusts the phase of

DRCG output clock, Busclk. Since the other elements in the

distributed loop have a fixed delay, adjusting Busclk adjusts the

phase of SynClk and thus the phase of SynClk/N.

In this manner, the distributed loop adjusts the phase of SynClk/N to

match that of Pclk/M, eliminating the phase error at the input of the

DRCG. When the clocks are aligned, data can be exchanged

directly from the Pclk domain to the SynClk domain.

The Gear Ratio Logic supports four clock ratios (2.0, 1.5, 1.33, and

1.0), where the ratio is defined as the ratio of Pclk/SynClk. Since

Busclk = 4*SynClk, this ratio also is equal to 4*Pclk/Busclk. Other

ratios could be used, depending on particular system

implementations.

Loading...

Loading...