Philips PCK2002DGG, PCK2002DL Datasheet

INTEGRATED CIRCUITS

PCK2002

2

0–300 MHz I

Product data

File under Integrated Circuits ICL03

C 1:18 clock buffer

2001 Jul 19

Philips Semiconductors Product data

2

0–300 MHz I

C 1:18 clock buffer

PCK2002

FEA TURES

•HIGH speed, LOW noise non-inverting 1–18 buffer

•Typically used to support four SDRAM DIMMs

•Multiple V

, VSS pins for noise reduction

DD

•3.3 V operation

•Separate 3-State pin for testing

•ESD protection exceeds 2000 V per Standard 801.2

•Optimized for 66 MHz, 100 MHz and 133 MHz operation

•Typical 175 ps skew outputs

•Available in 48-pin SSOP and TSSOP packages

•See PCK2002M for mobile (reduced pincount) 28-pin 1-10 buffer

•Spread spectrum compliant

•Individual clock output enable/disable via I

DESCRIPTION

The PCK2002 is a 1–18 fanout buffer used for 133/100 MHz CPU,

66/33 MHz PCI, 14.318 MHz REF, or 133/100/66 MHz SDRAM

clock distribution. 18 outputs are typically used to support up to

4 SDRAM DIMMS commonly found in desktop, workstation or

server applications.

All clock outputs meet Intel’s drive, rise/fall time, accuracy , and skew

requirements. An I

enabled/disabled individually. An output disabled via the I

interface will be held in the LOW state. In addition, there is an OE

input which 3-States all outputs.

2

C interface is included to allow each output to be

2

C

version

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS TYPICAL UNIT

t

t

I

PLH

PHL

t

r

t

f

CC

Propagation delay

BUF_IN to BUF_OUT

n

VCC = 3.3 V, CL = 30 pF

2.7

2.9

Rise time VCC = 3.3 V, CL = 30 pF 1.1 ns

Fall time VCC = 3.3 V, CL = 30 pF 1.0 ns

Total supply current VCC = 3.465 V 35 µA

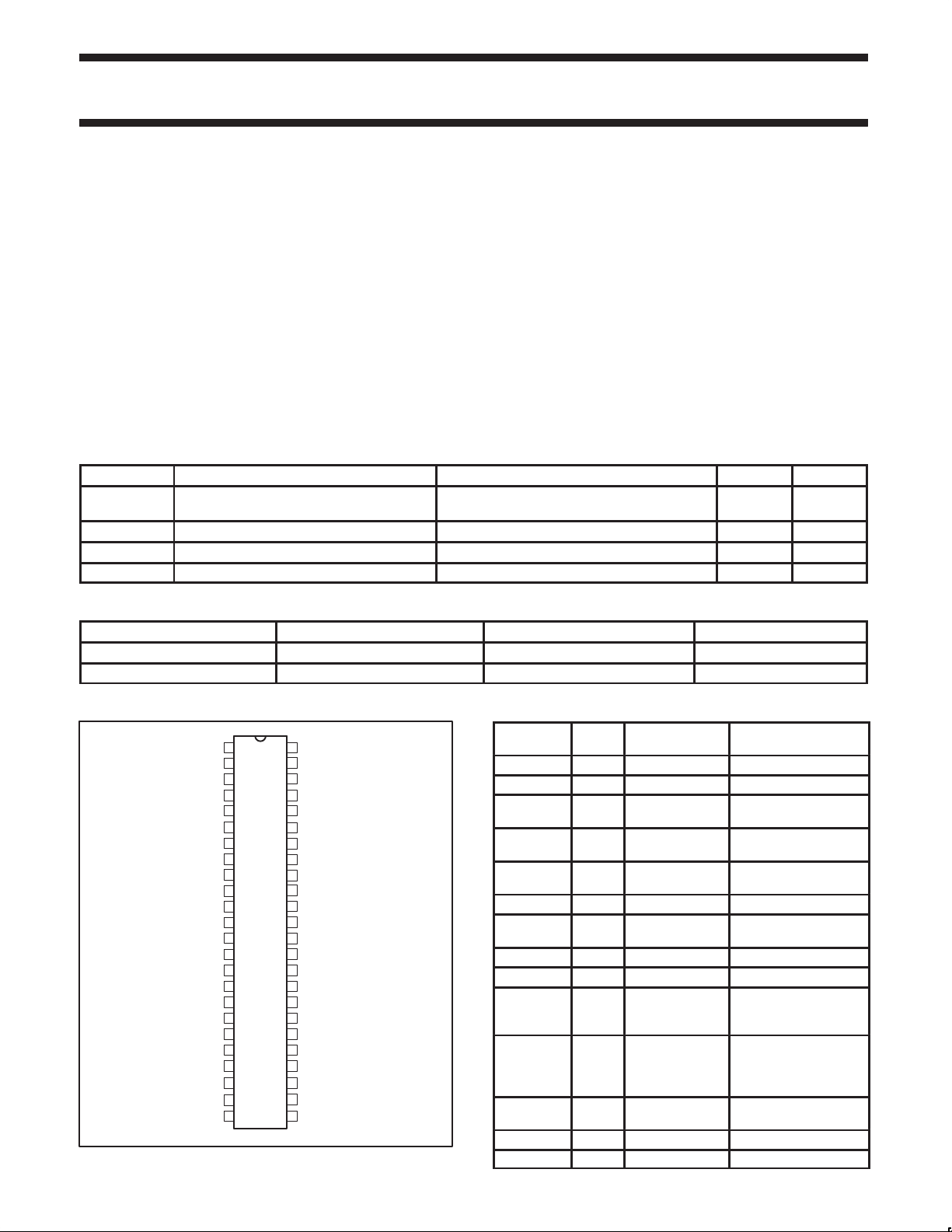

ORDERING INFORMATION

PACKAGES TEMPERATURE RANGE ORDER CODE DRAWING NUMBER

48-Pin Plastic TSSOP 0 to +70 °C PCK2002DGG SOT362-1

48-Pin Plastic SSOP 0 to +70 °C PCK2002DL SOT370-1

2

C

ns

PIN CONFIGURATION

RESERVED

RESERVED

BUF_OUT0

BUF_OUT1

BUF_OUT2

BUF_OUT3

BUF_OUT4

BUF_OUT5

BUF_OUT6

BUF_OUT7

BUF_OUT16

I2C is a trademark of Philips Semiconductors Corporation.

V

DD0

V

SS0

V

DD1

V

SS1

BUF_IN

V

DD2

V

SS2

V

DD3

V

SS3

V

DD4

V

SS4

V

DDI2C

SDA

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

RESERVED

47

RESERVED

V

46

DD9

45

BUF_OUT15

44

BUF_OUT14

V

43

SS9

V

42

DD8

41

BUF_OUT13

40

BUF_OUT12

V

39

SS8

OE

38

V

37

DD7

36

BUF_OUT11

35

BUF_OUT10

V

34

SS7

PCK2002

V

33

DD6

32

BUF_OUT9

BUF_OUT8

31

V

30

SS6

V

29

DD5

BUF_OUT17

28

V

27

SS5

V

SSI2C

26

25

SCL

SW00731

PIN DESCRIPTION

PIN

NUMBER

4, 5, 8, 9 Output BUF_OUT (0–3) Buffered clock outputs

13, 14, 17, 18 Output BUF_OUT (4–7) Buffered clock outputs

31, 32, 35,

36

40, 41, 44,

45

21, 28 Output

11 Input BUF_IN Buffered clock input

38 Input OE

24 I/O SDA I2C serial data

25 Input SCL I2C serial clock

3, 7, 12, 16,

20, 29, 33,

37, 42, 46

6, 10, 15,

19, 22,

27, 30, 34,

39, 43

23 Input V

26 Input V

1, 2, 47, 48 n/a RESERVED Undefined

I/O

TYPE

Output

Output

Input V

Input V

SYMBOL FUNCTION

BUF_OUT

(8–11)

BUF_OUT

(12–15)

BUF_OUT

(16–17)

Buffered clock outputs

Buffered clock outputs

Buffered clock outputs

Active high output

enable

DD (0–9)

SS (0–9)

DDI2C

SSI2C

3.3 V Power supply

Ground

3.3 V I2C Power

supply

I2C Ground

2001 Jul 19 853-2267 26745

2

Philips Semiconductors Product data

SYMBOL

PARAMETER

CONDITION

UNIT

SYMBOL

PARAMETER

CONDITIONS

UNIT

0–300 MHz I

2

C 1:18 clock buffer

PCK2002

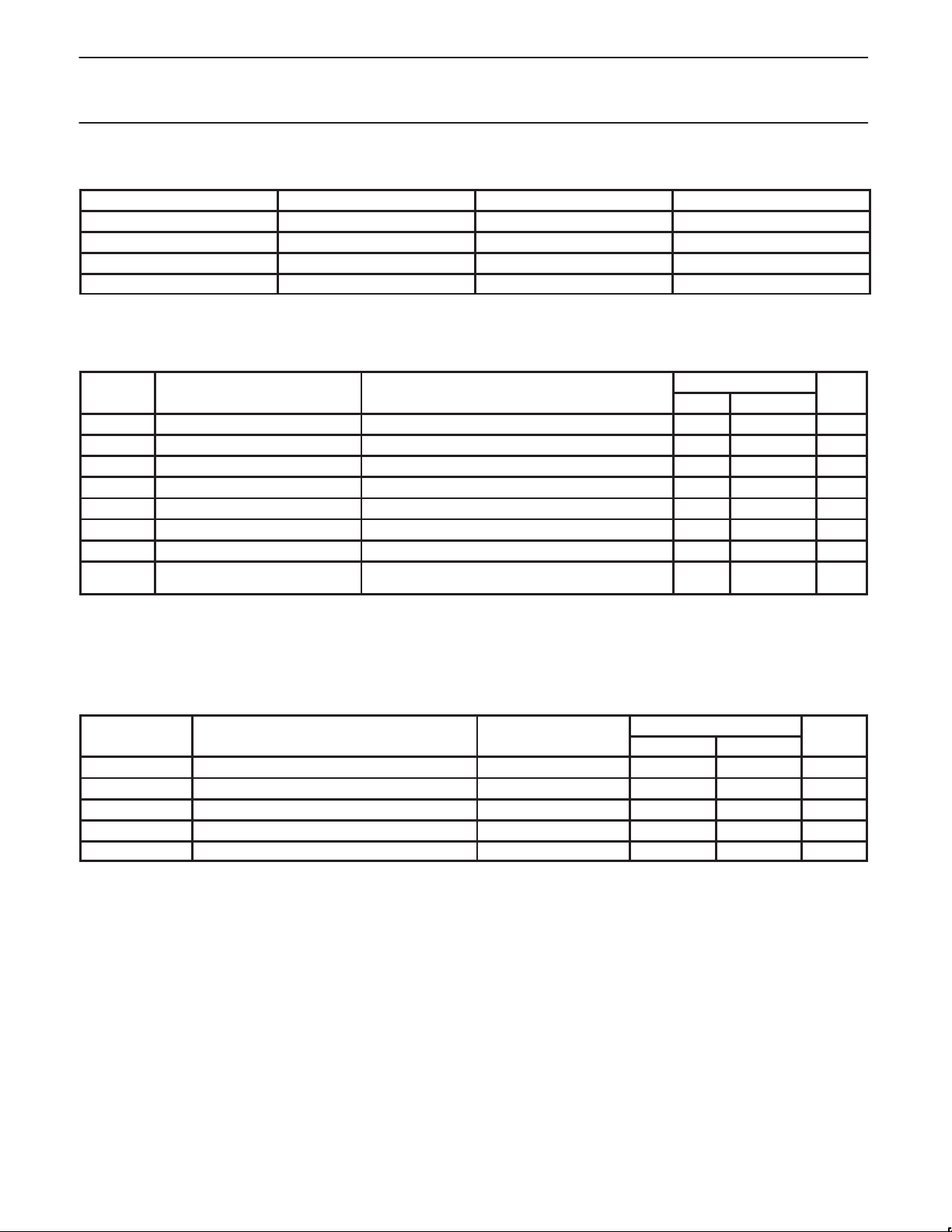

FUNCTION TABLE

OE BUF_IN I2CEN BUF_OUTn

L X X Z

H L X L

H H H H

H H L L

ABSOLUTE MAXIMUM RA TINGS

In accordance with the Absolute Maximum Rating System (IEC 134)

Voltages are referenced to V

V

DD

I

IK

V

I

OK

V

O

I

O

T

STG

P

TOT

NOTES:

1. Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the

device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to

absolute-maximum-rated conditions for extended periods may affect device reliability .

2. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

DC 3.3 V supply voltage –0.5 +4.6 V

DC input diode current VI < 0 –50 mA

DC input voltage Note 2 –0.5 +4.6 V

I

DC output diode current VO > VDD or VO < 0 ±50 mA

DC output voltage Note 2 –0.5 VCC + 0.5 V

DC output source or sink current VO >= 0 to V

Storage temperature range –65 +150 °C

Power dissipation per package

plastic medium-shrink SO (SSOP)

(VSS = 0V)

SS

1, 2

DD

For temperature range: 0 to +70°C

above +55°C derate linearly with 11.3mW/K

LIMITS

MIN MAX

±50 mA

850 mW

RECOMMENDED OPERATING CONDITIONS

V

T

C

V

V

amb

DD

L

I

O

Operating ambient temperature range in free air 0 +70 °C

DC 3.3 V supply voltage 3.135 3.465 V

Capacitive load 20 30 pF

DC input voltage range 0 V

DC output voltage range 0 V

LIMITS

MIN MAX

DD

DD

V

V

2001 Jul 19

3

Philips Semiconductors Product data

TEST CONDITIONS

VOH3.3V output HIGH voltage

V

VOL3.3V output LOW voltage

V

IOHOutput HIGH current

mA

IOLOutput LOW current

mA

2

0–300 MHz I

C 1:18 clock buffer

DC CHARACTERISTICS

SYMBOL PARAMETER

V

IH

V

IL

±I

I

±I

OZ

I

CC

∆I

CC

HIGH level input voltage 3.135 to 3.465 2.0 VDD + 0.3 V

LOW level input voltage 3.135 to 3.465 VSS – 0.3 0.8 V

p

p

p

p

Input leakage current 3.465 — ±5 µA

3-State output OFF-State current 3.465 V

Quiescent supply current 3.465 VI = VDD or GND IO = 0 — 100 µA

Additional quiescent supply

current given per control pin

PCK2002

LIMITS

T

= 0 to +70 °C UNIT

amb

VDD(V) OTHER MIN MAX

3.135 to 3.465 IOH = –1 mA VCC – 0.1 —

3.135 IOH = –36 mA 2.4 —

3.135 to 3.465 IOL= 1 mA — 0.1

3.135 IOL= 24 mA — 0.4

3.135 V

3.465 V

3.135 to 3.465 V

3.135 to 3.465 V

3.135 to 3.465 V

= 2.0 V –54 –126

OUT

= 3.135 V –21 –46

OUT

= 1.0 V 49 118

OUT

= 0.4 V 24 53

OUT

= VDDor GND IO = 0 — 10 µA

OUT

= VDD– 0.6V IO = 0 — 500 µA

I

AC CHARACTERISTICS

SYMBOL PARAMETER

TEST CONDITIONS

NOTES MIN TYP

T

T

T

T

PZL

PLZ

SDRISE

SDFALL

T

PLH

T

PHL

, T

PZH

, T

PHZ

SDRAM buffer LH propagation delay 4, 5 1.2 2.7 3.5 ns

SDRAM buffer HL propagation delay 4, 5 1.2 2.9 3.5 ns

SDRAM rise time 2, 4 1.5 2.0 4.0 V/ns

SDRAM fall time 2, 4 1.5 2.9 4.0 V/ns

SDRAM buffer enable time 4, 5 1.0 2.6 5.0 ns

SDRAM buffer disable time 4, 5 1.0 2.7 5.0 ns

DUTY CYCLE Output Duty Cycle Measured at 1.5 V 3, 4, 5 45 52 55 %

T

SDSKW

T

DDSKW

SDRAM Bus CLK skew 1, 4 — 150 250 ps

Device to device skew — — 500 ps

NOTES:

1. Skew is measured on the rising edge at 1.5 V .

SDRISE

and T

2. T

3. Duty cycle should be tested with a 50/50% input.

are measured as a transition through the threshold region VOL = 0.4 V and VOH = 2.4 V (1mA) JEDEC specification.

SDFALL

4. Over MIN (20 pF) to MAX (30 pF) discrete load, process, voltage, and temperature.

5. Input edge rate for these tests must be faster than 1 V/ns.

6. All typical values are at V

= 3.3 V and T

CC

amb

= 25 °C.

LIMITS

T

= 0 to +70 °C

amb

6

MAX

UNIT

2001 Jul 19

4

Loading...

Loading...