INTEGRATED CIRCUITS

DATA SH EET

PCD5090; PCA5097

DECT baseband controllers

Objective specification

File under Integrated Circuits, IC17

1996 Oct 17

Philips Semiconductors Objective specification

DECT baseband controllers PCD5090; PCA5097

INTRODUCTION

This data sheet details the specific features of the:

PCD5090/xxx; DSP-ROM, with external ROM

PCA5097/xxx; DSP-ROM, with Field Electronically

Erasable Programmable Read Only Memory

(FEEPROM).

• On-chip reference voltage

FEATURES

General

• The PCx509x is designed for GAP-compliant handsets

and simple base stations

• Embedded 80C51 microcontroller with twice the

performance of the classic architecture, up to

128 kbytes external memory or 64 kbytes FEEPROM

program memory and 3 kbytes of data memory on chip.

In addition there is 1 kbyte of on-chip data memory that

is shared with on-chip Burst Mode Logic (BML) and

DSP, the System Data RAM (SDR).

• 80C51 ports P0, P1, P2 and P3 available for interfacing

to display, keyboard, I

external memory. External program memory is

addressable up to 128 kbytes (PCD5090/xxx and

PCA5097/xxx).

• Portable Part (PP) and Fixed Part (FP) modes

• TDMA frame (de)multiplexing; transmission or reception

can be programmed for any slot

• Ciphering, scrambling, CRC checking/generation,

protected B-fields

• Speech and data buffering space for six handsets

• Local call and B-field loop-back

• Two interrupt lines for BML and DSP to interrupt 80C51

• On-chip, three-channel time-multiplexed 8-bit

Analog-to-Digital Converter (ADC) for RSSI

measurement and battery voltage measurement. One

channel available for other purposes.

• On-chip 8-bit DAC for frequency adjustment of

13.824 MHz on-chip crystal oscillator

• Phase error measurement and phase error correction by

hardware

• Digital-to-Analog Converters (DACs) and ADCs for

dynamic earpiece and dynamic or electret microphone

2

C-bus, interrupt sources and/or

• On-chip supply for electret microphone

• Very low ohmic buzzer output

• Serial interface to external ADPCM CODEC (PCD5032)

• IOM-2interface (Siemens registered trademark)

• Serial interface to synthesizer for frequency

programming

• Programmable timing of radio-control signals

• Programmable polarity of radio-control signals

• Easy interfacing with radio circuits, operating at other

supply voltage

• Programmable GMSK pulse shaper

• On-chip comparator for use as bit-slicer

• Power-on reset

• Low supply voltage (2.7 to 5.5 V)

• SACMOS technology.

DSP software features

• ADPCM encoding and decoding complying with G.721

• Speech filters

• Programmable gain in speech paths

• Side tone and soft mute

• Ringer and tone (DTMF) generator

• Dial tone detection

• Echo cancellation

• Automatic gain control

• Telephone Answering Machine (TAM) switch

• Conference call (PCD5090/400)

• Hands-free operation (PCD5090/311).

For each DSP software version a separate manual is

available, in which detailed information is provided on how

parameters must be set.

1996 Oct 17 2

Philips Semiconductors Objective specification

DECT baseband controllers PCD5090; PCA5097

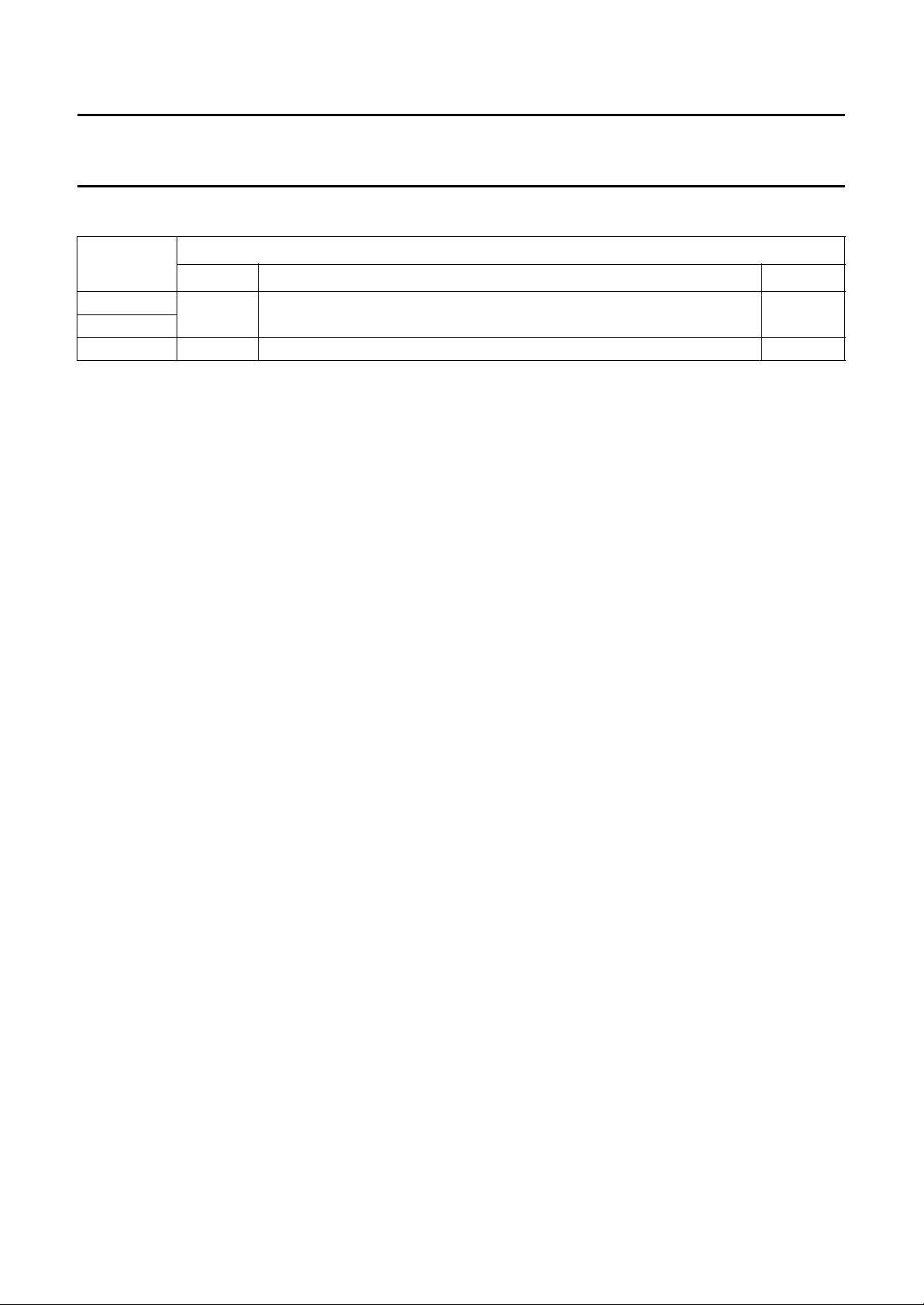

ORDERING INFORMATION

TYPE

NUMBER

PCD5090H

PCA5097H

PCD5090HZ LQFP100 plastic low profile quad flat package; 100 leads; body 14 × 14 × 1.4 mm SOT407-1

NAME DESCRIPTION VERSION

QFP100

plastic quad flat package; 100 leads (lead length 1.95 mm); body

14 × 20 × 2.8 mm

PACKAGE

SOT317-2

1996 Oct 17 3

Philips Semiconductors Objective specification

DECT baseband controllers PCD5090; PCA5097

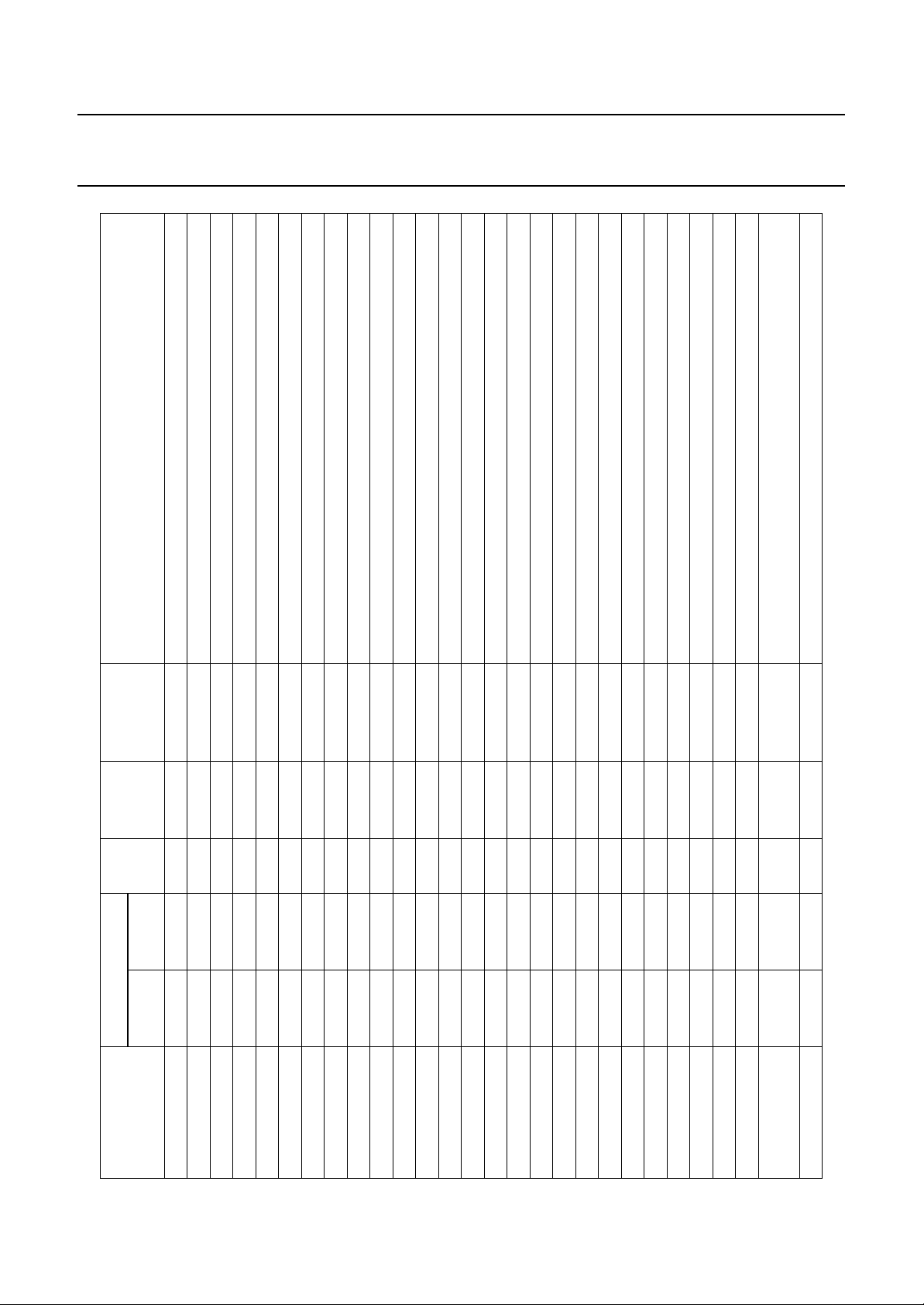

BLOCK DIAGRAM

digital pins

analog pins

supply pins

TST1

TST2

CLK3

DCK

BZP

BZM

EARP

DI

DO

FS1

EARM

LIFP

LIFM

MICP

MICM

VMIC

ref

V

VANLI

RSSI_AN

VBAT

DDA

V

SSA

V

DD

2 ×

V

SS

2 ×

V

DD_RF

V

SS_RF

V

PORT 3.7

PORT 3.0 to

PORT 2.7

PORT 2.0 to

8 8 8

PORT 1.7

PORT 1.0 to

8

PORT 0.7

PORT 0.0 to

DD_FEE

V

SS_FEE

V

DD

V

PORT 3

PORT 1 PORT 2

PORT 0

IB-BUS

80CL51- CORE

(TCB)

TEST CONTROL BLOCK

DD

V

C-BUS

2

I

(256 BYTES)

MICROCONTROLLER_RAM

AUX-RAM

(3 kBYTES)

FEEPROM

(64 kBYTES)

PGMFEE

(SPI)

IOM/ADPCM

SPEECH INTERFACE

(ABB)

BUZZER BUFFER

DD

V

MICROCONTROLLER

DD

V

DD

V

INTERFACE (ABCIF)

AB-MICROCONTROLLER

DD

V

DD_RF

V

MGE610

VANLO

handbook, full pagewidth

Fig.1 Functional blocks and signals in PCx509x.

EN_WATCHDOG RESET_OUT M_RESET VBGP

PEAK-HOLD

3 : 1

MUX

ANALOG

SOURCE

VOLTAGE

(AVR)

REFERENCE

OF

(DCA)

ANALOG

RESET

WATCHDOG

XTAL

ref

V

SUBTRACT

ADC

V

(AVS)

(POR)

POWER-ON RESET

(RGE)

GENERATOR

(WDT)

TIMER

(XOSC)

OSCILLATOR

CDC-on

ARA

ARF

ARD

1-BIT ADC

DDA

V

s

108f

(DNS)

NOISE

DIGITAL

SHAPER

s

4f

SIGNAL

DIGITAL

(BML)

MODE

LOGIC

BURST

LEVEL

SHIFTER

Σ ∆

s

108f

DIGITAL

DECIMATING

s

4f

(DSP)

PROCESSOR

RAM

DATA

(SDR)

SYSTEM

AMP

ATS

1-BIT ADC

(DDF)

FILTER

(1 kBYTE)

V

DDA

CODEC

AGM

AUXILIARY ADC (AAD)

DDA

V

DIGITAL

CONTROL

ISB BUS

CONTROLLER

BLOCK

TIMING CONTROL

CLOCK

GENERATOR

DD

V

ref

V

ANALOG VOLTAGE

(IBC)

(TICB)

(CLG)

PSE

EA

ALE

PGM

WEN

SC

SDI

OEN

SDO/A16

R_PWR

SLICE_CTR

REF_CLK

R_ENABLE

SYNTH_LOCK

S_CLK

S_DATA

S_ENABLE

S_PWR

ANT_SW0

VCO_BND_SW

1996 Oct 17 4

ANT_SW1

T_ENABLE

T_PWR_RMP

T_DATA

R_DATAP

R_DATAM

R_SLICED

T_GMSK

GP_CLK7

DPLL_DATA

XTAL1

XTAL2

CLK100

Philips Semiconductors Objective specification

DECT baseband controllers PCD5090; PCA5097

PIN TYPE PIN DESCRIPTION

STATE

AFTER

RESET

I/O

PIN

QFP100 LQFP100

ADPCM output or IOM data clock input/output

(ISF2UPES in PCD5090/xxx, PCA5097/xxx)

ISF2UPES

15 13 −−supply negative supply voltage for RF interface level shifters

16 14 −−supply positive supply voltage for RF interface level shifters

17 15 −−supply positive supply voltage for FEEPROM program memory

SYMBOL

ANT_SW1 1 99 O H ISP2DRF3 antenna switch 1 output

ANT_SW0 2 100 O H ISP2DRF3 antenna switch 0 output

CLK100 3 1 O H ISP2DPES 100 Hz signal related to DECT frame timing output

T_ENABLE 4 2 O H ISP2DRF3 enable transmitter output

T_PWR_RMP 5 3 O L ISP2DRF3 switch transmitter power output

T_DATA 6 4 O off ISF2DRF3 unmodulated transmitter data output

T_GMSK 7 5 O L ANAIOD1 GMSK modulated transmitter data output

VCO_BND_SW 8 6 O L ISP2DRF3 VCO band switch output

SYNTH_LOCK 9 7 I − DIPP0RF3 synthesizer lock input

S_ENABLE 10 8 O L ISP2DRF3 synthesizer enable output

S_DATA 11 9 O L ISP2DRF3 serial synthesizer data output

PINNING

S_CLK 12 10 O L ISP2DRF3 clock for serial synthesizer interface output

1996 Oct 17 5

SS_RF

DD_RF

S_PWR 13 11 O H ISP2DRF3 switch synthesizer power output

REF_CLK 14 12 O running ISP4DRF3 13.824 MHz reference clock for synthesizer output

V

DD_FEE

V

V

SLICE_CTR 18 16 O L ISP2DRF3 switch slicer time constant output

R_PWR 19 17 O H ISP2DRF3 switch receiver power output

R_DATAP 20 18 I − ANAIOD2 positive input for receiver data

R_DATAM 21 19 I − ANAIOD2 negative input for receiver data

R_ENABLE 22 20 O H ISP2DRF3 enable receiver output

RSSI_AN 23 21 I − ANAIOD1 analog input for RSSI measurement

VANLI 24 22 I − ANAIOD1 analog input to A/D converter

VBAT 25 23 I − ANAIOD1 analog input for battery voltage measurement

CLK3 26 24 O L ISP2DPES 3.456 MHz clock output for external ADPCM codec

DCK 27 25 I/O input ISF2DPES

DI 28 26 I − DIPP0PES ADPCM or IOM data input

Loading...

Loading...