Philips P80C575EHBB, P87C575EHPN, P87C575EHLKA, P87C575EHFFA, P87C575EHBB Datasheet

...

80C575/83C575/87C575

80C51 8-bit microcontroller family

8K/256 OTP/ROM/ROMless, 4 comparator,

failure detect circuitry, watchdog timer

Product specification

Supersedes data of 1998 Jan 27

IC20 Data Handbook

1998 May 01

INTEGRATED CIRCUITS

Philips Semiconductors Product specification

80C575/83C575/

87C575

80C51 8-bit microcontroller family

8K/256 OTP/ROM/ROMless, 4 comparator, failure detect circuitry, watchdog timer

2

1998 May 01 853-1684 19332

DESCRIPTION

The Philips 80C575/83C575/87C575 is a

high-performance microcontroller fabricated

with Philips high-density CMOS technology.

The Philips CMOS technology combines the

high speed and density characteristics of

HMOS with the low power attributes of

CMOS. Philips epitaxial substrate minimizes

latch-up sensitivity.

The 8XC575 contains an 8k × 8 ROM

(83C575) EPROM (87C575), a 256 × 8 RAM,

32 I/O lines, three 16-bit counter/timers, a

Programmable Counter Array (PCA), a

seven-source, two-priority level nested

interrupt structure, an enhanced UART, four

analog comparators, power-fail detect and

oscillator fail detect circuits, and on-chip

oscillator and clock circuits.

In addition, the 8XC575 has a low active

reset, and the port pins are reset to a low

level. There is also a fully configurable

watchdog timer, and internal power on clear

circuit. The part includes idle mode and

power-down mode states for reduced power

consumption.

FEA TURES

•80C51 based architecture

– 8k × 8 ROM (83C575)

– 8k × 8 EPROM (87C575)

– ROMless (80C575)

– 256 × 8 RAM

– Three 16-bit counter/timers

– Programmable Counter Array

– Enhanced UART

– Boolean processor

– Oscillator fail detect

– Low active reset

– Asynchronous low port reset

– Schmitt trigger inputs

– 4 analog comparators

– Watchdog timer

– Low V

CC

detect

•Memory addressing capability

– 64k ROM and 64k RAM

•Power control modes:

– Idle mode

– Power-down mode

•CMOS and TTL compatible

•4.0 to 16MHz

•Extended temperature ranges

•OTP package available

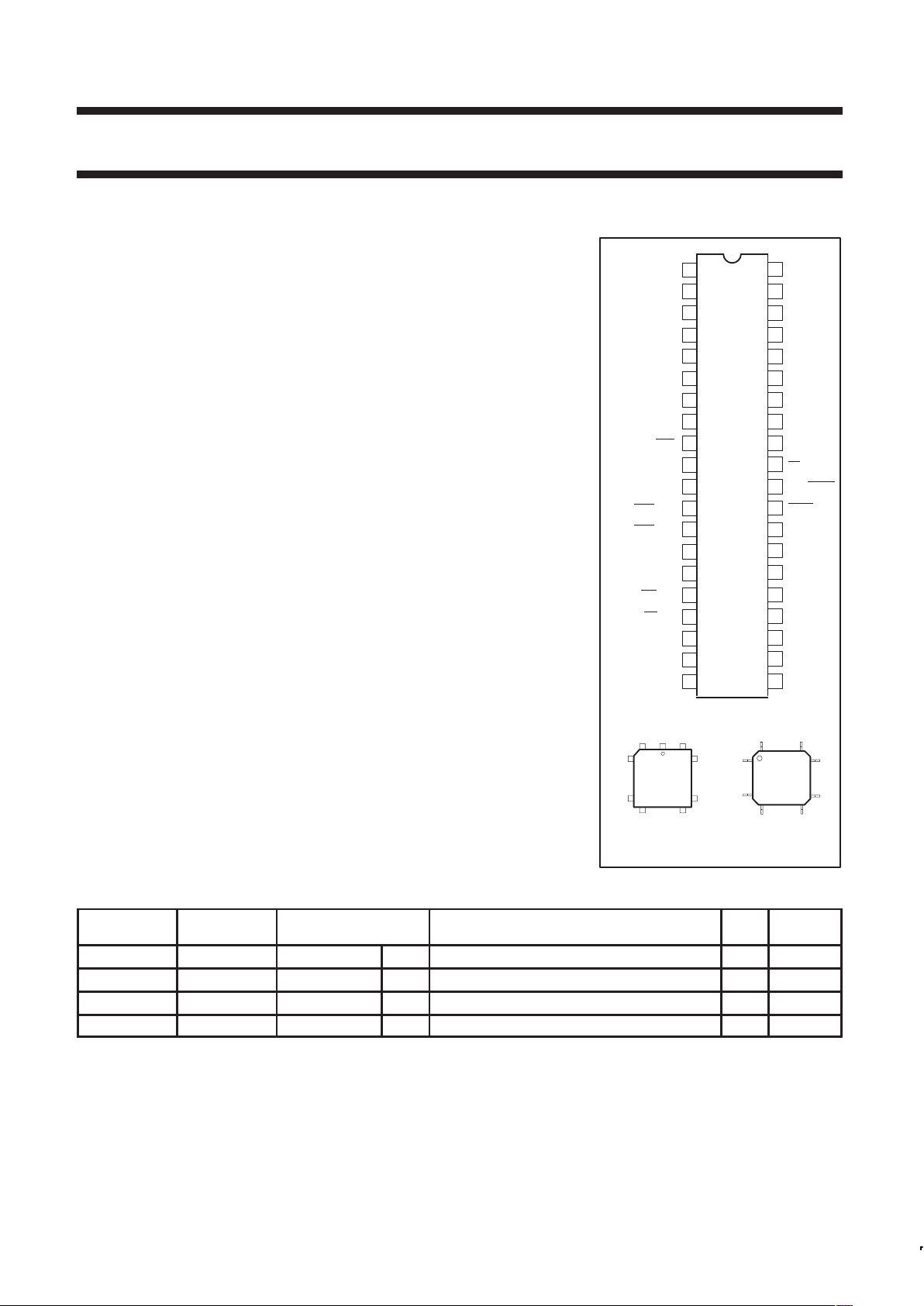

PIN CONFIGURATIONS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

CMP0+/P1.0/T2

CMP0-/P1.1/T2EX

ECI/P1.2

CMP0/CEX0/P1.3

CMP1/CEX1/P1.4

CMP2/CEX2/P1.5

CMP3/CEX3/P1.6

RST

RxD/P3.0

TxD/P3.1

INT0

/P3.2

INT1/P3.3

CMPR-/T0/P3.4

CMP1+/T1/P3.5

CEX4/P1.7

CMP2+/WR

/P3.6

CMP3+/RD/P3.7

XTAL2

XTAL1

V

SS

P2.0/A8

P2.1/A9

P2.2/A10

P2.3/A11

P2.4/A12

P2.5/A13

P2.6/A14

P2.7/A15

PSEN

ALE/PROG

EA/V

PP

P0.7/AD7

P0.6/AD6

P0.5/AD5

P0.4/AD4

P0.3/AD3

P0.2/AD2

P0.1/AD1

P0.0/AD0

V

DD

PQFP

644140

34

1

7

17

11

39

33

29

23

12

18 28

22

DUAL

IN-LINE

PACKAGE

LCC

SU00234

ORDERING INFORMA TION

ROMless ROM EPROM

1

TEMPERATURE RANGE °C AND PACKAGE

FREQ

(MHz)

DRAWING

NUMBER

P80C575EBPN P83C575EBPN P87C575EBPN OTP 0 to +70, 40-Pin Plastic Dual In-line Package 16 SOT129-1

P80C575EBAA P83C575EBAA P87C575EBAA OTP 0 to +70, 44-Pin Plastic Leaded Chip Carrier 16 SOT187-2

P80C575EHAA P83C575EHAA P87C575EHAA OTP –40 to +125, 44-Pin Plastic Leaded Chip Carrier 16 SOT187-2

P80C575EBBB P83C575EBBB P87C575EBBB OTP 0 to +70, 44-Pin Plastic Quad Flat Pack 16 SOT307-2

NOTE:

1. OTP - One Time Programmable EPROM.

Philips Semiconductors Product specification

80C575/83C575/

87C575

80C51 8-bit microcontroller family

8K/256 OTP/ROM/ROMless, 4 comparator, failure detect circuitry, watchdog timer

1998 May 01

3

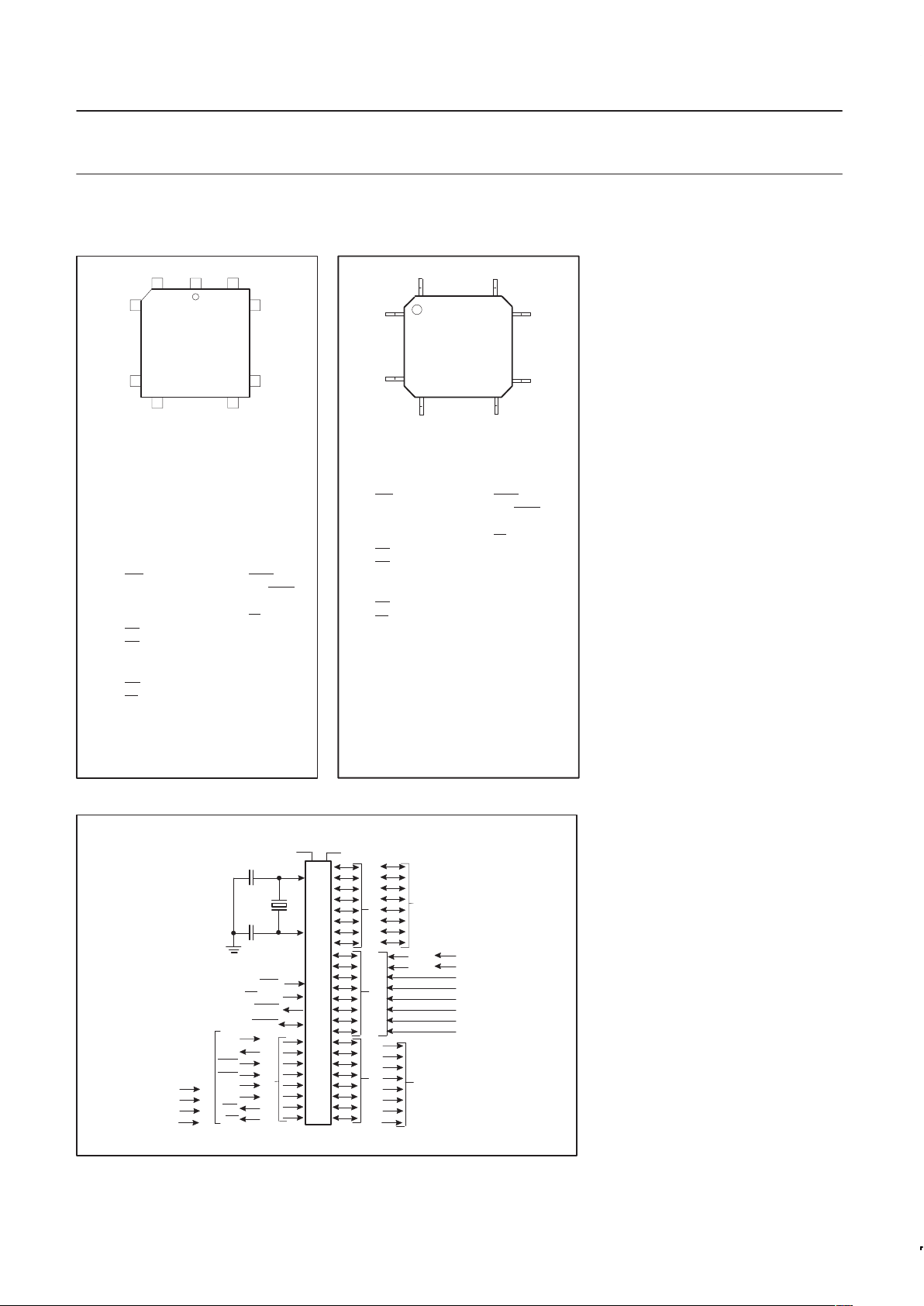

BLOCK DIAGRAM

PSEN

EA

ALE

RST

XTAL1 XTAL2

V

CC

V

SS

PORT 0

DRIVERS

PORT 2

DRIVERS

RAM ADDR

REGISTER

RAM

PORT 0

LATCH

PORT 2

LATCH

ROM/

EPROM

REGISTER

B

ACC

TMP2

TMP1

ALU

TIMING

AND

CONTROL

INSTRUCTION

REGISTER

PD

OSCILLATOR

PSW

PORT 1

LATCH

PORT 3

LATCH

PORT 1

DRIVERS

PORT 3

DRIVERS

PROGRAM

ADDRESS

REGISTER

BUFFER

PC

INCRE-

MENTER

PROGRAM

COUNTER

DPTR

P1.0-P1.7

P3.0-P3.7

P0.0-P0.7 P2.0-P2.7

STACK

POINTER

SFRs

TIMERS

PCA

SU00238

Philips Semiconductors Product specification

80C575/83C575/

87C575

80C51 8-bit microcontroller family

8K/256 OTP/ROM/ROMless, 4 comparator, failure detect circuitry, watchdog timer

1998 May 01

4

CERAMIC AND PLASTIC LEADED

CHIP CARRIER PIN FUNCTIONS

LCC

6140

7

17

39

29

18 28

Pin Function

1 NC*

2 T2/P1.0/CMP0+

3 T2EX/P1.1/CMP0–

4 P1.2/ECI

5 P1.3/CMP0/CEX0

6 P1.4/CMP1/CEX1

7 P1.5/CMP2/CEX2

8 P1.6/CMP3/CEX3

9 P1.7/CEX4

10 RST

11 RxD/P3.0

12 NC*

13 TxD/P3.1

14 INT

0/P3.2

15 INT

1/P3.3

16 T0/P3.4/CMPR–

17 T1/P3.5/CMP1+

18 WR

/P3.6/CMP2+

19 RD

/P3.7/CMP3+

20 XTAL2

21 XTAL1

22 V

SS

Pin Function

23 NC*

24 P2.0/A8

25 P2.1/A9

26 P2.2/A10

27 P2.3/A11

28 P2.4/A12

29 P2.5/A13

30 P2.6/A14

31 P2.7/A15

32 PSEN

33 ALE/PROG

34 NC*

35 EA

/V

PP

36 P0.7/AD7

37 P0.6/AD6

38 P0.5/AD5

39 P0.4/AD4

40 P0.3/AD3

41 P0.2/AD2

42 P0.1/AD1

43 P0.0/AD0

44 V

CC

SU00235

* NO INTERNAL CONNECTION

PLASTIC QUAD FLAT P ACK

PIN FUNCTIONS

PQFP

44 34

1

11

33

23

12 22

SU00236

Pin Function

1 P1.5/CMP2/CEX2

2 P1.6/CMP3/CEX3

3 P1.7/CEX4

4 RST

5 RxD/P3.0

6 NC*

7 TxD/P3.1

8 INT

0/P3.2

9 INT

1/P3.3

10 T0/P3.4/CMPR–

11 T1/P3.5/CMP1+

12 WR

/P3.6/CMP2+

13 RD

/P3.7CMP3+

14 XTAL2

15 XTAL1

16 V

SS

17 NC*

18 P2.0/A8

19 P2.1/A9

20 P2.2/A10

21 P2.3/A11

22 P2.4/A12

Pin Function

23 P2.5/A13

24 P2.6/A14

25 P2.7/A15

26 PSEN

27 ALE/PROG

28 NC*

29 EA

/V

PP

30 P0.7/AD7

31 P0.6/AD6

32 P0.5/AD5

33 P0.4/AD4

34 P0.3/AD3

35 P0.2/AD2

36 P0.1/AD1

37 P0.0/AD0

38 V

CC

39 NC*

40 T2/P1.0/CMP0+

41 T2EX/P1.1/CMP0–

42 P1.2/ECI

43 P1.3/CMP0/CEX0

44 P1.4/CMP1/CEX1

* NO INTERNAL CONNECTION

LOGIC SYMBOL

PORT 0

PORT 1PORT 2

PORT 3

ADDRESS AND

DATA BUS

ADDRESS BUS

T2

T2EX

RxD

TxD

INT0

INT1

T0

T1

WR

RD

SECONDARY FUNCTIONS

RST

EA/V

PP

PSEN

ALE/PROG

V

SS

V

CC

XTAL1

XTAL2

CMPR–

CMP1+

CMP2+

CMP3+

CMP0+

CMP0–

ECI

CMP0/CEX0

CMP1/CEX1

CMP2/CEX2

CMP3/CEX3

CEX4

SU00237

Philips Semiconductors Product specification

80C575/83C575/

87C575

80C51 8-bit microcontroller family

8K/256 OTP/ROM/ROMless, 4 comparator, failure detect circuitry, watchdog timer

1998 May 01

5

PIN DESCRIPTIONS

PIN NUMBER

MNEMONIC DIP LCC QFP TYPE NAME AND FUNCTION

V

SS

20 22 16 I Ground: 0V reference.

V

CC

40 44 38 I Power Supply: This is the power supply voltage for normal, idle, and power-down

operation.

P0.0-0.7 39-32 43-36 37-30 I/O Port 0: Port 0 is an open-drain bidirectional I/O port. Port 0 pins that have 1s written to them

float and can be used as high-impedance inputs. Port 0 is also the multiplexed low-order

address and data bus during accesses to external program and data memory. In this

application, it uses strong internal pull-ups when emitting 1s. Port 0 also receives code

bytes during EPROM programming and outputs code bytes during program verification.

External pull-ups are required during program verification. During reset, port 0 will be

asynchronously driven low and will remain low until written to by software. All port 0 pins

have Schmitt trigger inputs with 200mV hysteresis. A weak pulldown on port 0 guarantees

positive leakage current (see DC Electrical Characteristics: I

L1

).

P1.0-P1.7 1-8 2-9 40-44

1-3

I/O Port 1: Port 1 is an 8-bit bidirectional I/O port. Port 1 pins have internal pull-ups such that

pins that have 1s written to them can be used as inputs but will source current when

externally pulled low (see DC Electrical Characteristics: I

IL

). Port 1 receives the low-order

address byte during program memory verification and EPROM programming. During reset,

port 1 will be asynchronously driven low and will remain low until written to by software. All

port 1 pins have Schmitt trigger inputs with 50mV hysteresis. Port 1 pins also serve

alternate functions as follows:

1 2 40 I/O P1.0 T2 Timer 2 external I/O – clockout (programmable)

CMP0+ Comparator 0 positive input

2 3 41 I P1.1 T2EX Timer 2 capture input

CMP0- Comparator 0 negative input

3 4 42 I P1.2 ECI PCA count input

4 5 43 I/O P1.3 CEX0 PCA module 0 external I/O

CMP0 Comparator 0 output

5 6 44 I/O P1.4 CEX1 PCA module 1 external I/O

CMP1 Comparator 1 output

6 7 1 I/O P1.5 CEX2 PCA module 2 external I/O

CMP2 Comparator 2 output

7 8 2 I/O P1.6 CEX3 PCA module 3 external I/O

CMP3 Comparator 3 output

8 9 3 I/O P1.7 CEX4 PCA module 4 external I/O

P2.0-P2.7 21-28 24-31 18-25 I/O Port 2: Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s

written to them can be used as inputs, but will source current when externally pulled low

(see DC Electrical Characteristics: I

IL

). Port 2 emits the high-order address byte during

accesses to external program and data memory that use 16-bit addresses (MOVX

@DPTR). In this application, it uses strong internal pull-ups when emitting 1s. Port 2

receives the high-order address byte during program verification and EPROM programming.

During reset, port 2 will be asynchronously driven low and will remain low until written to by

software. Port 2 can be made open drain by writing to the P2OD register (AIH). In open

drain mode, weak pulldowns on port 2 guarantee positive leakage current (see DC

Electrical Characteristics I

L1

).

P3.0-P3.7 10-17 11,

13-195,7-13

I/O Port 3: Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins except P3.1

that have 1s written to them can be used as inputs but will source current when externally

pulled low (see DC Electrical Characteristics: I

IL

). P3.1 will be a high impedance pin except

while transmitting serial data, in which case the strong pull-up will remain on continuously

when outputting a 1 level. The P3.1 output drive level when transmitting can be set to one of

two levels by the writing to the P3.1 register bit. During reset all pins (except P3.1) will be

asynchronously driven low and will remain low until written to by software. All port 3 pins

have Schmitt trigger inputs with 200mV hysteresis, except P3.2 and P3.3, which have 50mV

hysteresis. Port 3 pins serve alternate functions as follows:

Philips Semiconductors Product specification

80C575/83C575/

87C575

80C51 8-bit microcontroller family

8K/256 OTP/ROM/ROMless, 4 comparator, failure detect circuitry, watchdog timer

1998 May 01

6

PIN DESCRIPTIONS (Continued)

PIN NUMBER

MNEMONIC DIP LCC QFP TYPE NAME AND FUNCTION

Port 3: (continued)

10 11 5 I P3.0 RxD Serial receive port

11 13 7 O P3.1 TxD Serial transmit port enabled only when transmitting serial data

12 14 8 I P3.2 INT0 External interrupt 0

13 15 9 I P3.3 INT1 External interrupt 1

14 16 10 I P3.4 T0 Timer/counter 0 input

CMPR- Common - reference to comparators 1, 2, 3

15 17 11 I P3.5 T1 T imer/counter 1 input

CMP1+ Comparator 1 positive input

16 18 12 O P3.6 WR External data memory write strobe

CMP2+ Comparator 2 positive input

17 19 13 O P3.7 RD External data memory read strobe

CMP3+ Comparator 3 positive input

RST 9 10 4 I Reset: A low on this pin asynchronously resets all port pins to a low state except P3.1. The

pin must be held low with the oscillator running for 24 oscillator cycles to initialize the

internal registers. An internal diffused resistor to V

CC

permits a power on reset using only

an external capacitor to V

SS

. RST has a Schmitt trigger input stage to provide additional

noise immunity with a slow rising input voltage.

ALE/PROG 30 33 27 I/O Address Latch Enable/Program Pulse: Output pulse for latching the low byte of the

address during an access to external memory. In normal operation, ALE is emitted at a

constant rate of 1/6 the oscillator frequency, and can be used for external timing or clocking.

Note that one ALE pulse is skipped during each access to external data memory. ALE is

switched off if the bit 0 in the AUXR register (8EH) is set. This pin is also the program pulse

input (PROG

) during EPROM programming.

PSEN 29 32 26 O Program Store Enable: The read strobe to external program memory. When the device is

executing code from the external program memory, PSEN is activated twice each machine

cycle, except that two PSEN

activations are skipped during each access to external data

memory. PSEN

is not activated during fetches from internal program memory.

EA/V

PP

31 35 29 I External Access Enable/Programming Supply Voltage: EA must be externally held low

to enable the device to fetch code from external program memory locations 0000H to

1FFFH. If EA

is held high, the device executes from internal program memory unless the

program counter contains an address greater than 1FFFH. This pin also receives the

12.75V programming supply voltage (V

PP

) during EPROM programming.

XTAL1 19 21 15 I Crystal 1: Input to the inverting oscillator amplifier and input to the internal clock generator

circuits.

XTAL2 18 20 14 O Crystal 2: Output from the inverting oscillator amplifier.

Philips Semiconductors Product specification

80C575/83C575/

87C575

80C51 8-bit microcontroller family

8K/256 OTP/ROM/ROMless, 4 comparator, failure detect circuitry, watchdog timer

1998 May 01

7

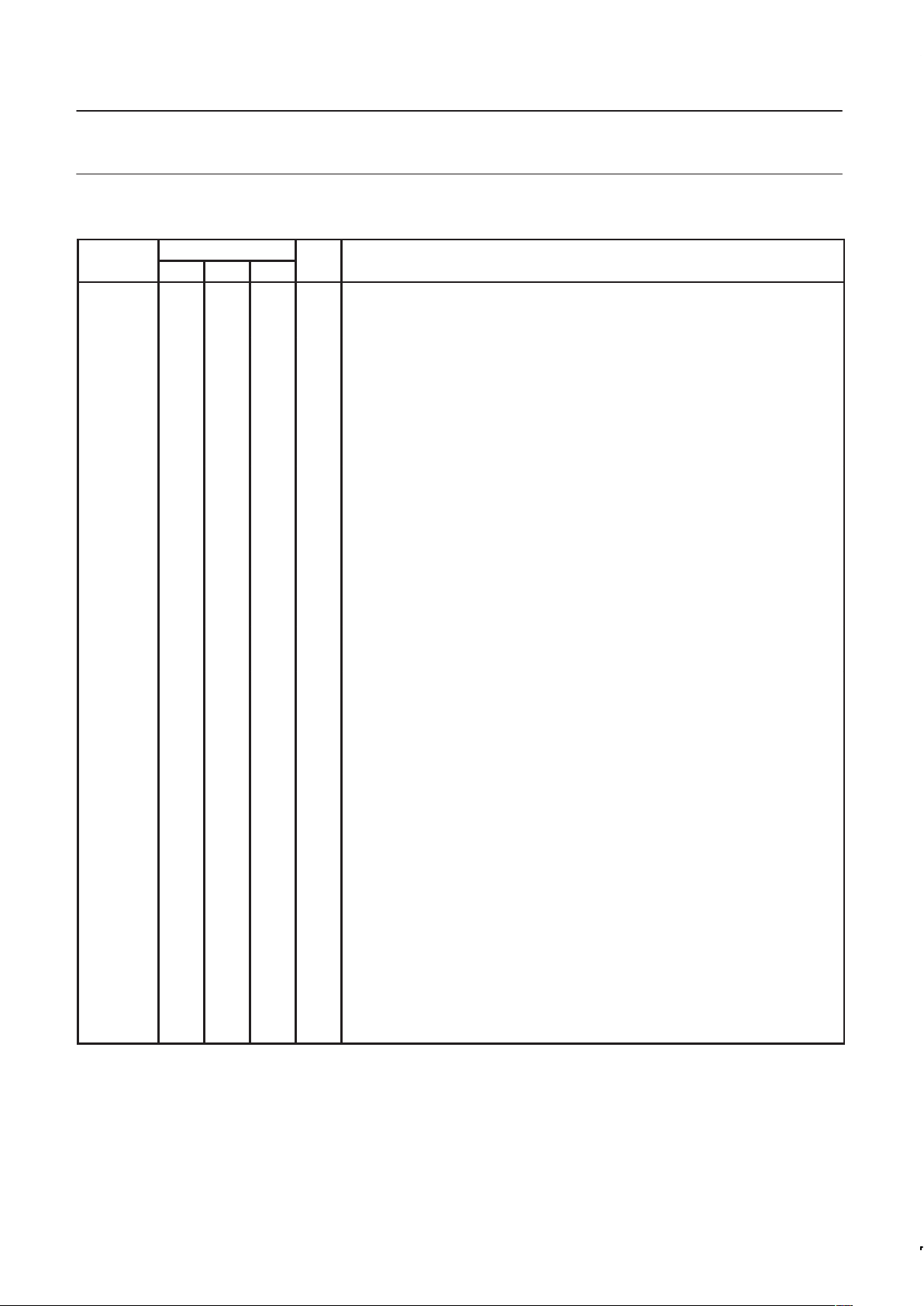

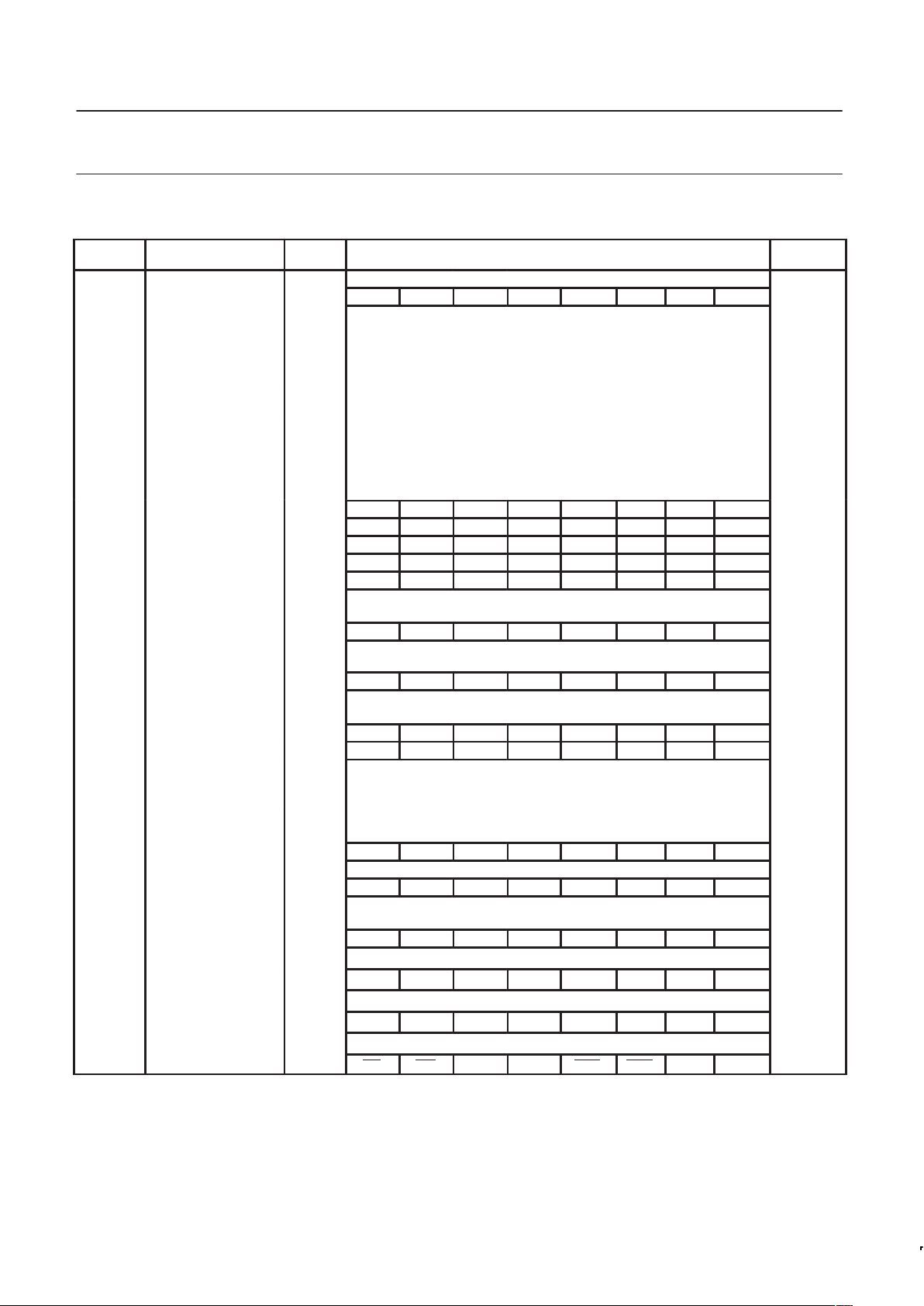

Table 1. 87C575 Special Function Registers

SYMBOL DESCRIPTION

DIRECT

ADDRESS

BIT ADDRESS, SYMBOL, OR ALTERNATIVE PORT FUNCTION

MSB LSB

RESET

VALUE

ACC* Accumulator E0H E7 E6 E5 E4 E3 E2 E1 E0 00H

AUXR# Auxiliary 8EH – – – – – – LO AO xxxxxx00B

B* B register F0H F7 F6 F5 F4 F3 F2 F1 F0 00H

CCAP0H# Module 0 Capture High FAH xxxxxxxxB

CCAP1H# Module 1 Capture High FBH xxxxxxxxB

CCAP2H# Module 2 Capture High FCH xxxxxxxxB

CCAP3H# Module 3 Capture High FDH xxxxxxxxB

CCAP4H# Module 4 Capture High FEH xxxxxxxxB

CCAP0L# Module 0 Capture Low EAH xxxxxxxxB

CCAP1L# Module 1 Capture Low EBH xxxxxxxxB

CCAP2L# Module 2 Capture Low ECH xxxxxxxxB

CCAP3L# Module 3 Capture Low EDH xxxxxxxxB

CCAP4L# Module 4 Capture Low EEH xxxxxxxxB

CCAPM0# Module 0 Mode DAH – ECOM CAPP CAPN MAT TOG PWM ECCF x0000000B

CCAPM1# Module 1 Mode DBH – ECOM CAPP CAPN MAT TOG PWM ECCF x0000000B

CCAPM2# Module 2 Mode DCH – ECOM CAPP CAPN MAT TOG PWM ECCF x0000000B

CCAPM3# Module 3 Mode DDH – ECOM CAPP CAPN MAT TOG PWM ECCF x0000000B

CCAPM4# Module 4 Mode DEH – ECOM CAPP CAPN MAT TOG PWM ECCF x0000000B

DF DE DD DC DB DA D9 D8

CCON*# PCA Counter Control D8H CF CR – CCF4 CCF3 CCF2 CCF1 CCF0 00x00000B

CH# PCA Counter High F9H 00H

CL# PCA Counter Low E9H 00H

CMOD# PCA Counter Mode D9H CIDL WDTE – – – CPS1 CPS0 ECF 00xxx000B

EF EE ED EC EB EA E9 E8

CMP*# Comparator E8H EC3DP EC2DP EC1DP EC0DP C3RO C2RO C1RO C0RO 00H

CMPE# Comparator Enable 91H

EC3TDC EC2TDC EC1TDC EC0TDC EC3OD EC2OD EC1OD EC0OD

00H

DPTR: Data Pointer (2 bytes)

DPH Data Pointer High 83H 00H

DPL Data Pointer Low 82H 00H

AF AE AD AC AB AA A9 A8

IE* Interrupt Enable A8H EA EC ET2 ES ET1 EX1 ET0 EX0 00H

BF BE BD BC BB BA B9 B8

IP* Interrupt Priority B8H – PPC PT2 PS PT1 PX1 PT0 PX0 x0000000B

87 86 85 84 83 82 81 80

P0* Port 0 80H AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 00H

97 96 95 94 93 92 91 90

P1* Port 1 90H CEX4 CEX3 CEX2 CEX1 CEX0 EXI T2EX T2 00H

A7 A6 A5 A4 A3 A2 A1 A0

P2* Port 2 A0H AD15 AD14 AD13 AD12 AD11 AD10 AD9 AD8 00H

B7 B6 B5 B4 B3 B2 B1 B0

P3* Port 3 B0H RD WR T1 T0 INT1 INT0 TxD RxD 00H

* SFRs are bit addressable.

# SFRs are modified from or added to the 80C51 SFRs.

1. 87C575 only.

Philips Semiconductors Product specification

80C575/83C575/

87C575

80C51 8-bit microcontroller family

8K/256 OTP/ROM/ROMless, 4 comparator, failure detect circuitry, watchdog timer

1998 May 01

8

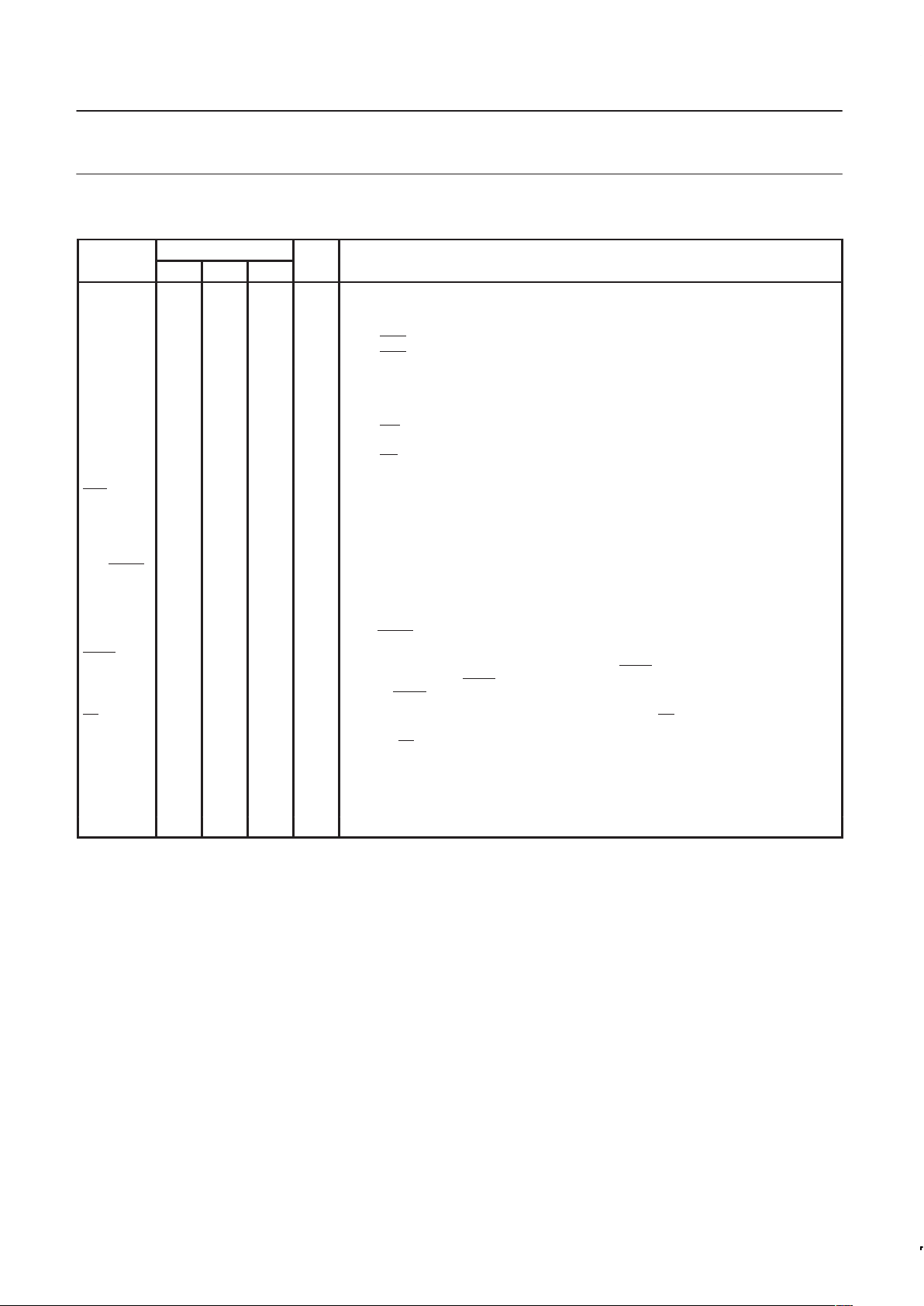

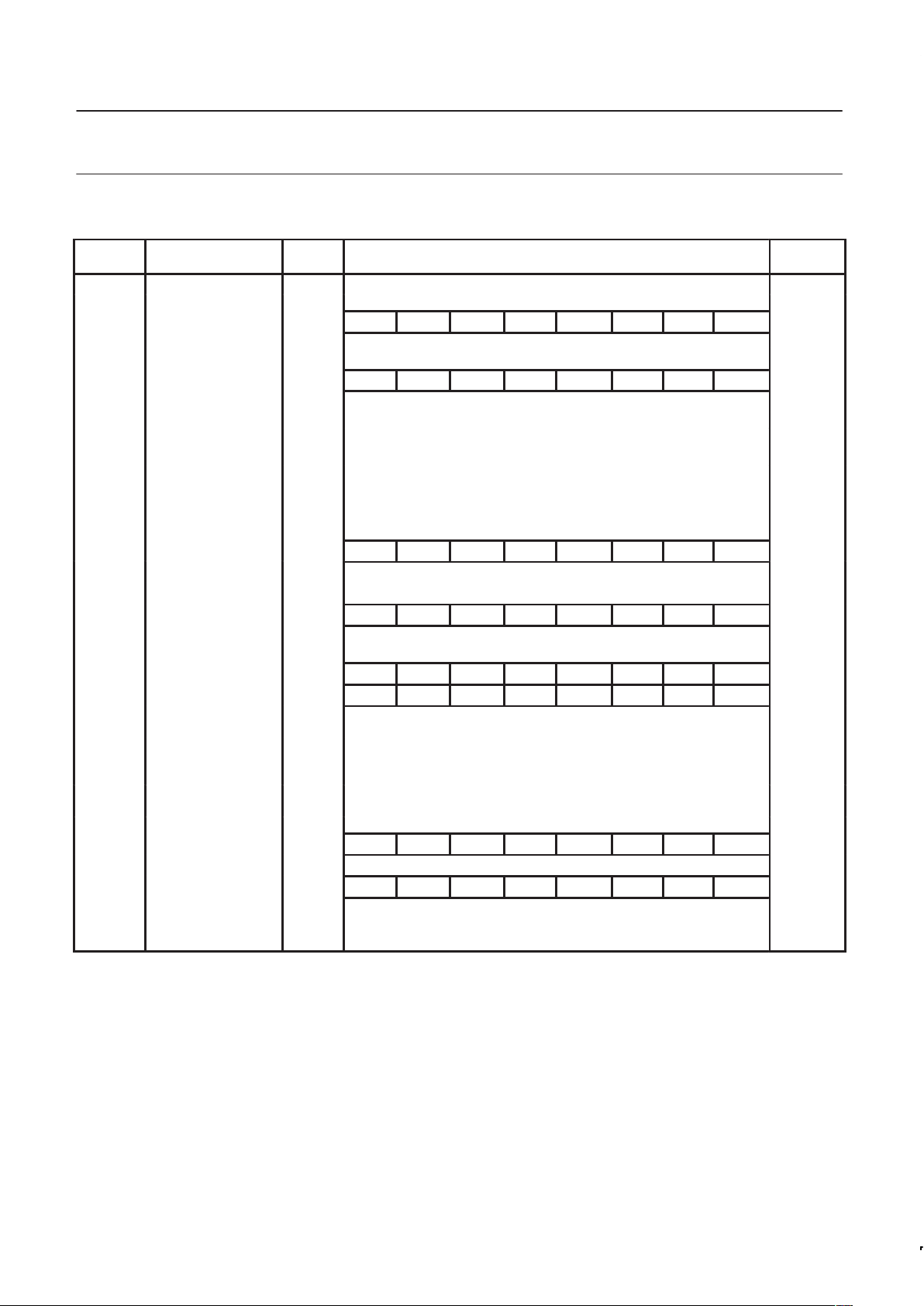

Table 1. 87C575 Special Function Registers (Continued)

SYMBOL DESCRIPTION

DIRECT

ADDRESS

BIT ADDRESS, SYMBOL, OR ALTERNATIVE PORT FUNCTION

MSB LSB

RESET

VALUE

P2OD# Port 2 Pullup Disable A1H 00H

PCON# Power Control 87H

SMOD1 SMOD0

OSF1POF1LVF

1

GF0 PD IDL 00xxx000B

D7 D6 D5 D4 D3 D2 D1 D0

PSW* Program Status Word D0H CY AC F0 RS1 RS0 OV – P 00H

RACAP2H#

Timer 2 Capture High CBH 00H

RACAP2L

# Timer 2 Capture Low CAH 00H

SADDR# Slave Address A9H 00H

SADEN# Slave Address Mask B9H 00H

SBUF Serial Data Buffer 99H xxxxxxxxB

9F 9E 9D 9C 9B 9A 99 98

SCON* Serial Control 98H SM0 SM1 SM2 REN TB8 RB8 TI RI 00H

SP Stack Pointer 81H 07H

8F 8E 8D 8C 8B 8A 89 88

TCON* Timer Control 88H TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0 00H

CF CE CD CC CB CA C9 C8

T2CON* Timer 2 Control C8H TF2 EXF2 RCLK TCLK EXEN2 TR2 C/T2 CP/RL2 00H

T2MOD# Timer 2 Mode Control C9H – – – – – – T2OE2DCEN xxxxxxx0B

TH0 Timer High 0 8CH 00H

TH1 Timer High 1 8DH 00H

TH2# Timer High 2 CDH 00H

TL0 Timer Low 0 8AH 00H

TL1 Timer Low 1 8BH 00H

TL2# T imer Low 2 CCH 00H

TMOD Timer Mode 89H GA TE C/T M1 M0 GA TE C/T M1 M0 00H

C7 C6 C5 C4 C3 C2 C1 C0

WDCON*#Watchdog Timer Control

C0H PRE2 PRE1 PRE0 LVRE OFRE

WDRUN WDTOF WDMOD

11111101B

WDL#

Watchdog Timer Reload

C1H 00H

WFEED1# Watchdog Feed 1 C2H xxH

WFEED2# Watchdog Feed 2 C3H xxH

* SFRs are bit addressable.

# SFRs are modified from or added to the 80C51 SFRs.

1. Reset value depends on reset source.

2. Programmable clock-out.

Philips Semiconductors Product specification

80C575/83C575/

87C575

80C51 8-bit microcontroller family

8K/256 OTP/ROM/ROMless, 4 comparator, failure detect circuitry, watchdog timer

1998 May 01

9

POWER ON CLEAR/

POWER ON FLAG

An on-chip Power On Detect Circuit resets

the 8XC575 and sets the Power Off Flag

(PCON.4) on power up or if V

CC

drops to

zero momentarily. The POF can only be

cleared by software. The RST pin is not

driven by the power on detect circuit. The

POF can be read by software to determine

that a power failure has occurred and can

also be set by software.

LOW VOLTAGE DETECT

An on-chip Low Voltage Detect circuit sets

the Low Voltage Flag (PCON.3) if V

CC

drops

below V

LOW

(see DC Electrical

Characteristics) and resets the 8XC575 if the

Low Voltage Reset Enable bit (WDCON.4) is

set. If the LVRE is cleared, the reset is

disabled but L VF will still be set if V

CC

is low.

The RST pin is not driven by the low voltage

detect circuit. The LVF can be read by

software to determine that V

CC

was low. The

LVF can be set or cleared by software.

OSCILLATOR FAIL DETECT

An on-chip Oscillator Fail Detect circuit sets

the Oscillator Fail Flag (PCON.5) if the

oscillator frequency drops below OSCF for

one or more cycles (see AC Electrical

Characteristics: OSCF) and resets the

8XC575 if the Oscillator Fail Reset Enable bit

(WDCON.3) is set. If OFRE is cleared, the

reset is disabled but OSF will still be set if the

oscillator fails. The RST pin is not driven by

the oscillator fail detect circuit. The OSF can

be read by software to determine that an

oscillator failure has occurred. The OSF can

be set or cleared by software.

LOW ACTIVE RESET

One of the most notable features on this part

is the low active reset. At this time this is the

only 80C51 derivative available that has low

active reset. This feature makes it easier to

interface the 8XC575 into an application to

accommodate the power-on and low voltage

conditions that can occur. The low active

reset operates exactly the same as high

active reset with the exception that the part is

put into the reset mode by applying a low

level to the reset pin. For power-on reset it is

also necessary to invert the power-on reset

circuit; connecting the 8.2K resistor from the

reset pin to V

CC

and the 10µf capacitor from

the reset pin to ground. Figure 1 shows all of

the reset related circuitry.

When reset the port pins on the 87C575 are

driven low asynchronously. This is different

from all other 80C51 derivatives.

The 8XC575 also has Low voltage detection

circuitry that will, if enabled, force the part to

reset when V

CC

(on the part) fails below a set

level. Low Voltage Reset is enabled by a

normal reset. Low Voltage Reset can be

disabled by clearing LVRE (bit 4 in the

WDCON SFR) then executing a watchdog

feed sequence (A5H to WFEED1 followed

immediately by 5A to WFEED2). In addition

there is a flag (LVF) that is set if a low voltage

condition is detected. The LVF flag is set

even if the Low Voltage detection circuitry is

disabled. Notice that the Low voltage

detection circuitry does not drive the RST#

pin so the LVF flag is the only way that the

microcontroller can determine if it has been

reset due to a low voltage condition.

The 8XC575 has an on-chip power-on

detection circuit that sets the POF (PCON.4)

flag on power up or if the V

CC

level

momentarily drops to 0V. This flag can be

used to determine if the part is being started

from a power-on (cold start) or if a reset has

occurred due to another condition (warm

start).

TIMERS

The 87C575 has four on-chip timers.

Timers 0 and 1 are identical in every way to

Timers 0 and 1 on the 80C51.

Timer 2 on the 8XC575 is identical to the

80C52 Timer 2 (described in detail in the

80C52 overview) with the exception that it is

an up or down counter. To configure the

Timer to count down the DCEN bit in the

T2MOD special function register must be set

and a low level must be present on the T2EX

pin (P1.1).

The Watchdog timer operation and

implementation is the same as that for the

8XC550 (described in the 8XC550 overview)

with the exception that the reset values of the

WDCON and WDL special function registers

have been changed. The changes in these

registers cause the watchdog timer to be

enabled with a timeout of 98304 × T

OSC

when the part is reset. The watchdog can be

disabled by executing a valid feed sequence

and then clearing WDRUN (bit 2 in the

WDCON SFR).

PRE2 PRE1 PRE0 LVRE OFRE WDRUN WDTOF WDMOD

WDCON

(C0H)

SHADOW REGISTER

FOR WDCON

WATCHDOG FEED

SMOD1 SMOD0 OSF LVF GF0 GF1 IDL

PCON

(87GH)

OSC FREQ BELOW OSCF

(MIN FREQUENCY)

RST

+

–

V

CC

VLOW

(LOW V

CC

REFERENCE)

POWER-ON DETECT

PCA WATCHDOG

WATCHDOG TIMER

8xC575

INTERNAL

RESET

POF

SU00239

Figure 1. Reset Circuitry

Philips Semiconductors Product specification

80C575/83C575/

87C575

80C51 8-bit microcontroller family

8K/256 OTP/ROM/ROMless, 4 comparator, failure detect circuitry, watchdog timer

1998 May 01

10

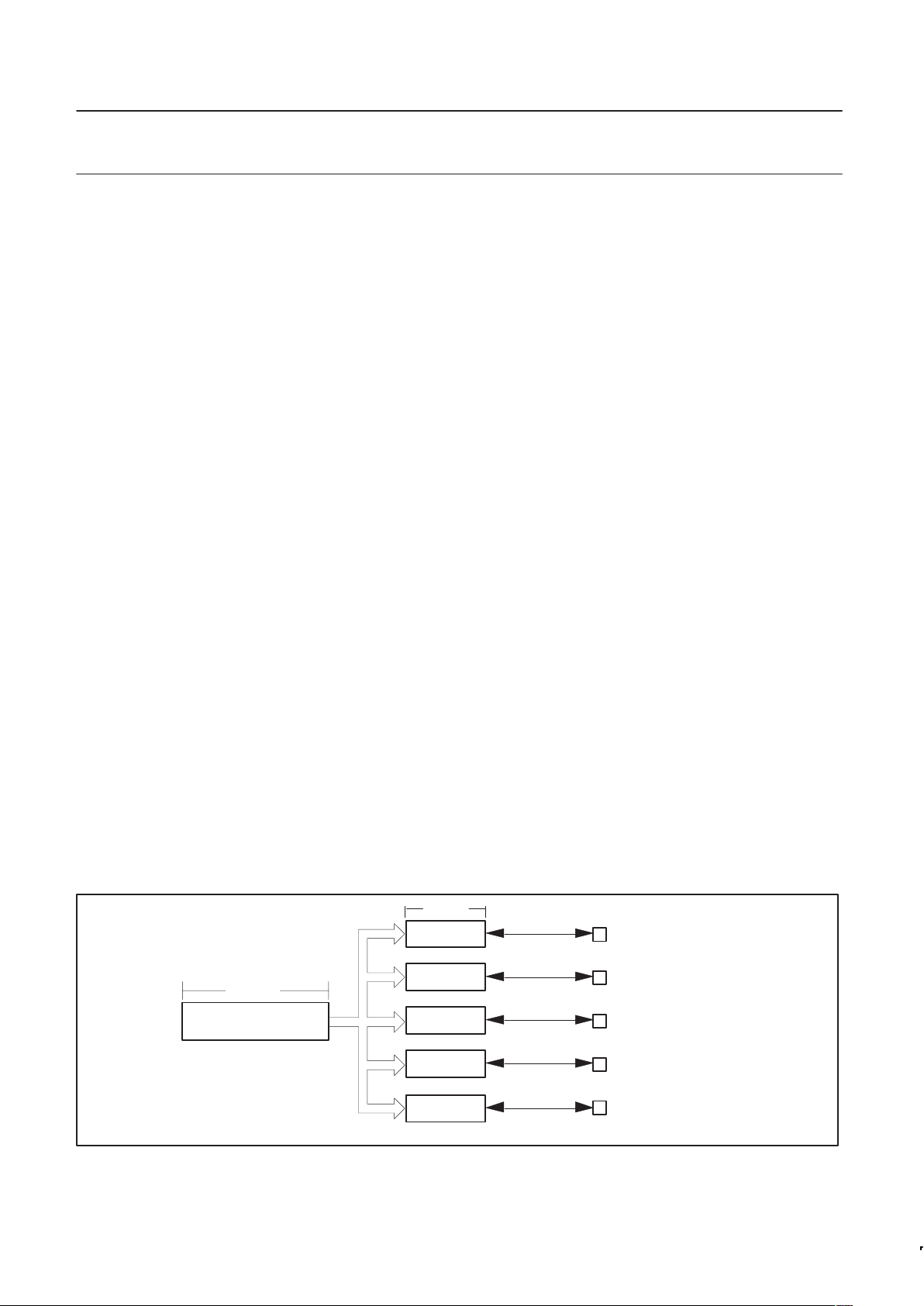

PROGRAMMABLE COUNTER

ARRAY (PCA)

The Programmable Counter Array is a

special Timer that has five 16-bit

capture/compare modules associated with it.

Each of the modules can be programmed to

operate in one of four modes: rising and/or

falling edge capture, software timer,

high-speed output, or pulse width modulator.

Each module has a pin associated with it in

port 1. Module 0 is connected to P1.3(CEX0),

module 1 to P1.4(CEX1), etc.. The basic

PCA configuration is shown in Figure 2.

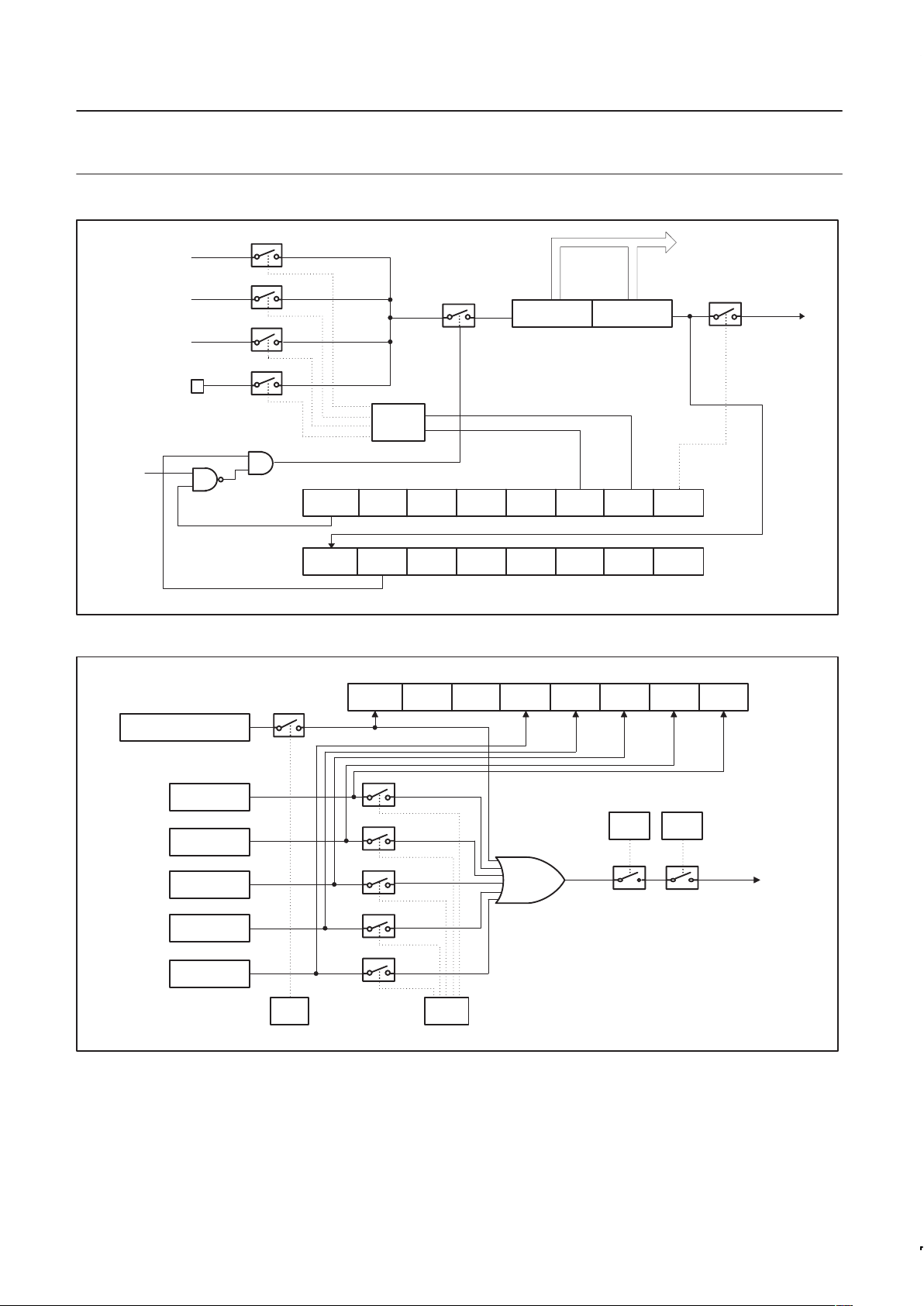

The PCA timer is a common time base for all

five modules and can be programmed to run

at: 1/12 the oscillator frequency, 1/4 the

oscillator frequency , the Timer 0 overflow, or

the input on the ECI pin (P1.2). The timer

count source is determined from the CPS1

and CPS0 bits in the CMOD SFR as follows

(see Figure 3):

CPS1 CPS0 PCA Timer Count Source

0 0 1/12 oscillator frequency

0 1 1/4 oscillator frequency

1 0 Timer 0 overflow

1 1 External Input at ECI pin

In the CMOD SFR are three additional bits

associated with the PCA. They are CIDL

which allows the PCA to stop during idle

mode, WDTE which enables or disables the

watchdog function on module 4, and ECF

which when set causes an interrupt and the

PCA overflow flag CF (in the CCON SFR) to

be set when the PCA timer overflows. These

functions are shown in Figure 3.

The watchdog timer function is implemented

in module 4 as implemented in other parts

that have a PCA that are available on the

market. However, if a watchdog timer is

required in the target application, it is

recommended to use the hardware watchdog

timer that is implemented on the 87C575

separately from the PCA (see Figure 14).

The CCON SFR contains the run control bit

for the PCA and the flags for the PCA timer

(CF) and each module (refer to Figure 6). To

run the PCA the CR bit (CCON.6) must be

set by software. The PCA is shut off by

clearing this bit. The CF bit (CCON.7) is set

when the PCA counter overflows and an

interrupt will be generated if the ECF bit in

the CMOD register is set, The CF bit can only

be cleared by software. Bits 0 through 4 of

the CCON register are the flags for the

modules (bit 0 for module 0, bit 1 for module

1, etc.) and are set by hardware when either

a match or a capture occurs. These flags

also can only be cleared by software. The

PCA interrupt system shown in Figure 4.

Each module in the PCA has a special

function register associated with it. These

registers are: CCAPM0 for module 0,

CCAPM1 for module 1, etc. (see Figure 7).

The registers contain the bits that control the

mode that each module will operate in. The

ECCF bit (CCAPMn.0 where n=0, 1, 2, 3, or

4 depending on the module) enables the CCF

flag in the CCON SFR to generate an

interrupt when a match or compare occurs in

the associated module. PWM (CCAPMn.1)

enables the pulse width modulation mode.

The TOG bit (CCAPMn.2) when set causes

the CEX output associated with the module to

toggle when there is a match between the

PCA counter and the module’s

capture/compare register . The match bit MAT

(CCAPMn.3) when set will cause the CCFn

bit in the CCON register to be set when there

is a match between the PCA counter and the

module’s capture/compare register .

The next two bits CAPN (CCAPMn.4) and

CAPP (CCAPMn.5) determine the edge that

a capture input will be active on. The CAPN

bit enables the negative edge, and the CAPP

bit enables the positive edge. If both bits are

set both edges will be enabled and a capture

will occur for either transition. The last bit in

the register ECOM (CCAPMn.6) when set

enables the comparator function. Figure 8

shows the CCAPMn settings for the various

PCA functions.

There are two additional registers associated

with each of the PCA modules. They are

CCAPnH and CCAPnL and these are the

registers that store the 16-bit count when a

capture occurs or a compare should occur.

When a module is used in the PWM mode

these registers are used to control the duty

cycle of the output.

PCA Capture Mode

To use one of the PCA modules in the

capture mode either one or both of the

CCAPM bits CAPN and CAPP for that

module must be set. The external CEX input

for the module (on port 1) is sampled for a

transition. When a valid transition occurs the

PCA hardware loads the value of the PCA

counter registers (CH and CL) into the

module’s capture registers (CCAPnL and

CCAPnH). If the CCFn bit for the module in

the CCON SFR and the ECCFn bit in the

CCAPMn SFR are set then an interrupt will

be generated. Refer to Figure 9.

16-bit Software Timer Mode

The PCA modules can be used as software

timers by setting both the ECOM and MAT

bits in the modules CCAPMn register. The

PCA timer will be compared to the module’s

capture registers and when a match occurs

an interrupt will occur if the CCFn (CCON

SFR) and the ECCFn (CCAPMn SFR) bits for

the module are both set (see Figure 10).

High Speed Output Mode

In this mode the CEX output (on port 1)

associated with the PCA module will toggle

each time a match occurs between the PCA

counter and the module’s capture registers.

To activate this mode the TOG, MAT, and

ECOM bits in the module’s CCAPMn SFR

must be set (see Figure 11).

MODULE FUNCTIONS:

16-BIT CAPTURE

16-BIT TIMER

16-BIT HIGH SPEED OUTPUT

8-BIT PWM

WATCHDOG TIMER (MODULE 4 ONLY)

MODULE 0

MODULE 1

MODULE 2

MODULE 3

MODULE 4

P1.3/CEX0

P1.4/CEX1

P1.5/CEX2

P1.6/CEX3

P1.7/CEX4

16 BITS

PCA TIMER/COUNTER

TIME BASE FOR PCA MODULES

16 BITS

SU00032

Figure 2. Programmable Counter Array (PCA)

Philips Semiconductors Product specification

80C575/83C575/

87C575

80C51 8-bit microcontroller family

8K/256 OTP/ROM/ROMless, 4 comparator, failure detect circuitry, watchdog timer

1998 May 01

11

CF CR CCF4 CCF3 CCF2 CCF1 CCF0––

CCON

(D8H)

CH CL

OVERFLOW

INTERRUPT

16–BIT UP COUNTER

IDLE

TO PCA

MODULES

CMOD

(D9H)

CIDL WDTE –– –– –– CPS1 CPS0 ECF

OSC/12

OSC/4

TIMER 0

OVERFLOW

EXTERNAL INPUT

(P1.2/ECI)

DECODE

00

01

10

11

SU00033

Figure 3. PCA Timer/Counter

MODULE 0

MODULE 1

MODULE 2

MODULE 3

MODULE 4

PCA TIMER/COUNTER

CF CR CCF4 CCF3 CCF2 CCF1 CCF0––

CMOD.0 ECF

CCAPMn.0 ECCFn

TO

INTERRUPT

PRIORITY

DECODER

CCON

(D8H)

IE.6

EC

IE.7

EA

SU00034

Figure 4. PCA Interrupt System

Philips Semiconductors Product specification

80C575/83C575/

87C575

80C51 8-bit microcontroller family

8K/256 OTP/ROM/ROMless, 4 comparator, failure detect circuitry, watchdog timer

1998 May 01

12

CMOD Address = OD9H

Reset Value = 00XX X000B

CIDL WDTE – – – CPS1 CPS0 ECF

Bit:

Symbol Function

CIDL Counter Idle control: CIDL = 0 programs the PCA Counter to continue functioning during idle Mode. CIDL = 1 programs

it to be gated off during idle.

WDTE Watchdog Timer Enable: WDTE = 0 disables Watchdog Timer function on PCA Module 4. WDTE = 1 enables it.

– Not implemented, reserved for future use.*

CPS1 PCA Count Pulse Select bit 1.

CPS0 PCA Count Pulse Select bit 0.

CPS1 CPS0 Selected PCA Input**

0 0 0 Internal clock, f

OSC

÷ 12

0 1 1 Internal clock, f

OSC

÷ 4

1 0 2 Timer 0 overflow

1 1 3 External clock at ECI/P1.2 pin (max. rate = f

OSC

÷ 8)

ECF PCA Enable Counter Overflow interrupt: ECF = 1 enables CF bit in CCON to generate an interrupt. ECF = 0 disables

that function of CF.

NOTE:

* User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new features. In that case, the reset or inactive value of the

new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

** f

OSC

= oscillator frequency

SU00035

76543210

Figure 5. CMOD: PCA Counter Mode Register

CCON Address = OD8H

Reset Value = 00X0 0000B

CF CR – CCF4 CCF3 CCF2 CCF1 CCF0

Bit Addressable

Bit:

Symbol Function

CF PCA Counter Overflow flag. Set by hardware when the counter rolls over. CF flags an interrupt if bit ECF in CMOD is

set. CF may be set by either hardware or software but can only be cleared by software.

CR PCA Counter Run control bit. Set by software to turn the PCA counter on. Must be cleared by software to turn the PCA

counter off.

– Not implemented, reserved for future use*.

CCF4 PCA Module 4 interrupt flag. Set by hardware when a match or capture occurs. Must be cleared by software.

CCF3 PCA Module 3 interrupt flag. Set by hardware when a match or capture occurs. Must be cleared by software.

CCF2 PCA Module 2 interrupt flag. Set by hardware when a match or capture occurs. Must be cleared by software.

CCF1 PCA Module 1 interrupt flag. Set by hardware when a match or capture occurs. Must be cleared by software.

CCF0 PCA Module 0 interrupt flag. Set by hardware when a match or capture occurs. Must be cleared by software.

NOTE:

* User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new features. In that case, the reset or inactive value of the

new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

SU00036

76543210

Figure 6. CCON: PCA Counter Control Register

Loading...

Loading...