查询P80C557E4供应商查询P80C557E4供应商

INTEGRATED CIRCUITS

P83C557E4/P80C557E4/P89C557E4

Single-chip 8-bit microcontroller

Product specification 1999 Mar 02

Supersedes data of 1999 Feb 15

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

1. FEATURES

• 80C51 central processing unit

• 32 K × 8 ROM respectively FEEPROM (Flash-EEPROM),

expandable externally to 64 Kbytes

• ROM/FEEPROM Code protection

• 1024 × 8 RAM, expandable externally to 64 Kbytes

• Two standard 16-bit timer/counters

• An additional 16-bit timer/counter coupled to four capture

registers and three compare registers

• A 10-bit ADC with eight multiplexed analog inputs and

programmable autoscan

• Two 8-bit resolution, pulse width modulation outputs

• Five 8-bit I/O ports plus one 8-bit input port shared with analog

inputs

2

• I

C-bus serial I/O port with byte oriented master and slave

functions

• Full-duplex UART compatible with the standard 80C51

• On-chip watchdog timer

• 15 interrupt sources with 2 priority levels (2 to 6 external sources

possible)

• Extended temperature range (–40 to +85°C)

• 4.5 to 5.5 V supply voltage range

• Frequency range for 80C51-family standard oscillator:

3.5 MHz to 16 MHz

• PLL oscillator with 32 kHz reference and software-selectable

system clock frequency

• Seconds Timer

• Software enable/disable of ALE output pulse

• Electromagnetic compatibility improvements

• Wake-up from Power-down by external or seconds interrupt

2. GENERAL DESCRIPTION

The P80C557E4/P83C557E4/P89C557E4 (hereafter generically

referred to as P8xC557E4) single-chip 8-bit microcontroller is

manufactured in an advanced CMOS process and is a derivative of

the 80C51 microcontroller family. The P8xC557E4 has the same

instruction set as the 80C51. Three versions of the derivative exist:

• P83C557E4 — 32 Kbytes mask programmable ROM

• P80C557E4 — ROMless version of the P83C557E4

• P89C557E4 — 32 Kbytes FEEPROM (Flash-EEPROM)

The P8xC557E4 contains a non-volatile 32 Kbytes mask

programmable ROM (P83C557E4) or electrically erasable

FEEPROM respectively (P89C557E4), a volatile 1024 × 8 read/write

data memory , five 8-bit I/O ports, one 8-bit input port, two 16-bit

timer/event counters (identical to the timers of the 80C51), an

additional 16-bit timer coupled to capture and compare latches, a

15-source, two-priority-level, nested interrupt structure, an 8-input

ADC, a dual DAC pulse width modulated interface, two serial

interfaces (UART and I2C-bus), a “watchdog” timer, an on-chip

oscillator and timing circuits. For systems that require extra

capability the P8xC557E4 can be expanded using standard TTL

compatible memories and logic.

In addition, the P8xC557E4 has two software selectable modes of

power reduction — Idle Mode and power-down mode. The Idle

Mode freezes the CPU while allowing the RAM, timers, serial ports,

and interrupt system to continue functioning. The power-down mode

saves the RAM contents but freezes the oscillator, causing all other

chip functions to be inoperative.

The device also functions as an arithmetic processor having

facilities for both binary and BCD arithmetic as well as bit-handling

capabilities. The instruction set consists of over 100 instructions: 49

one-byte, 45 two-byte, and 17 three- byte. With a 16 MHz system

clock, 58% of the instructions are executed in 0.75 µs and 40% in

1.5 µs. Multiply and divide instructions require 3 µs.

1999 Mar 02

2

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

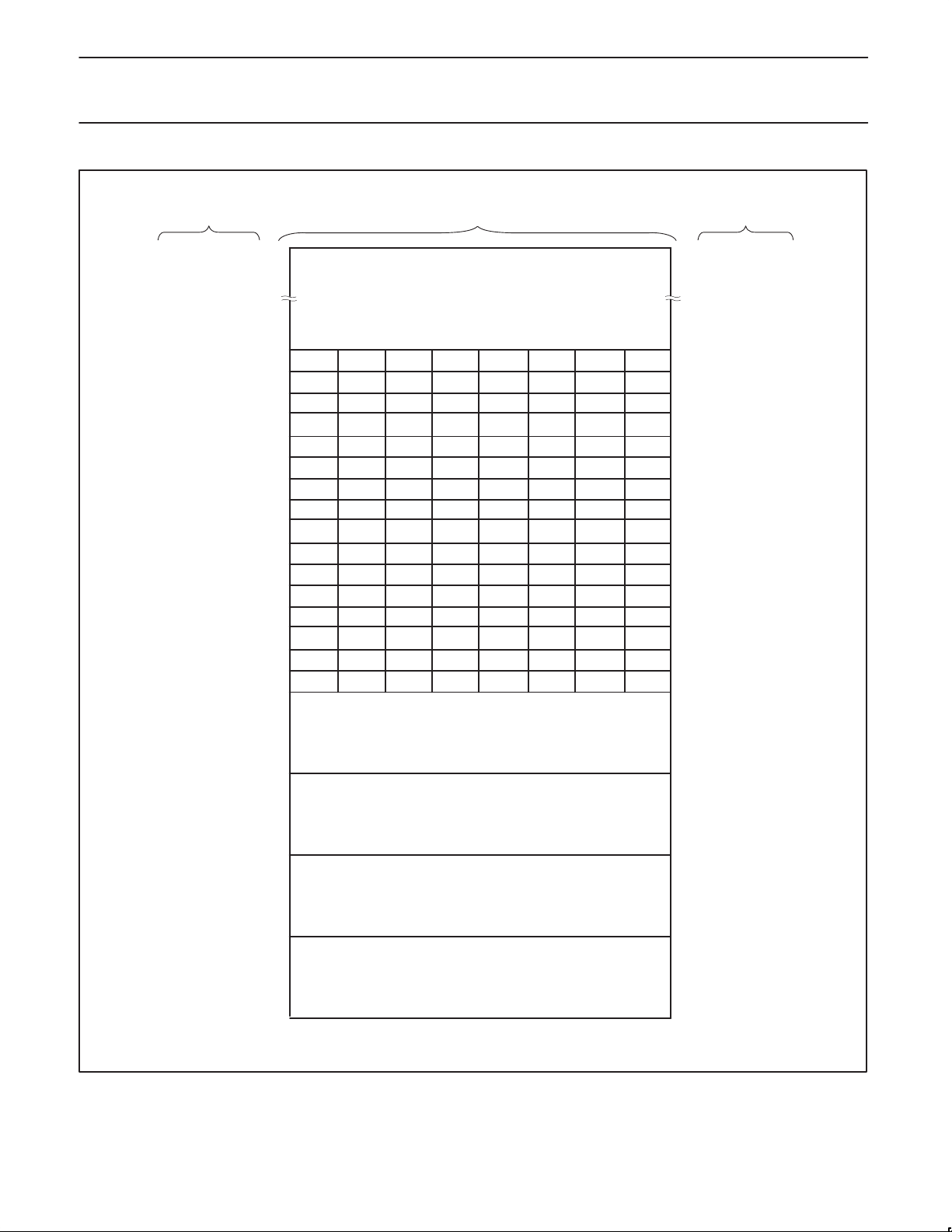

3. ORDERING INFORMATION

EXTENDED TYPE

NUMBER

NAME DESCRIPTION CODE

PACKAGE

FREQUENCY RANGE TEMPERATURE

(MHz) RANGE (°C)

ROMless

P80C557E4EBB QFP80 Plastic Quad Flat Pack; 80 leads SOT318-1 3.5 to 16 0 to +70

P80C557E4EFB QFP80 Plastic Quad Flat Pack; 80 leads SOT318-1 3.5 to 16 –40 to +85

ROM coded

P83C557E4EBB/YYY

P83C557E4EFB/YYY

1

1

QFP80 Plastic Quad Flat Pack; 80 leads SOT318-1 3.5 to 16 0 to +70

QFP80 Plastic Quad Flat Pack; 80 leads SOT318-1 3.5 to 16 –40 to +85

FEEPROM

P89C557E4EBB QFP80 Plastic Quad Flat Pack; 80 leads SOT318-1 3.5 to 16 0 to +70

P89C557E4EFB QFP80 Plastic Quad Flat Pack; 80 leads SOT318-1 3.5 to 16 –40 to +85

NOTE:

1.

YYY denotes the ROM code number

SELXTAL1

RSTIN

XTAL1

XTAL2

EA

ALE

PSEN

3

WR

3

RD

T0 T1 INT0 INT1

3 3 3 3

T0, T1

TWO 16-BIT

TIMER/EVENT

COUNTERS

80C51 CORE

EXCLUDING

ROM/RAM

CPU

V

DD

PROGRAM

MEMORY

32 K x 8 ROM

/FEEPROM,

6 7

1 K x 8

boot ROM

8-BIT INTERNAL BUS

V

SS

DATA

MEMORY

256 x 8 RAM

768 x 8 RAM

+

PWM0 PWM1

DUAL

PWM

AV

REF

–

ADEXS

ADC

ADC0-7 SDA SCL

5

2

C

I

SERIAL

I/O

AV

SS

+

AV

DD

0

AD0-7

2

A8-15

0

ALTERNATE FUNCTION OF PORT0

1

ALTERNATE FUNCTION OF PORT1

2

ALTERNATE FUNCTION OF PORT2

EXTERNAL BUS

P0 P1 P2 P3 TxD RxD P5 P4 CT0I-CT3I T2 RT2

1999 Mar 02

PARALLEL I/O

PORTS AND

SERIAL

UART

PORT

3 3

3

4

5

8-BIT

PORTS

ALTERNATE FUNCTION OF PORT 3

ALTERNATE FUNCTION OF PORT 4

ALTERNATE FUNCTION OF PORT 5

Figure 1. Block diagram P8xC557E4

16

COMPARA-

REGISTERS

T2

16-BIT

TORS

WITH

FOUR

16-BIT

CAPTURE

LATCHES

1 1 1 4

T2

16

16-BIT

TIMER/

EVENT

COUNT-

ERS

6

NOT PRESENT IN P80C557E4

7

ONLY PRESENT IN P89C557E4

3

COMPARA-

TOR

OUTPUT

SELECTION

CMSR0-CMSR5

CMT0, CMT1

T3

WATCH–

DOG

TIMER

RSTOUT

XTAL3 XTAL4

EW

PLL

oscillator

+

”seconds”

timer

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

ADC0-7

CMSR0-5

CMT0

CMT1

RSTOUT

V

SS

V

DD

XTAL1

XTAL2

EA

ALE/WE

PSEN

AV

SS

AV

DD

AVref+

AVref–

ADEXS

PWM0

PWM1

SCL

SDA

PORT 5

PORT 4

RSTIN

EW

XTAL3

XTAL4

SELXTAL1

0

1

2

*

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

P8xC557E4

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

PORT 0

PORT 1PORT 2PORT 3

0

1

2

3

4

5

6

7

CT0I/INT2

CT1I/INT3

CT2I/INT4

CT3I/INT5

T2

RT2

HIGH ORDER ADDRESS BUS

A8–15

RXD/DATA

TXD/CLOCK

INT0

INT1

T0

T1

WR

RD

LOW ORDER ADDRESS

AND DATA BUS AD0–7

1999 Mar 02

*) only P89C557E4 with alternate function WE

Figure 2. Functional diagram

4

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

4. PINNING

DD2

SELXTAL1

80

XTAL4

79

XTAL3

78

SS2

AV

77

AV

76

P0.0/AD0

P0.1/AD1

75

74

P0.2/AD2

P0.3/AD3

73

72

P0.4/AD4

P0.5/AD5

71

70

P0.6/AD6

69

SS4VDD4

P0.7/AD7

68

67

EA

V

66

65

AV

ref–

AV

ref+

AV

SS

1

AV

DD1

P5.7/ADC7

P5.6/ADC6

P5.5/ADC5

P5.4/ADC4

P5.3/ADC3

P5.2/ADC2

P5.1/ADC1

P5.0/ADC0

V

SS1

V

DD1

ADEXS

PWM0

PWM1

EW

P4.0/CMSR0

P4.1/CMSR1

P4.2/CMSR2

P4.3/CMSR3

RSTOUT

P4.4/CSMR4

11

10

12

13

14

15

16

17

18

19

20

21

22

23

24

1

2

3

4

5

6

7

8

9

P8xC557E4

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

ALE/WE

PSEN

P2.7/A15

P2.6/A14

P2.5/A13

P2.4/A12

P2.3/A11

P2.2/A10

P2.1/A9

P2.0/A8

V

SS3

V

DD3

XTAL1

XTAL2

n.c.

n.c.

P3.7/RD

P3.6/WR

P3.5/T1

P3.4/T0

P3.3/INT1

P3.2/INT0

P3.1/TXD

P3.0/RXD

*

25

26

27

P4.6/CMT0

P4.7/CMT1

P4.5/CMSR5

n.c. = not connected

* = only P89C557E4 with alternate function WE

Figure 3. Pinning diagram for QFP80 (SOT318)

1999 Mar 02

28

29

DD2VSS2

V

31

30

RSTIN

P1.0/CT0I/INT2

32

33

34

35

P1.4/T2

P1.1/CT1I/INT3

P1.2/CT2I/INT4

P1.3/CT3I/INT5

5

36

P1.5/RT2

37

P1.6

38

P1.7

39

SCL

40

SDA

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

4.1 PIN DESCRIPTION

SYMBOL PIN DESCRIPTION

AV

ref–

AV

ref+

AV

SS1

AV

DD1

AV

SS2

AV

DD2

P5.7 – P5.0 5 – 12

V

, V

, V

, V

, V

DD2

DD4

SS2

SS4

,

DD1

V

DD3

V

SS1

V

SS3

ADEXS 15 Start ADC operation: Input starting analog to digital conversion triggered by a programmable edge (ADC

PWM0 16 Pulse width modulation output 0

PWM1 17 Pulse width modulation output 1

EW 18 Enable watchdog timer: Enable for T3 watchdog timer and disable Power-down Mode.This pin must not

P4.0 – P4.7 19 – 22

RSTIN 30 Reset: Input to reset the P8xC557E4.

RSTOUT 23 Reset: Output of the P8xC557E4 for resetting peripheral devices during initialization and Watchdog Timer

P1.0 – P1.7 31 – 38 Port 1

1

2

3

4

77

76

Low end of analog to digital conversion reference resistor

High end of analog to digital conversion reference resistor.

Analog ground for ADC

Analog power supply (+5 V) for ADC

Analog ground; for PLL oscillator

Analog power supply; (+5 V) for PLL oscillator

Port 5

8-bit input port

Port pin Alternative function

P5.0–P5.7 Eight input channels to ADC (ADC0–ADC7)

14, 28,

53, 66

13, 29,

Digital power supply: +5 V power supply pins during normal operation and power reduction modes. All pins

must be connected.

Digital ground: circuit ground potential. All pins must be connected.

54, 67

operation can also be started by software). This pin must not float

float.

Port 4

8-bit quasi-bidirectional I/O port

24 – 27

Port pin Alternative function

P4.0 CMSR0 }

P4.1 CMSR1 }

P4.2 CMSR2 } compare and set/reset

P4.3 CMSR3 } outputs on a match with timer T2

P4.4 CMSR4 }

P4.5 CMSR5 }

P4.6 CMT0 } compare and toggle outputs

P4.7 CMT1 } on a match with timer T2

overflow.

8-bit quasi-bidirectional I/O port

Port pin Alternative function

P1.0 CT0I/INT2}

P1.1 CT1I/INT3} : Capture timer inputs for

P1.2 CT2I/INT4} timer T2 or external interrupt inputs

P1.3 CT3I/INT5}

P1.4 T2 : T2 event input, rising edge triggered

P1.5 RT2 : T2 timer reset input, rising edge triggered

P1.6

P1.7

SCL 39 I2C-bus serial clock I/O port

SDA 40 I2C-bus serial data I/O port

If SCL and SDA are not used, they must be connected to V

1999 Mar 02

.

SS

6

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

PIN DESCRIPTION (Continued)

SYMBOL PIN DESCRIPTION

P3.0 – P3.7 41 – 48 8-bit quasi-bidirectional I/O port

N.C. 49 – 50 Not connected pins.

XTAL2 51 Crystal pin 2: output of the inverting amplifier that forms the oscillator. Left open-circuit when an external

XTAL1 52 Crystal pin 1: input to the inverting amplifier that forms the oscillator, and input to the internal clock

P2.0 – P2.7 55 – 62 Port2: 8-bit quasi-bidirectional I/O port with internal pull-ups.During access to external memories

PSEN 63 Program Store Enable output: read strobe to the external program memory via Port 0 and 2. Is activated

ALE/WE

EA 65 External Access Input: If, during RESET, EA is held at a TTL level HIGH the CPU executes out of the

P0.7–P0.0 68 –75 Port 0: 8-bit open drain bidirectional I/O port. It is also the multiplexed low-order address and data bus during

XTAL3 78 Crystal pin, output of the inverting amplifier that forms the 32 kHz oscillator

XTAL4 79 Crystal pin, input to the inverting amplifier that forms the 32 kHz oscillator. XT AL3 and XTAL4 are pulled

SELXTAL1 80 Must be connected to logic HIGH level to select the HF oscillator, using the XT AL1/XTAL2 crystal. If pulled low

64 Address Latch Enable output: latches the low byte of the address during access of external memory in

Port pin Alternative function

P3.0 RXD : Serial input port

P3.1 TXD : Serial output port

P3.2 INT0

P3.3 INT1

P3.4 T0 : Timer 0 external input

P3.5 T1 : Timer 1 external input

P3.6 WR

P3.7 RD

oscillator clock is used.

generator. Receives the external oscillator clock signal when an external oscillator is used. Must be

connected to logic HIGH if the PLL oscillator is selected (SELXTAL1 = LOW).

(RAM/ROM) that use 16-bit addresses (MOVX@DPTR) Port 2 emits the high order address byte. The

alternative function of P2.7 for the P89C557E4 is the output enable signal for verify/read modes (active low).

Port 2 can sink/source one TTL (=4 LSTTL) input. It can drive CMOS inputs without external pull-ups.

twice each machine cycle during fetches from external program memory. When executing out of external

program memory two activations of PSEN

is not activated (remains HIGH) during no fetches from external program memory. PSEN can sink/source 8

LSTTL inputs. It can drive CMOS inputs without external pull-ups.

normal operation. It is activated every six oscillator periods except during an external data memory access.

ALE/WE

alternative function for the P89C557E4 is the programming pulse input WE

To prohibit the toggling of ALE pin (RFI noise reduction) the bit RFI in the PCON Register (PCON.5) must be

set by software. This bit is cleared on RESET and can be set and cleared by software. When set, ALE pin

will be pulled down internally, switching an external address latch to a quiet state. The MOVX instruction will

still toggle ALE if external memory is accessed.

ALE will retain its normal high value during Idle Mode and a low value during Power-down Mode while in the

“RFI” mode. Additionally during internal access (EA

the internal program memory size. During external access (EA

the flag “RFI” is set or not.

internal program memory, provided the program counter is less than 32768. If, during RESET, EA

TTL level LOW the CPU executes out of external program memory via Port 0 and Port 2. EA

to float. EA

accesses to external memory (during theses accesses internal pull-ups are activated). Port 0 can sink/source

8 LSTTL inputs.

LOW if the PLL oscillator is not selected (SELXTAL1 = HIGH) or if Reset is active.

the PLL is selected for clocking of the controller, using the XTAL3/ XTAL4 crystal.

can sink/-source 8 LSTTL inputs. It can drive CMOS inputs without an external pull-up. The

is latched during RESET and don’t care after RESET.

: External interrupt

: External interrupt

: External data memory write strobe

: External data memory read strobe

are skipped during each access to external data memory. PSEN

.

= 1) ALE will toggle normally when the address exceeds

= 0) ALE will always toggle normally, whether

is held at a

is not allowed

NOTE:

1. To avoid a ‘latch-up’ effect at Power-on, the voltage at any pin at any time must not be higher or lower than V

respectively.

1999 Mar 02

7

+ 0.5 V or VSS– 0.5 V

DD

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

5. ELECTROMAGNETIC COMPATIBILITY (EMC)

IMPROVEMENTS

Primary attention was paid on the reduction of electromagnetic

emission of the microcontroller P8xC557E4.

The following features effect in reducing the electromagnetic

emission and additionally improve the electromagnetic susceptibility:

• Four supply voltage pins (V

pairs of V

package.

• Separated V

and VSS at two adjacent pins at each side of the

DD

pins for the internal logic and the port buffers

DD

) and four ground pins (VSS) with

DD

• Internal decoupling capacitance improves the EMC radiation

behavior and the EMC immunity

• External capacitors are to be located as close as possible

between pins V

well as V

recommended (100nF).

DD4

DD1

and V

and V

SS4

V

DD2

and V

SS1,

; ceramic chip capacitors are

Useful in applications that require no external memory or temporarily

no external memory:

• The ALE output signal (pulses at a frequency of f

disabled under software control (bit 5 in the SFR PCON: “RFI”); if

disabled, no ALE pulse will occur. ALE pin will be pulled down

internally , switching an external address latch to a quiet state.

The MOVX instruction will still toggle ALE (external data memory

is accessed). ALE will retain its normal HIGH value during Idle

Mode and a LOW value during Power-down mode while in the

“RFI” reduction mode. Additionally during internal access

(EA

= 1) ALE will toggle normally when the address exceeds the

internal program memory size. During external access (EA

ALE will always toggle normally, whether the flag “RFI” is set or

not.

SS2,

V

DD3

CLK

and V

SS3

/6) can be

= 0)

as

6. FUNCTIONAL DESCRIPTION

6.1 General

The P8xC557E4 is a stand-alone high-performance microcontroller

designed for use in real time applications such as instrumentation,

industrial control, medium to high-end consumer applications and

specific automotive control applications.

In addition to the 80C51 standard functions, the device provides a

number of dedicated hardware functions for these applications.

The P8xC557E4 is a control-oriented CPU with on-chip program

and data memory. It can be extended with external program memory

up to 64 Kbytes. It can also access up to 64 Kbytes of external data

memory. For systems requiring extra capability, the P8xC557E4 can

be expanded using standard memories and peripherals.

The P8xC557E4 has two software selectable modes of reduced

activity for further power reduction – Idle and Power-down. The Idle

Mode freezes the CPU while allowing the RAM, timers, serial ports

and interrupt system to continue functioning. The Power-down Mode

saves the RAM contents but freezes the oscillator causing all other

chip functions to be inoperative. The Power-down Mode can be

terminated by an external Reset, by the seconds interrupt and by

any one of the two external interrupts. (See description Wake-up

from Power-down Mode.)

6.2 Memory organization

The central processing unit (CPU) manipulates operands in three

memory spaces; these are the 64 Kbytes external data memory,

1024 bytes internal data memory (consisting of 256 bytes standard

RAM and 768 bytes AUX-RAM) and the 32 Kbytes internal and/or

64 Kbytes external program memory (see Figure 4).

32767

0

64 K

32768

Internal

(EA

= 1)

External

32767

0

Program Memory

External

(EA = 0)

Overlapped

Space

255

127

0

INDIRECT

ONLY

DIRECT AND

INDIRECT

Special

Function

Registers

Internal

Data Memory

Figure 4. Memory map & address space

(ARD = 0)

AUXILIARY

RAM

64 K

768

0

(ARD = 1)

External

Data Memory

1999 Mar 02

8

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

6.2.1 Program Memory

The program memory of the P8xC557E4 consists of 32 Kbytes

ROM respectively FEEPROM (”Flash Memory”) on-chip, externally

expandable up to 64 Kbytes. If, during RESET, the EA

HIGH, the P8xC557E4 executes out of the internal program memory

unless the address exceeds 7FFFH. Locations 8000H through

0FFFFH are then fetched from the external program memory. If the

EA

pin was held LOW during RESET the P8xC557E4 fetches all

instructions from the external program memory. The EA

latched during RESET and is don’t care after RESET.

The internal program memory content is protected, by setting a

mask programmable security bit (ROM) or by the software

programmable security byte (FEEPROM) respectively, i.e. it cannot

be read out at any time by any test mode or by any instruction in the

external program memory space. The MOVC instructions are the

only ones which have access to program code in the internal or

external program memory. The EA

and is ’don’t care’ after RESET. This implementation prevents from

reading internal program code by switching from external program

memory to internal program memory during MOVC instruction or an

instruction that handles immediate data. Table 1 lists the access to

the internal and external program memory with MOVC instructions

when the security feature has been activated.

6.2.2 Internal Data Memory

The internal data memory is divided into three physically separated

parts:

256 bytes of RAM, 768 bytes of AUX-RAM, and a 128 bytes special

function area. These can be addressed each in a different way (see

also Table 2).

– RAM 0 to 127 can be addressed directly and indirectly as in the

80C51. Address pointers are R0 and R1 of the selected

registerbank.

input is latched during RESET

pin was held

input is

– RAM 128 to 255 can only be addressed indirectly.

Address pointers are R0 and R1 of the selected registerbank.

– AUX-RAM 0 to 767 is also indirectly addressable as external

DATA MEMORY locations 0 to 767 via MOVX-Datapointer

instruction, unless it is disabled by setting ARD = 1.

AUX-RAM 0 to 767 is indirectly addressable via pageregister

(XRAMP) and MOVX-Ri instructions, unless it is disabled by

setting ARD = 1 (see Figure 5).

When executing from internal program memory, an access to

AUX-RAM 0 to 767 will not affect the ports P0, P2, P3.6 and P3.7.

An access to external DATA MEMORY locations higher than 767

will be performed with the MOVX @ DPTR instructions in the

same way as in the 80C51 structure, so with P0 and P2 as

data/address bus and P3.6 and P3.7 as write and read timing

signals. Note that the external DATA MEMORY cannot be

accessed with R0 and R1 as address pointer if the AUX-RAM is

enabled (ARD = 0, default).

– The Special Function Registers (SFR) can only be addressed

directly in the address range from 128 to 255 (see Table 5).

– Four register banks, each 8 registers wide, occupy locations 0

through 31 in the lower RAM area. Only one of these banks may

be enabled at a time. The next 16 bytes, locations 32 through 47,

contain 128 directly addressable bit locations.The stack can be

located anywhere in the internal 256 bytes RAM.The stack depth

is only limited by the available internal RAM space of 256 bytes

(see Figure 7).

All registers except the program counter and the four register

banks reside in the Special Function Register address space.

Table 1. Memory Access by the MOVC Instruction for Protected ROMs

MOVC LOCATION

MOVC in internal program memory YES YES

MOVC in external program memory NO YES

NOTE:

1.

If the security feature has not been activated, there are no restrictions for MOVC instructions.

ACCESS TO INTERNAL

PROGRAM MEMORY

ACCESS TO EXTERNAL

PROGRAM MEMORY

Table 2. Internal Data Memory Map

LOCATION ADDRESSED

RAM 0 to 127 Direct and indirect

AUX-RAM 0 to 767 Indirect only with MOVX

RAM 128 to 255 Indirect only

SFR 128 to 255 Direct only

1999 Mar 02

9

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

255

(XRAMP) = 02 H

0

MOVX @Ri, A

MOVX A, @Ri

Figure 5. Indirect addressing of AUX-RAM (768 Bytes), ARD bit in PCON = 0

6.2.2.1 AUX-RAM Page Register XRAMP

The AUX-RAM Page Register is used to select one of three 256

bytes pages of the internal 768 bytes AUX-RAM for

MOVX-accesses via R0 or R1. Its reset value is (XXXXXX00).

7 6 5 4 3 2 1 0

XRAMP (FAH)

x x x x x x XRAMP1 XRAMP0

255

(XRAMP) = 01 H

0

255

(XRAMP) = 00 H

0

767

512

511

MOVX @DPTR,A

MOVX A,@DPTR

256

255

0

x: undefined during read, a write operation must write “0” to these locations

Figure 6. AUX-RAM page register.

Table 3. Description of XRAMP Bits

BIT SYMBOL FUNCTION

XRAMP.2–7 XRAMPx reserved for future use

XRAMP.1 XRAMP1 AUX-RAM page select bit 1

XRAMP.0 XRAMP0 AUX-RAM page select bit 0

Table 4. Memory Locations for All Possible MOVX Accesses

1

ARD

0 0 0 AUX-RAM locations 0 .. 255 (reset condition)

0 0 1 AUX-RAM locations 256 .. 511

0 1 0 AUX-RAM locations 512 .. 767

0 1 1 no valid memory access; reserved for future use

1 X X External RAM locations 0 .. 255

0 X X AUX-RAM locations 0 .. 767 (reset condition)

1 X X External RAM locations 0 .. 65535

NOTE:

1. ARD (AUX-RAM Disable) is a bit in the Special Function Register PCON

XRAMP1 XRAMP0 MOVX @Ri,A and MOVX A,@Ri instructions access:

MOVX @DPTR,A and MOVX A,@DPTR instructions access:

External RAM locations 768 .. 65535

1999 Mar 02

10

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

Table 5. Special Function Register Memory Map and Reset Values

HIGH NIBBLE OF SFR ADDRESS

LOW 8 9 A B C D E F

0 P0 %

11111111

1 SP 00000111

2 DPL

00000000

3 DPH

00000000

4

5

6 ADRSL0 #

XXXXXXXX

7 PCON

00000000

8 TCON %

00000000

9 TMOD

00000000

A TL0

00000000

B TL1

00000000

C TH0

00000000

D TH1

00000000

E CTL2 #

F CTL3 #

NOTES:

% = Bit addressable register

# = Read only register

X = Undefined

* = FMCON only in P89C557E4

P1 %

11111111

ADRSL1 #

XXXXXXXX

S0CON %

00000000

S0BUF

XXXXXXXX

P2 %

11111111

ADRSL2 #

XXXXXXXX

IEN0 %

00000000

CML0

00000000

CML1

00000000

CML2

00000000

CTL0 #

XXXXXXXX

CTL1 #

XXXXXXXX

XXXXXXXX

XXXXXXXX

P3 %

11111111

ADRSL3 #

XXXXXXXX

IP0 %

X0000000

P4 %

11111111

ADRSL4 #

XXXXXXXX

P5 #

XXXXXXXX

TM2IR %

00000000

CMH0

00000000

CMH1

00000000

CMH2

00000000

CTH0 #

XXXXXXXX

CTH1 #

XXXXXXXX

CTH2 #

XXXXXXXX

CTH3 #

XXXXXXXX

PSW %

00000000

ADRSL5 #

XXXXXXXX

ADCON

00000000

S1CON %

00000000

S1STA #

11111000

S1DAT

00000000

S1ADR

00000000

ACC %

00000000

ADRSL6 #

XXXXXXXX

ADPSS

00000000

IEN1 %

00000000

TM2CON

00000000

CTCON

00000000

TML2 #

00000000

TMH2 #

00000000

STE

11000000

RTE

00000000

B %

00000000

ADRSL7 #

XXXXXXXX

ADRSH #

000000XX

IP1 %

00000000

PLLCON

00001 101

XRAMP

XXXXXX00

FMCON *

000X0000

PWM0

00000000

PWM1

00000000

PWMP

00000000

T3

00000000

6.3 Addressing

The P8xC557E4 has five methods for addressing:

•Register

•Direct

•Register-Indirect

•Immediate

•Base-Register plus Index-Register-Indirect

The first three methods can be used for addressing destination

operands. Most instructions have a “destination/source” field that

specifies the data type, addressing methods and operands involved.

For operations other than MOVs, the destination operand is also a

source operand.

1999 Mar 02

Access to memory addresses is as follows:

•Register in one of the four register banks through Register, Direct

or Register-Indirect addressing

•1024 bytes of internal RAM through Direct or Register-Indirect

addressing.

– Bytes 0–127 of internal RAM may be addressed

directly/indirectly . Bytes 128–255 of internal RAM share their

address location with the SFRs and so may only be addressed

indirectly as data RAM.

– Bytes 0–767 of AUX-RAM can only be addressed indirectly via

MOVX.

•Special Function Register through direct addressing at address

locations 128–255 (see Figure 8).

•External data memory through Register-Indirect addressing

•Program memory look-up tables through Base-Register plus

Index-Register-Indirect addressing

11

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

BYTE ADDRESS

(HEX)

FFH

2FH

2DH

2CH

2BH

2AH

29H

28H

27H

26H

25H

24H

23H

22H

21H

20H

1FH

BIT ADDRESS (HEX)

(MSB) (LSB)

78797B 7A7C7D7F 7E

707173 72747577 762EH 46

68696B 6A6C6D6F 6E

606163 62646567 66

58595B 5A5C5D5F 5E

505153 52545557 56

48494B 4A4C4D4F 4E

404143 42444547 46

38393B 3A3C3D3F 3E

303133 32343537 36

28292B 2A2C2D2F 2E

202123 22242527 26

18191B 1A1C1D1F 1E

101113 12141517 16

08090B 0A0C0D0F 0E

000103 02040507 06

BYTE ADDRESS

(DECIMAL)

255

47

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

18H

17H

10H

0FH

08H

07H

00H

Bank 3

24

23

Bank 2

16

15

Bank 1

8

7

Bank 0

0

Figure 7. RAM bit addresses

1999 Mar 02

12

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

DIRECT BYTE

ADDRESS (HEX)

F8H

F0H

E8H

E0H

D8H

D0H

C8H

C0H

B8H

BIT ADDRESS (HEX)

(MSB) (LSB)FFH

PT2 PCM2 PCM1 PCM0 PCT3 PCT2 PCT1 PCT0

F8F9FB FAFCFDFF FE

F0F1F3 F2F4F5F7 F6

ECT0ECT1ECT3 ECT2ECM0ECM1ET2 ECM2

E8E9EB EAECEDEF EE

E0E1E3 E2E4E5E7 E6

CR0CR1SI AASTOSTACR2 ENS1

D8D9DB DADCDDDF DE

PF1RS0 OVRS1F0CY AC

D0D1D3 D2D4D5D7 D6

CTI0CTI1CTI3 CTI2CMI0CMI1T2OV CMI2

C8C9CB CACCCDCF CE

C0C1C3 C2C4C5C7 C6

PX0PT0PT1 PX1PS0PS1–PAD

B8B9BB BABCBDBF BE

REGISTER

MNEMONIC

IP1

B

IEN1

ACC

S1CON

PSW

TM2IR

P4

IP0

B0H

A8H

A0H

98H

90H

88H

80H

SM0

SM1

Figure 8. Special Function Register bit addresses

B0B1B3 B2B4B5B7 B6

EX0ET0ET1 EX1ES0ES1EA EAD

A8A9AB AAACADAF AE

A0A1A3 A2A4A5A7 A6

RITITB8 RB8RENSM2

98999B 9A9C9D9F 9E

909193 92949597 96

IT0IE0IE1 IT1TR0TF0TF1 TR1

88898B 8A8C8D8F 8E

808183 82848587 86

P3

IEN0

P2

S0CON

P1

TCON

P0

1999 Mar 02

13

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

6.4 I/O Facilities

The P8xC557E4 has six 8-bit ports. Ports 0 to 3 are the same as in

the 80C51, with the exception of the additional functions of Port 1.

The parallel I/O function of Port 4 is equal to that of Ports 1, 2 and 3.

Port 5 has a parallel input port function, but has no function as an

output port.

The SDA and SCL lines serve the serial port SIO1 (I

2

the I

C-bus may be active while the device is disconnected from

V

these pins, are provided with open drain drivers.

DD,

Ports 0, 1, 2, 3, 4 and 5 perform the following alternative functions:

Port 0 : provides the multiplexed low-order address and data

bus used for expanding the P8xC557E4 with standard

memories and peripherals.

Port 1 : Port 1 is used for a number of special functions:

4 capture inputs (or external interrupt request inputs if

capture information is not utilized)

– external counter input

– external counter reset input

Port 2 : provides the high-order address bus when the

P8xC557E4 is expanded with external Program

Memory and/or external Data Memory.

Port 3 : pins can be configured individually to provide:

– external interrupt request inputs

– counter inputs

– receiver input and transmitter output of seri port

SIO 0 (UART)

– control signals to read and write external Data

Memory

2

C). Because

Port 4 : can be configured to provide signals indicating a match

between timer counter T2 and its compare registers.

Port 5 : may be used in conjunction with the ADC interface.

Unused analog inputs can be used as digital inputs. As

Port 5 lines may be used as inputs to the ADC, these

digital inputs have an inherent hysteresis to prevent the

input logic from drawing too much current from the

power lines when driven by analog signals. Channel to

channel crosstalk should be taken into consideration

when both digital and analog signals are simultaneously

input to Port 5 (see DC characteristics).

All ports are bidirectional with the exception of Port 5 which is an

input port.

Pins of which the alternative function is not used may be used as

normal bidirectional I/Os.

The generation or use of a Port 1, Port 3 or Port 4 pin as an

alternative function is carried out automatically by the P8xC557E4

provided the associated Special Function Register bit is set HIGH.

The pull-up arrangements of Ports 1 – 4 are shown in Figure 9.

QN

From Port

Latch

2 System Clock Periods

V

V

DD

P1 P2 P3

DD

V

DD

n

Input Data

Read Port Pin

P1 is turned on for 2 system clock periods after QN makes a 1-to-0 transition.

During this time, P1 also turns on P3 through the inverter to form an additional pull up.

Figure 9. I/O buffers in the P8xC557E4 (Ports 1, 2, 3 and 4)

Port

Pin

1999 Mar 02

14

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

6.5 Pulse Width Modulated Outputs

The P8xC557E4 contains two pulse width modulated output

channels (see Figure 13). These channels generate pulses of

programmable length and interval. The repetition frequency is

defined by an 8-bit prescaler PWMP, which supplies the clock for the

counter. The prescaler and counter are common to both PWM

channels. The 8-bit counter counts module 255, i.e., from 0 to 254

inclusive. The value of the 8-bit counter is compared to the contents

of two registers: PWM0 and PWM1. Provided the contents of either

of these registers is greater than the counter value, the

corresponding PWM0

these registers are equal to, or less than the counter value, the

output will be HIGH. The pulse-width-ratio is therefore defined by the

contents of the registers PWM0 and PWM1. The pulse-width-ratio is

in the range of 0/255 to 255/255 and may be programmed in

increments of 1/255.

Buffered PWM outputs may be used to drive DC motors. The

rotation speed of the motor would be proportional to the contents of

PWMn. The PWM outputs may also be configured as a dual DAC. In

this application, the PWM outputs must be integrated using

PWMP (FEH) PWMP.7 PWMP.6 PWMP.5 PWMP.4 PWMP.3 PWMP.2 PWMP.1 PWMP.0

or PWM1 output is set LOW. If the contents of

76543210

Figure 10. Prescaler frequency control register PWMP.

conventional operational amplifier circuitry. If the resulting output

voltages have to be accurate, external buffers with their own analog

supply should be used to buffer the PWM outputs before they are

integrated. The repetition frequency fpwm, at the PWMn outputs is

give by:

f

fpwm

This gives a repetition frequency range of 123 Hz to 31.4 kHz (f

= 16 MHz). By loading the PWM registers with either 00H or FFH,

the PWM channels will output a constant HIGH or LOW level,

respectively. Since the 8-bit counter counts modulo 255, it can never

actually reach the value of the PWM registers when they are loaded

with FFH.

When a compare register (PWM0 or PWM1) is loaded with a new

value, the associated output is updated immediately. It does not

have to wait until the end of the current counter period. Both PWMn

output pins are driven by push-pull drivers. These pins are not used

for any other purpose.

2 (1 PWMP) 255

CLK

CLK

Table 6. Description of PWMP Bits

BIT FUNCTION

PWMP.0 to 7 Prescaler division factor = (PWMP) + 1

NOTE:

1. Reading PWMP gives the current reload value. The actual count of the prescaler cannot be read.

76543210

PWM0 (FCH) PWM0.7 PWM0.6 PWM0.5 PWM0.4 PWM0.3 PWM0.2 PWM0.1 PWM0.0

Figure 11. Pulse width register PWM0.

Table 7. Description of PWM0 bits

BIT FUNCTION

PWM0.0 to 7

LOW/HIGH ration of PWM0 signal =

(PWM0)

255 – (PWM0)

1999 Mar 02

15

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

76543210

PWM1 (FDH) PWM1.7 PWM1.6 PWM1.5 PWM1.4 PWM1.3 PWM1.2 PWM1.1 PWM1.0

Figure 12. Pulse width register PWM1.

Table 8. Description of PWM1 bits

BIT FUNCTION

PWM1.0 to 7

Internal Bus

LOW/HIGH ration of PWM1 signal =

PWM0

8-Bit Comparator

f

CLK

Prescaler1/2

PWMP

Figure 13. Functional Diagram of Pulse Width Modulated Outputs.

8-Bit Counter

8-Bit Comparator

PWM1

(PWM1)

255 – (PWM1)

Output

Buffer

Output

Buffer

PWM0

PWM1

1999 Mar 02

16

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

6.6 Analog/Digital Converter (ADC)

The P8xC557E4 A/D Converter is a 10-bit, successive

approximation ADC with 8 multiplexed analog input channels. It

additionally contains a high input impedance comparator, a DAC

built with 1024 series resistors and analog switches, registers and

control logic.

Input voltage range is from AV

A set of 8 buffer registers (10-bit) store the conversion results of the

proper analog input channel each.

11 Special Function Registers (SFR) perform the user software

interface to the ADC: a control SFR (ADCON), an analog port

scan-select SFR (ADPSS), 8 input channel related conversion result

SFR with the 8 lower result bits (ADRSL0...ADRSL7), one common

result SFR for the upper 2 result bits (ADRSH). An extra SFR (P5)

allows for reading digital input port data as an alternative function of

the 8 analog input pins.

In order to have a minimum of ADC service overhead in the

microcontroller program, the ADC is able to operate autonomously

within its user configurable autoscan function.

The functional diagram of the ADC is shown in Figure 15.

Feature Overview:

(typical 0V) to AV

ref–

(typical +5V).

ref+

•10-bit resolution.

•8 multiplexed analog inputs.

•Programmable autoscan of the analog inputs.

•Bit oriented 8-bit scan-select register to select analog inputs.

•Continuous scan or one time scan configurable from 1 to 8 analog

inputs.

•Start of a conversion by software or with an external signal.

•Eight 10-bit buffer registers, one register for each analog input

channel.

•Interrupt request after one channel scan loop.

•Programmable prescaler (dividing by 2, 4, 6, 8) to adapt to

different system clock frequencies.

•Conversion time for one A/D conversion: 15 µs ... 50 µs

•Differential non-linearity : DLe ±1 LSB.

•Integral non-linearity : ILe ±2 LSB.

•Offset error : OSe ±2LSB.

•Gain error : Ge ±0.4 %.

•Absolute voltage error : Ae ±3 LSB.

•Channel to channel matching : Mctc ±1LSB.

•Crosstalk between analog inputs : Ct < –60dB. @100 kHz.

•Monotonic and no missing codes.

•Separated analog (AV

voltages.

•Reference voltage at two special pins : AV

For further information on the ADC characteristics, refer to the

“DC CHARACTERISTICS” section.

, AVSS) and digital (VDD, VSS) supply

DD

and AV

REF–

REF+

.

6.1.1 Functional description:

Table 9. A/D Special Function Registers

SYMBOL NAME ACCESS

ADCON A/D control register read/write

ADPSS Analog port scan-select register read/write

ADRSLn 8 A/D result registers, the 8 lower bits (n: 0...7) read only

ADRSH A/D result register, the 2 higher bits read only

P5 Digital input port (shared with analog inputs) read only

A/D Control Register ADCON

The Special Function Register ADCON contains control and status

bits for the A/D Converter peripheral block. The reset value of

ADCON is (00000000). Its hardware address is D7H. ADCON is not

bit addressable.

76543210

ADCON (D7H) ADPR1 ADPR0 ADPOS ADINT ADSST ADCSA ADSRE ADSFE

Figure 14. ADC control register.

1999 Mar 02

17

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

ADC0

ADC7

AV

ref+

AV

ref–

AV

DD1

AV

SS1

ADEXS

ANALOG

Mux.

SCAN LOGIC

ADPSS ADCON

88

COMPARATOR SAR

+

–

DAC

10–bit result

registers

2 LATCHES

Read

ADRSH

10

8x

2

Read

ADRSL

2

10

10

8

n

8

INTERNAL BUS

Figure 15. Functional diagram of AD converter.

Table 10. Description of ADCON bits

SYMBOL BIT FUNCTION

ADCON.7 ADPR1 Control bit for the prescaler.

ADCON.6 ADPR0 Control bit for the prescaler.

ADCON.5 ADPOS ADPOS is reserved for future use. Must be ’0’ if ADCON is written.

ADCON.4 ADINT ADC interrupt flag. This flag is set when all selected analog inputs are converted, as well in continuous

ADCON.3 ADSST ADC start and status. Setting this bit by software or by hardware (via ADEXS input) starts the A/D

ADCON.2 ADCSA 1 = Continuous scan of the selected analog inputs after a start of an A/D conversion.

ADCON.1 ADSRE 1 = A rising edge at input ADEXS will start the A/D conversion and generate a capture signal.

ADCON.0 ADSFE 1 = A falling edge at input ADEXS will start the A/D conversion and generate a capture signal.

ADPR1=0 ADPR0=0 Prescaler divides by 2 (default by reset)

ADPR1=0 ADPR0=1 Prescaler divides by 4

ADPR1=1 ADPR0=0 Prescaler divides by 6

ADPR1=1 ADPR0=1 Prescaler divides by 8

scan as in one-time scan mode. An interrupt is invoked if this interrupt is enabled. ADINT must be cleared

by software. It cannot be set by software.

conversion of the selected analog inputs. ADSST stays a ‘one’ in continuous scan mode. In one-time scan

mode, ADSST is cleared by hardware when the last selected analog input channel has been converted. As

long as ADSST is ’1’, new start commands to the ADC-block are ignored.

An A/D conversion in progress is aborted if ADSST is cleared by software.

0 = One-time scan of the selected analog inputs after a start of an A/D conversion.

0 = A rising edge at input ADEXS has no effect.

0 = A falling edge at input ADEXS has no effect.

1999 Mar 02

18

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

A/D Input Port Scan-Select Register ADPSS

The Special Function Register ADPSS contains control bits to select

the analog input channel(s) to be scanned for A/D conversion. The

reset value of ADPSS is (00000000). Its hardware address is E7H.

ADPSS is not bit addressable.

If all bits are ‘0’ then no A/D conversion can be started. If ADPSS is

written while an A/D conversion is in progress (ADSST in the

ADCON register is ‘1’) then the autoscan loop with the previous

selected analog inputs is completed first. The next autoscan loop is

performed with the new selected analog inputs.

76543210

ADPSS (E7H) ADPSS7 ADPSS6 ADPSS5 ADPSS4 ADPSS3 ADPSS2 ADPSS1 ADPSS0

ADPSS7–0 For each individual bit position: 0 = The corresponding analog input is skipped in the auto-scan loop.

Figure 16. A/D input port scan-select register.

1 = The corresponding analog input is included in the auto-scan loop.

A/D Result Registers ADRSLn and ADRSH:

The binary result code of A/D conversions is accessed by these

Special Function Registers. The result SFR are read only registers.

The read value after reset is indeterminate. Their data are not

affected by chip reset. They are not bit addressable.

There are 8 Special Function Registers ADRSLn

(ADRSL0...ADRSL7) – A/D Result Low byte – and one general SFR

ADRSH – A/D Result High byte – . Each of ADRSLn is associated

with the coincidently indexed analog input channel ADCn

(ADC0/P5.0...ADC7/P5.7). Reading an ADRSLn register by

software copies at the same time the two highest bits of the 10-bit

conversion result into two latches, thus preserving them until the

next read of any ADRSLn register. These two latches form bit

positions 0 and 1 of SFR ADRSH, the upper 6 bits of ADRSH are

always read as ’0’.

Thus it is ensured to get the 10-bit result of the same single A/D

conversion by reading any register ADRSLn first and after it the

register ADRSH.

76543210

ADRSLn ADRSn.7 ADRSn.6 ADRSn.5 ADRSn.4 ADRSn.3 ADRSn.2 ADRSn.1 ADRSn.0

(n: 0...7)

ADRSH 0 0 0 0 0 0 ADRSn.9 ADRSn.8

1999 Mar 02

76543210

Figure 17. A/D Result Registers.

19

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

Digital Input Port Register P5

Port 5 Special Function Register P5 always represents the binary

value of the logic level at input pins P5.0/ADC0...P5.7/ADC7. P5 is

not affected by chip reset. P5 is a read only register . Its hardware

address is C7H. P5 is not bit addressable.

Reading Special Function Register P5 does not affect A/D

conversions. But it is recommended to use the digital input port

function of the hardware Port 5 only as an alternative to analog input

voltage conversions. Simultaneous mixed operation is discouraged

for the sake of A/D conversion result reliability and accuracy.

For further information on Port 5, refer to the “I/O facilities” section.

For further information on A/D Special Function Registers, refer to

the “Internal Data Memory” section.

76543210

P5 (C7H) P5.7 P5.6 P5.5 P5.4 P5.3 P5.2 P5.1 P5.0

Figure 18. Digital input port register P5.

Reset

After a RESET of the microcontroller the ADCON and ADPSS

register bits are initialized to zero. Registers ADRSLn and ADRSH

are not initialized by a RESET.

Idle and Power-down Mode

The A/D Converter is active only when the microcontroller is in

normal operating mode. If the Idle or Power-down Mode is activated,

then the ADC is switched off and put into a power saving idle state –

a conversion in progress is aborted, a previously set ADSST flag is

cleared and the internal clock is halted. The conversion result

registers are not affected.

The interrupt flag ADINT will not be set by activation of Idle or

Power-down Mode. A previously set flag ADINT will not be cleared

by the hardware. (Note: ADINT cannot be cleared by hardware at

all, except for a RESET – it must be cleared by the user software.)

After a wakeup from Idle or Power-down Mode a set flag ADINT

indicates that at least one autoscan loop was finished completely

before the microcontroller was put into the respective power

reduction mode and it indicates that the stored result data may be

fetched now – if desired.

For further information on Idle and Power-down Mode, refer to the

“Power reduction modes” section.

Timing

A programmable prescaler is controlled by the bits ADPR1 and

ADPR0 in register ADCON to adapt the conversion time for different

microcontroller clock frequencies.

Table 11 shows conversion times (tconv) for one A/D conversion at

some convenient system clock frequencies (fclk) and ADC prescaler

divisors (m), which are user selectable by the bits ADCON.7/ADPR1

and ADCON.6/ADPR0.

For conversion times outside the limits for tconv the specified ADC

characteristics are not guaranteed; (prohibited conversion times are

put in brackets):

Table 11. Conversion time configuration

examples (tconv/µs)

f

CLK

m 6 MHz 8 MHz 12 MHz 16 MHz

2

4

6

8

Conversion time tconv = (6 m + 1) machine cycles

A conversion time tconv consists of one sample time period (which

equals two bit conversion times), 10 bit conversion time periods and

one machine cycle to store the result.

After result storage an extra initializing time period follows to select

the next analog input channel (according to the contents of SFR

ADPSS), before the input signal is sampled.

Thus the time period between two adjacent conversions within an

autoscan loop is larger than the pure time tconv. This autoscan cycle

time is ( 7 m ) machine cycles.

At the start of an autoscan conversion the time between writing to

SFR ADCON and the first analog input signal sampling depends on

the current prescaler value (m) and the relative time offset between

this write operation and the internal (divided) ADC clock. This gives

a variation range for the A/D conversion start time of ( m / 2 )

machine cycles.

26

50

[74]

[98]

19.5

37.5

[55.5]

[73.5]

[13]

25

37

49

[9.75]

18.75

27.75

36.75

1999 Mar 02

20

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

(AV

Configuration and Operation

6.6.2

Every A/D conversion is an autoscan conversion. The two user

selectable general operation modes are continuous scan and

one-time scan mode.

The desired analog input port channel/s for conversion is/are

selected by programming A/D input port scan-select bits in SFR

ADPSS. An analog input channel is included in the autoscan loop if

the corresponding bit in ADPSS is 1, a channel is skipped if the

corresponding bit in ADPSS is 0.

An autoscan is always started according to the lowest bit position of

ADPSS that contains a 1.

An autoscan conversion is started by setting the flag ADSST in

register ADCON either by software or by an external start signal at

input pin ADEXS, if enabled. Either no edge (external start totally

disabled), a rising edge or/and a falling edge of ADEXS is selectable

for external conversion start by the bits ADSRE and ADSFE in

register ADCON.

After completion of an A/D conversion the 10-bit result is stored in

the corresponding 10-bit buffer register . Then the next analog input

is selected according to the next higher set bit position in ADPSS,

converted and stored, and so on. When the result of the last

conversion of this autoscan loop is stored, flag ADCON.4/ADINT,

the ADC interrupt flag, is set. It is not cleared by interrupt hardware

– it must be cleared by software.

In continuous scan mode (ADCON.2/ADCSA=1) the ADC start and

status flag ADCON.3/ADSST retains the set state and the autoscan

loop restarts from the beginning. In one-time scan mode (ADCSA=0)

conversions stop after the last selected analog input was converted,

ADINT is set and ADSST is cleared automatically.

ADSST cannot be set (neither externally nor by software) as long as

ADINT=1, i.e. as long as ADINT is set, a new conversion start – by

setting flag ADSST – is inhibited; actually it is only delayed until

ADINT is cleared.

(If a ‘1’ is written to ADSST while ADINT=1, this new value is

internally latched and preserved, not setting ADSST until

ADCON.4/ADINT=0. In this state, a read of SFR ADCON will display

ADCON.3/ADSST=0, because always the effective ADC status is

read.)

Note that under software control the analog inputs can also be

converted in arbitrary order, when one-time scan mode is selected

and in SFR ADPSS only one bit is set at a time. In this case ADINT

is set and ADSST is cleared after every conversion.

6.6.3 Resolution and Characteristics

The ADC system has its own analog supply pins AV

is referenced by two special reference voltage input pins sourcing

the resistance ladder of the DAC: AV

between AV

the 10-bit resolution the full scale range is divided into 1024 unit

steps. The unit step voltage is 1 LSB, which is typically 5 mV

(AV

= 5.12 V, AV

ref+

The DAC’s resistance ladder has 1023 equally spaced taps,

separated by a unit resistance ’R’. The first tap is located 0.5 x R

above AV

results in a total ladder resistance of 1024 x R. This structure

ensures that the DAC is monotonic and results in a symmetrical

quantization error. For input voltages between AV

+ 1/2 LSB) the 10-bit conversion result code will be

(AV

ref–

00 0000 0000 B = 000H = 0D. For input voltages between

and AV

REF+

ref–

, the last tap is located 1.5 x R below AV

ref–

defines the full-scale range. Due to

REF–

= 0 V = AVSS).

ref+

and AV

and AVSS. It

DD

. The voltage

ref–

ref+

and

ref–

. This

– 3/2 LSB) and AV

ref+

be 11 11 11 1 111 B = 3FFH = 1023D.

The result code corresponding to an analog input voltage (AV

be calculated from the formula:

ResultCode + 1024

The analog input voltage should be stable when it is sampled for

conversion. At any times the input voltage slew rate must be less

than 10 V/ms (5 V conversion range) in order to prevent an

undefined result.

This maximum input voltage slew rate can be ensured by an RC low

pass filter with R = 2k2 and C = 100 nF. The capacitor between

analog input pin and analog ground pin shall be placed close to the

pins in order to have maximum effect in minimizing input noise

coupling.

6.7 Timer/Counters

The P8xC557E4 contains three 16-bit timer/event counters: Timer 0,

Timer 1 and Timer T2 and one 8-bit timer, T3. Timer 0 and Timer 1

may be programmed to carry out the following functions:

•Measure time intervals and pulse durations

•Count events

•Generate interrupt requests

6.7.1 Timer 0 and Timer 1

Timers 0 and 1 each have a control bit in SFR TMOD that selects

the timer or counter function of the corresponding timer.

In the timer function, the register is incremented every machine

cycle. Thus, one can think of it as counting machine cycles. Since a

machine cycle consists of 12 oscillator periods, the count rate is

1/12 of the oscillator frequency.

In the counter function, the register is incremented in response to a

1-to-0 transition at the corresponding external input pin, T0 or T1. In

this function, the external input is sampled during S5P2 of every

machine cycle. When the samples show a HIGH in one cycle and a

LOW in the next cycle, the counter is incremented. Thus, it takes

two machine cycles (24 oscillator periods) to recognize a 1-to-0

transition. There are no restrictions on the duty cycle of the external

input signal, but to insure that a given level is sampled at least once

before it changes, it should be held for at least one full machine

cycle.

Timer 0 and Timer 1 can be programmed independently to operate

in one of four modes:

•Mode 0:

8-bit timer or 8-bit counter each with divide-by-32 prescaler

•Mode 1:

16-bit time-interval or event counter

•Mode 2:

8-bit time-interval or event counter with automatic reload

upon overflow

•Mode 3:

–Timer 0: one 8-bit time-interval or event counter and

one 8-bit time-interval counter

–Timer 1: stopped

the 10-bit conversion result code will

ref+

AV

* AV

IN

* AV

ref*

ref*

AV

ref)

in

) can

1999 Mar 02

21

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

When Timer 0 is in Mode 3, Timer 1 can be programmed to operate

in Modes 0, 1 or 2 but cannot set an interrupt request flag or

generate an interrupt. However the overflow from Timer 1 can be

used to pulse the serial port baud-rate generator.

With a 16 MHz crystal, the counting frequency of these

timer/counters is as follows:

•In the timer function, the timer is incremented at a frequency of

1.33 MHz – a division by 12 of the system clock frequency

•0 Hz to an upper limit of 0.66 MHz (1/24 of the system clock

frequency) when programmed for external inputs

76543210

TMOD (89H) GATE C/T M1 M0 GATE C/T M1 M0

Timer 1

Figure 19. Timer/Counter mode control (TMOD) register.

Both internal and external inputs can be gated to the counter by a

second external source for directly measuring pulse durations.

When configured as a counter, the register is incremented on every

falling edge on the corresponding input pin, T0 or T1. The

incremented register value can be read earliest during the second

machine cycle after that one, during which the incrementing pulse

occurred.

The counters are started and stopped under software control. Each

one sets its interrupt request flag when it overflows from all HIGHs

to all LOWs (or automatic reload value), with the exception of mode

3 as previously described.

Table 12. Description of TMOD bits

SYMBOL BIT FUNCTION

Gate TMOD.7

C/T TMOD.6

M1

M0

TMOD.3

TMOD.2

TMOD.5

TMOD.1

TMOD.4

TMOD.0

Gating control when set. Timer/Counter “x” is enabled only while “INTx” pin is high and “TRx” control pin is set.

When cleared Timer “x” is enabled whenever “TRx” control bit is set.

Timer or Counter Selector cleared for Timer operation (input from internal system clock). Set for Counter

operation (input from “Tx” input pin).

Timer 0, Timer 1 mode select see Table 13.

Timer 0

Table 13. T imer 0 / Timer 1 operation select

M1 M0 OPERATING

0 0 8048 Timer “TLx” serves as 5-bit prescaler.

0 1 16-bit Timer/Counter “THx” and “TLx” are cascaded; there is no prescaler.

1 0 8-bit auto-reload Timer/Counter “THx” holds a value which is to be reloaded into “TLx” each time it overflows.

1 1 (Timer 0) TL0 is an 8-bit Timer/Counter controlled by the standard Timer 0 control bits. TH0 is an 8-bit timer

1 1 (Timer 1) Timer/Counter 1 stopped.

1999 Mar 02

only controlled by Timer 1 control bits.

22

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

76543210

TCON (88H) TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

Figure 20. Timer/Counter mode control (TCON) register.

Table 14. Description of TCON bits

SYMBOL BIT FUNCTION

TF1 TCON.7 Timer 1 overflow flag. Set by hardware on Timer/Counter overflow. Cleared by hardware when processor

TR1 TCON.6 Timer 1 run control bit. Set/cleared by software to turn Timer/Counter on/off.

TF0 TCON.5 Timer 0 overflow flag. Set by hardware on Timer/Counter overflow. Cleared by hardware when processor

TR0 TCON.4 Timer 0 run control bit. Set/cleared by software to turn Timer/Counter on/off.

IE1 TCON.3 Interrupt 1 edge flag. Set by hardware when external interrupt edge detected. Cleared when interrupt

IT1 TCON.2 Interrupt 1 type control bit. Set/cleared by software to specify falling edge/low level triggered external interrupts.

IE0 TCON.1 Interrupt 0 edge flag. Set by hardware when external interrupt edge detected. Cleared when interrupt

IT0 TCON.0 Interrupt 0 type control bit. Set/cleared by software to specify falling edge/low level triggered external interrupts.

vectors to interrupt routine.

vectors to interrupt routine.

processed.

processed.

1999 Mar 02

23

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

6.7.2 Timer T2

Timer T2 is a 16 bit timer/counter which has capture and compare

facilities. The operational diagram is shown in Figure 21.

The 16 bit timer/counter is clocked via a prescaler with a

programmable division factor of 1, 2, 4 or 8. The input of the

prescaler is clocked with 1/12 of the clock frequency, or by an

external source connected to the T2 input, or it is switched off. The

maximum repetition rate of the external clock source is f

CLK

/12,

twice that of Timer 0 and Timer 1. The prescaler is incremented on a

rising edge. It is cleared if its division factor or its input source is

changed, or if the timer/counter is reset (see also Figure 22:

TM2CON). T2 is readable ’on the fly’, without any extra read

latches; this means that software precautions have to be taken

against misinterpretation at overflow from least to most significant

CT1I

CTI1

f

CLK

INTCT0I

CTI0

CT0 CT1 CT2 CT3

off

1/12

T2

Prescaler T2 Counter

byte while T2 is being read. T2 is not loadable and is reset by the

RST signal or at the positive edge of the input signal RT2, if

enabled. In the Idle or Power-down Mode the timer/counter and

prescaler are reset and halted.

T2 is connected to four 16-bit Capture Registers: CT0, CT1, CT2

and CT3. A rising or falling edge on the inputs CT0I, CT1I, CT2I or

CT3I (alternative function of Port 1) results in loading the contents of

T2 into the respective Capture Registers and an interrupt request.

Using the Capture Register CTCON (see Figure 23), these inputs

may invoke capture and interrupt request on a positive, a negative

edge or on both edges. If neither a positive nor a negative edge is

selected for capture input, no capture or interrupt request can be

generated by this input.

CT2I

INTINT

CTI2

8-bit overflow interrupt

16-bit overflow interrupt

CT3I

INT

CTI3

RT2

T2ER

External reset

S

S

S

S

S

S

TG

TG

STE RTE

enable

COMP

R

R

R

R

R

R

T

T

P4.0

P4.1

P4.2

P4.3

P4.4

P4.5

P4.6

P4.7

CMO (S)

I/O port 4

S = set

R = reset

T = toggle

TG = toggle status

INT

COMP

CM1 (R)

T2 SFR address: TML2 = lower 8 bits

TMH2 = higher 8 bits

INT

COMP

CM2 (T)

INT

Figure 21. Block diagram of Timer 2.

1999 Mar 02

24

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

76543210

TM2CON (EAH) T2IS1 T2IS0 T2ER T2BO T2P1 T2P0 T2MS1 T2MS0

Figure 22. T2 control register (TM2CON).

Table 15. Description of TM2CON bits

SYMBOL BIT FUNCTION

T2IS1 TM2CON.7 Timer T2 16-bit overflow interrupt select

T2IS0 TM2CON.6 Timer T2 byte overflow interrupt select

T2ER TM2CON.5 Timer T2 external reset enable. When this bit is set, Timer T2 may be reset by a rising edge on RT2 (P1.5).

T2BO TM2CON.4 Timer T2 byte overflow interrupt flag

T2P1 TM2CON.3 Timer T2 prescaler select

T2P0 TM2CON.2

T2MS1 TM2CON.1 Timer T2 mode select

T2MS0 TM2CON.0

Table 16. T imer 2 prescaler select

T2P1 T2P0 TIMER T2 CLOCK

0 0 Clock source

0 1 Clock source/2

1 0 Clock source/4

1 1 Clock source/8

Table 17. T imer 2 mode select

T2MS1 T2MS0 MODE SELECTED

0 0 Timer T2 halted (off)

0 1 T2 clock source = f

1 0 Test mode; do not use

1 1 T2 clock source = pin T2

CLK

/12

1999 Mar 02

25

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

76543210

CTCON (EBH) CTN3 CTP3 CTN2 CTP2 CTN1 CTP1 CTN0 CTP0

Figure 23. Capture control register (CTCON).

Table 18. Description of CTCON bits

SYMBOL BIT FUNCTION

CTN3 CTCON.7 Capture Register 3 triggered by a falling edge on CT3I

CTP3 CTCON.6 Capture Register 3 triggered by a rising edge on CT3I

CTN2 CTCON.5 Capture Register 2 triggered by a falling edge on CT2I

CTP2 CTCON.4 Capture Register 2 triggered by a rising edge on CT2I

CTN1 CTCON.3 Capture Register 1 triggered by a falling edge on CT1I

CTP1 CTCON.2 Capture Register 1 triggered by a rising edge on CT1I

CTN0 CTCON.1 Capture Register 0 triggered by a falling edge on CT0I

CTP0 CTCON.0 Capture Register 0 triggered by a rising edge on CT0I

The contents of the Compare Registers CM0, CM1 and CM2 are

continuously compared with the counter value of Timer T2. When a

match occurs, an interrupt may be invoked. A match of CM0 sets

the bits 0–5 of Port 4, a CM1 match resets these bits and a CM2

match toggles bits 6 and 7 of Port 4, provided these functions are

enabled by the STE respectively RTE registers. A match of CM0

and CM1 at the same time results in resetting bits 0–5 of Port 4.

CM0, CM1 and CM2 are reset by the RSTIN signal.

76543210

TM2IR (C8H) T2OV CMI2 CMI1 CMI0 CTI3 CTI2 CTI1 CTI0

Figure 24. Interrupt flag register (TM2IR).

Table 19. Description of TM2IR bits

SYMBOL BIT FUNCTION

T2OV TM2IR.7 Timer T2 16-bit overflow interrupt flag

CMI2 TM2IR.6 CM2 interrupt flag

CMI1 TM2IR.5 CM1 interrupt flag

CMI0 TM2IR.4 CM0 interrupt flag

CTI3 TM2IR.3 CT3 interrupt flag

CTI2 TM2IR.2 CT2 interrupt flag

CTI1 TM2IR.1 CT1 interrupt flag

CTI0 TM2IR.0 CT0 interrupt flag

1999 Mar 02

26

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

76543210

STE (EEH) TG47 TG46 SP45 SP44 SP43 SP42 SP41 SP40

Figure 25. Set enable register (STE).

Table 20. Description of STE bits

SYMBOL BIT FUNCTION

TG47 STE.7 If “1” then P4.7 is reset on the next toggle, if LOW P4.7 is set on the next toggle

TG46 STE.6 If “1” then P4.6 is reset on the next toggle, if LOW P4.6 is set on the next toggle

SP45 STE.5 If “1” then P4.5 is set on a match between CM0 and Timer T2

SP44 STE.4 If “1” then P4.4 is set on a match between CM0 and Timer T2

SP43 STE.3 If “1” then P4.3 is set on a match between CM0 and Timer T2

SP42 STE.2 If “1” then P4.2 is set on a match between CM0 and Timer T2

SP41 STE.1 If “1” then P4.1 is set on a match between CM0 and Timer T2

SP40 STE.0 If “1” then P4.0 is set on a match between CM0 and Timer T2

76543210

RTE (EFH) TP47 TP46 RP45 RP44 RP43 RP42 RP41 RP40

Figure 26. Reset/Toggle enable register (RTE).

Table 21. Description of RTE bits

SYMBOL BIT FUNCTION

TP47 RTE.7 If “1” then P4.7 toggles on a match between CM2 and Timer T2

TP46 RTE.6 If “1” then P4.6 toggles on a match between CM2 and Timer T2

RP45 RTE.5 If “1” then P4.5 toggles on a match between CM1 and Timer T2

RP44 RTE.4 If “1” then P4.4 toggles on a match between CM1 and Timer T2

RP43 RTE.3 If “1” then P4.3 toggles on a match between CM1 and Timer T2

RP42 RTE.2 If “1” then P4.2 toggles on a match between CM1 and Timer T2

RP41 RTE.1 If “1” then P4.1 toggles on a match between CM1 and Timer T2

RP40 RTE.0 If “1” then P4.0 toggles on a match between CM1 and Timer T2

For more information concerning the TM2CON, CTCON, TM2IR and

the STE/RTE registers see IC20 handbook, chapter “80C51 family

hardware description”.

Port 4 can be read and written by software without affecting the

toggle, set and reset signals. At a byte overflow of the least

significant byte, or at a 16-bit overflow of the timer/counter, an

interrupt sharing the same interrupt vector is requested. Either one

or both of these overflows can be programmed to request an

interrupt.

All interrupt flags must be reset by software.

1999 Mar 02

27

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

6.8 Watchdog Timer T3

In addition to Timer T2 and the standard timers, a watchdog timer

(T3) consisting of an 11-bit prescaler and an 8-bit timer is also

incorporated (see Figure 27).

The timer is incremented every 1.5 ms, derived from the system

clock frequency of 16 MHz by the following:

f

12 2048

f

CLK

CLK

/12

Prescaler

(11-bit)

Clear

f

timer

When a timer overflow occurs, the microcontroller is reset and a

reset output pulse is generated at pin RSTOUT. Also the PLL control

register is reset.

To prevent a system reset the timer must be reloaded in time by the

application software. If the processor suffers a hardware/software

malfunction, the software will fail to reload the timer. This failure will

produce a reset upon overflow thus preventing the processor

running out of control.

The watchdog timer can only be reloaded if the condition flag

WLE = PCON.4 has been previously set by software.

At the moment the counter is loaded the condition flag is

automatically cleared.

The time interval between the timer’s reloading and the occurrence

of a reset depends on the reloaded value. For example, this may

range from 1.5 ms to 0.375 s when using an oscillator frequency of

16 MHz.

In the Idle state the watchdog timer and reset circuitry remain active.

The watchdog timer is controlled by the watchdog enable pin (EW

A LOW level enables the watchdog timer and disables the

Power-down Mode. A HIGH level disables the watchdog timer and

enables the Power-down Mode.

Internal Bus

Timer T3

(8-bit)

LOAD LOADEN

to reset circuitry (see Figure 46)

).

EW

Write T3

Clear

WLE

PCON.4

Internal Bus

Figure 27. Watchdog timer.

PD

LOADEN

PCON.1

1999 Mar 02

28

Philips Semiconductors Product specification

P83C557E4/P80C557E4/P89C557E4Single-chip 8-bit microcontroller

6.9 Serial I/O

The P8xC557E4 is equipped with two independent serial ports:

SIO0 and SI01. SIO0 is the full duplex UART port, identical to the

PCB80C51 serial port. SIO1 is an I

byte oriented master and slave functions.

6.9.1 SIO0 (UART)

SIO 0 is a full duplex serial I/O port – it can transmit and receive

simultaneously. This serial port is also receive-buffered. It can

commence reception of a second byte before the previously

received byte has been read from the receive register. If, however,

the first byte has still not been read by the time reception of the

second byte is complete, one of the bytes will be lost. The SIO0

receive and transmit registers are both accessed via the S0BUF

special function register. Writing to S0BUF loads the transmit

register, and reading S0BUF accesses to a physically separate

receive register. SIO0 can operate in 4 modes:

Mode 0: Serial data is transmitted and received through RXD.

TXD outputs the shift clock. 8 data bits are

transmitted/received (LSB first). The baud rate is

fixed at 1/12 of the oscillator frequency. A write into

S0CON should be avoided during a transmission to

avoid spikes on RXD/TXD.

Mode 1: 10 bits are transmitted via TXD or received through

RXD: a start bit (0), 8 data bits (LSB first), and a

stop bit(1). On receive, the stop bit is put into RB8

(S0CON special function register). The baud rate is

variable.

2

C-bus serial I/O interface with

Mode 2: 11 bits are transmitted through TXD or received

through RXD: a start bit (0), 8 data bits (LSB first), a

programmable 9th data bit, and a stop bit (1). On

transmit, the 9th data bit (TB8 in S0CON) can be

assigned the value of 0 or 1. With nominal software,

TB8 can be the parity bit (P in PSW). During a

receive, the 9th data bit is stored in RB8 (S0CON),

and the stop bit is ignored. The baud rate is

programmable to either 1/32 or 1/64 of the oscillator

frequency.

Mode 3: 11 bits are transmitted through TXD or received

through RXD: a start bit (0), 8 data bits (LSB first), a

programmable 9th data bit, and a stop bit (1). Mode

3 is the same as Mode 2 except the baud rate which

is variable in Mode 3.

In all four modes, transmission is initiated by any instruction that

writes to the S0BUF function register. Reception is initiated in Mode

0 when RI = 0 and REN = 1. In the other three modes, reception is

initiated by the incoming start bit provided that REN = 1.

Modes 2 and 3 are provided for multiprocessor communications. In