Philips OQ2536WC-C2, OQ2536HP-C2 Datasheet

DATA SH EET

Product specification

File under Integrated Circuits, IC19

1998 Mar 10

INTEGRATED CIRCUITS

OQ2536HP

SDH/SONET STM16/OC48

demultiplexer

1998 Mar 10 2

Philips Semiconductors Product specification

SDH/SONET STM16/OC48 demultiplexer OQ2536HP

FEATURES

• Normal and loop (test) modes

• 1.2 V GTL (Gunning Transceiver Logic) level compatible

data and clock outputs (low speed interface)

• Differential CML (Current-Mode Logic) data and clock

inputs

• High input sensitivity (100 mV for the high speed inputs)

• Boundary Scan Test (BST) at low speed interface, in

accordance with

“IEEE Std 1149.1-1990”

• Low power dissipation (typically 1.45 W).

DESCRIPTION

The OQ2536HP is a 32-channel demultiplexer intended

for use in STM16/OC48 applications. It demultiplexes a

single 2.5 Gbits/s input channel to 32 × 78 Mbits/s output

channels. The data and clock outputs on the low speed

interface are GTL compatible, while the high speed data

and clock inputs are CML compatible.

ORDERING INFORMATION

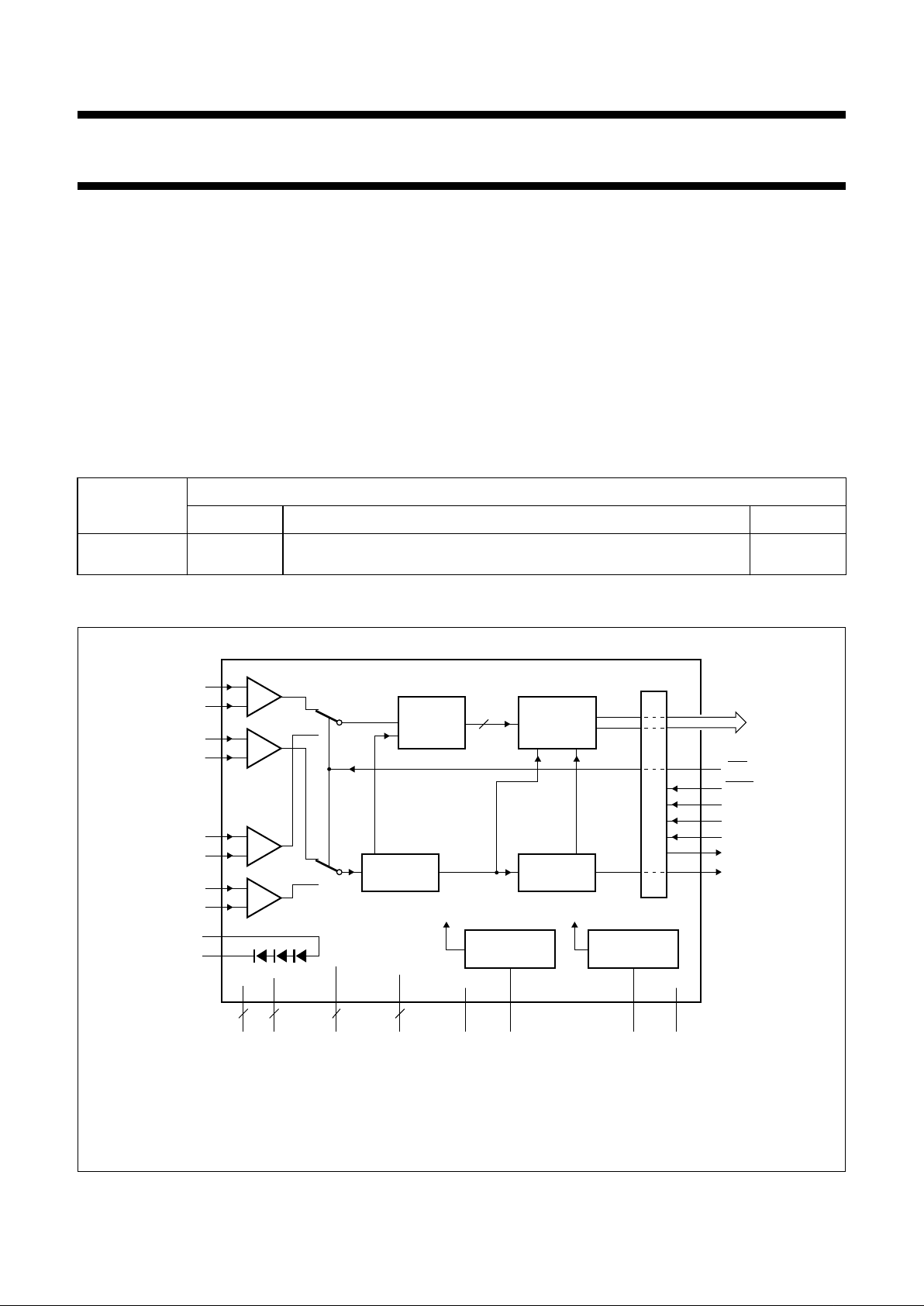

BLOCK DIAGRAM

TYPE

NUMBER

PACKAGE

NAME DESCRIPTION VERSION

OQ2536HP HLQFP100 plastic heat-dissipating low profile quad flat package; 100 leads; body

14 × 14 × 1.4 mm

SOT470-1

Fig.1 Block diagram.

(1) See Chapter “Pinning” for D0 to D31 pin numbers.

(2) Pins 1, 8, 17, 22, 25, 29, 33, 35, 40 to 50, 52, 55, 58, 61, 64, 67, 78, 82, 91 and 96.

handbook, full pagewidth

4

ENL

TRST

TMS

TCK

TDI

TDO

CDIV

DIN

DINQ

CIN

CINQ

DLOOP

DLOOPQ

CLOOP

CLOOPQ

DIOA

DIOC

1 : 4 DMUX

DIVIDE BY 4

622 MHz

OQ2536HP

78 MHz

2.5 GHz

BAND GAP

REFERENCE 1

DIVIDE BY 8

BST LOGIC

4 ×

1 : 8 DMUX

622

Mbits/s

2.5 Gbits/s

78

Mbits/s

75

70

72

69

68

71

12

26, 27, 28,

76, 77

13, 14, 36,

37, 63, 85,

86

11, 38, 39,

62, 88

V

DD

V

CC1

V

EE

V

CC2

BGCAP1

29 5 7 5

(2)

(1)

GND

74 51

BAND GAP

REFERENCE 2

BGCAP2

34 73

REFC

54

53

56

57

65

66

60

59

32

31

D0

to

D31

MGK346

1998 Mar 10 3

Philips Semiconductors Product specification

SDH/SONET STM16/OC48 demultiplexer OQ2536HP

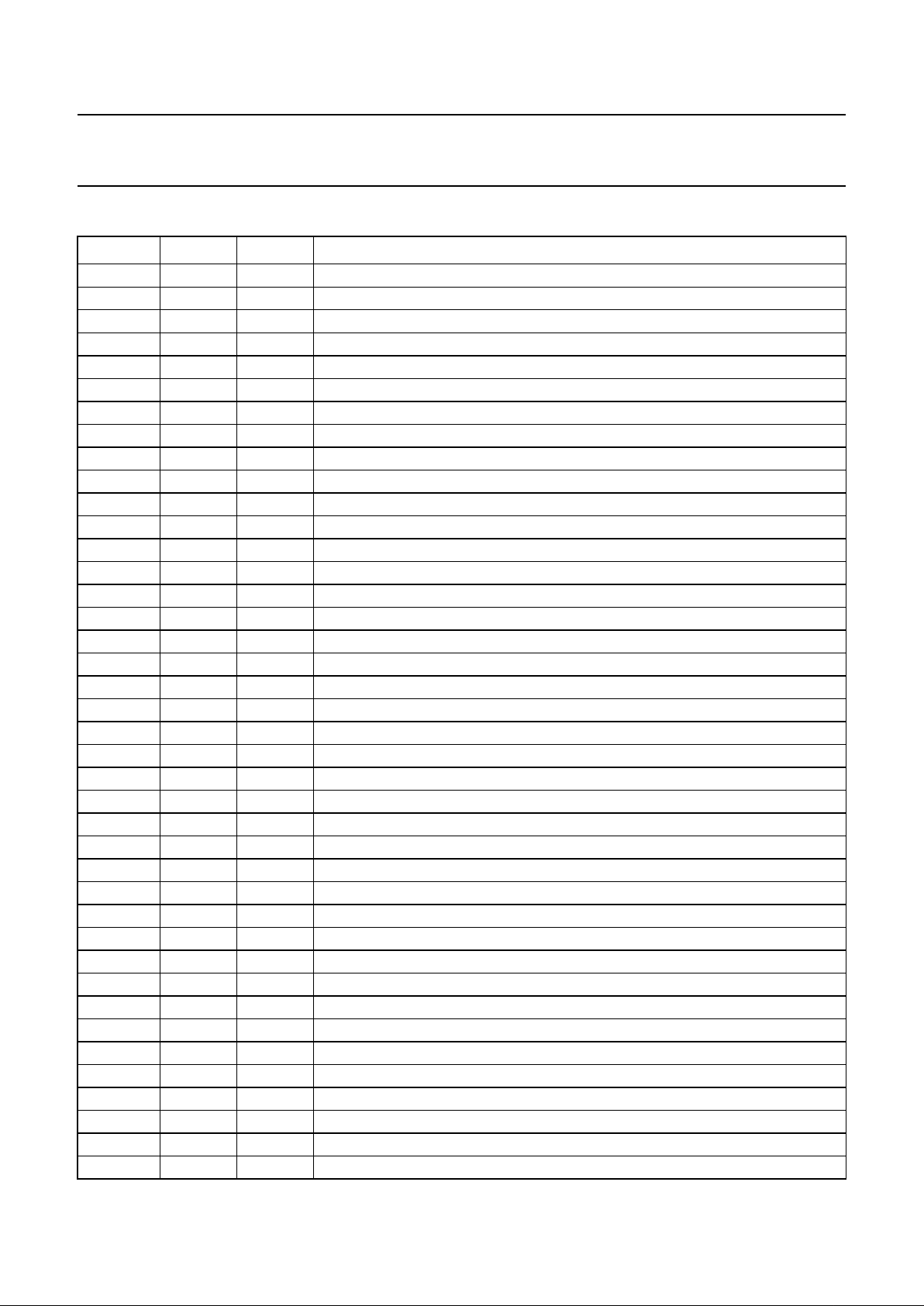

PINNING

SYMBOL PIN TYPE

(1)

DESCRIPTION

GND 1 S ground

D29 2 O 78 Mbits/s data output channel for D29

D25 3 O 78 Mbits/s data output channel for D25

D21 4 O 78 Mbits/s data output channel for D21

D17 5 O 78 Mbits/s data output channel for D17

D13 6 O 78 Mbits/s data output channel for D13

D9 7 O 78 Mbits/s data output channel for D9

GND 8 S ground

D5 9 O 78 Mbits/s data output channel for D5

D1 10 O 78 Mbits/s data output channel for D1

V

EE

11 S supply voltage (−4.5 V)

CDIV 12 O 78 MHz clock output

V

CC2

13 S supply voltage (+1.5 V)

V

CC2

14 S supply voltage (+1.5 V)

D28 15 O 78 Mbits/s data output channel for D28

D24 16 O 78 Mbits/s data output channel for D24

GND 17 S ground

D20 18 O 78 Mbits/s data output channel for D20

D16 19 O 78 Mbits/s data output channel for D16

D12 20 O 78 Mbits/s data output channel for D12

D8 21 O 78 Mbits/s data output channel for D8

GND 22 S ground

D4 23 O 78 Mbits/s data output channel for D4

D0 24 O 78 Mbits/s data output channel for D0

GND 25 S ground

V

DD

26 I supply voltage (+3.3 V)

V

DD

27 I supply voltage (+3.3 V)

V

DD

28 I supply voltage (+3.3 V)

GND 29 S ground

i.c. 30 − internally connected, to be left open-circuit

DIOC 31 A cathode of temperature diode array

DIOA 32 A anode of temperature diode array

GND 33 S ground

BGCAP2 34 A pin for connecting external band gap decoupling capacitor (4 × 1 : 8 DMUX)

GND 35 S ground

V

CC2

36 S supply voltage (+1.5 V)

V

CC2

37 S supply voltage (+1.5 V)

V

EE

38 S supply voltage (−4.5 V)

V

EE

39 S supply voltage (−4.5 V)

GND 40 S ground

1998 Mar 10 4

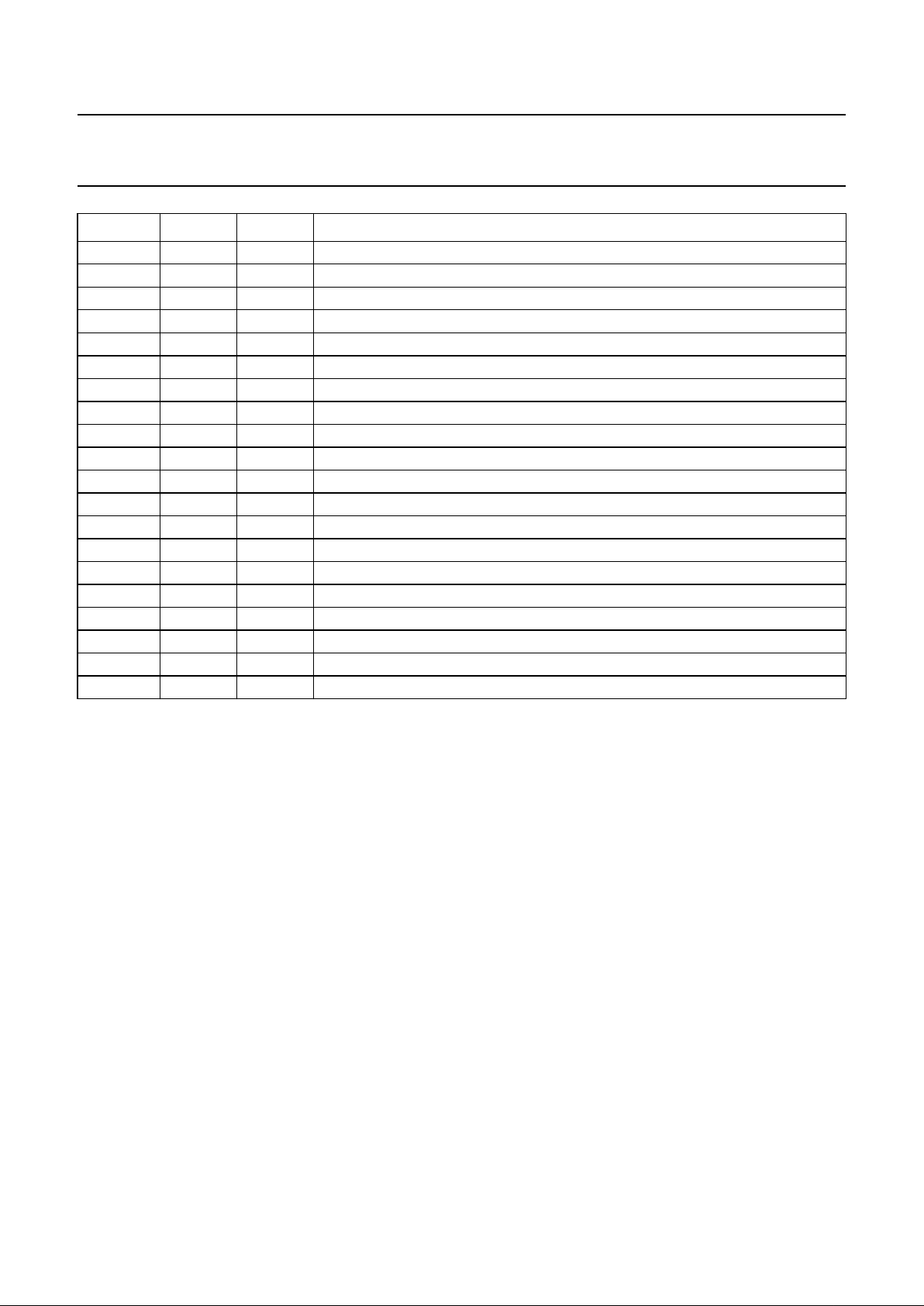

Philips Semiconductors Product specification

SDH/SONET STM16/OC48 demultiplexer OQ2536HP

GND 41 S ground

GND 42 S ground

GND 43 S ground

GND 44 S ground

GND 45 S ground

GND 46 S ground

GND 47 S ground

GND 48 S ground

GND 49 S ground

GND 50 S ground

BGCAP1 51 A pin for connecting external band gap decoupling capacitor (1 : 4 DMUX)

GND 52 S ground

DINQ 53 I inverted data input in normal mode

DIN 54 I data input in normal mode

GND 55 S ground

CIN 56 I clock input in normal mode

CINQ 57 I inverted clock input in normal mode

GND 58 S ground

CLOOPQ 59 I inverted clock input from multiplexer IC OQ2535 (loop mode)

CLOOP 60 I clock input from multiplexer IC OQ2535 (loop mode)

GND 61 S ground

V

EE

62 S supply voltage (−4.5 V)

V

CC2

63 S supply voltage (+1.5 V)

GND 64 S ground

DLOOP 65 I data input from multiplexer IC OQ2535 (loop mode)

DLOOPQ 66 I inverted data input from multiplexer IC OQ2535 (loop mode)

GND 67 S ground

TRST 68 I test RESET input for BST mode (active LOW)

TMS 69 I test mode select input for BST

TCK 70 I test clock input for BST mode

TDO 71 O serial test data output for BST mode

TDI 72 I serial test data input for BST mode

REFC 73 A pin for connecting external reference decoupling capacitor (for standard TTL

reference)

V

CC1

74 S supply voltage (+5.0 V)

ENL 75 I loop mode enable input (active LOW)

V

DD

76 I supply voltage (+3.3 V)

V

DD

77 I supply voltage (+3.3 V)

GND 78 S ground

D31 79 O 78 Mbits/s data output channel for D31

D27 80 O 78 Mbits/s data output channel for D27

SYMBOL PIN TYPE

(1)

DESCRIPTION

1998 Mar 10 5

Philips Semiconductors Product specification

SDH/SONET STM16/OC48 demultiplexer OQ2536HP

Note

1. Pin type abbreviations: O = Output, I = Input, S = power Supply, A = Analog function.

D23 81 O 78 Mbits/s data output channel for D23

GND 82 S ground

D19 83 O 78 Mbits/s data output channel for D19

D15 84 O 78 Mbits/s data output channel for D15

V

CC2

85 S supply voltage (+1.5 V)

V

CC2

86 S supply voltage (+1.5 V)

D11 87 O 78 Mbits/s data output channel for D11

V

EE

88 S supply voltage (−4.5 V)

D7 89 O 78 Mbits/s data output channel for D7

D3 90 O 78 Mbits/s data output channel for D3

GND 91 S ground

D30 92 O 78 Mbits/s data output channel for D30

D26 93 O 78 Mbits/s data output channel for D26

D22 94 O 78 Mbits/s data output channel for D22

D18 95 O 78 Mbits/s data output channel for D18

GND 96 S ground

D14 97 O 78 Mbits/s data output channel for D14

D10 98 O 78 Mbits/s data output channel for D10

D6 99 O 78 Mbits/s data output channel for D6

D2 100 O 78 Mbits/s data output channel for D2

SYMBOL PIN TYPE

(1)

DESCRIPTION

1998 Mar 10 6

Philips Semiconductors Product specification

SDH/SONET STM16/OC48 demultiplexer OQ2536HP

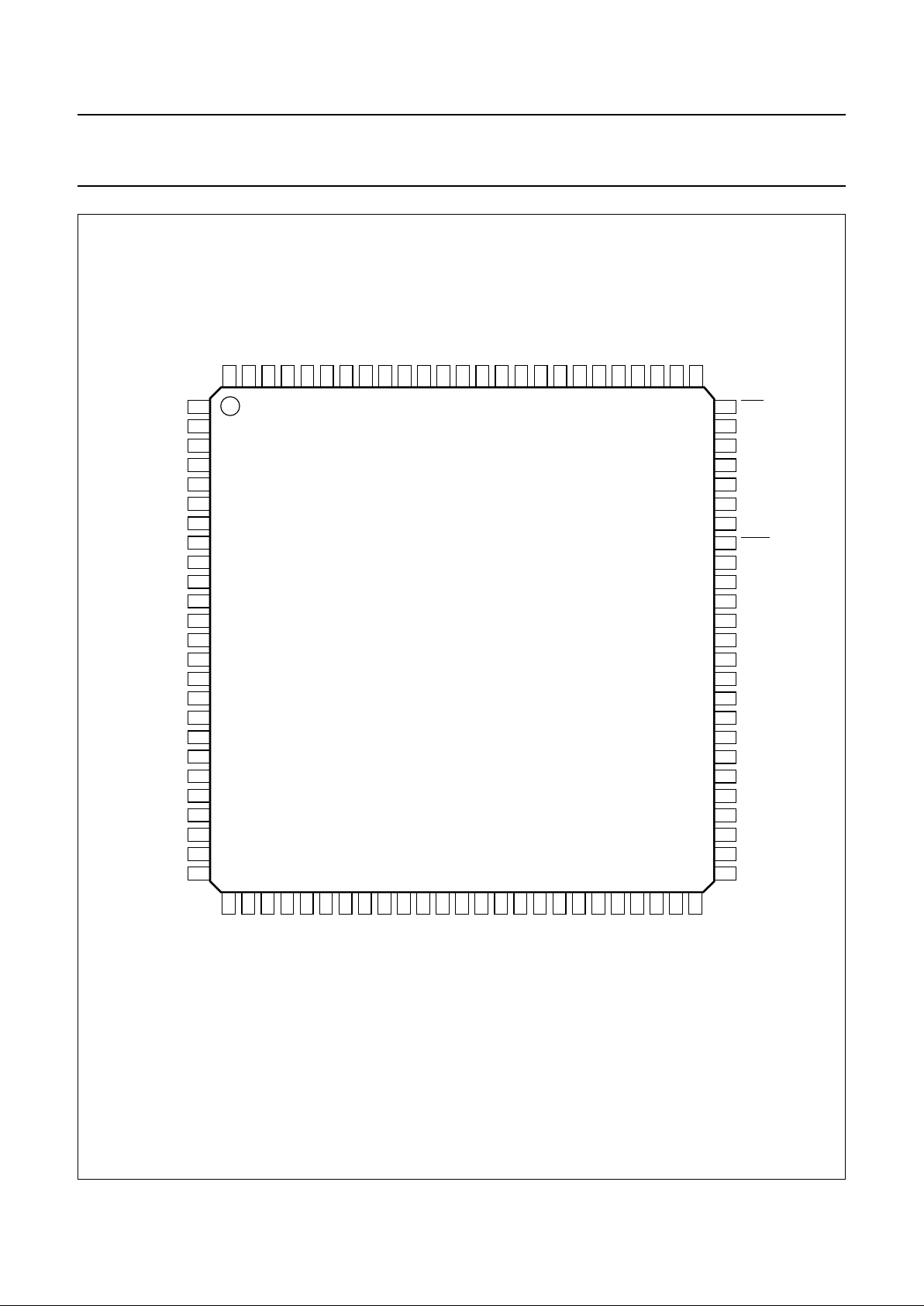

Fig.2 Pin configuration.

handbook, full pagewidth

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

8079787776

ENL

V

CC1

REFC

TDI

TDO

TCK

TMS

TRST

GND

DLOOPQ

DLOOP

GND

V

CC2

V

EE

GND

CLOOP

CLOOPQ

GND

CINQ

CIN

GND

DIN

DINQ

GND

BGCAP1

MGK345

GND

D29

D25

D21

D17

D13

D9

GND

D5

D1

V

EE

CDIV

V

CC2

V

CC2

D28

D24

GND

D20

D16

D12

D8

GND

D4

D0

GND

D27

D31

GND

VDDV

DD

D2D6D10

D14

GND

D18

D22

D26

D30

GNDD3D7

VEED11

V

CC2VCC2

D15

D19

GND

D23

DIOC

DIOA

GND

BGCAP2

GND

V

CC2VCC2

VEEV

EE

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

VDDVDDV

DD

GND

i.c.

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

100

99989796959493929190898887868584838281

31323334353637383940414243444546474849

50

OQ2536HP

Loading...

Loading...