查询OM6211供应商

INTEGRATED CIRCUITS

DATA SH EET

OM6211

48 × 84 dot matrix LCD driver

Product specification

File under Integrated Circuits, IC12

2002 Jan 17

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

CONTENTS

1 FEATURES

2 APPLICATIONS

3 GENERAL DESCRIPTION

4 ORDERING INFORMATION

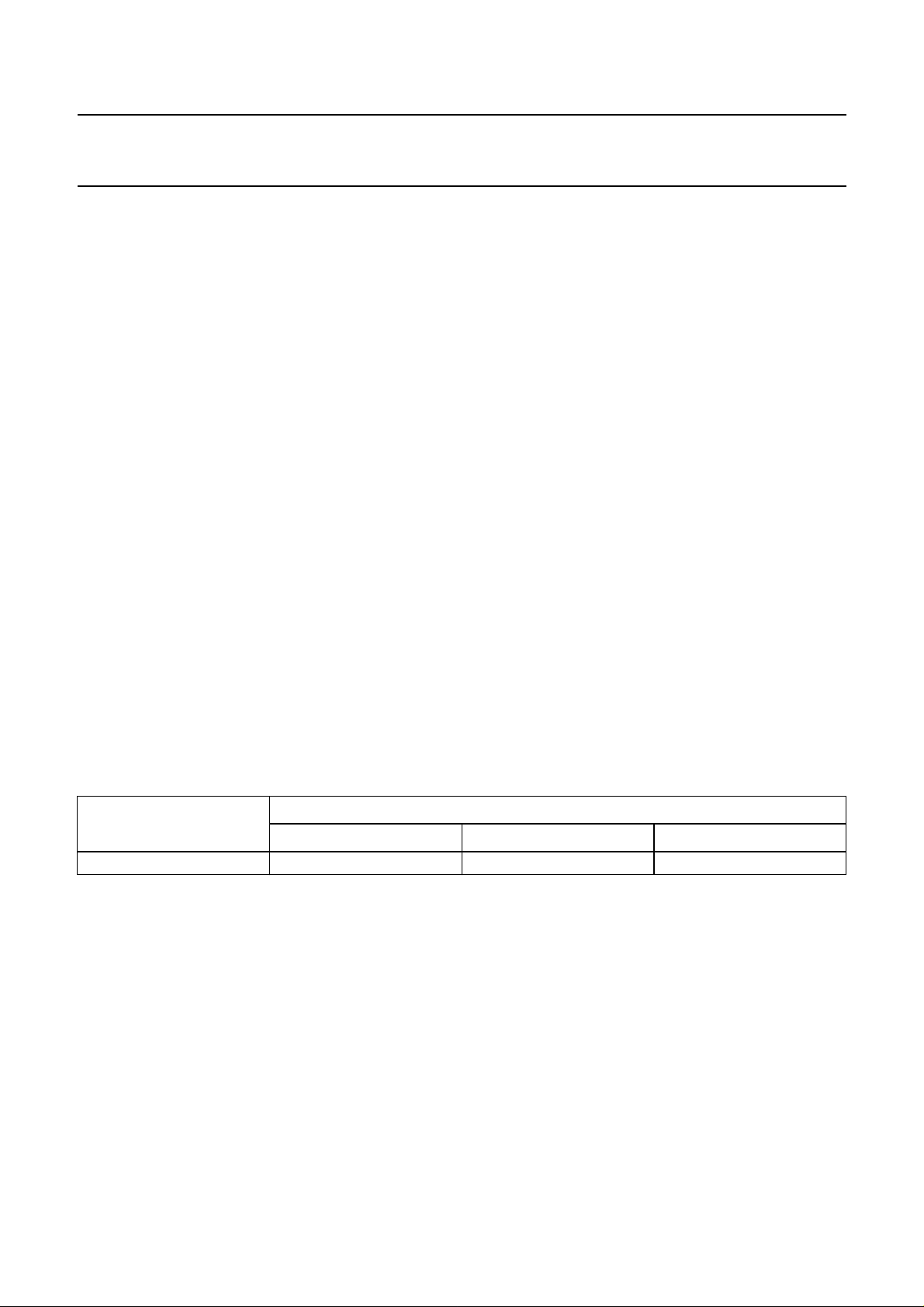

5 BLOCK DIAGRAM

6 PINNING

7 PIN FUNCTIONS

7.1 ROW 0 to ROW 47 row driver outputs

7.2 COL 0 to COL 83 column driver outputs

7.3 V

7.4 V

7.5 V

and V

SS1

to V

DD1

LCDOUT

: negative power supply rails

SS2

: positive power supply rails

DD3

, V

LCDIN

and V

LCDSENSE

: LCD power

supply

7.6 V

OS4

to V

: calibration inputs

OS0

7.7 SDIN: serial data input

7.8 SDOUT: serial data output

7.9 SCLK: serial clock input

7.10 SCE: chip enable

7.11 OSC: oscillator

7.12 MX: horizontal mirroring

7.13 ID3 and ID4: identification inputs

7.14 RES: reset

7.15 T1, T2, T3, T4, T5 and T6: test pins

8 BLOCK DIAGRAM FUNCTIONS

8.1 Oscillator

8.2 Serial interface control

8.3 Command decoder

8.4 Display data RAM (DDRAM)

8.5 Timing generator

8.6 Address Counter (AC)

8.7 Display address counter

8.8 V

generator

LCD

8.9 Bias voltage generator

8.10 LCD row and column drivers

8.11 Reset

9 FUNCTIONAL DESCRIPTION

9.1 Reset

9.2 Power-down

9.3 LCD voltage selector

9.4 Oscillator

9.5 Timing

9.6 Column driver outputs

9.7 Row driver outputs

9.8 Drive waveforms

9.9 Bias system

9.10 Voltage multiplier control

9.11 Temperature compensation

9.12 V

generator

LCD

10 INITIALIZATION

10.1 Initialization sequence

10.2 Frame frequency calibration (OC)

11 ADDRESSING

11.1 Addressing

11.2 Serial interface

11.2.1 Write mode

11.2.2 Read mode

12 INSTRUCTIONS

12.1 Instruction set

13 LIMITING VALUES

14 HANDLING

15 DC CHARACTERISTICS

16 AC CHARACTERISTICS

16.1 Serial interface timing

16.2 Reset timing

17 APPLICATION INFORMATION

18 MODULE MAKER PROGRAMMING

18.1 V

calibration

LCD

18.2 VPR default value

18.3 Seal bit

18.4 OTP architecture

18.5 Serial interface commands

18.5.1 Enable OTP

18.5.2 CALMM

18.5.3 Load factory default

18.5.4 Refresh

18.6 Example of filling the shift register

18.7 Programming flow

18.8 Programming specification

19 BONDING PAD LOCATIONS

20 DEVICE PROTECTION DIAGRAM

21 TRAY INFORMATION

22 DATA SHEET STATUS

23 DEFINITIONS

24 DISCLAIMERS

2002 Jan 17 2

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

1 FEATURES

• Single-chip LCD controller/driver

• 48 row, 84 column outputs

• Display data RAM 48 × 84 bits

• 3-line serial interface, maximum 4.0 Mbit/s

• On-chip:

– Generation of LCD supply voltage V

LCD

– Generation of intermediate LCD bias voltages

– Oscillator (requires no external components).

• CMOS compatible inputs

• Mux rate1:48

• Logic supply voltage range V

DD1

to VSS:

– 1.7 to 2.3 V.

• Supply voltage range for high voltage part V

DD2

to VSS:

– 2.5 to 4.5 V.

• LCD supply voltage range V

LCD

to VSS:

– 4.5 to 9.0 V.

• Low power consumption (typical 90 µA), suitable for

battery operated systems

• External reset

• Temperature compensation of V

• Temperature range: T

amb

LCD

= −40 to +85 °C

• Manufactured in N-well silicon gate CMOS process.

2 APPLICATIONS

• Battery powered telecommunication systems.

3 GENERAL DESCRIPTION

The OM6211 is a low power CMOS LCD row/column

driver, designed to drive a dot matrix graphic display of

48 rows and 84 columns. All necessary functions for the

display are provided in a single chip, including on-chip

generation ofLCDsupply and bias voltages, resulting in a

minimum of external components and low power

consumption. The OM6211 interfaces to microcontrollers

via a 3-line serial interface.

4 ORDERING INFORMATION

PACKAGE

TYPE NUMBER

NAME DESCRIPTION VERSION

OM6211U/2/F1 tray chip with bumps in tray −

2002 Jan 17 3

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

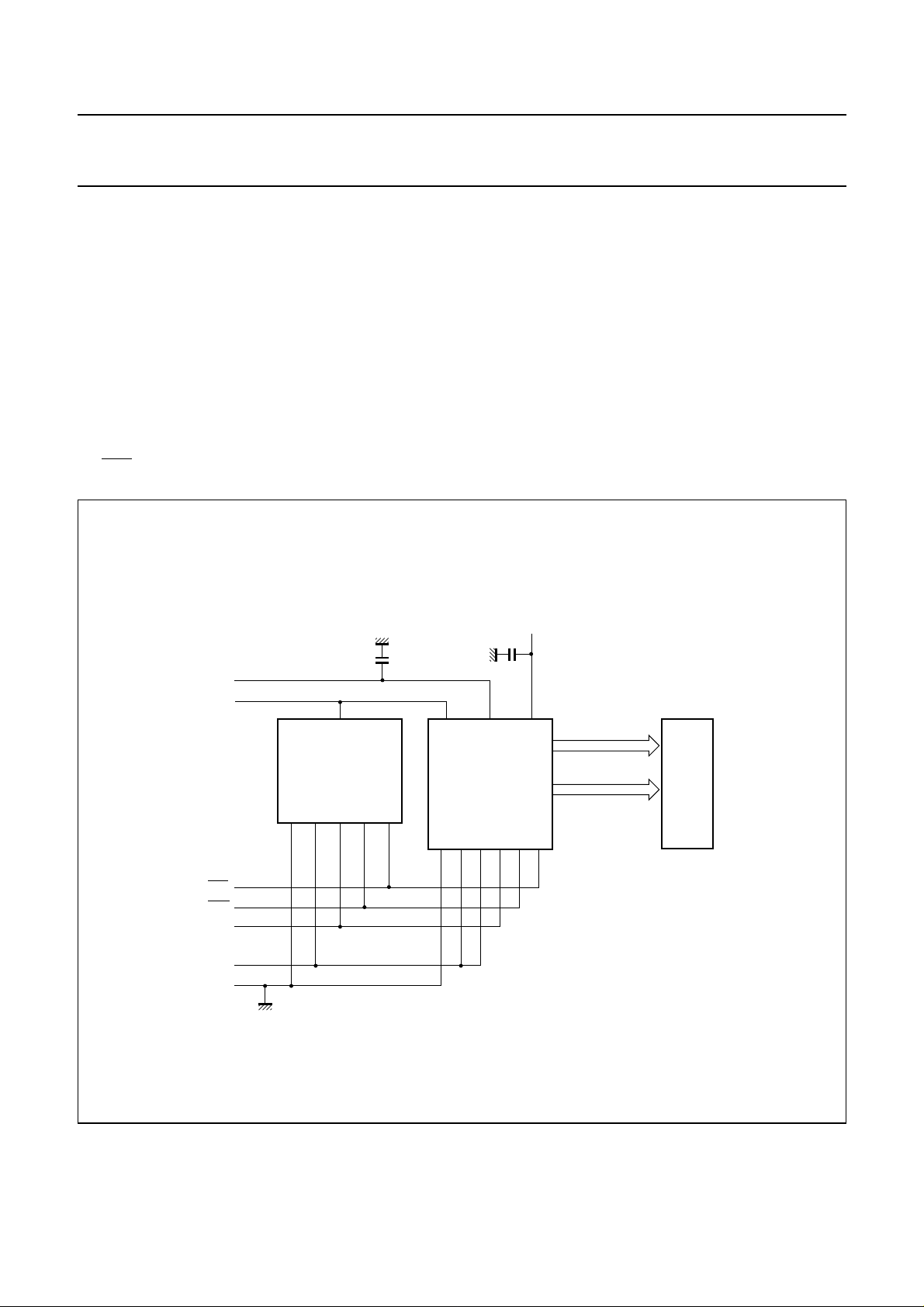

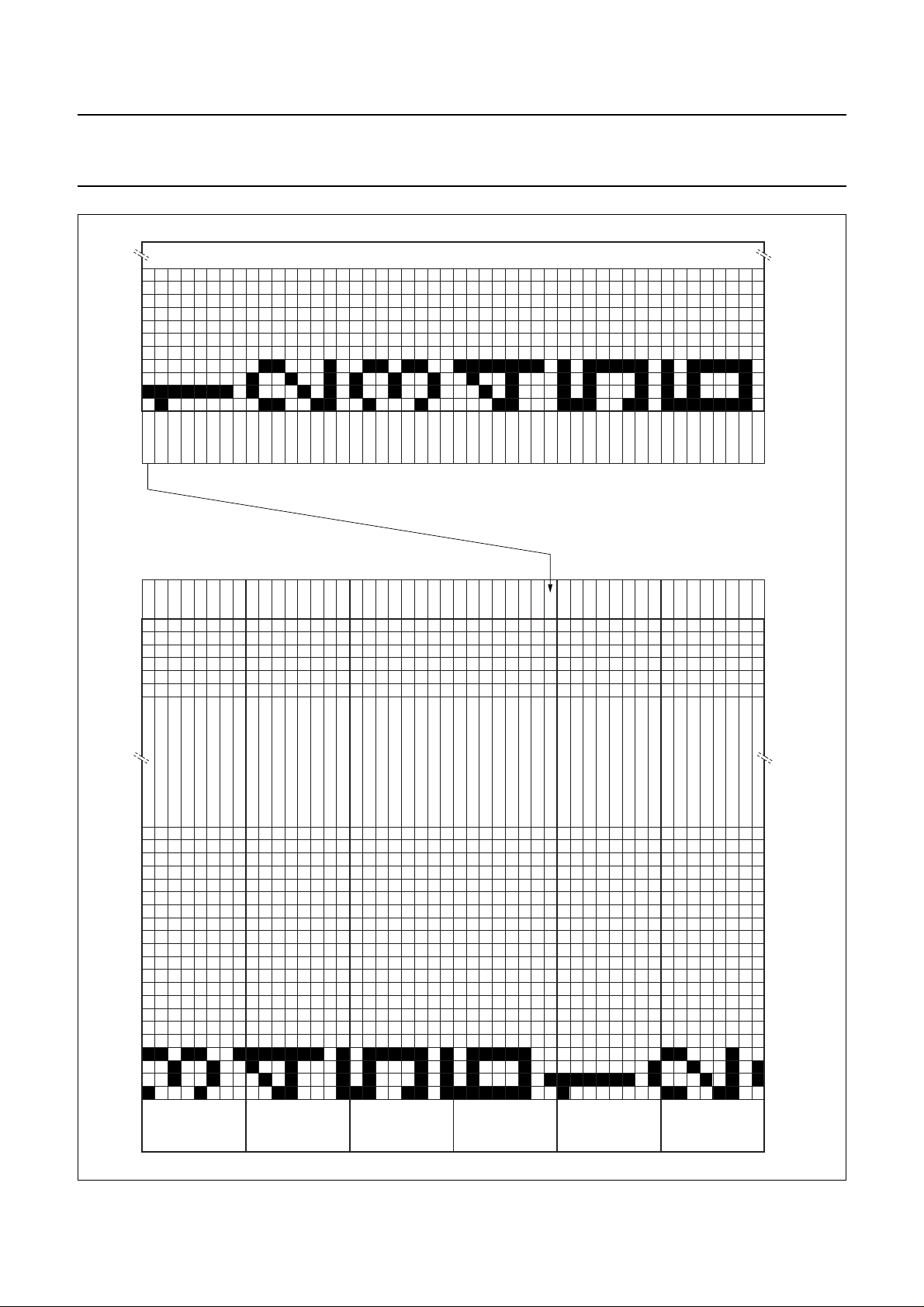

5 BLOCK DIAGRAM

V

handbook, full pagewidth

DD1

V

DD2VDD3

COL0 to COL83

ROW0 to ROW47

V

V

T4, T5,

T1, T2,

ID3, ID4

V

LCDIN

V

LCDsense

V

LCDOUT

V

OS

SCLK

SDOUT

SS1

SS2

T6

T3

MX

[

4:0

SDIN

84

COLUMN DRIVERS

3

3

2

BIAS

VOLTAGE

GENERATOR

V

LCD

GENERATOR

5

]

SERIAL INTERFACE

CONTROL

OM6211

DATA LATCHES

DISPLAY DATA RAM

48 × 84 bits

COMMAND

DECODER

SCE

SHIFT REGISTER

48

ROW DRIVERS

RESET

OSCILLATOR

TIMING

GENERATOR

DISPLAY

ADDRESS

COUNTER

ADDRESS

COUNTER

RES

OSC

MGU272

Fig.1 Block diagram.

2002 Jan 17 4

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

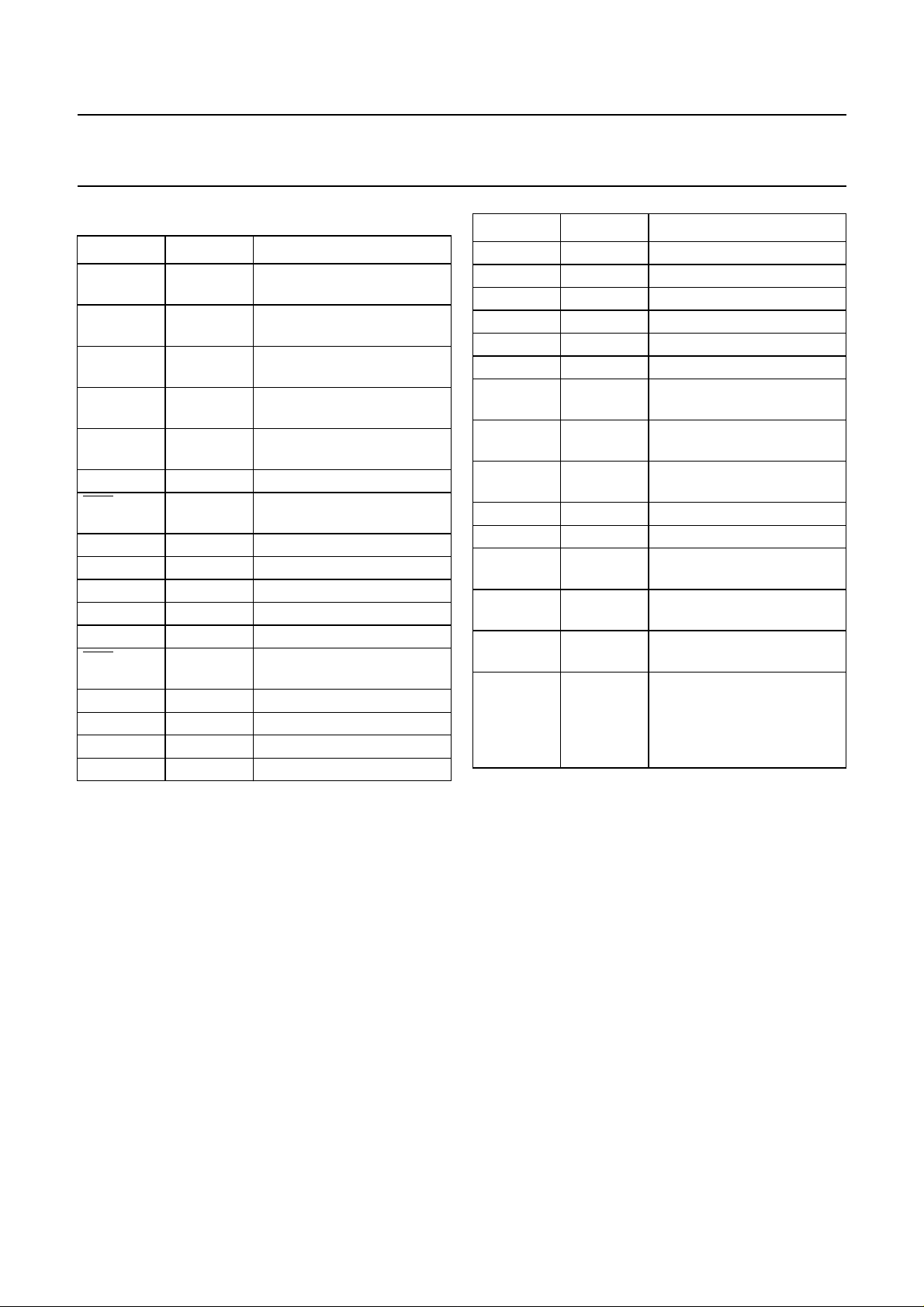

6 PINNING

SYMBOL PAD DESCRIPTION

V

OS4

3 input pin 4 for V

LCD

calibration

V

OS3

4 input pin 3 for V

LCD

calibration

V

OS2

5 input pin 2 for V

LCD

calibration

V

OS1

6 input pin 1 for V

LCD

calibration

V

OS0

7 input pin 0 for V

LCD

calibration

T6 8 to 11 test input 6

RES 16 external reset input

(active LOW)

T5 17 test input 5

T4 18 test input 4

T3 19 test output 3

T2 20 test output 2

T1 21 test output 1

SCE 22 chip enable input

(active LOW)

V

SS2

V

SS1

23 to 30 ground

31 to 38 ground

OSC 40 oscillator input

SDOUT 41 serial data output

SYMBOL PAD DESCRIPTION

SDIN 42 serial data input

SCLK 43 serial clock input

ID4 44 module identification input

ID3 45 module identification input

MX 46 horizontal mirroring input

V

DD1

V

DD2

47 to 52 logic supply voltage

53 to 60 voltage multiplier supply

voltage

V

DD3

61 to 64 voltage multiplier supply

voltage

V

LCDSENSE

65 V

generator regulation

LCD

input

V

LCDOUT

V

LCDIN

ROW 0 to

66 to 72 V

generator output

LCD

73 to 78 LCD supply voltage input

89 to 112 LCD row driver outputs

ROW 23

COL0to

113 to 196 LCD column driver outputs

COL 83

ROW 47 to

197 to 220 LCD row driver outputs

ROW 24

1,12 to 15,

dummy pads

39, 79,

81 to 88

and

221 to 225

7 PIN FUNCTIONS

7.1 ROW 0 to ROW 47 row driver outputs

These pads output the display row signals.

7.2 COL 0 to COL 83 column driver outputs

These pads output the display column signals.

7.3 V

Negative power supply rails V

SS1

and V

: negative power supply rails

SS2

SS1

and V

must be

SS2

connected together, hereafter referred to as VSS. When a

pin has to be connected externally to VSS, then pin V

SS1

should be used.

7.4 V

Positivepowersupplyrails: V

V

DD3

connected together, hereafter referred to as V

DD1

to V

: positive power supply rails

DD3

for voltage multiplier. V

forlogicsupply,V

DD1

and V

DD2

DD3

must be

DD2

DD2

.

and

2002 Jan 17 5

7.5 V

LCDOUT

, V

LCDIN

and V

LCDSENSE

: LCD power

supply

If the internal V

must be connected together. If not (V

disabledand an external voltageisapplied to V

V

must be left open-circuit, V

LCDOUT

connected to V

generator is used, then all three pins

LCD

generator is

LCD

LCDIN

must be

LCDIN

, V

DD2

and V

LCDSENSE

should be applied

DD3

),then

according to the specified voltage range. The following

settings are also required: HVE = 0, S1= 1 and S0=0.

7.6 V

Five pull-up input pins for on-glass V

OS4

to V

: calibration inputs

OS0

calibration. Each

LCD

pin may be connected to VSS, which corresponds to

logic 0, or left open-circuit, which corresponds to logic 1.

All five pins define a 5-bit two’s complement number

ranging from −16 to 15 decimal (from 10000 to 01111).

The default value, with all pins connected to VSS, is

0 decimal (00000).

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

In order to reduce current consumption related to the

pull-up circuitry, the 5-bit number is stored in a register

when exiting the Power-down mode. The pull-up circuitry

is then disabled. Additionally, the register is refreshed by

each HVE command.

7.7 SDIN: serial data input

Serial data input.

7.8 SDOUT: serial data output

Serial data output (3-state, push-pull). If bidirectional data

transmission is required, SDOUT and SDIN should be

connected externally. If the read mode is not used,

SDOUT should be left open-circuit.

7.9 SCLK: serial clock input

Serial clock input.

7.10 SCE: chip enable

Chip enable input, active LOW. If SCE is HIGH, the SCLK

pulses are ignored.

7.11 OSC: oscillator

External clock input. The external clock is active only in a

special test mode, so in the application it is not available.

In normal mode (the internal on-chip oscillator used) this

input must be connected to VSS. If OSC is held HIGH, the

internal oscillator is disabled.

8 BLOCK DIAGRAM FUNCTIONS

8.1 Oscillator

The on-chip oscillator provides the clock signal for the

display system. It has no external components.

8.2 Serial interface control

Detects the serial interface protocol, commands and

display data bytes. The serial interface converts the data

input (serial-to-parallel) as well as the output bits.

8.3 Command decoder

Decodes all commands.

8.4 Display Data RAM (DDRAM)

The OM6211 contains a 48 × 84 bit static RAM which

stores the display data. The RAM is divided into six banks

of 84 bytes (6 × 8 × 84 bits). During RAM access, data is

transferred to the RAM via the serial interface. There is a

directcorrespondencebetween the X address and column

output number.

8.5 Timing generator

The timing generator produces the various signals

required to drive the internal circuitry. Internal chip

operation is not disturbed by operations of the serial

interface.

8.6 Address Counter (AC)

7.12 MX: horizontal mirroring

Horizontal mirroring input. When MX = 1 the X address

space is mirrored.

7.13 ID3 and ID4: identification inputs

LCD module identification inputs. Their state can be read

out via the serial interface in order to identify the module

version.

7.14 RES: reset

External reset pin. When LOW the chip will be reset as

defined in Section 9.1. The initialization by the RES pin is

always required during power-on. Timing for the RES pin

is illustrated in Fig.18.

7.15 T1, T2, T3, T4, T5 and T6: test pins

Test pins. Inthe application T4 and T5 mustbe connected

toVSS.T1, T2, T3 and T6 must be left open-circuit(T6 has

a pull-down resistor).

2002 Jan 17 6

The address counter assigns addresses to the display

data RAM for writing. The X address (X6to X0) and the

Y address (Y2to Y0) are set separately. After a write

operation the address counter is automatically

incremented by 1.

8.7 Display address counter

The display is generated by continuously shifting rows of

RAM data to the dot matrix LCD via the column outputs.

The display status(all dotson/off, normal/inverse video) is

set via the serial interface.

8.8 V

generator

LCD

A voltage multiplier (charge pump) with a programmable

number of stages. Internal capacitors are used for the

voltage multiplier, therefore only decoupling capacitors for

V

LCD

and V

are required.

DD2

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

8.9 Bias voltage generator

Generates 4 intermediate LCD bias voltages. The bias

system is selectable; see Section 9.9.

8.10 LCD row and column drivers

The OM6211 contains 48 row and 84 column drivers,

which connect the appropriate LCD bias voltages in

sequence to the display in accordance with the data to be

displayed. Figure 3 shows typical waveforms.

8.11 Reset

A reset initializes the chip. It can be performed either by

the RES pin being LOW or by a command.

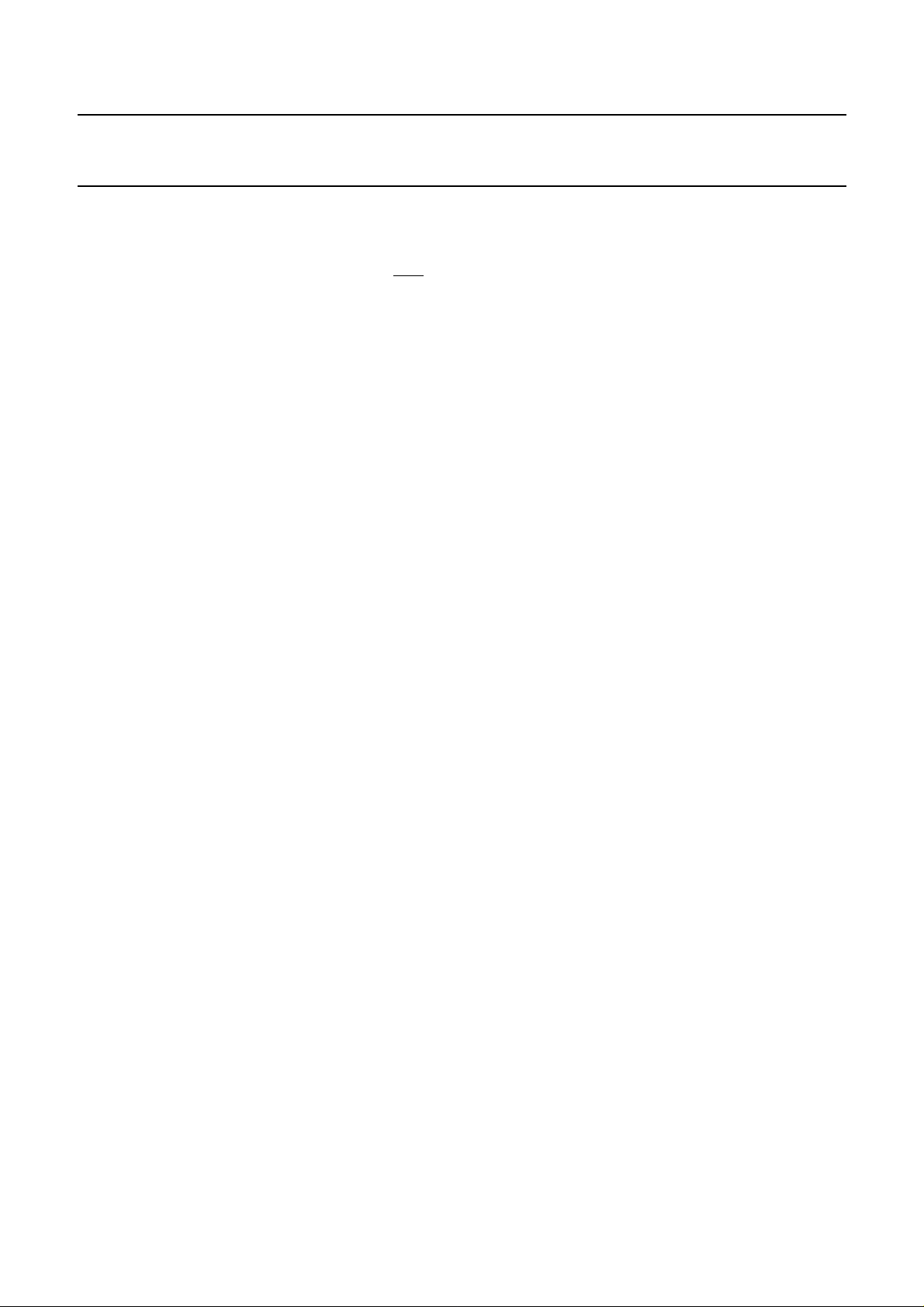

handbook, full pagewidth

V

V

V

DD2

DD1

DD2, 3

V

DD1

9 FUNCTIONAL DESCRIPTION

The OM6211 is a low power LCD driver designed to

interface with microprocessors/microcontrollers and a

wide variety of LCDs.

The host microprocessor or microcontroller and the

OM6211 are connected via a serial interface. The internal

oscillator requires no external components. The

appropriate intermediate bias voltages for the multiplexed

LCD waveforms are generated on-chip. The only other

connections required to complete the system are to the

power supplies (V

capacitors for decoupling V

V

LCD

DD1

, V

DD2

, VSS and V

and V

LCD

) and suitable

LCD

.

DD2

RES

SCE

SCLK

SDA

V

SS

HOST

MICROPROCESSOR/

MICROCONTROLLER

V

SS

84 column drivers

48 row drivers

V

SS1, 2

OM6211

Fig.2 Typical system configuration.

LCD

PANEL

MGU273

2002 Jan 17 7

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

9.1 Reset

TheOM6211 has no internalPower-onreset, only external

reset and reset by command. After power-on an external

reset is required. A reset initiated either from the RES pin

or by command will initialize the chip to the following

starting conditions:

• Power-down mode (DON = 0 and DAL = 1):

– Internal oscillator stopped

– The V

(HVE = 0) and V

generator (HV generator) is switched off

LCD

is 3-state

LCDOUT

– Display is off and all LCD outputs are internally

connected to VSS (DON = 0)

– Display all points is on (DAL = 1).

• Serial interface initialized; write mode

• Display normal video (E = 0)

• Address counter X6to X0=0;Y2to Y0= 0; display start

line Z5to Z0= 0; no Y mirroring (MY = 0)

1

• Bias system

• V

selection V

LCD

⁄7 (BS2to BS0= 100)

PR7

to V

PR0

=0

• Voltage multiplication factor 4 (S1and S0= 10)

• Temperature control mode TC3 (TC1and TC0= 11)

• Frequency not calibrated and OC = 0

• RAM data is unchanged (after power-up undefined).

9.3 LCD voltage selector

The practical value for V

V

with a defined LCD threshold voltage (Vth),

off(rms)

is determined by equating

LCD

typically when the LCD exhibits approximately 10%

contrast.

9.4 Oscillator

The internal logic operation and the multi-level drive

signals of the OM6211 are clocked by the built-in RC

oscillator. No external components are required. The

oscillator is in operation as long as the chip is not in

Power-down mode.

9.5 Timing

The timing of the OM6211 organizesthe internal data flow

of the device. The timing also generates the LCD frame

frequency that is derived from the clock frequency

generated by the internal clock generator.

9.6 Column driver outputs

The LCD drive section includes 84 column outputs, which

should be connected directly to the LCD. The column

output signals are generated in accordance with the

multiplexed row signals and with the data in the display

latch. If less than 84 columns are required, the unused

column outputs should be left open-circuit.

9.2 Power-down

The chip is in Power-down mode if the display is off

(DON = 0) and display all points is on (DAL = 1),

regardless of the order in which both bits are set. During

the Power-down mode almost all static currents are

switched off (no internal oscillator, no timing and no LCD

segment drive system), and all LCD outputs are internally

connected to VSS. The V

generator is switched off (but

LCD

HVEis not affected).The serial interfacefunction remains.

RAM data is unchanged. When exiting the Power-down

mode, the VOS value is stored in a register.

9.7 Row driver outputs

The LCD drive section includes 48 row outputs, which

should be connected directly to the LCD. If less than

48 rows are required, the unused row outputs should be

left open-circuit.

2002 Jan 17 8

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

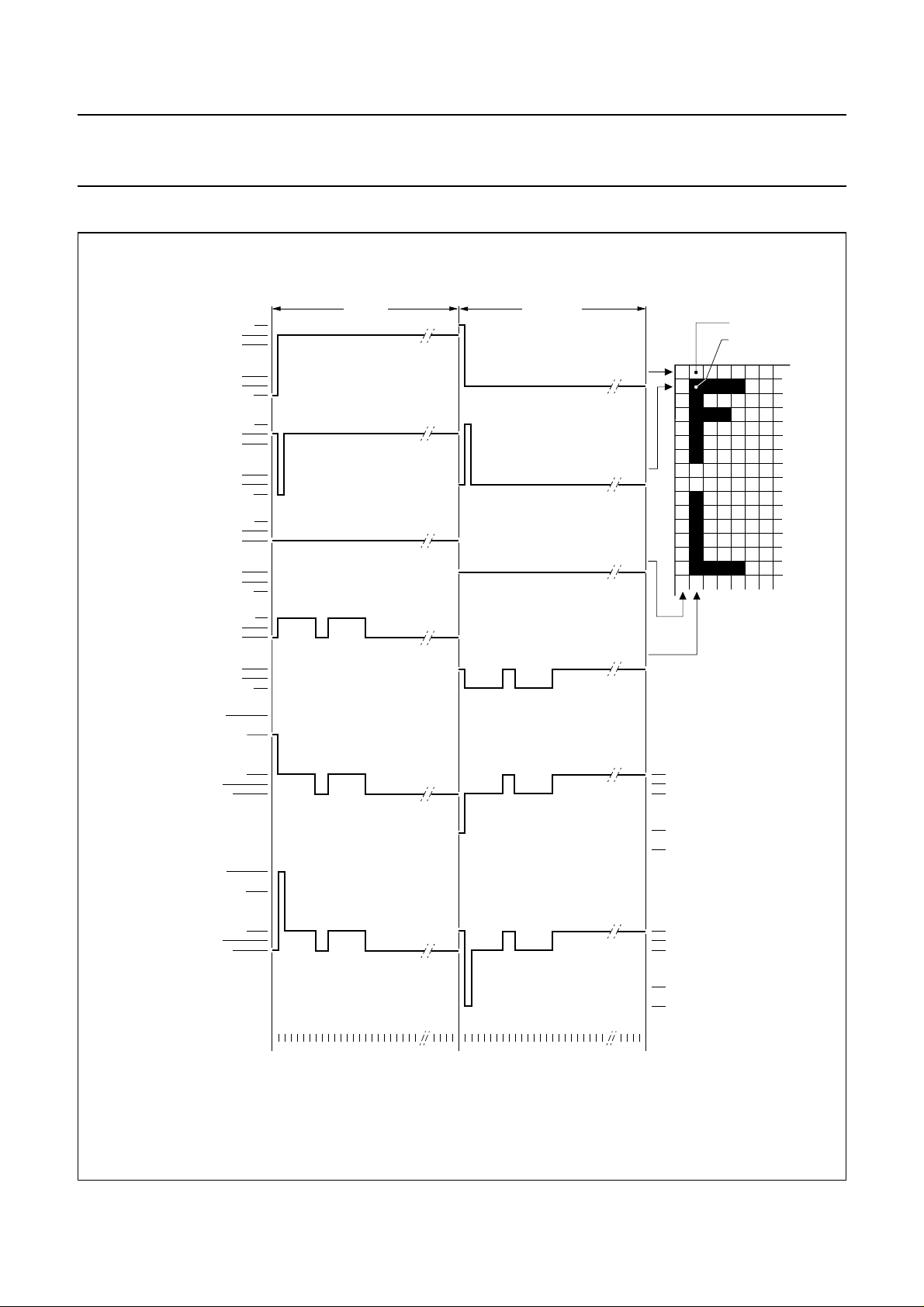

9.8 Drive waveforms

ROW 0

R0 (t)

ROW 1

R1 (t)

COL 0

C0 (t)

COL 1

C1 (t)

V

V3 − V

LCD

SS

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

LCD

2

3

4

5

SS

LCD

2

3

4

5

SS

LCD

2

3

4

5

SS

LCD

2

3

4

5

SS

frame n frame n + 1

V

state1

V

state2

(t)

(t)

V

− V

LCD

V

V

V

(t) = C1(t) − R0(t).

state1

V

(t) = C1(t) − R1(t).

state2

state1

state2

(t)

(t)

0 V

V3 − V

V

LCD

V3 − V

V

LCD

0 V

V3 − V

2

SS

− V

2

2

2

012345678... ... 47 012345678... ... 47

Fig.3 Typical LCD driver waveforms.

2002 Jan 17 9

V4 − V

0 V

VSS − V

V4 − V

− V

LCD

V4 − V

0 V

VSS − V

V4 − V

− V

LCD

MGU274

5

5

LCD

5

5

LCD

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

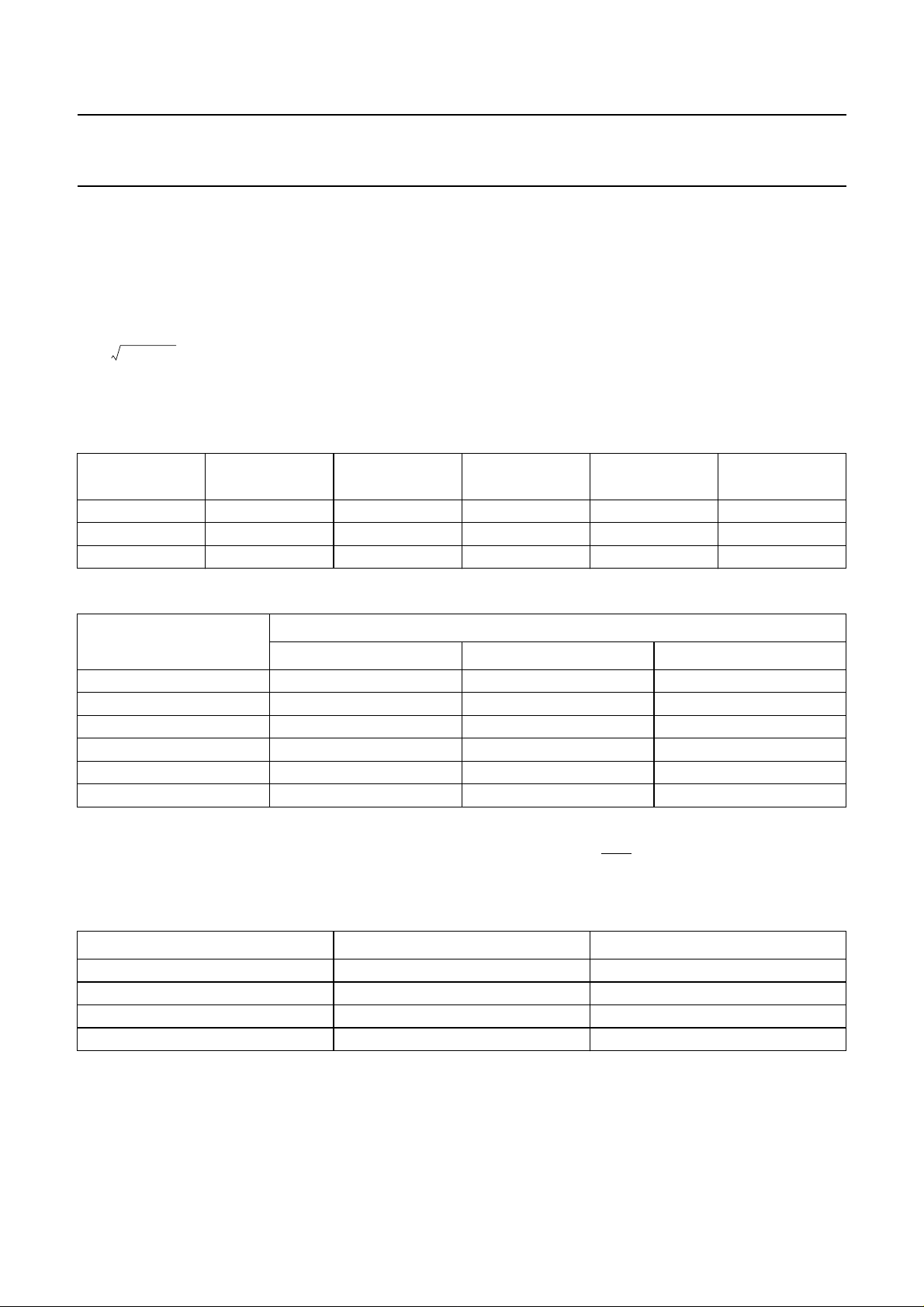

9.9 Bias system

The bias voltage levels are set in the ratio of

R-R-nR-R-R. Different multiplex rates require

different factors of n. This is programmed by BS2to BS0.

For optimum bias values, n can be calculated from the

following equation:

n Mux rate 3–=

; where Mux rate is 48.

Changing the bias system from the optimum setting will

have a consequence on the contrast and viewing angle.

Table 1 Programming the required bias system

BS

2

BS

1

BS

0

0114

1003

1012

Table 2 LCD bias voltages for

SYMBOL

V1 V

V2

V3

V4

V5

V6 V

1

⁄6bias,1⁄7bias and1⁄8bias.

1

⁄6BIAS FOR1⁄7BIAS FOR1⁄8BIAS

FOR

LCD

5

⁄6V

LCD

4

⁄6V

LCD

2

⁄6V

LCD

1

⁄6V

LCD

SS

One reason to depart from the optimum would be to

reduce the required V

contrast and V

must be found for any particular

LCD

voltage. A compromise between

LCD

application.

In the OM6211 one of three possible values of the bias

1

system can be selected. The value

n BIAS MODE

1

⁄

8

1

⁄

7

1

⁄

6

⁄7 is default.

TYPICAL MUX

RATES

1 : 55 and 1 : 48

1:33

1:24

BIAS VOLTAGE

V

LCD

6

⁄7V

LCD

5

⁄7V

LCD

2

⁄7V

LCD

1

⁄7V

LCD

V

SS

V

LCD

7

⁄8V

LCD

6

⁄8V

LCD

2

⁄8V

LCD

1

⁄8V

LCD

V

SS

9.10 Voltage multiplier control

The OM6211 incorporates a software configurable voltage multiplier. After reset (

4V

. Other voltage multiplier factors are set via the serial interface (S1and S0).

DD2

Table 3 HV generator multiplication

S

1

S

0

002V

013V

104V

1 1 not available

2002 Jan 17 10

RES) the voltage multiplier is set to

MULTIPLICATION

DD2

DD2

DD2

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

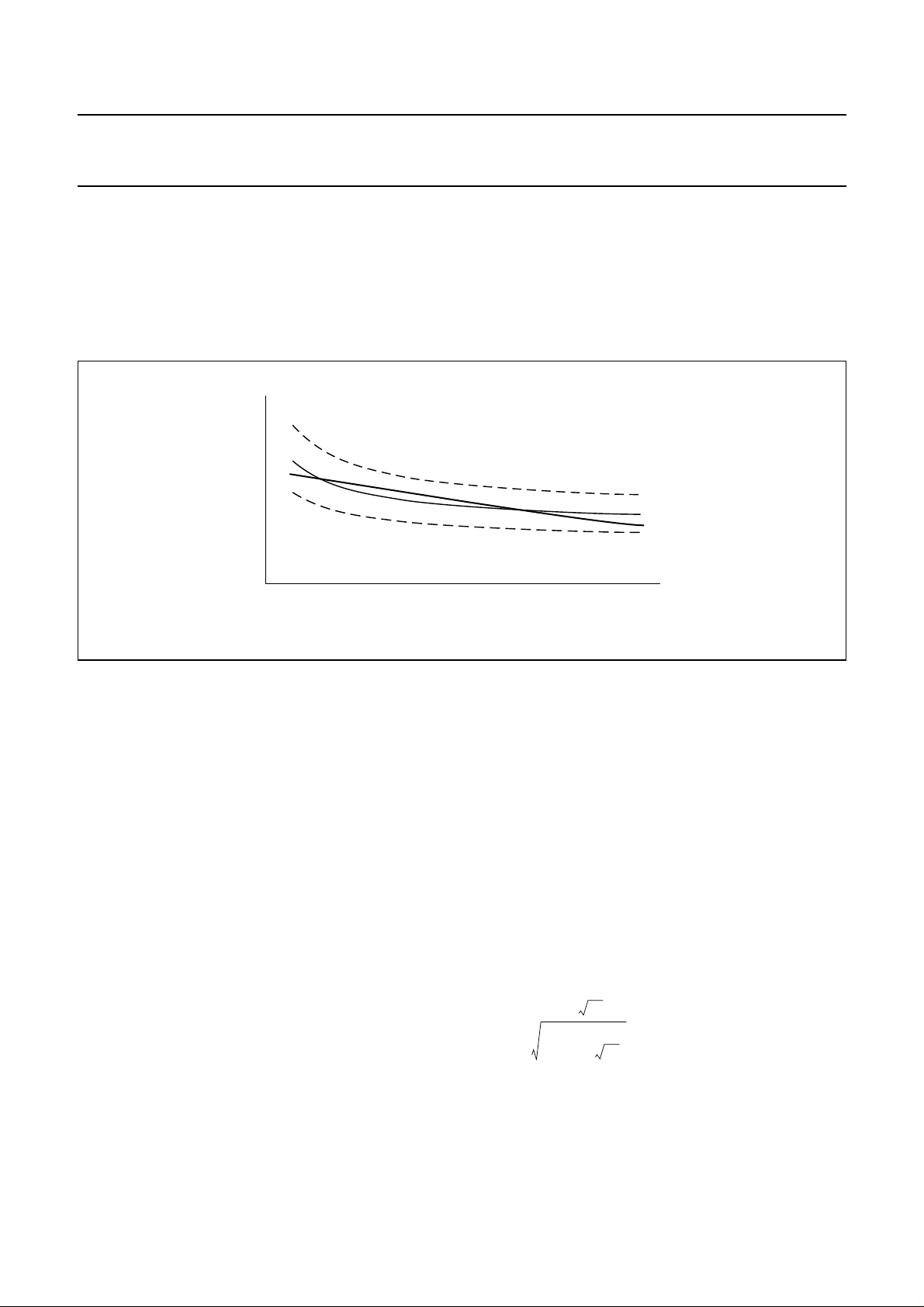

9.11 Temperature compensation

Due to thetemperature dependencyof the liquid crystals viscosity, the LCDcontrolling voltage(V

at lower temperatures to maintain optimum contrast. Figure 4 shows V

as a function of temperature for a typical high

LCD

multiplex rate liquid.

In the OM6211 the temperature coefficient of V

can be selected from 4 values by setting bits TC1and TC0,

LCD

see Tables 4 and 8.

handbook, full pagewidth

9.12 V

generator

LCD

Thebinary number V

V

LCD

Fig.4 V

representingthe operating voltage

OP

as a function of liquid crystal temperature (typical values).

LCD

can be set by the serial interface command and can be

adjusted (calibrated) by 5 input pins according to the

following formula:

V

OP

V

+=

PRVOS

(1)

where:

is an 8-bit unsigned number set by the serial

• V

PR

interface command

• VOS is a 5-bit two’s complement number set by the

5 input pins V

OS4

to V

, see Table 9

OS0

• VOP is an 8-bit unsigned number used internally for

generation of the LCD supply voltage V

To avoid numerical overflow the allowed values of V

LCD

.

PR

should be limited to the range 32 to 225 (decimal).

The corresponding voltage at the reference temperature,

T

, can be calculated as follows:

nom

V

LCD(Tnom)

The generated voltage at V

aVOPb×+()=

is dependent on the

LCD

(2)

V

LCD

T

nom

aV

+ b×()1TC TT

OP

, a and b foreach temperaturecoefficient are given in

Table 4. The maximum voltage that can be generated is

dependent on the voltage of V

current.

As the programming range for the internally generated

V

allows values abovethe maximumallowed V

LCD

user has to ensure while setting the VPR register and

selecting the Temperature Compensation, that under all

conditions and including all tolerances the V

maximum 9 V will never be exceeded.

For a particular liquid crystal, the optimum value of V

can be calculated for a givenmultiplex rate. Fora Mux rate

of 1 : 48, the optimum operating voltage of the liquid

crystal can be calculated as follows;

V

LCD

where V

148+

---------------------------------------

21

×

is the thresholdvoltage of theliquid crystal used.

th

–

1

---------48

T

MGT848

× 6.06 Vth×==

V

DD2

th

temperature, programmed Temperature Coefficient (TC)

and the programmedvoltage at thereference temperature

(T

).

nom

) must beincreased

LCD

–()×+[]×=

nom

and the display load

LCD

limit of

LCD

(3)

, the

LCD

(4)

2002 Jan 17 11

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

Table 4 Typical values for parameters of the HV generator programming

SYMBOL TC0 TC1 TC2 TC3 UNIT

a 4.57 4.28 4.04 3.79 V

b 30.0 28.0 26.5 25.0 mV

T

nom

TC 0 −0.25 −0.5 −0.75 10

27 27 27 27 °C

-3

/°C

Example: to achieve V

Example for calibration: Before calibration VPR= 180 was applied, but the measured voltage was V

To decrease V

by 100 mV the best value for VOSis −4 decimal (11100 binary in the two’s complement notation). So

LCD

= 8.3 V at temperature T

LCD

for TC3 it is necessary to set VPR= 180 (decimal).

nom

LCD

= 8.4 V.

after calibration with VOS= −4 the proper VPR value is still 180.

As VOS is used for calibration and the default value is 0, for selecting the value of VPR it can always be considered that

VOS=0.

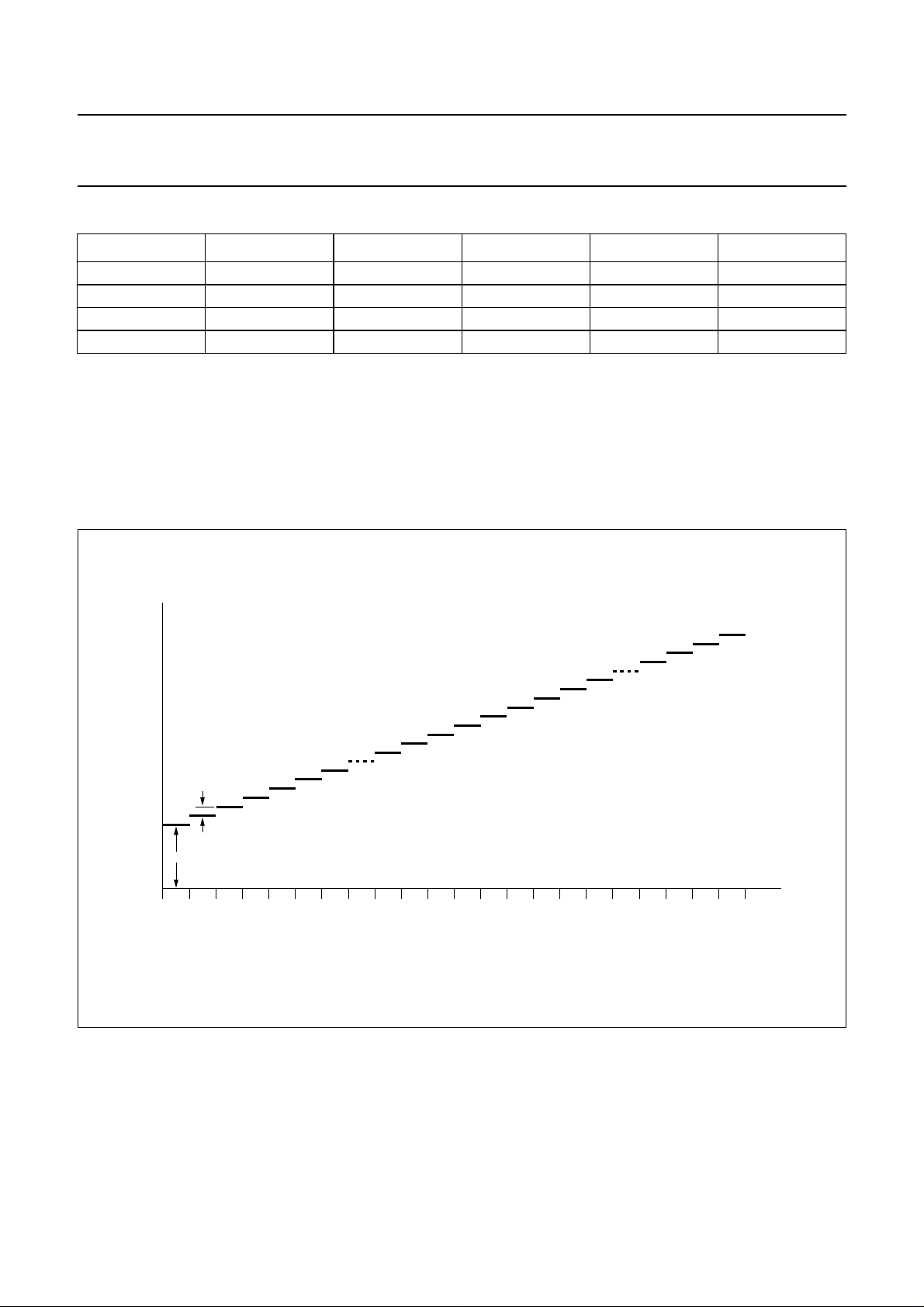

handbook, full pagewidth

V

LCD

b

MGT847

a

00 01 02

V

to V

OP7

programming, (00H to FFH).

OP0

03 04 05 06

. . . . . . FD FE FF

Fig.5 V

programming of OM6211.

LCD

2002 Jan 17 12

V

OP

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

10 INITIALIZATION

10.1 Initialization sequence

After reset (RES) it is recommended to initialize the V

LCD

generator using the following sequence; a starting state of

HVE = 0, DON = 0 and DAL = 1 is assumed:

1. Set the required VOP and, if required, the voltage

multiplier S1and S

0

2. SetDAL = 0to leave thePower-downstate (in order to

precharge the charge pump V

is set to V

LCD

DD2

)

3. Waitfor at least 1 msand set HVE = 1to switch-on the

V

generator

LCD

4. Set DON = 1 to switch the display on.

10.2 Frame frequency calibration (OC)

The OM6211 incorporates frame frequency calibration via

software. The calibrationis achievedby tuning the internal

oscillator. After reset the frame frequency calibration is

disabled (OC = 0). The calibration can only be performed

if the driver is not in Power-down mode. The calibration is

started by setting OC = 1 via the serial interface (start

command) and will be stopped by setting OC = 0 (stop

command). The time between start and stop of the

calibration must be 200 ms to give a frame frequency of

80 Hz. Any variation in calibration time (deviation from

200 ms) results in a corresponding variation in frame

frequency. During calibration all other commands are

allowed.

The calibration may be repeated and is always performed

with the previously calibrated frequency. Through

repeated calibrations a better accuracy can be expected

and, most especially, the temperature drift can be

compensated for. A minimum time delay of 500 ms

between consecutive calibration events is necessary

(between stop and start).

The calibration will always be performed if the calibration

time is between 190 and 210 ms. If, however, the

calibration time is lower then 58 ms or higher than 690 ms

(orthe stop commanddoesnot occur at all),the calibration

attemptisignored and the previously selectedfrequencyis

maintained. For the remaining values of the calibration

time(from 58 to 190 ms andfrom 210 to 690 ms) itcannot

be determined if the calibration will be performed or

ignored.

11 ADDRESSING

11.1 Addressing

Data is downloaded in bytes into the RAM matrix of

OM6211 as illustrated in Figs 6 and 7. The display RAM

has a matrix of 48 × 84 bits. The columns are addressed

by the address pointer. The address ranges are

X = 0 to 83 (1010011) and Y = 0 to 5 (101). Addresses

outside of these ranges are not allowed. The X address

increments after each byte (see Fig.7). After the last

X address (X = 83) X wrapsaround to 0 and Y increments

toaddress the next row.Afterthe very lastaddress(X = 83

and Y = 5) the address pointers wrap around to address

X = 0 and Y = 0.

The selection of the MX input allows horizontal mirroring:

whenMX = 1, the X addressspace is mirrored(see Fig.6).

When MX = 0 the mirroring is disabled. MX affects data

only during writing to the RAM, so after a change of MX

RAM data must be re-written.

The MY bit allows vertical mirroring: when MY = 1, then

the Y address space is mirrored. MY does not affect the

RAM content, but defines the way RAM data is written to

the display. A change of MY has an immediate effect on

the display.

Vertical scrolling of the display is controlled by the

Z address with a range from 0 to 47 (101111). The

Z address specifies which rows of the RAM are output to

which row outputs. The value of the Z address defines

which row of the RAM will be ROW 0 of the display (which

is normally the top row of the display). For example, if the

Z address is set to 31 (see Fig.8), then the data displayed

on ROW 0 of the display will be the data from ROW 31 of

the RAM and the data on ROW 1 will be from ROW 32 of

the RAM. When the MY is active (MY = 1), then the

Z address defines which row of the RAM is written to

ROW 47 of the display. For example, when the Z address

is set to 31, ROW 47 of the display would come from

ROW 31 of the RAM and ROW 46 from ROW 32 of the

RAM (see Fig.9).

The Z address does not affect the RAM content, but

defines the way RAM data is written to the display.

A change of Z address has an immediate effect on the

display.

2002 Jan 17 13

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

handbook, full pagewidth

LSB

MSB

MX = 0

MX = 1

0

83

X address

Fig.6 RAM format, addressing.

0

Y address

5

83

0

MGU275

handbook, full pagewidth

012

84 85 86

168 169 170

252 253 254

336 337 338

420 421 422

083X address

Fig.7 Sequence of writing data bytes into RAM.

2002 Jan 17 14

0

Y address

5503

MGT845

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

MGU276

ROW 0

ROW 1

ROW 2

ROW 3

ROW 4

ROW 5

ROW 6

ROW 7

ROW 8

ROW 9

ROW 10

ROW 11

ROW 12

ROW 13

ROW 14

ROW 15

ROW 16

ROW 17

ROW 18

ROW 19

ROW 20

ROW 21

ROW 22

ROW 23

ROW 24

ROW 25

ROW 26

ROW 27

ROW 28

ROW 29

ROW 30

ROW 31

ROW 32

ROW 33

ROW 34

ROW 35

ROW 36

ROW 37

ROW 38

ROW 39

ROW 40

ROW 41

ROW 42

ROW 43

ROW 44

ROW 45

ROW 46

ROW 47

012345678

Z address when MY = 0

RAM DISPLAY

9

1011121314151617181920212223242526272829303132

Z address = 31

333435363738394041424344454647

Fig.8 Programming the Z address when MY = 0.

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

2002 Jan 17 15

Y address

0

1

2

3

4

5

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

MGU277

ROW 0

ROW 1

ROW 2

ROW 3

ROW 4

ROW 5

ROW 6

ROW 7

ROW 8

ROW 9

ROW 10

ROW 11

ROW 12

ROW 13

ROW 14

ROW 15

ROW 16

ROW 17

ROW 18

ROW 19

ROW 20

ROW 21

ROW 22

ROW 23

ROW 24

ROW 25

ROW 26

ROW 27

ROW 28

ROW 29

ROW 30

ROW 31

ROW 32

ROW 33

ROW 34

ROW 35

ROW 36

ROW 37

ROW 38

ROW 39

ROW 40

ROW 41

ROW 42

ROW 43

ROW 44

ROW 45

ROW 46

ROW 47

012345678

Z address with MY = 1

RAM DISPLAY

9

1011121314151617181920212223242526272829303132

Z address = 31

333435363738394041424344454647

Fig.9 Programming the Z address when MY = 1.

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

2002 Jan 17 16

Y address

0

1

2

3

4

5

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

DDRAM

bank 0

top of LCD

R0

bank 1

R8

bank 2

bank 3

bank 4

bank 5

R16

LCD

R24

R32

R40

Fig.10 DDRAM to display mapping (Z = 0).

2002 Jan 17 17

R47

MGT842

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

11.2 Serial interface

The serial interface is a 3-line bidirectional interface for

communication between the microcontroller and the LCD

driver chip. The 3 lines are: SCE (chip enable), SCLK

(serial clock) and SDA (serial data). The OM6211 is

connected to SDA by two pins: SDIN (data input) and

SDOUT (data output) connected together.

11.2.1 WRITE MODE

The write mode of the interface means that the

microcontrollerwritescommandsand data to the OM6211.

Each data packet contains a control bit D/C and a

transmission byte. If D/C is LOW, the following byte is

interpreted as a command byte (see Table 5). If D/C is

HIGH,the following byte is storedin the displaydata RAM.

After every data byte the address counter is incremented

automatically. Figure 11 shows the general format of the

write mode and the definition of the transmission byte.

Every command can be sent in any order to the OM6211.

The MSB of a byte is transmitted first. The serial interface

is initialized when SCE is HIGH. In this state, SCLK clock

pulses have no effect and no power is consumed by the

serial interface. A falling edge on SCE enables the serial

interface and indicates the start of a data transmission.

Figures 12, 13 and 14 show the protocol of the write

mode:

• When SCE is HIGH, SCLK clocks are ignored: during

the HIGH time of SCE the serial interface is initialized

(see Fig.12)

• At the falling edge of SCE SCLK must be LOW (see

Fig.16); for the transmission of eachdata bit arising and

then a falling edge of SCLK is necessary

• SDIN is sampled at the rising edge of SCLK

• D/C indicates whether the byte is a command (D/C=0)

or RAM data (D/C = 1); it is sampled with the first rising

SCLK edge

• IfSCE stays LOWafter the last bitof a commandordata

byte, the serial interface expects the D/C bit of the next

byte at the next rising edge of SCLK (see Fig.13)

• A reset pulse with RES interrupts the transmission. The

data being written into the RAM may be corrupted. The

registers are cleared. If SCE is LOW after the rising

edge of RES, the serial interface is ready to receive the

D/C bit of a command or data byte (see Fig.14).

handbook, full pagewidth

Transmission Byte (TB) (command byte OR data byte)

D/C DB7 DB6 DB5 DB4 DB3

MSB LSB

D/C

TB

DB2 DB1 DB0

D/C

TB

Fig.11 Serial data stream, write mode.

2002 Jan 17 18

D/C

TB

MGU278

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

handbook, full pagewidth

SCE

SCLK

SDIN

D/C

DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

Fig.12 Write mode: a control bit followed by a transmission byte.

handbook, full pagewidth

SCE

SCLK

SDIN DB7D/C DB6 DB5 DB4 DB3 DB2 DB1 DB0

MGU279

DB7D/C DB6 DB5 DB4 DB3 DB2 DB1 DB0 D/C

MGU280

Fig.13 Write mode: transmission of several bytes.

handbook, full pagewidth

SCE

RES

SCLK

SDIN DB7D/C DB6 DB5 DB4 DB7DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

Fig.14 Write mode: interrupted by reset (RES).

2002 Jan 17 19

DB6D/C D/C

MGU281

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

11.2.2 READ MODE

In the read mode of the interface the microcontroller reads

data from the OM6211. To do so the microcontroller first

has to send the read status command, and then the

following byte is transmitted in the opposite direction

(using SDOUT). After that SCE is required to go HIGH

before a new command is sent (see Fig.15).

The OM6211 samples the SDIN data on the rising edges

of SCLK, but shifts SDOUT data on the falling edges of

SCLK. Thus the microcontroller is supposed to read

SDOUT data on the rising edges of SCLK.

After the read status command has been sent, the SDIN

line must be set to 3-state not later then the falling SCLK

edge of the last bit (see Fig.15).

The 8th read bit is shorter than the others because it is

terminated by the rising edge of SCLK (see Fig.15). The

last rising edge of SCLK sets SDOUT to 3-state after the

delay time t3 (see Section 10.1 and Fig.17).

There are 5 bitsof information only that canbe read by the

microcontroller (see Table 7). Two of them are chip

identification bits and have fixed values. The next two bits

are LCD module identification bits and can be set by

connecting the ID3 and ID4 pins to V

bit is the V

voltage monitor bit VM.

LCD

or VSS. The fifth

DD1

It indicates that the charge pump is running and the

voltage level of V

contrast of the display (VM = 1). If the V

is sufficient to provide enough

LCD

LCD

generator

cannot produce a voltage defined by VOP, then VM = 0.

VM has a valid value 45 ms after a delay time of

approximately 45 ms starting from the time the V

LCD

generatorhas been switched on(by setting HVE = 1). This

delay time is dependent on the external V

decoupling

LCD

capacitor (here 100 nF is assumed).

For more details concerning the VM bit see Chapter 22

The reading out of the chip identification bits and module

identification bits can be used to implement different

initialization schemes for different applications. The

reading out of VM can be used to check the proper

electrical contacts of the LCD module.

One read status command enables one status bit to be

read, i.e. 5 commands are needed to read the status of all

5 bits. The first 4 bits of the read byte (DB7 to DB4) are

always equal to the corresponding status bit and the next

4 bits (DB3 to DB0) areequal to the complement of this bit.

As stated before the SDOUT data is supposed to be read

on the risingedge ofSCLK. Care must be taken, however,

when running the SCLK at maximum frequency. Because

of the access time limit t2(see Section 10.1 and Fig.17) it

might happen that the first bits of each group (DB7 to DB4

and DB3 to DB0) are not valid at the time of the

corresponding SCLK edges. Thus it is recommended to

read the bits DB4 and DB0 only.

handbook, full pagewidth

SCE

SCLK

SDIN

SDOUT

DB7D/C DB6 DB5 DB4

DB3 DB2 DB1 DB0

Fig.15 Read mode.

2002 Jan 17 20

DB7 DB6 DB5 DB4 DB3 DB2 DB1

D/C

DB0

MGU282

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

12 INSTRUCTIONS

12.1 Instruction set

Table 5 Instruction set; see notes 1 and 2 and Table 6

INSTRUCTION D/

C

DESCRIPTION

DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

NOP 0 1 1 1 0 0 0 1 1 no operation

Reset 0 1 1 1 0 0 0 1 0 software reset

COMMAND BYTE

Write data 1 D

7

6

D

5

D

4

D

3

D

2

D0write data to display RAM

1

D

D

Read status 0 1 1 0 1 1 SB2 SB1 SB0 read one of the status bits; Table 7

Display control 0 1 0 1 0 1 1 1 DON display on/off; see Table 6

0 1 0 1 0 0 1 1 E normal, reverse mode; see Table 6

0 1 0 1 0 0 1 0 DAL all pixels on; see Table 6

0 1 1 0 0 MY X X X mirror Y; see Table 6

Address

commands

Display start line 0 0 1 Z

010110Y

00001XX

00000X

Z

5

Z

4

3

3

2

6

X

2

Z

2

Y

1

X

5

X

1

Z

1

Y

set Yaddress; 0 ≤ Y ≤ 5

0

X

set X address; 0 ≤ X ≤ 83

4

X

set X address; 0 ≤ X ≤ 83

0

Z0set start ROW, 0 ≤ Z ≤ 47

Power control 0 0 0 1 0 1 HVE HVE HVE switch HV-gen on/off; see Table6

Frame

calibration

0100V

000100V

PR4VPR3VPR2VPR1VPR0

PR7VPR6VPR5

0 1 0 1 0 1 1 0 OC frame calibration start/stop;

lower part of VPR; see Equation (1)

higher part of V

PR

see Table 6

TC 0 0 0 1 1 1 0 TC1 TC0 set temperature coefficient;

see Table 8

HV-gen stages 0 0 0 1 1 1 1 S

S0set multiplication factor;

1

see Table 3

Bias system 0 0 0 1 1 0 BS2 BS1 BS0 set bias system; see Table 1

Test 0 1 0 1 0 1 0 0 X reserved

0 1 1 1 0 1 0 1 1 reserved

0 1 1 1 0 1 1 0 0 reserved

0 1 1 1 0 1 1 1 1 reserved

Notes

1. X = don’t care.

2. DB7 = MSB.

2002 Jan 17 21

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

Table 6 Explanations for symbols in Table 5

BIT LOGIC 0 LOGIC 1

DON display off display on

DAL normal display (only if DON = 1) all pixels on

E normal display inverse video mode (only if DAL = 0)

HVE V

MY no Y mirroring Y mirroring

OC stop frame frequency calibration start frame frequency calibration

generator (HV generator) is switched off V

LCD

generator is switched on

LCD

Table 7 Read status

SB[2:0]

READ

STATUS BIT

DESCRIPTION

010 ID1 fixed value 0

011 ID2 fixed value 1

100 ID3 defined by input pin ID3

101 ID4 defined by input pin ID4

111 VM VM

Table 8 Temperature coefficients

TC[1:0]

00 TC0

01 TC1

10 TC2

11 TC3

Table 9 V

values in two’s complement notation

OS

DECIMAL BINARY

+0 00000

+1 00001

+2 00010

+3 00011

+4 00100

+5 00101

+6 00110

+7 00111

+8 01000

DECIMAL BINARY

+9 01001

+10 01010

+11 01011

+12 01100

+13 01101

+14 01110

+15 01111

−1 11111

−2 11110

−3 11101

−4 11100

−5 11011

−6 11010

−7 11001

−8 11000

−9 10111

−10 10110

−11 10101

−12 10100

−13 10011

−14 10010

−15 10001

−16 10000

2002 Jan 17 22

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

13 LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 60134); notes 1 and 2.

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

DD

V

LCD

VI, V

O

II, I

O

IDD, ISS, I

P

tot

P

out

T

stg

T

j(max)

LCD

Notes

1. Stresses above those listed under limiting values may cause permanent damage to the device.

2. Parameters are valid over operating temperature range unless otherwise specified. All voltages are referenced to

V

unless otherwise specified.

SS

3. VSS=0V.

supply voltage −0.5 +6.5 V

LCD supply voltage −0.5 +9.0 V

input/output voltage (any input/output) −0.5 V

DD1

+ 0.5 V

DC input or output current −10 +10 mA

VDD, VSS or V

current note 3 −50 +50 mA

LCD

total power dissipation per package − 100 mW

power dissipation per output − 10 mW

storage temperature −65 +150 °C

maximum junction temperature − 150 °C

14 HANDLING

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is

recommended to take normal precautions appropriate to handling MOS devices (see

“Handling MOS Devices”

).

15 DC CHARACTERISTICS

V

= 1.7 to 2.3 V; V

DD1

= 2.5 to 4.5 V; VSS=0V; V

DD2

= 4.5 to 9.0 V; T

LCD

= −40 to +85 °C; unless otherwise

amb

specified.

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Supplies

V

DD1

V

DD2,

V

DD3

V

LCDIN

V

LCDOUT

V

LCD(tol)

I

DD1

logic supply voltage 1.7 1.8 2.3 V

supply voltage for voltage multiplier note 1 2.5 2.78 4.5 V

LCD supply voltage 4.5 − 9.0 V

generated LCD supply voltage note 2 6.8 −− V

tolerance of generated V

V

supply current Power-down mode; note 4 − 210µA

DD1

LCD

with calibration; note 3 −70 − +70 mV

normal mode; note 4 − 12 −µA

I

DD2,IDD3VDD2

and V

supply current Power-down mode; note 4 − 15 µA

DD3

normal mode; note 4 − 78 −µA

I

DD(tot)

total supply current (V

V

)

DD3

DD1

and V

DD2,

normal mode; note 4 − 90 −µA

normal mode; note 5 − 120 −µA

2002 Jan 17 23

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Logic

V

IL

V

IH

I

OL

I

OH

I

L

Column and row outputs

R

o(col)

R

o(row)

V

bias(col)

V

bias(row)

Calibration inputs

R

on(Vos)

R

off(Vos)

Notes

1. V

DD2

2. Conditions are: V

T

amb

3. Valid for values of temperature, V

4. Conditionsare:V

or VSS, serial interface inactive, internal V

5. Conditionsare:V

or VSS, serial interface inactive, internal V

6. Load current 10 µA, outputs tested one at a time.

LOW-level input voltage V

SS

HIGH-level input voltage 0.7V

LOW-level output current (SDOUT) VOL= 0.4 V; V

HIGH-level output current (SDOUT) VOH= 1.4 V; V

leakage current VI=V

column output resistance (COL 0 to

note 6 − 420kΩ

DD1

or V

= 1.8 V 0.5 −− mA

DD1

= 1.8 V −−−0.5 mA

DD1

SS

−1 − +1 µA

− 0.3V

− V

DD1

DD1

COL 83)

row output resistance (ROW 0 to

note 6 − 420kΩ

ROW 47)

bias tolerance (COL 0 to COL 83) −100 0 +100 mV

bias tolerance (ROW 0 to ROW 47) −100 0 +100 mV

external resistance between a VOS pin

and the V

pin for logic 0

SS1

external resistance between a VOS pin

and the V

is always equal V

pin for logic 1

SS1

.

DD3

= 2.5 V, voltage multiplier = 3V

DD2

, bias system1⁄6, V

DD2

−−10 kΩ

5 −− MΩ

output is loaded by 10 µA,

LCD

=25°C.

and TC used at the calibration.

PR

= 1.8 V,V

DD1

= 1.8 V,V

DD1

= 2.78 V,V

DD2

= 2.78 V,V

DD2

= 6.8 V,voltage multiplier = 3V

LCD

generation, V

LCD

= 8.3 V,voltage multiplier = 4V

LCD

generation, V

LCD

DD2

output is loaded by 10 µA; T

LCD

DD2

output is loaded by 10 µA; T

LCD

,bias system1⁄6,inputs at V

=25°C.

amb

,bias system1⁄7,inputs at V

=25°C.

amb

DD1

V

V

DD1

DD1

2002 Jan 17 24

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

16 AC CHARACTERISTICS

V

= 1.7 to 2.3 V; V

DD1

specified.

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

f

osc(int)

f

frame

t

VHRL

t

RW

t

R(op)

internal oscillator frequency note 1 − 251 − kHz

frame frequency uncalibrated; note 2 46 80 142 Hz

V

DD1

reset LOW pulse width see Fig.18 1000 −−ns

end of reset pulse to interface

being operational

Serial interface timing

f

SCLK

t

cyc

t

PWH1

t

PWL1

t

S2

t

H2

t

PWH2

t

H5

t

S1

t

H1

t

2

t

3

t

4

t

5

clock frequency 0 − 4.00 MHz

clock cycle SCLK 250 −−ns

SCLK pulse width HIGH 120 −−ns

SCLK pulse width LOW 100 −−ns

SCE set-up time 60 −−ns

SCE hold time 100 −−ns

SCE minimum HIGH time 100 −−ns

SCE start hold time note 7 100 −−ns

SDIN set-up time 100 −−ns

SDIN hold time 100 −−ns

SDOUT access time note 8 0 − 450 ns

SDOUT disable time 25 − 450 ns

SCE hold time 100 −−ns

SCE hold time 20 −−ns

= 2.5 to 4.5 V; VSS=0V; V

DD2

= 4.5 to 9.0 V; T

LCD

= −40 to +85 °C; unless otherwise

amb

calibrated; notes 3 and 4 63 80 97 Hz

calibrated; notes 3 and 5 75 80 85 Hz

to RES LOW see Fig.18; note 6 0 − 30 ms

−−1000 ns

Notes

f

1.

f

frame

2. Temperature range T

3. CalibratedatV

=

osc

------------3136

amb

= 1.8 Vand T

DD1

= −30 to +70 °C.

=25°C,valid for bothOTPcalibration and softwarecalibration, exact calibration

amb

time assumed.

4. Measured at V

5. Measured at V

6. It is recommended that RES is LOW before V

= 1.8 V, temperature range T

DD1

DD1

= 1.8 V, T

amb

=25°C.

= −30 to +70 °C.

amb

goes HIGH

DD1

7. tH5is the time from the previous SCLK rising edge (irrespective of the state of SCE) to the falling edge of SCE (see

Fig.16).

8. Capacitive load at pin SDOUT less than 50 pF.

2002 Jan 17 25

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

16.1 Serial interface timing

handbook, full pagewidth

SCE

SCLK

SDIN

t

5

t

PWL1

t

S2

t

PWH1

t

t

S1

H1

Fig.16 Serial interface timing: write mode.

t

H2

(tH5)

t

t

cyc

S2

t

PWH2

t

H5

MGU283

handbook, full pagewidth

SCE

SCLK

SDIN

SDOUT

t

H1

t

2

t

2

Fig.17 Serial interface timing: read mode.

2002 Jan 17 26

t

4

t

S1

t

t

2

3

MGU284

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

16.2 Reset timing

handbook, full pagewidth

V

RES

SCE

DD1

t

VHRL

t

RW

t

R(oper)

MGU285

Fig.18 Reset timing.

17 APPLICATION INFORMATION

The pinning of the OM6211 is optimized for single plane wiring e.g. for chip-on-glass display modules. Display size:

48 × 84 pixels.

handbook, full pagewidth

DISPLAY 48 × 84 PIXELS

OM6211

4

V

I/O

V

DD1

DD2

Fig.19 Application diagram.

The required minimum value for the two external capacitors (C

Higher capacitor values are recommended for ripple reduction.

2002 Jan 17 27

8424 24

C

ext

V

SS

) in an application with the OM6211 is 100 nF (min.).

ext

V

LCD

MGU286

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

18 MODULE MAKER PROGRAMMING

TheOne Time Programmable (OTP)technology has been

implemented on the OM6211. It enables the module

maker to programsome extended featuresof the OM6211

after it has been assembled on an LCD module.

Programming is made under the control of the serial

interface and the use of one special pin. This pin must be

made available on the module glass but needs not to be

accessed by the set maker.

As the module maker programming is an extension of the

normal functions ofthe OM6211it will not be effective until

specifically instructed with the ‘Enable OTP’ command.

The OM6211 features 3 module maker programmable

parameters:

• V

calibration

LCD

• VPR default value

• Seal bit.

18.1 V

The first feature included is the ability to tune the V

calibration

LCD

LCD

voltage with a 5-bit code. This code is implemented in

two’s complement notation giving rise to a positive or

negative offset to the VPR register.

Thisis in thesame manner asthe on-glass calibration pins

(laser trim pins). In theory, both maybe usedtogether

V

OS

but it is recommended that the laser trim pins are tied to

VSSwhen OTP calibrationis being used. This willset them

toa default offsetof zero. If bothare used thentheaddition

of the two 5-bit numbers must not exceed a 5-bit result

otherwise the resultant value will be undefined. The final

adder in the circuit has underflow and overflow protection.

In the event of an overflow, the output will be clamped

to 255;and during anunderflow the outputwill be clamped

to 0.

The final control to the high voltage generator, VOP, will be

the sum of all the calibration registers and pins. The V

OP

equation (1) given in Section 9.12 must be extended to

include the OTP calibration.

OP

V

PRVOS

V

The additional offset applied to V

MMVOPCAL++=

can be calculated

LCD

(5)

from equation (2) and (5), where b is the step size as

defined in Table 4.

OFFSET V

V

LCD

The possible MMVOPCAL

MMVOPCAL+()b×=

OS

to MMVOPCAL0 values are

4

(6)

the same as the VOS[4:0] values, see Table 9.

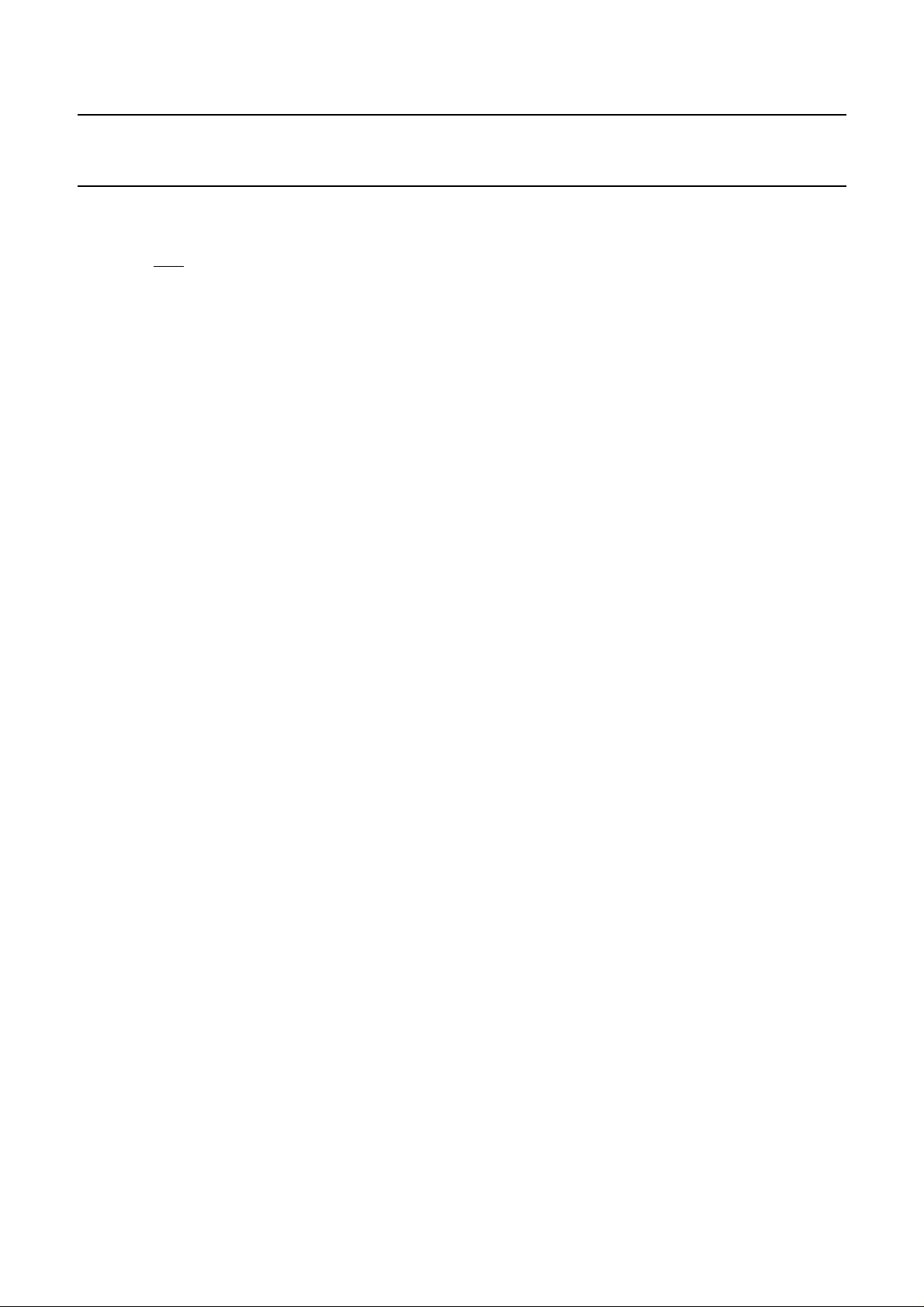

handbook, full pagewidth

OTP V

MMVOPCAL[4:0

V

OS

V

PR

calibration: 5-bit offset

LCD

]

laser trim pins: 5-bit offset

[

]

4:0

VPR register: 8-bit value

[

]

7:0

range −16 to +15

range −16 to +15

range 0 to +255

usable range +32 to +255

Fig.20 V

LCD

2002 Jan 17 28

+

calibration.

VOP[7:0]

+

range: 0 to +255

to high voltage

generator

MGU287

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

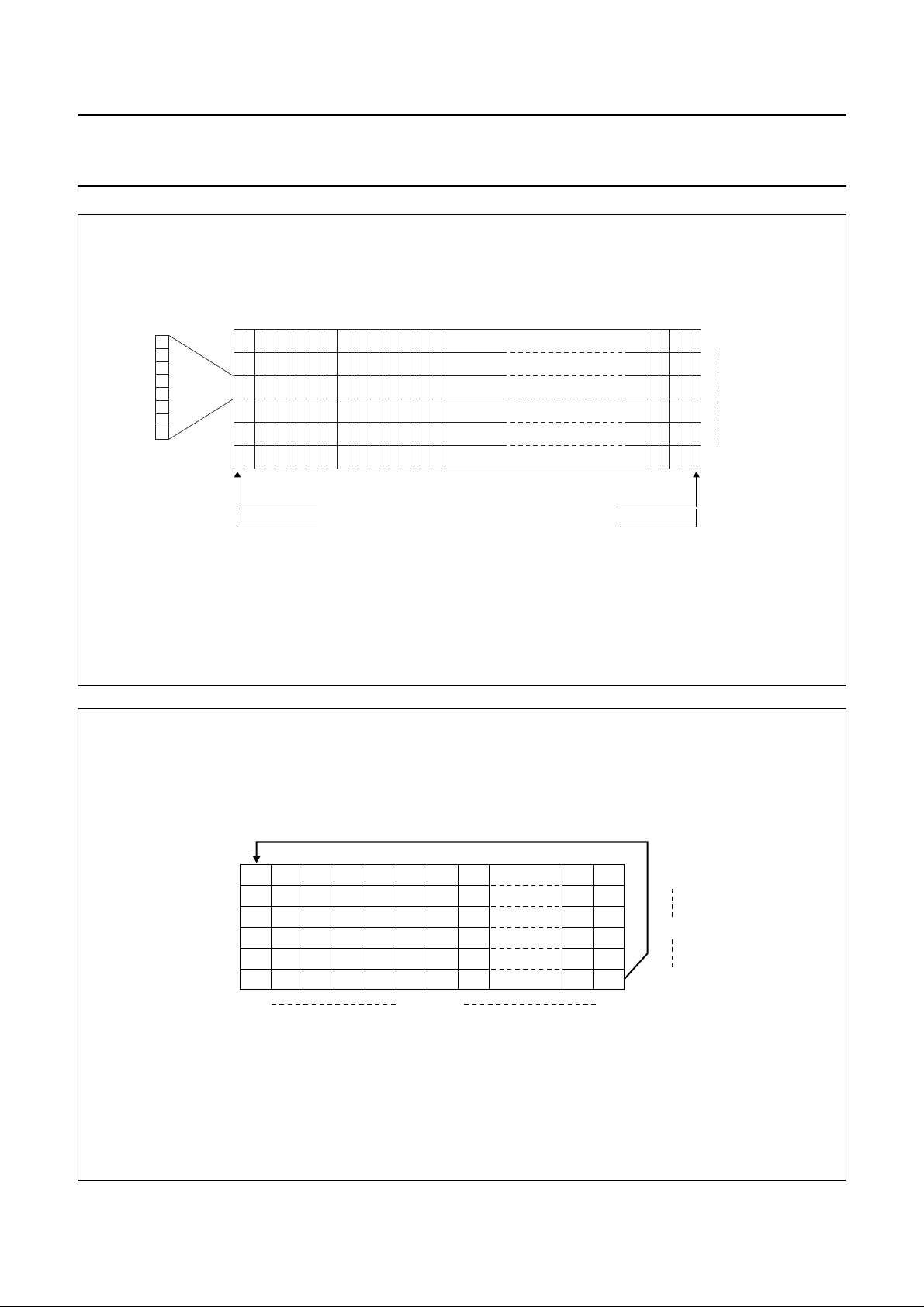

18.2 VPR default value

The second feature is an OTP factory default setting for V

. This is an 8-bit value from which the VPR register can be

PR

loaded using the ‘Load factory default’ command. The idea of this feature is to make it unnecessary for the set maker to

specify the VPRvalue. The factory default may be overridden by the set maker in the normal fashion using the ‘Set VPR’

commands.

handbook, full pagewidth

OTP VPR default register, 8-bit value

interface data

load VPR via the interface

VPR register: 8-bit value

load VPR from an OTP

default register.

+

MGU288

Fig.21 Load VPR register: default or specified via interface.

18.3 Seal bit

The module maker programming is performed in a special

mode: the calibration mode (CALMM). This mode is

entered via a special interface command, CALMM.

To prevent wrongful programming, a seal bit has been

implemented which prevents the device from entering the

calibration mode. This seal bit, once programmed, cannot

be reversed, thus further changes in programmed values

Each OTP slice consists of 2 main parts: the OTP cell

(a non-volatile memory cell) and the shift register cell

(a flip-flop). The OTP cells are only accessible through

their shift registercells: onthe one hand both reading from

and writing to the OTP cells is performed with the shift

register cells, on the other hand only the shift register cells

are visible to the rest of the circuit. The basic OTP

architecture is shown in Fig.22.

are not possible. However, it is possible to disable all

programmed values by not applying the ‘Enable OTP’

command.

Applying the programming voltages when not in CALMM

mode will have no effect on the programmed values.

This OTP architecture enables the following operations:

1. Reading data from the OTP cells. The content of the

non-volatile OTP cells is transferred to the shift

register where it may affect the OM6211 operation

(provided it has been enabled by the ‘Enable OTP’

Table 10 Seal bit definition

SEAL BIT ACTION

0 possible to enter calibration mode

1 calibration mode disabled

command).

2. Writingdata tothe OTPcells. Firstly, all 14 bits of data

areshifted into theshiftregister via theserialinterface.

The content of the shift register is then transferred to

the OTP cells (there are some limitations related to

storing data in these cells, see Section 18.7).

18.4 OTP architecture

The OTP circuitry in the OM6211 contains 14 bits of data:

5 for V

calibration, 8 for VPRdefault and 1 seal bit. The

LCD

3. Checking calibration without writing to the OTP cells.

Shiftingdata into theshift register allowsthe effects on

the V

voltage to be observed.

LCD

circuitry for 1-bit is called an OTP slice, thus there are

14 OTP slices.

2002 Jan 17 29

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

All OTP circuitry of the OM6211 is disabled until the

‘Enable OTP’ command is given. Once enabled, the

reading of data from the OTP cells is initiated by either:

• Exit from Power-down mode

• The ‘Refresh’ command.

It should be noted that in both cases the reading operation

needs up to 5 ms to complete.

The shifting of data into the shift register is performed in a

special mode called CALMM. In the OM6211 the CALMM

mode is entered through the CALMM command. Once in

the CALMM mode the data is shifted into the shift register

via the serial interface at the rate of 1-bit per command.

Aftertransmitting the last(14th) bit and exitingthe CALMM

mode the serial interface returns to the normal mode and

allothercommands can be sent.Careshouldbetaken that

all 14 bits of data (or a multiple of 14) are transferred

before exiting the CALMM mode, otherwise the bits will be

in the wrong positions.

In the shift register the value of the seal bit is, like the

others, always zero at reset. To ensure that the security

feature works correctly, the CALMM command is disabled

until a refresh has been performed. Once the refresh is

completed, the seal bit value in the shift register is valid

and permission to enter CALMM mode can thus be

determined.

The14 bits are shiftedintothe shift register ina predefined

order: firstly the 8 bits of MMOTPVOP7 to MMOTPVOP0,

thenthe 5 bits ofMMVOPCAL4toMMVOPCAL0andlastly

the seal bit. The MSB is always first, thus the first bit

shifted is MMOTPVOP7 and the two last bits are

MMVOPCAL0 and the seal bit.

handbook, full pagewidth

read data

from the

OTP cell

OTP slice

SHIFT

REGISTER

FLIP-FLOP

OTP CELL

write data

to the

OTP cell

SHIFT

REGISTER

DATA

INPUT

DATA TO THE CIRCUIT FOR

CONFIGURATION AND CALIBRATION

SHIFT

REGISTER

OTP CELLs

MGU289

Fig.22 Basic OTP architecture.

2002 Jan 17 30

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

18.5 Serial interface commands

These instructions are in addition to those indicated in Table 5.

Table 11 Additional instructions

INSTRUCTION D/C

Enable OTP 011101011enable OTP circuitry

CALMM 011101111enter CALMM mode

Load factory

default

Power control

(refresh)

18.5.1 ENABLE OTP

This is aspecial instructionfor the OM6211 which enables

all included OTP circuitry. Once enabled the mode can

only be disabled via a reset.

18.5.2 CALMM

This instruction puts the device into the calibration mode.

This mode enablesthe shiftregister for loading and allows

programming of the non-volatile OTP cells to take place. If

the seal bit is set then this mode cannot be accessed and

the instruction willbe ignored.Once in calibration mode all

commandsareinterpreted as shift register data.Themode

can only be exited by sending data with bit DB7 set to

logic 0.A reset willalso clear thismode. Each shift register

databyteis preceded by D/C = 0 andhasonly2 significant

bits, thus the remaining 6 bits are ignored. Bit DB7 is the

continuation bit (DB7 = 1 remain in CALMM mode,

DB7 = 0 exit CALMMmode). Bit DB0is the data bit andits

value is shifted into the OTP shift register (on the falling

edge of SCLK).

18.5.3 LOAD FACTORY DEFAULT

The‘Load factory default’instruction is used totransfer the

contents of the OTP shift register bits MMOTPVOP7 to

MMOTPVOP0 into the normal working register of VPR;

see Fig.21. This is opposite to the calibration register

MMVOPCAL4 to MMVOPCAL0 which is active

immediately after a refresh.

DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

011101100load MMOTPVOP

000101HVEHVEHVEset HVE; force a refresh of the

COMMAND BYTE

ACTION

MMOTPVOP0 into VPR register

shift register

During this time all other instructions may be sent,

however, instructions requiring the output of the shift

register (‘Load factory default’) should be avoided as the

register contents may not be valid.

In the OM6211 the ‘Refresh’ instruction is associated to

the ‘Set HVE’ instruction so that the shift register is

automatically refreshed every time the high voltage

generator is enabled or disabled. It should be noted

however,thatif this instruction issentwhile in Power-down

mode, then the HVE bit is updated but the refreshing is

ignored.

18.6 Example of filling the shift register

An example sequence of commands and data is shown in

Table 12. In this example the shift register is filled with the

following data: MMVOPCAL = −4 (11100B),

MMOTPVOP = 19 (00010011B) and the seal bit is 0.

It is assumed that the OM6211 has just been reset. After

transmitting the last bit the OM6211 can exit or remain in

CALMM mode (see step 18). It should be noted that while

in CALMM mode the interface does not recognize

commands in the normal sense.

After this sequence has been applied it is possible to

observethe impact ofthedata shifted in. Thissequence is,

however, not useful for OTP programming because the

number of bits with the value ‘1’ is greater than that

allowed for programming (see Section 18.7). Figure 23

shows the shift register after this action.

to

7

18.5.4 REFRESH

The action of the ‘Refresh’ instruction is to force the OTP

shift register to re-load from the non-volatile OTP cells.

This instruction takes up to 5 ms to complete.

2002 Jan 17 31

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

Table 12 Example sequence for filling the shift register; note 1

STEP D/

C

ACTION

DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

1 0 1 1 1 0 1 0 1 1 send enable OTP command

2 0 1 0 1 0 1 1 1 1 exit Power-down (e.g. DON = 1)

3 wait 5 ms for refresh to take effect.

4 0 1 1 1 0 1 1 1 1 enter CALMM mode

COMMAND BYTE

5 0 1 X X X X X X 0 shift in data; MMOTPVOP

6 0 1 X X X X X X 0 MMOTPVOP

7 0 1 X X X X X X 0 MMOTPVOP

8 0 1 X X X X X X 1 MMOTPVOP

9 0 1 X X X X X X 0 MMOTPVOP

10 0 1 X X X X X X 0 MMOTPVOP

11 0 1 X X X X X X 1 MMOTPVOP

12 0 1 X X X X X X 1 MMOTPVOP

13 0 1 X X X X X X 1 MMVOPCAL

14 0 1 X X X X X X 1 MMVOPCAL

15 0 1 X X X X X X 1 MMVOPCAL

16 0 1 X X X X X X 0 MMVOPCAL

17 0 1 X X X X X X 0 MMVOPCAL

6

5

4

3

2

1

0

4

3

2

1

0

is first bit; note 2

7

18 0 0 X X X X X X 0 seal bit; exit CALMM mode

An alternative ending could be to stay in CALMM mode

18 0 1 X X X X X X 0 seal bit; remain in CALMM mode

Notes

1. X = don’t care.

2. The data for the bits is not in the correct shift register position until all bits have been sent.

handbook, full pagewidth

shifting

direction

SEAL

BIT = 0

LSB

MMVOPCAL[4:0]

0

0 1 1 1

OTP SHIFT REGISTER

LSB

MSB

1

1 0 0 0 0 01

MMOTPVOP[7:0]

Fig.23 Shift register contents after example sequence of Table 12.

2002 Jan 17 32

MSB

MGU290

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

18.7 Programming flow

Programming is achievedwhilst in CALMMmode andwith

the application of the programming voltages. As

mentioned previously, the data for programming the OTP

cell is contained in the corresponding shift register cell.

Theshift register cellmust be loadedwith a logic 1in order

to program the corresponding OTP cell. If the shift register

cell contains a logic 0, then no action will take place when

the programming voltages are applied.

Once programmed, an OTP cell can not be

un-programmed. An already programmed cell, that is an

OTP cell containing a logic 1, must not be re-programmed.

Once this bit has been programmed it will not be possible

to re-enter the CALMM mode.

During programming a substantial current flows in the

V

pin. For this reason it is recommended to program

LCDIN

only one OTP cell at a time. This is achieved by filling all

but one shift register cells with logic 0. It should be noted

thattheprogramming specification refers to thevoltagesat

the chip pins, contact resistance must therefore be

considered by the user.

An example sequence of commands and data for OTP

programming is shown in Table 13.

It is assumed that the OM6211 has just been reset.

The order for programming cells is not significant.

However, it is recommended that the seal bit is

programmed last.

Table 13 Example sequence for OTP programming; note 1

COMMAND BYTE

STEP D/

C

ACTION

DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

1 0 1 1 1 0 1 0 1 1 send Enable OTP command

2 0 1 0 1 0 1 1 1 1 exit Power-down (e.g. DON = 1)

3 wait 5 ms for refresh to take effect

4 0 1 0 1 0 1 1 1 0 re-enter Power-down (DON = 0)

5 0 1 1 1 0 1 1 1 1 enter CALMM mode

6 0 1 X X X X X X 0 shift in data. MMOTPVOP

7 0 1 X X X X X X 0 MMOTPVOP

8 0 1 X X X X X X 0 MMOTPVOP

6

5

7

9 0 1 X X X X X X 1 MMOTPVOP4 (the only bit with the value 1)

10 0 1 X X X X X X 0 MMOTPVOP

11 0 1 X X X X X X 0 MMOTPVOP

12 0 1 X X X X X X 0 MMOTPVOP

13 0 1 X X X X X X 0 MMOTPVOP

14 0 1 X X X X X X 0 MMVOPCAL

15 0 1 X X X X X X 0 MMVOPCAL

16 0 1 X X X X X X 0 MMVOPCAL

17 0 1 X X X X X X 0 MMVOPCAL

18 0 1 X X X X X X 0 MMVOPCAL

3

2

1

0

4

3

2

1

0

19 0 1 X X X X X X 0 seal bit; remain in CALMM mode

20 apply programming voltage at pins T6 and

V

according to Section 18.8

LCDIN

Repeat steps 6 to 20 for each bit that should be programmed to 1

21 apply external reset

Note

1. X = don’t care.

2002 Jan 17 33

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

18.8 Programming specification

Table 14 Programming specification; see Fig.24

SYMBOL PARAMETER CONDITION MIN. TYP. MAX. UNIT

V

T6

V

LCDIN

I

LCDIN

I

T6

T

amb(prog)

t

su;SCLK

t

h;SCLK

t

su;T6

t

h;T6

t

W

voltage applied to T6 pin relative to V

voltage applied to V

V

SS1

current drawn by V

pin relative to

LCDIN

during

LCDIN

programming

current drawn by VT6 during

programming

ambient temperature during

programming

set-up of internal data after last clock 1 −−µs

hold of internal data before next clock 1 −−µs

set-up of VT6 prior to programming 1 − 10 ms

hold of VT6 after programming 1 − 10 ms

pulse width of programming voltage 100 120 200 ms

programming active;

SS1

notes 1 and 2

programming inactive;

notes 1 and 2

programming active;

notes 1 and 3

programming inactive;

notes 1 and 3

when programming a

single bit to logic 1

11 11.5 12 V

V

− 0.2 0 0.2 V

SS

9 9.5 10 V

−0.2 0 +4.5 V

− 850 1000 µA

− 100 200 µA

02540°C

Notes

1. Thevoltage drop acrossthe ITOtrack and zebraconnector must betaken into account to guaranteesufficient voltage

at the chip pins.

2. The maximum voltage must not be exceeded even for a short period of time. Therefore care must be taken when

applying programming waveforms to avoid overshoot.

3. The Power-down mode (DON = 0 and DAL = 1) and CALMM mode must be active while the V

LCDIN

pin is being

driven.

t

h;T6

t

h;SCLK

MGU291

handbook, full pagewidth

V

LCDIN

SCLK

V

T6

t

sw;SCLK

t

sw;T6

t

w

Fig.24 Programming waveforms.

2002 Jan 17 34

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

19 BONDING PAD LOCATIONS

Table 15 Bonding pad information

PAD ROWS AND COLS SIDE INTERFACE SIDE UNIT

Pad pitch minimum 60 minimum 70 µm

Pad size (aluminium) 50 × 90 60 × 100 µm

CBB opening 26 × 66 36 × 76 µm

Bump dimensions 40 × 80 × 17.5 (±5) 50 × 90 × 17.5 (±5) µm

Wafer thickness (excluding bumps) 381 (±25) µm

handbook, halfpage

1.91

mm

9.46 mm

OM6211

pitch

y

x

Fig.25 Chip size and pad pitch.

MGU292

handbook, halfpage

y center

100

µm

x center

MGT855

Fig.26 Shape of alignment mark.

2002 Jan 17 35

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

Table 16 Bonding pad location

All x and y co-ordinates are referenced to the centre of

the chip (dimensions in µm; see Fig.27).

COORDINATES

SYMBOL PAD

xy

Dummy 1 −835 +4630

Alignment mark 2 −825 +4527.5

V

V

V

V

V

OS4

OS3

OS2

OS1

OS0

3 −835 +4425

4 −835 +4215

5 −835 +4005

6 −835 +3795

7 −835 +3585

T6 8 −835 +3375

T6 9 −835 +3305

T6 10 −835 +3235

T6 11 −835 +3165

Dummy 12 −835 +3095

Dummy 13 −835 +3025

Dummy 14 −835 +2955

Dummy 15 −835 +2885

RES 16 −835 +2395

T5 17 −835 +2185

T4 18 −835 +1975

T3 19 −835 +1765

T2 20 −835 +1555

T1 21 −835 +1345

SCE 22 −835 +1135

V

SS2

V

SS2

V

SS2

V

SS2

V

SS2

V

SS2

V

SS2

V

SS2

V

SS1

V

SS1

V

SS1

V

SS1

V

SS1

V

SS1

V

SS1

23 −835 +1065

24 −835 +995

25 −835 +925

26 −835 +855

27 −835 +785

28 −835 +715

29 −835 +645

30 −835 +575

31 −835 +505

32 −835 +435

33 −835 +365

34 −835 +295

35 −835 +225

36 −835 +155

37 −835 +85

SYMBOL PAD

COORDINATES

xy

V

SS1

38 −835 +15

Dummy 39 −835 −405

OSC 40 −835 −825

SDOUT 41 −835 −1035

SDIN 42 −835 −1245

SCLK 43 −835 −1455

ID4 44 −835 −1665

ID3 45 −835 −1875

MX 46 −835 −2085

V

DD1

V

DD1

V

DD1

V

DD1

V

DD1

V

DD1

V

DD2

V

DD2

V

DD2

V

DD2

V

DD2

V

DD2

V

DD2

V

DD2

V

DD3

V

DD3

V

DD3

V

DD3

V

LCDSENSE

V

LCDOUT

V

LCDOUT

V

LCDOUT

V

LCDOUT

V

LCDOUT

V

LCDOUT

V

LCDOUT

V

LCDIN

V

LCDIN

V

LCDIN

V

LCDIN

47 −835 −2155

48 −835 −2225

49 −835 −2295

50 −835 −2365

51 −835 −2435

52 −835 −2505

53 −835 −2575

54 −835 −2645

55 −835 −2715

56 −835 −2785

57 −835 −2855

58 −835 −2925

59 −835 −2995

60 −835 −3065

61 −835 −3135

62 −835 −3205

63 −835 −3275

64 −835 −3345

65 −835 −3415

66 −835 −3485

67 −835 −3555

68 −835 −3625

69 −835 −3695

70 −835 −3765

71 −835 −3835

72 −835 −3905

73 −835 −3975

74 −835 −4045

75 −835 −4115

76 −835 −4185

2002 Jan 17 36

Philips Semiconductors Product specification

48 × 84 dot matrix LCD driver OM6211

SYMBOL PAD

V

LCDIN

V

LCDIN

Dummy 79 −835 −4395

Alignment mark 80 −825 −4500

Dummy 81 −835 −4605

Dummy 82 +840 −4590

Dummy 83 +840 −4530

Dummy 84 +840 −4470

Dummy 85 +840 −4410

Dummy 86 +840 −4350

Dummy 87 +840 −4290

Dummy 88 +840 −4230

ROW 0 89 +840 −4050

ROW 1 90 +840 −3990

ROW 2 91 +840 −3930

ROW 3 92 +840 −3870

ROW 4 93 +840 −3810

ROW 5 94 +840 −3750

ROW 6 95 +840 −3690

ROW 7 96 +840 −3630

ROW 8 97 +840 −3570

ROW 9 98 +840 −3510

ROW 10 99 +840 −3450