查询OM6208供应商

INTEGRATED CIRCUITS

DATA SH EET

OM6208

65 x 96 pixels matrix grey-scale

LCD driver

Product specification

Supersedes data of 2003 Jan 30

2003 feb 10

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

CONTENTS

1 FEATURES

2 APPLICATIONS

3 GENERAL DESCRIPTION

4 ORDERING INFORMATION

5 BLOCK DIAGRAM

6 PINNING

7 FUNCTIONAL DESCRIPTION

7.1 I/O buffers and interfaces

7.2 Oscillator

7.3 Address counter

7.4 Display data RAM

7.5 Display address counter

7.6 Timing generator

7.7 Data processing

7.8 High voltage generator

7.9 Bias voltage generator

7.10 Command decoder

7.11 Orthogonal function generator

7.12 Reset

7.13 Row drivers and column drivers

8 RAM ADDRESSING

8.1 Display data RAM structure

8.1.1 Horizontal/vertical addressing

8.1.2 Mirror Y

8.1.3 Mirror X

9 SERIAL INTERFACING

9.1 Serial peripheral interface

9.1.1 Write mode

9.1.2 Read mode

9.2 Serial interface (3-line)

9.2.1 Write mode

9.2.2 Read mode

9.2.3 Read data format

10 I2C-BUS INTERFACE

10.1 Characteristics of the I2C-bus (Hs-mode)

10.1.1 System configuration

10.1.2 Bit transfer

10.1.3 Start and stop conditions

10.1.4 Acknowledge

10.2 I2C-bus Hs-mode protocol

10.3 Command decoder

10.4 Read mode

11 INSTRUCTIONS

11.1 Description of command bits

11.2 Frame frequency setting and oscillator tuning

11.3 Initialization

11.4 Reset function

11.5 Power-down mode

11.6 Display Control

11.6.1 Horizontal mirroring

11.6.2 Vertical mirroring

11.7 Set Y address of RAM

11.8 Set X address of RAM

11.9 Bias levels

11.10 LCD drive voltage

11.10.1 LCD drive voltage generation

11.10.2 Temperature measurement

11.10.3 Temperature compensation

11.11 Grey-scale mode and black-and-white mode

11.12 N-line inversion and frame inversion

12 LIMITING VALUES

13 HANDLING

14 DC CHARACTERISTICS

15 AC CHARACTERISTICS

16 APPLICATION INFORMATION

16.1 Protection from light

16.2 Chip-on-glass displays

16.3 Application examples

17 MODULE MAKER PROGRAMMING

17.1 V

17.2 Factory defaults

17.2.1 Configuration derived from OTP cells

17.2.2 Defaults from interface registers

17.3 Seal bit

17.4 OTP architecture

17.4.1 OTP operational effects

17.5 Interface commands

17.5.1 CALMM instruction

17.5.2 Refresh instruction

17.6 Example of filling the shift register

17.7 Programming flow

17.8 Programming specification

18 DEVICE PROTECTION DIAGRAM

19 BONDING PAD INFORMATION

20 TRAY INFORMATION

21 DATA SHEET STATUS

22 DEFINITIONS

23 DISCLAIMERS

24 PURCHASE OF PHILIPS I2C COMPONENTS

calibration

LCD

2003 feb 10 2

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

1 FEATURES

• Single chip LCD Multiple Row Addressing (MRA)

grey-scale/colour controller/driver

• Four grey levels/colours

• 65 row outputs and 96 column outputs

• Display Data RAM (DDRAM) 65 × 96 × 2 bits

• Selectable interface:

– 6.5 MHz 3-line or 4-line Serial Peripheral

Interface (SPI)

– 6.5 MHz 3-line serial interface

– High speed I2C-bus interface.

• On-chip:

– Configurable voltage multiplier generating V

external V

– Four-segment V

also possible

LCD

LCD

temperature compensation

LCD

;

– Generation of intermediate LCD bias voltage

– Oscillator requires noexternal components; external

clock input also possible

– Integrated charge pump capacitors (reducing total

system cost).

• External reset input

• Temperature read-back

• Selectable N-line inversion and frame inversion

• CMOS compatible inputs

• Logic supply voltage range 1.7 to 3.3 V

• High-voltage generator supply voltage range

2.4 to 4.5 V

• Display supply voltage range 5 to 9 V

• Low power consumption; suitable for battery operated

systems

• Programmable row pad mirroring for compatibility with

Tape Carrier Packages (TCP) and with Chip-On

Glass (COG) applications

• Status read which allows chip recognition

• Start address line; for example, for scrolling the

displayed image

• Slim chip layout; suitable for COG, COF and TCP

applications

• Operating temperature range −40 to +85 °C.

2 APPLICATIONS

• Telecom equipment

• Portable instruments

• Point of sale terminals.

3 GENERAL DESCRIPTION

The OM6208 is a low power CMOS LCD controller driver,

designed to drive a graphic display of 65 rows and

96 columns. All necessary functions for the display are

provided in a single chip, including on-chip generation of

LCD supply and bias voltages, resulting in a minimum of

external components and low power consumption. The

OM6208 can be interfaced to microcontrollers via a serial

bus and I2C-bus.

The OM6208 is manufactured in n-well CMOS technology.

Operation is with the substrate at VSS potential.

4 ORDERING INFORMATION

PACKAGE

TYPE NUMBER

NAME DESCRIPTION VERSION

OM6208MU/2DA/1 − chip with bumps in tray −

2003 feb 10 3

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

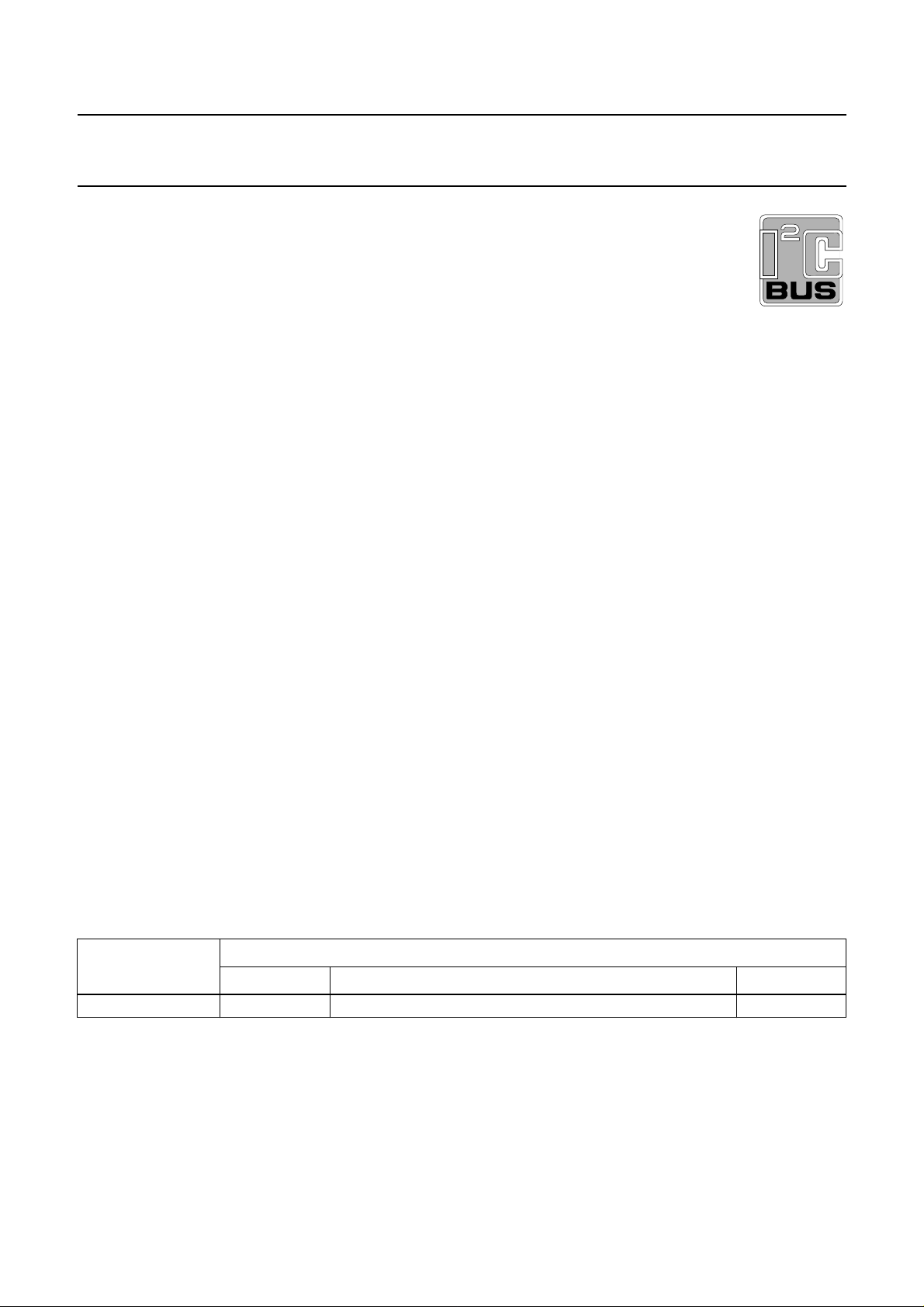

5 BLOCK DIAGRAM

handbook, full pagewidth

V

LCDIN

V

OTPPROG

V

LCDSENSE

V

LCDOUT

V

V

V

V

V

DD1

DD2

DD3

SS1

SS2

T1

T2

T3

T4

T5

T6

T7

T8

BIAS

VOLTAGE

GENERATOR

HIGH

VOLTAGE

GENERATOR

C0 to C95

COLUMN DRIVERS

DATA PROCESSING

DISPLAY DATA RAM

(DDRAM)

[65 × 96] × 2

ADDRESS COUNTER

COMMAND

DECODER

I/O BUFFERS and INTERFACES

OM6208

R0 to R64

ROW DRIVERS

ORTHOGONAL

FUNCTION

GENERATOR

RESET

OSCILLATOR

TIMING

GENERATOR

DISPLAY

ADDRESS

COUNTER

RES

OSC

V

2H

V

1H

V

C

V

1L

V

2L

ID3/SA0; ID4/SA1

]

1:0

[

PS

D/C

MX

Fig.1 Block diagram.

2003 feb 10 4

SCLH/SCE

SCLK

SDATA

SDO

MGW821

SDAH

SDAHOUT

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

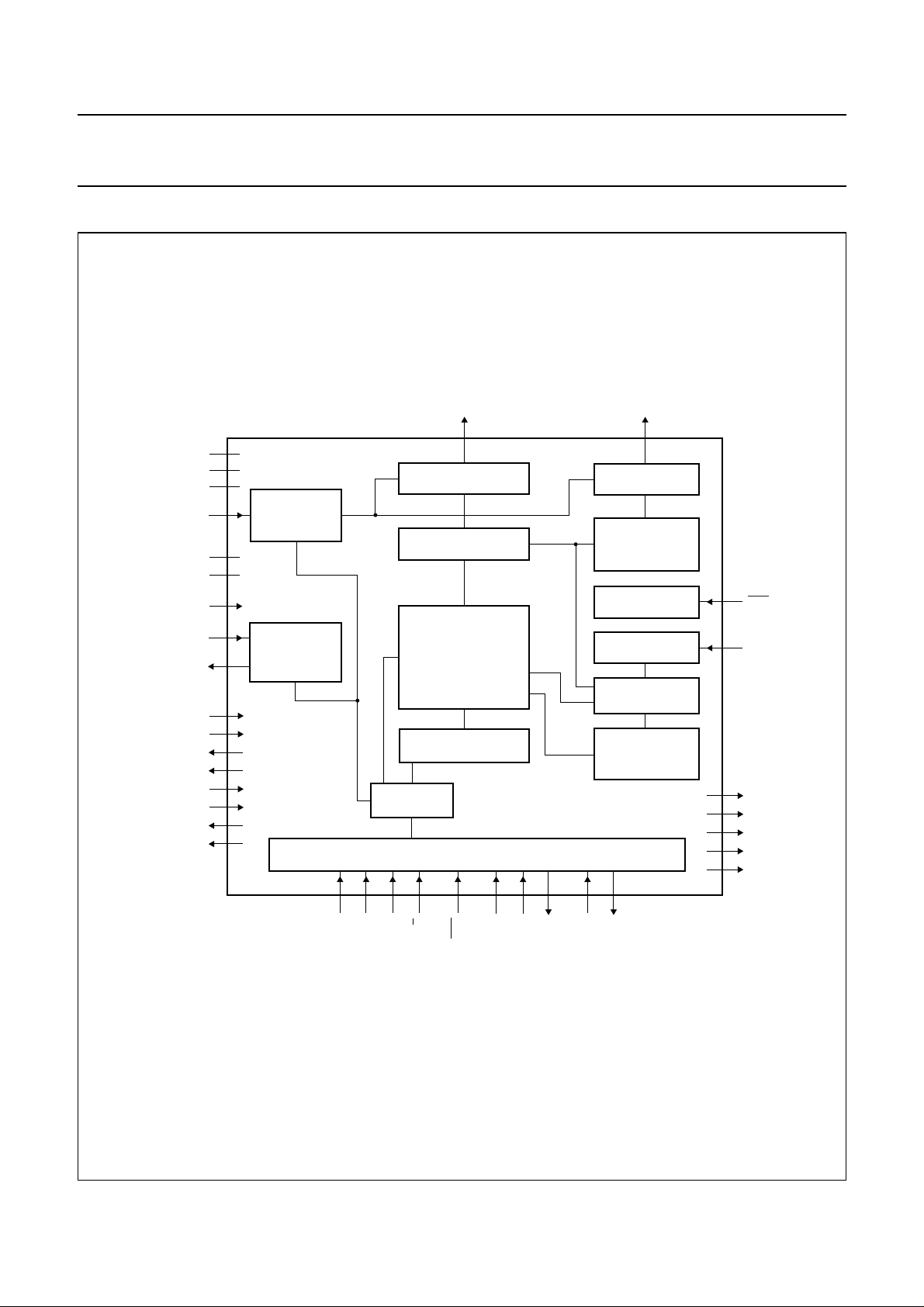

6 PINNING

SYMBOL PAD

V

LCDIN

V

LCDOUT

V

LCDSENSE

V

DD2

V

DD3

(1)

DESCRIPTION

5 to 8 LCD supply voltage input; note 2

9 to 15 LCD supply voltage output from high voltage generator; note 2

16 regulation input to high voltage generator; note 2

17 to 26 supply voltage 2; note 3

27 to 29 supply voltage 3; note 3

OSC 30 oscillator input; note 4

D/

C 31 data/command input/output; note 5

PS[1:0] 32 and 33 interface selection inputs

V

DD1

SDAHOUT 44 I

34 to 39 supply voltage 1; note 3

2

C-bus data output; note 6

SCLK 46 serial data clock input; used in 3-line or 4-line SPI or 3-line serial interface

mode

SDAH 52 I2C-bus data input; note 7

SDO 53 serial data output; note 8

SDATA 54 serial data input; note 9

V

SS2

V

SS1

55 to 61 ground 2 (analog ground); note 10

62 to 67 ground 1 (digital ground); note 10

MX 68 horizontal mirroring input

T3 69 test outputs; note 11

T4 70

T1 71

T2 72

T5 73

T6 74

2

ID3/SA0; ID4/SA1 75 and 76 manufacturer device identification/I

V

DD1

SCE 83 I2C-bus clock input/serial chip enable input in 3-line or 4-line SPI mode; note 5

SCLH/

V

OTPPROG

77 supply voltage 1 (tie-off pad)

84 to 86 supply voltage input for OTP programming; note 13

C-bus slave address input pads; note 12

RES 88 external reset input; active low; must be applied to initialize the chip properly

R32 to R64 105 to 137 LCD row driver outputs

V

C

138 bias buffer output; note 14

T8 141 test outputs; note 11

T7 142

V

1L

143 bias buffer output; note 14

C95 to C48 144 to 191 LCD column driver outputs

C47 to C0 194 to 241

R31 to R0 247 to 278 LCD row driver outputs

V

1H

V

2L

V

2H

244 bias buffer outputs; note 14

245

246

2003 feb 10 5

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

Notes

1. Dummy pads are located at positions 1, 2, 4, 40 to 43, 45, 47 to 51, 78 to 82, 87, 89 to 92, 95 to 104, 139, 140, 192,

193, 242, 243, 279 and 280; alignment marks are located at positions 3 and 93; an alignment bump is located at

position 94.

2. Positive power supply for the liquid crystal display (see also Figs 38, 39 and 40):

a) If the internal voltage generator is used, pads V

LCDIN,VLCDSENSE

b) An external LCD supply voltage can be incorporated using the V

then switched off, pad V

connected to the V

LCDIN

LCDOUT

input; V

must be open-circuit (not connected to pad V

should be applied according to the specified voltage range. In Power-down

DD2,3

mode, the external LCD supply voltage must be switched off.

3. V

DD2

and V

supply the internal voltage generator, both have the same voltage and may be connected together

DD3

outside of the chip; V

supplies the remainder of the chip. V

DD1

then care must be taken with respect to the supply voltage range.

4. When the on-chip oscillator is used, the OSC input must be connected to V

then this is connected to the OSC input. If both the oscillator and external clock are inhibited by connecting pad OSC

to V

, the display is not clocked and may be in a DC state. To avoid this, the chip should always be put into

SS1

Power-down mode before stopping the clock.

5. This input is not used with the 3-line serial interface and must be connected to V

use.

6. SDAHOUT is the serial data acknowledge output from the I2C-bus interface. By connecting SDAHOUT to SDAH

externally, the SDAH line becomes fully I2C-bus compatible. Having the acknowledge output separated from the

serial data line is advantageous in COG applications because here the track resistance from the SDAHOUT pad to

the system SDAH line can be significant and a potential divider can be generated by the bus pull-up resistor and the

ITO track resistance. It is possible that during the acknowledge cycle the OM6208 will not be able to create a valid

logic 0. By splitting the SDAH input from the SDAHOUT output the device could be used in a mode that ignores the

acknowledgebit.ThereforeinCOGapplicationswheretheacknowledgecycleis required, it is necessary to minimize

the track resistance from the SDAHOUT pad to the system SDAH line to guarantee a valid logic 0. When SDAHOUT

is not used, it must be connected to V

7. When I2C-bus is not used, this pad must be connected to V

DD1

or V

SS1

.

DD1

8. SDO is a push-pull output; when it is intended to use the readback function of the OM6208, this pad must be

connected to the SDATA pad, or used separately; when I2C-bus interface is selected, this pad should be connected

to V

DD1

or V

SS1

.

9. When I2C-bus interface is selected this pin should be connected to V

10. Supply rails V

SS1

and V

must be connected together.

SS2

11. Test padsT1 to T8arenotaccessibletousers:T1, T2, T5 and T6 must be connected to VSS; T3,T4,T7and T8 must

be open-circuit.

12. Module identification bits: these bits may be read back via the ‘read back’ instruction; when the I2C-bus interface is

being used, these bits are the two LSBs of the slave address.

13. V

OTPROG

configuration, then V

can be connected to SCLH/SCE pad to reduce the external connections. If not connected in this

OTPROG

should be open-circuit during normal operation.

14. These pads are not accessible to users and must be left open-circuit; an explanation of the bias buffer function is

given in Section 11.9.

DD1

or V

, V

and V

pad; the internal voltage generator must

LCDIN

and V

DD2

.

SS1

or V

DD1

must be connected together.

LCDOUT

) and pad V

LCDIN

can be connected together but

DD3

. If an external clock signal is used,

DD1

or V

SS1

DD1

.

SS1

LCDSENSE

when this interface is in

2003 feb 10 6

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

7 FUNCTIONAL DESCRIPTION

7.1 I/O buffers and interfaces

One of four industrial standard interfaces can be selected

using the interface configuration inputs PS1 and PS0.

2

Table 1 Serial/I

C-bus interface selection

PS1 PS0 SELECTED INTERFACE

0 0 3-line SPI

0 1 4-line SPI

10I

2

C-bus interface

1 1 3-line serial interface

7.2 Oscillator

The on-chip oscillator provides the clock signal for the

display system. No external components are required

when the internal oscillator is used. An external clock

signal, if used, is connected to this input.

7.3 Address counter

The Address Counter (AC) assigns addresses to the

displaydataRAMforwriting. The X address X[6:0] and the

Y address Y[4:0] are set separately.

7.6 Timing generator

The timing generator produces the various signals

required to drive the internal circuitry. Internal chip

operation is not affected by operations on the data bus.

7.7 Data processing

The data processing block receives data from the RAM

and the orthogonal function from the logic circuits, then

selects the correct voltage level to be provided to the

columns.

7.8 High voltage generator

The high voltage generator provides the programmed

V

to the bias voltage generator block.

LCD

7.9 Bias voltage generator

Thebiasvoltagegeneratorgeneratesallthevoltagelevels

required for the MRA driving system.

7.10 Command decoder

The command decoder identifies command words arriving

at the interface and routes the data bytes that follow to

their destination.

7.4 Display data RAM

The OM6208 contains a 65 × 96 × 2 bit static RAM which

stores the display data. The display data RAM is divided

into 17 banks of 96 bytes, although only two bits of the

17th bank are used. During RAM access, data is

transferred to the RAM via the serial interface. There is a

direct correspondence between X address and column

output number.

7.5 Display address counter

The display is generated by simultaneously reading out

the RAM content for two or four rows, depending on the

current display size that is selected. This content will be

processed with the corresponding set of two or four

orthogonal functions and so generate the signals for

switchingthepixelsofthedisplayonoroff according to the

RAM content.

The display status (all dots on/all dots off and

normal/inverse video) is set by the bits DON, DAL and E

in the command Display control (see Table 8).

7.11 Orthogonal function generator

The orthogonal function generator generates a set of

orthogonal functions suitable for the selected value of p

(number of active rows).

7.12 Reset

The reset block handles the hardware reset input (RES)

andsoftware reset and provides all internal blocks with the

required reset signal.

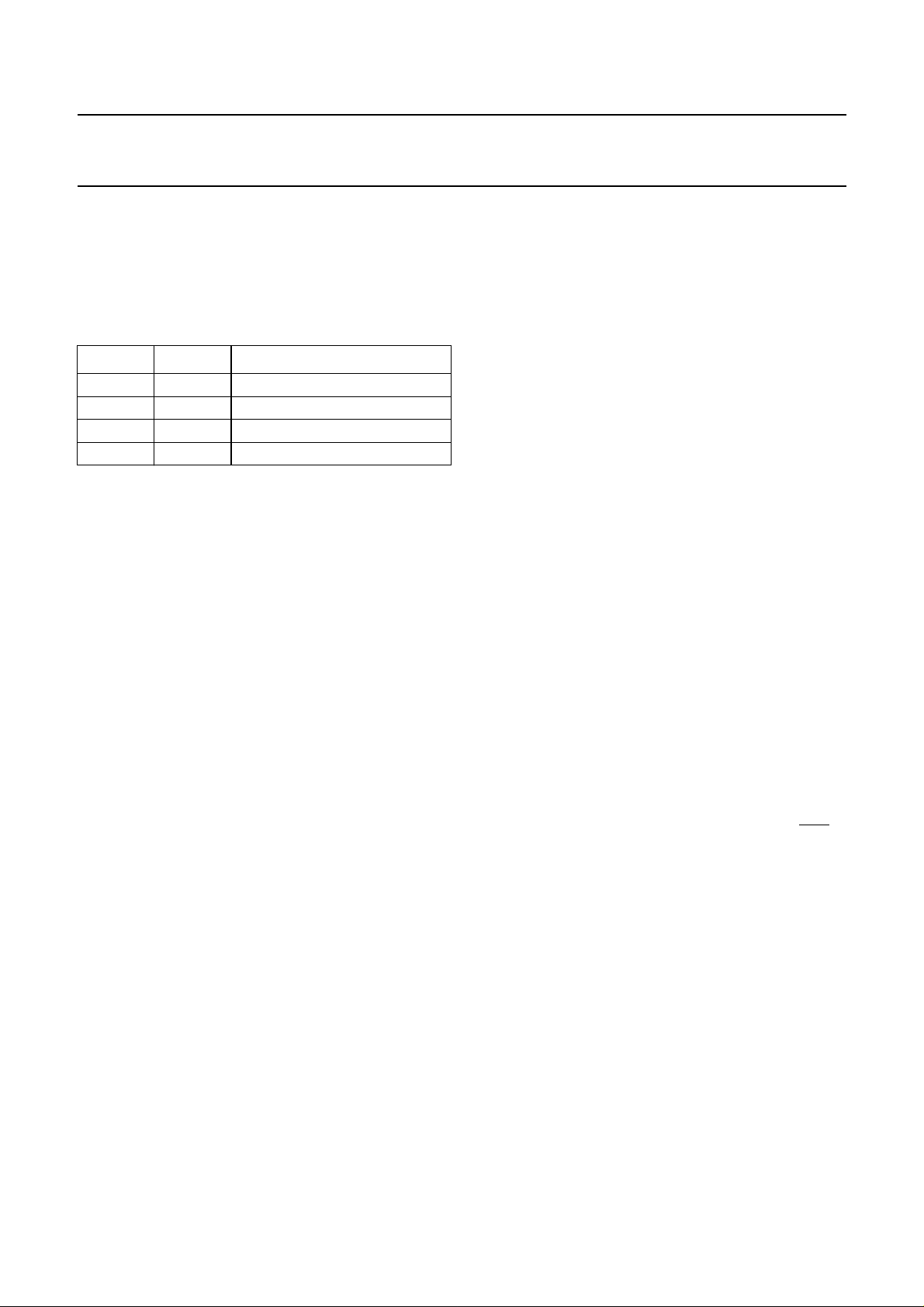

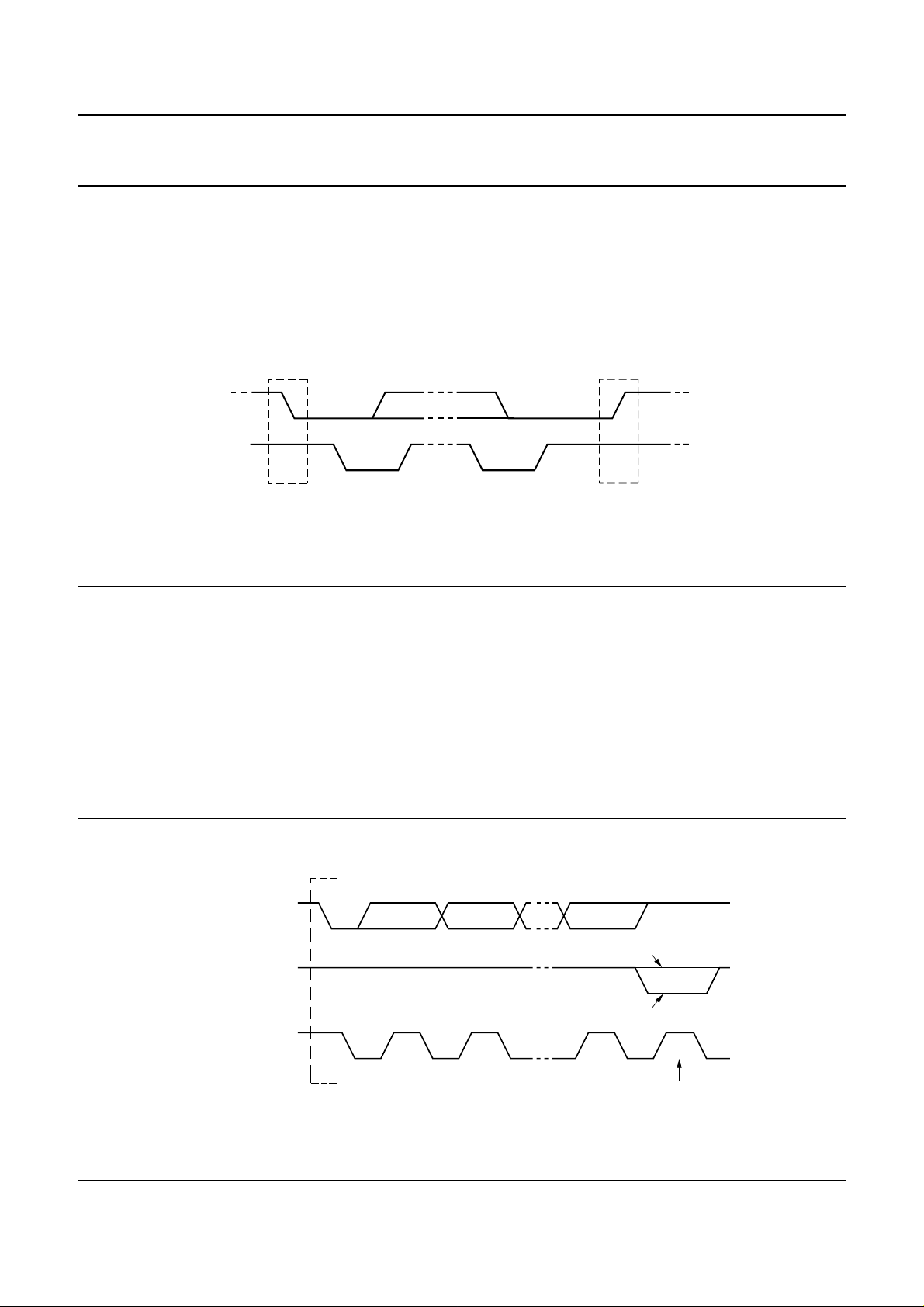

7.13 Row drivers and column drivers

The OM6208 contains 65 row and 96 column drivers

which connect the appropriate LCD bias voltages in

sequence to the display in accordance with the data to be

displayed. A typical MRA driving scheme with waveforms

for p = 4 is shown in Fig.2. The value of p represents the

number of simultaneously selected rows.

2003 feb 10 7

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

handbook, full pagewidth

F1(t)

F2(t)

F3(t)

F4(t)

G1(t)

F1(t)

V

col(max)

V

C

V

col(min)

G1(t)

G1(t) = C [+ F1(t) − F2(t) − F3(t) + F4(t)

G1(t)

G2(t) G3(t)

G2(t) G3(t)

]

F2(t)

F3(t)

F4(t)

V

col(max)

G1(t)

V

C

V

col(min)

Fig.2 Typical MRA LCD driver waveforms for p = 4.

2003 feb 10 8

G1(t) = C [− F1(t) − F2(t) − F3(t) + F4(t)

MGW822

]

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

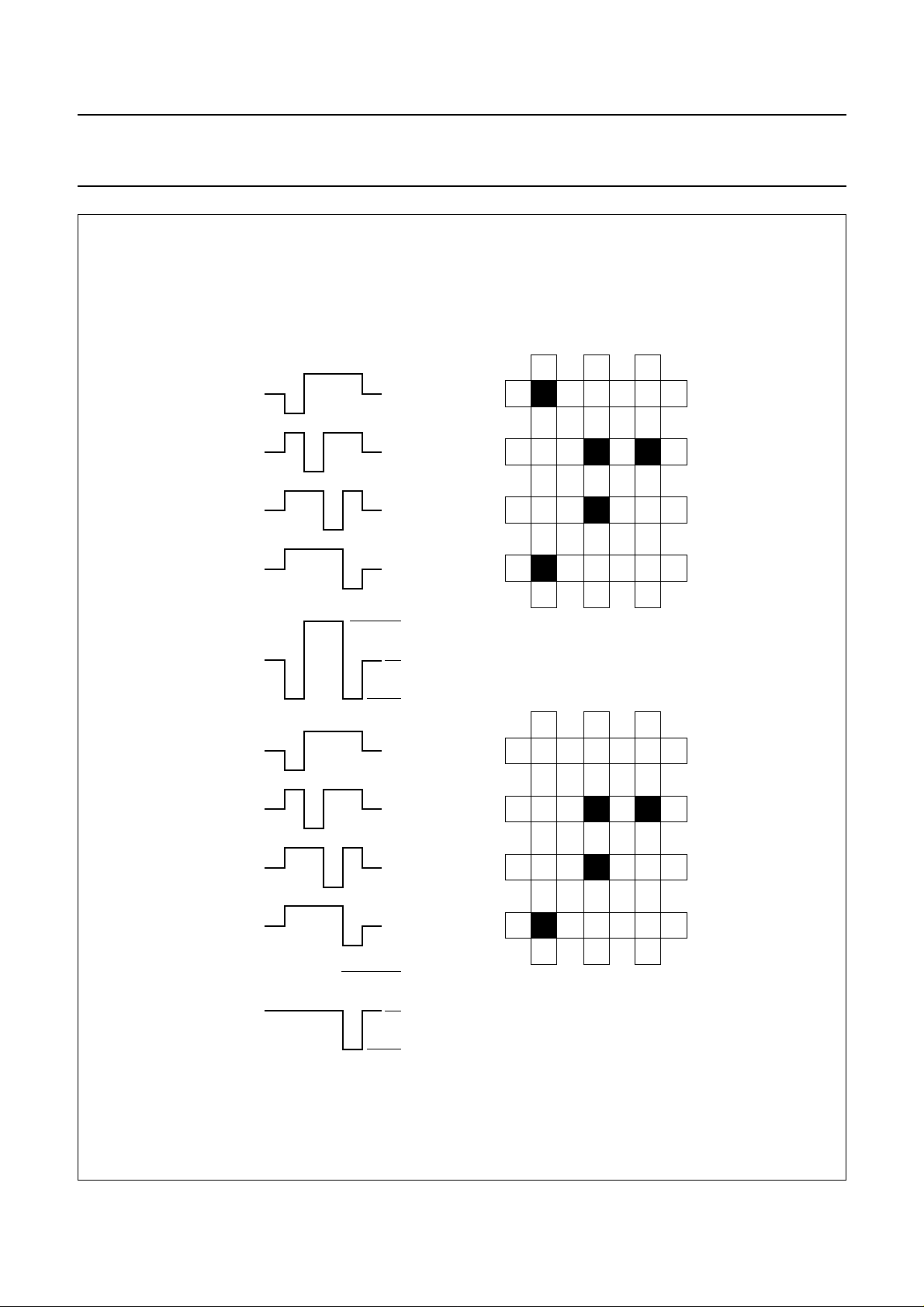

8 RAM ADDRESSING

Data is downloaded in bytes into the RAM matrix of the

OM6208 as indicated in Fig.3. The display RAM has a

matrix of 65 × 96 × 2 bits. The columns are addressed by

the address pointer. The address ranges (decimal values)

handbook, full pagewidth

DOR = 1

LSB

MSB

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

P0

MSB

P0

LSB

P1

MSB

P1

LSB

P2

MSB

P2

LSB

P3

MSB

P3

LSB

P0

P1

P2

P3

P0

bank 0

P1

P2

P3

bank 1

bank 2

bank 3

.

DOR = 0

LSB

MSB

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

P3

LSB

P3

MSB

P2

LSB

P2

MSB

P1

LSB

P1

MSB

P0

LSB

P0

MSB

.

.

bank 13

bank 14

bank 15

X

X

X

bank 16

X

X

X

areX=0to95andY=0to16.TheYaddressrepresents

the bank number. Addresses outside these ranges are not

allowed.

The Data Order Bit (DOR) defines the bit order (LSB on

top or MSB on top) for writing into the RAM.

LSB

MSB

top of LCD

R0

R4

R8

R12

.

.

.

.

.

LCD

R16

R52

R56

R60

R64

Fig.3 DDRAM-to-display mapping.

2003 feb 10 9

MGW823

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

8.1 Display data RAM structure

The mode for storing data in the display data RAM is

dependent on:

• Horizontal/vertical addressing mode set by bit V in the

‘RAM addressing mode’ instruction

• Data order set by bit DOR in the ‘data order’ instruction

• Mirror the X-axis set by input MX.

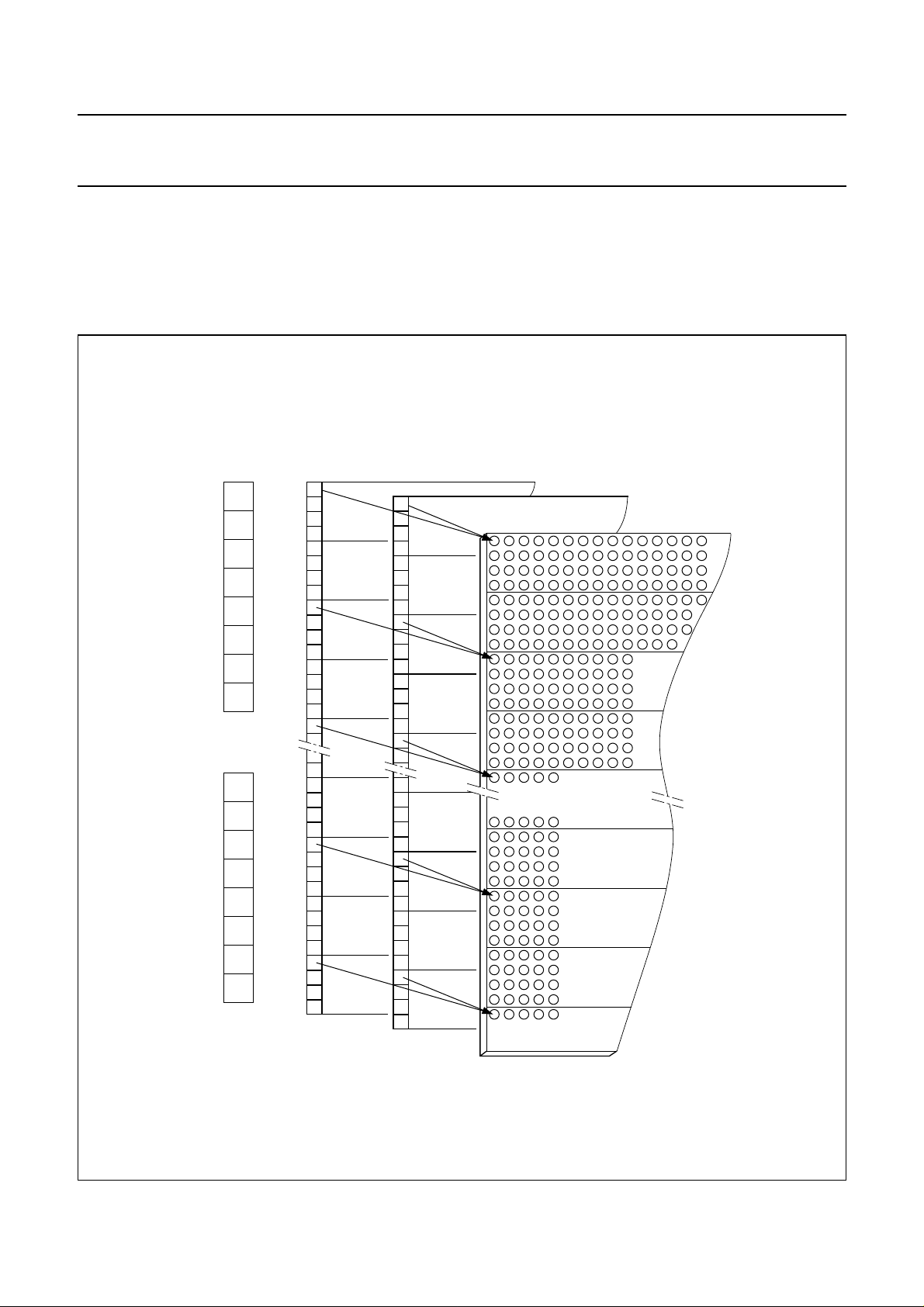

8.1.1 HORIZONTAL/VERTICAL ADDRESSING

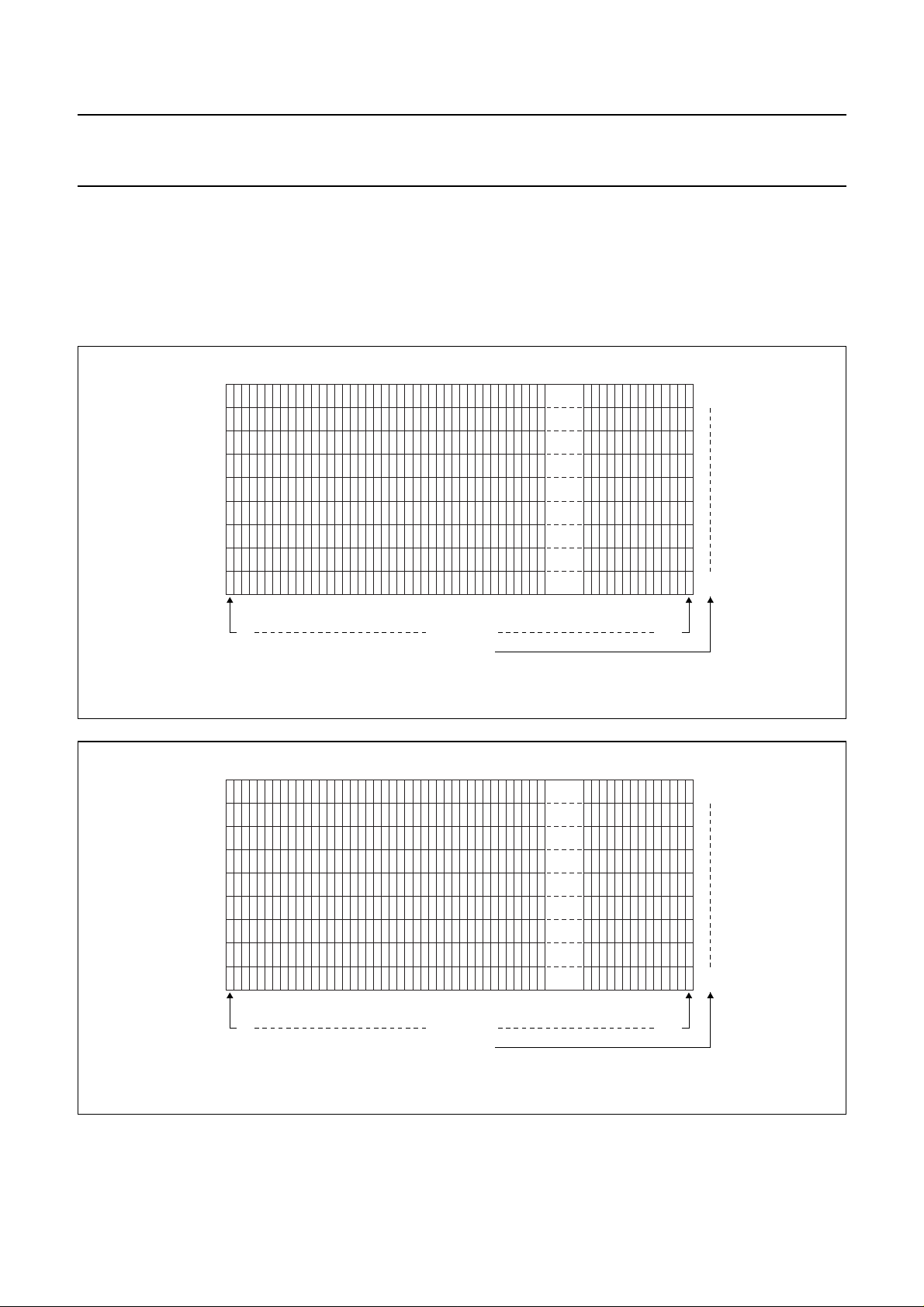

Two different addressing modes are possible; horizontal

addressing mode and vertical addressing mode.

handbook, full pagewidth

01

192 193

288 289

384

2

98

194

290

386385

In the horizontal addressing mode (V = 0) the X address

increments after each byte. After the last X address

(X = 95), X wraps around to 0 and Y increments to

address the next row (see Fig.4).

In the vertical addressing mode (V = 1), the Y address

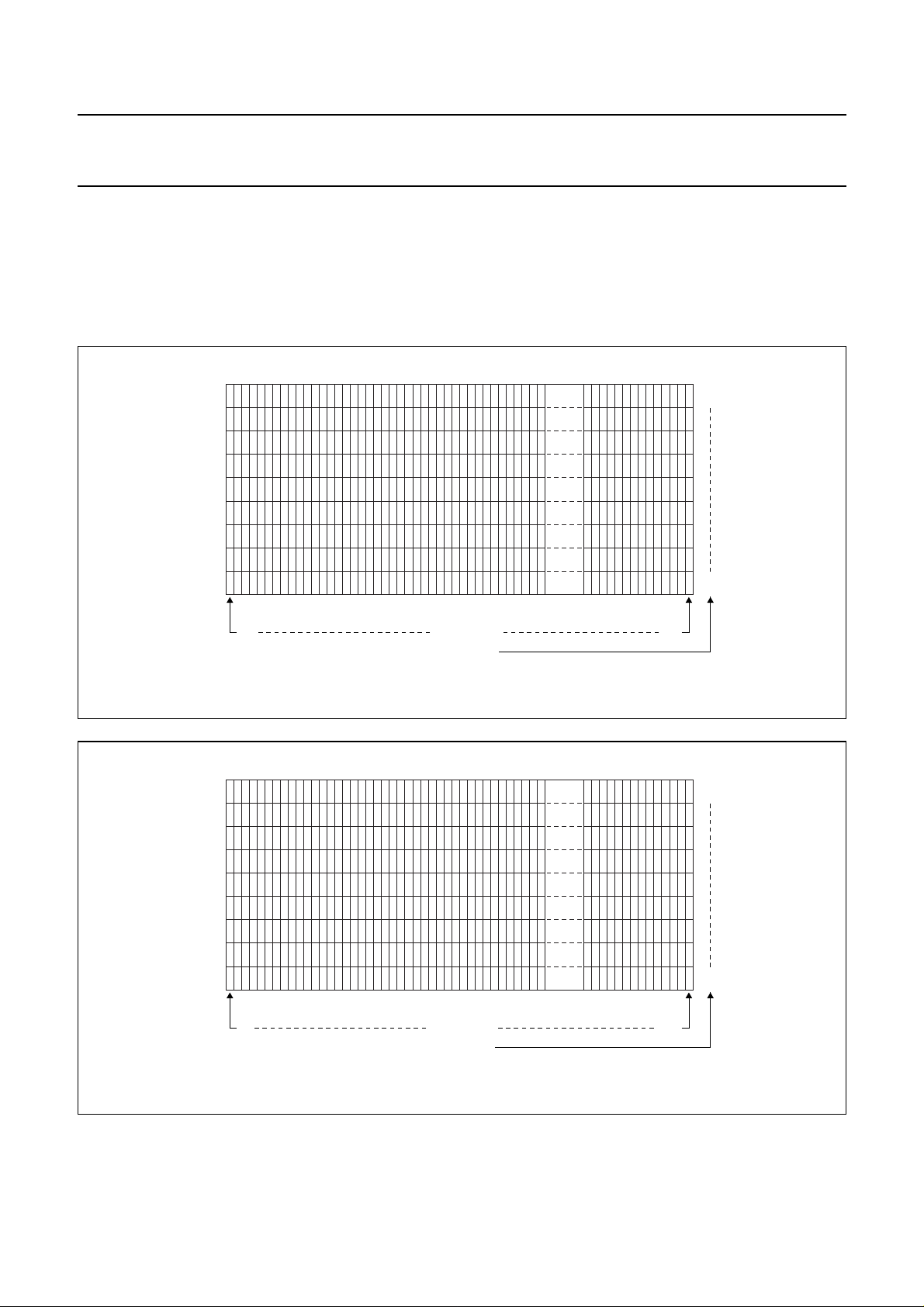

increments after each byte. After the last Y address

(Y = 16), Y wraps around to 0 and X increments to

address the next column (see Fig.5).

After the very last address, the address pointers wrap

around to address X = 0 and Y = 0 in both horizontal and

vertical addressing modes.

95

19196 97

0

Y address

handbook, full pagewidth

1440

1441 1442

1536

1537

0 95X address

1535

161631

MGW824

Fig.4 Sequence of writing data bytes into RAM with horizontal addressing (V = 0).

017

118

219

320

421

522

16 33

0 95X address

0

Y address

161631

MGW825

Fig.5 Sequence of writing data bytes into the RAM with vertical addressing (V = 1).

2003 feb 10 10

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

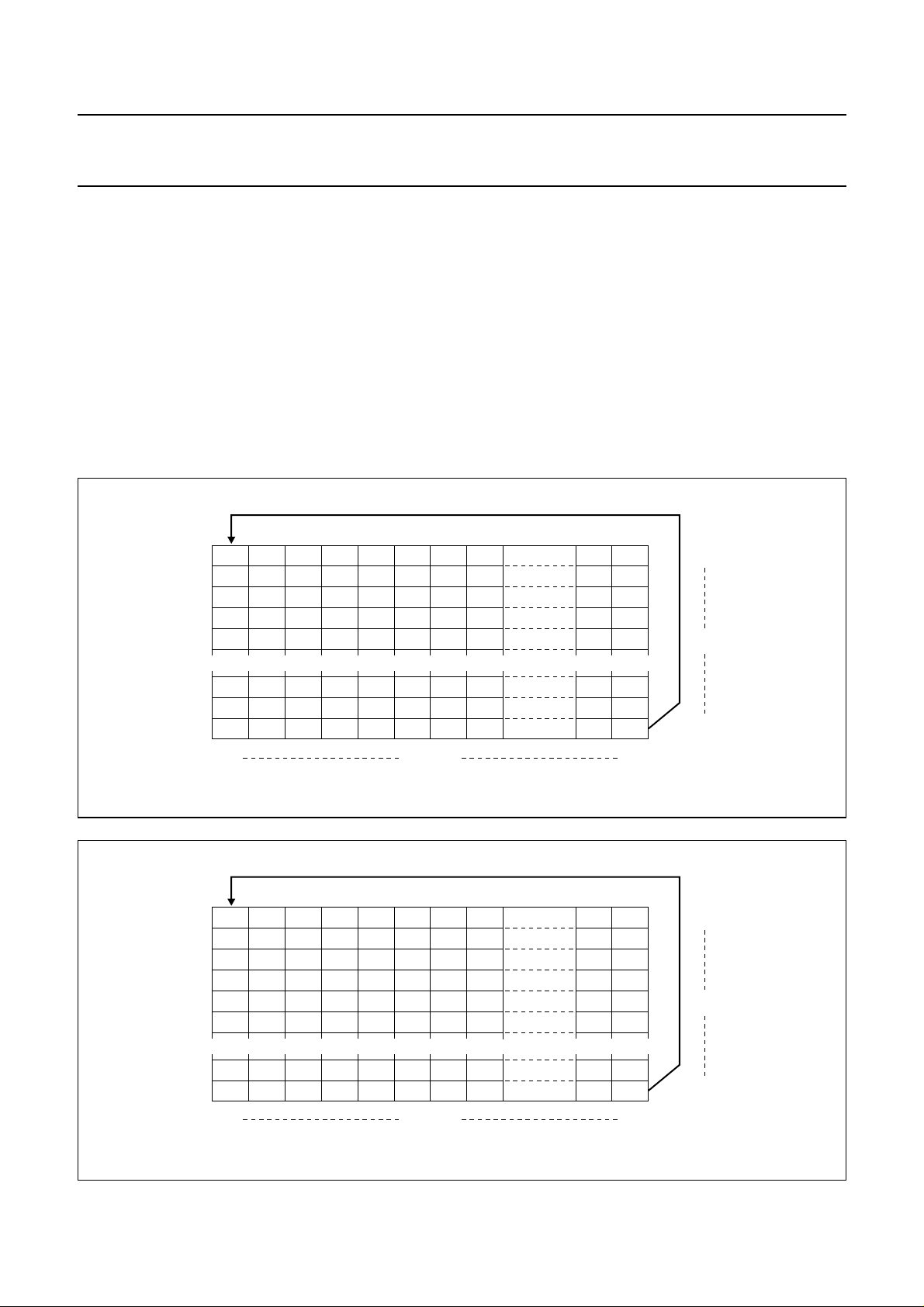

8.1.2 MIRROR Y

The Mirror Y (MY) bit allows vertical mirroring:

• When MY = 1, the Y address space is mirrored; the

address Y = 0 is then located at the bottom of the

display (see Fig.6)

handbook, full pagewidth

0 95X address

• When MY = 0, the mirroring is disabled and the address

Y = 0 is located at top of the display (see Fig.7).

Refer also to Section 11.6.

16

0

Y address

MGW826

handbook, full pagewidth

Fig.6 RAM format addressing (MY = 1).

0 95X address

Y address

Fig.7 RAM format addressing (MY = 0).

0

16

MGW827

2003 feb 10 11

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

8.1.3 MIRROR X

The Mirror X (MX) input allows a horizontal mirroring:

• When MX = 1, the X address space is mirrored; the

address X = 0 is then located at the right side (X

max

the display (see Fig.8)

handbook, full pagewidth

95 0X address

) of

Y address

• When MX = 0, the mirroring is disabled and the address

X = 0 is located at the left side (column 0) of the display

(see Fig.9).

Refer also to Section 11.6.

0

16

MGW828

handbook, full pagewidth

Fig.8 RAM format addressing (MX = 1).

0 95X address

Y address

Fig.9 RAM format addressing (MX = 0).

0

16

MGW829

2003 feb 10 12

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

9 SERIAL INTERFACING

Communication with the microcontroller can occur via a

clock-synchronized serial peripheral interface. It is

possible to select two different 3-line (SPI and serial

interface) or a 4-line SPI interface. Selection is done via

the PS[1:0] inputs.

9.1 Serial peripheral interface

The Serial Peripheral Interface (SPI) is a 3-line or 4-line

interface for communication between the microcontroller

and the LCD driver chip. Three lines are common to both

3-line and 4-line SPI, these are SCE (chip enable), SCLK

(serial clock) and SDATA (serial data). For the 4-line SPI a

separate D/C line is added. The OM6208 is connected to

the serial data I/O of the microcontroller by pads SDATA

(data input) and SDO (data output) connected together.

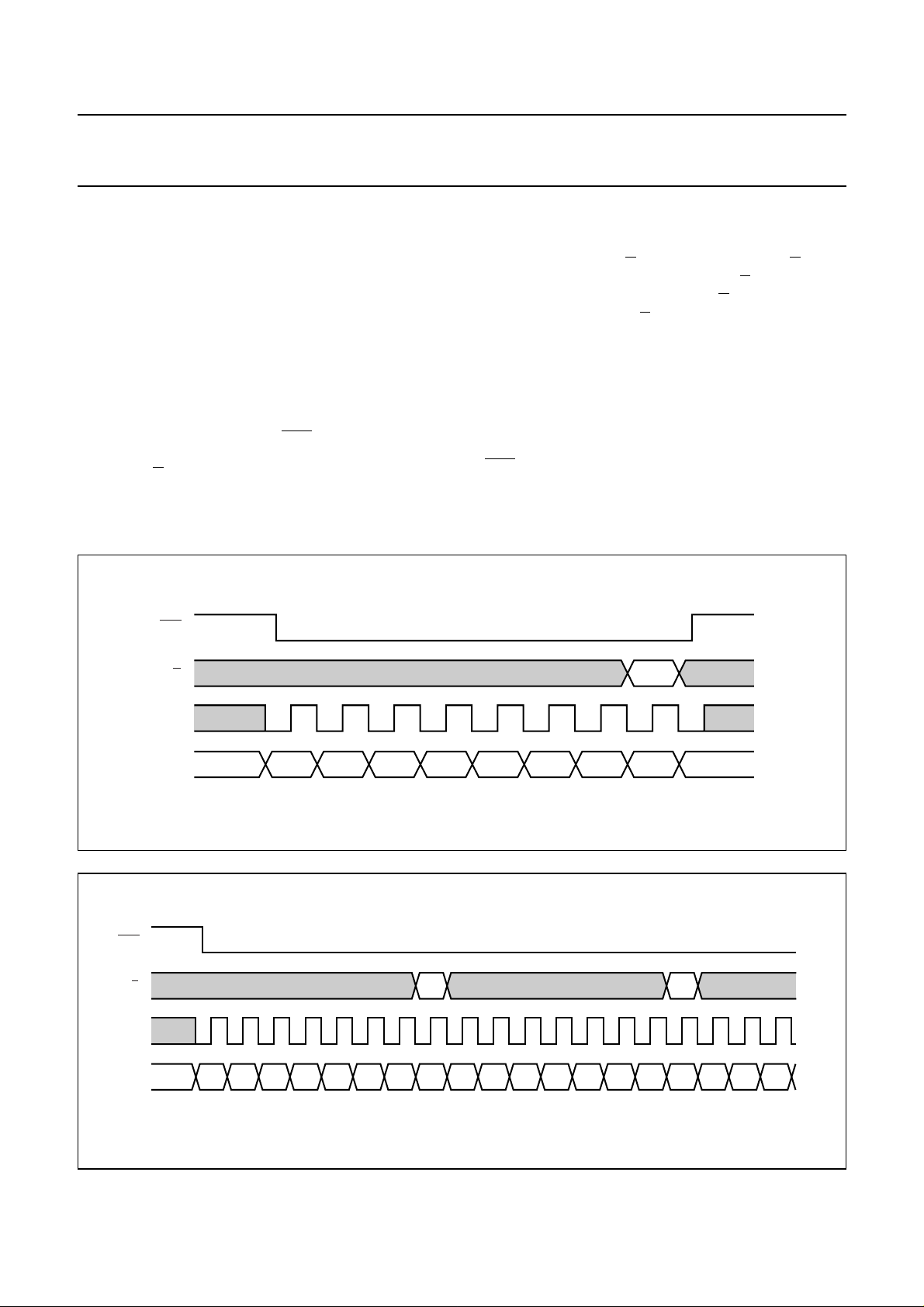

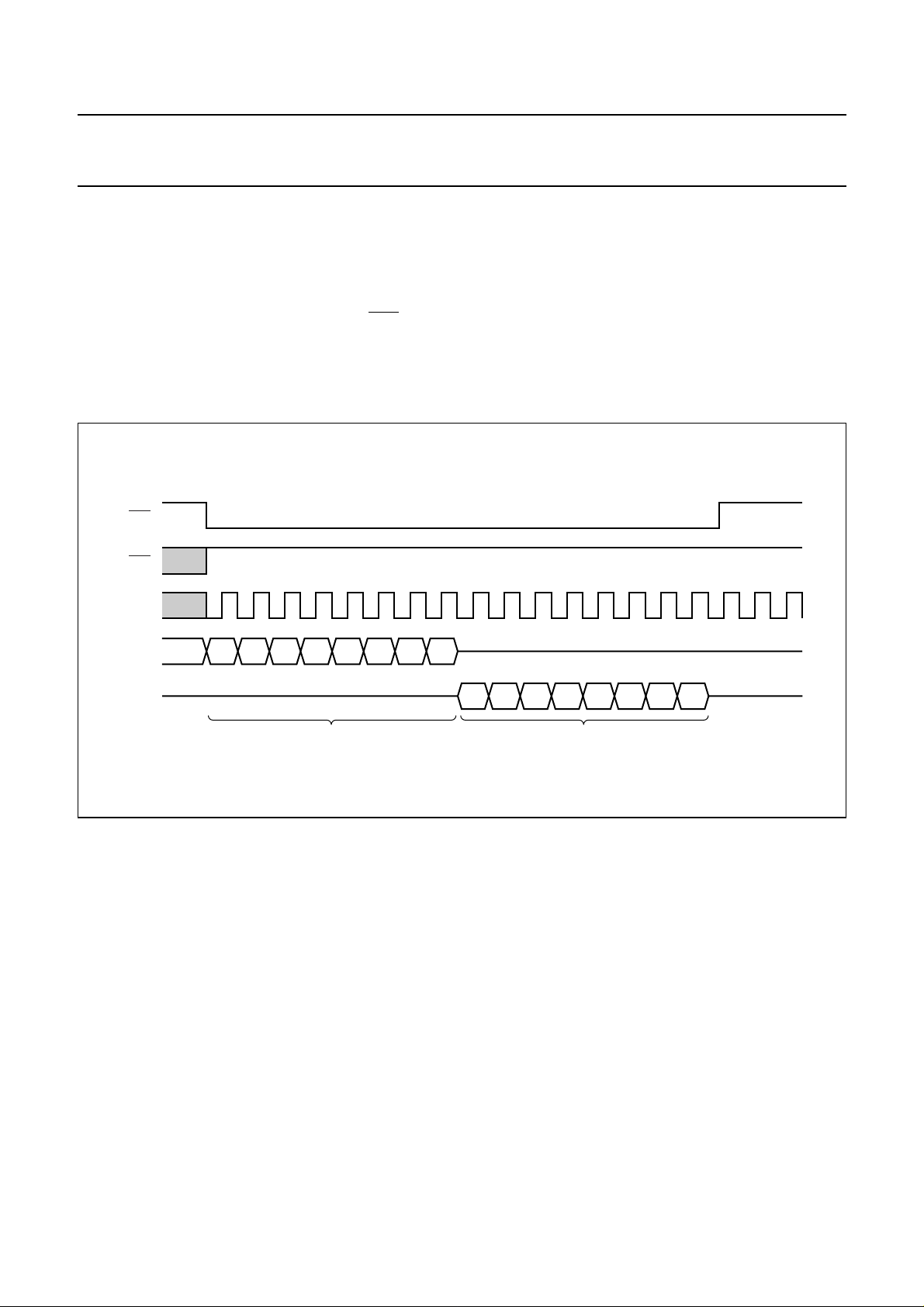

handbook, full pagewidth

SCE

9.1.1 WRITE MODE

The display data/command indication may be controlled

by software or by the D/C select pin. When the D/C pad is

used, display data is transmitted when D/C is HIGH, and

command data is transmitted when D/C is LOW (see

Figs 10 and 11). When D/C is not used, the ‘display data

length’instructionis used toindicatethata specific number

of display data bytes (1 to 255) are to be transmitted (see

Fig.11). The next byte after the display data string is

handled as an instruction command.

When the 3-line SPI interface is used the display

data/command is controlled by software (see Fig.12).

If SCE is pulled high during a serial display data stream,

the interrupted byte is invalid data but all previously

transmitted data is valid. The next byte received will be

handled as an instruction command (see Fig.13).

D/C

SCLK

SDATA

DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

Fig.10 4-line SPI bus protocol; transmission of one byte.

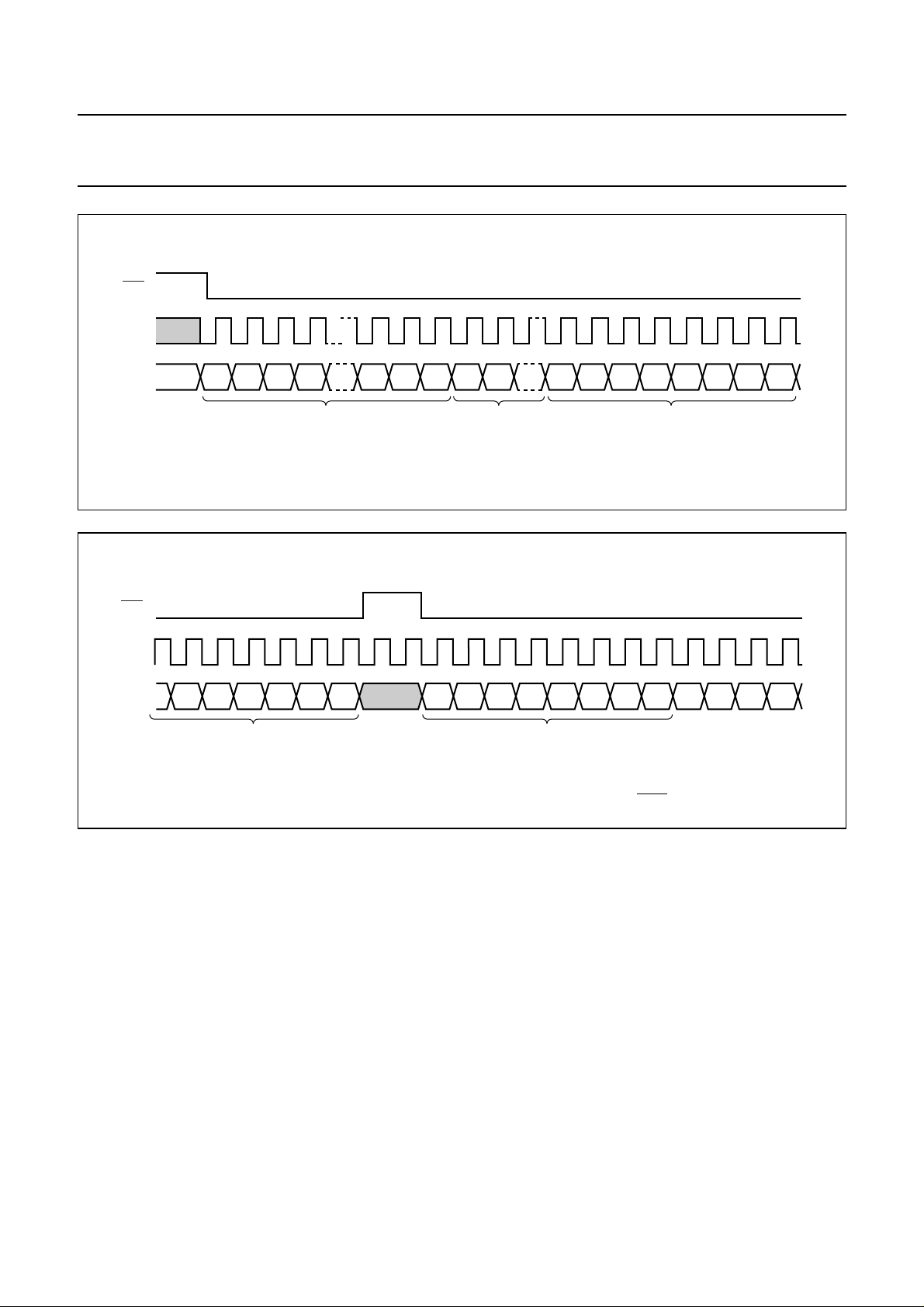

handbook, full pagewidth

SCE

D/C

SCLK

SDATA DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 DB7DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

MGW744

DB6 DB5

MGW745

Fig.11 4-line SPI bus protocol; transmission of several bytes.

2003 feb 10 13

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

handbook, full pagewidth

SCE

SCLK

SDATA DB7 DB6 DB5 DB4

handbook, full pagewidth

SCE

SCLK

SDATA

datadata data data data data

display data string

Fig.13 3-line SPI bus protocol: transmission interrupted by SCE.

DB2 DB1 DB0 DB2

display length instruction

and length data (two bytes)

data data

last

DB7 DB6 DB5 DB4 DB3 DB1 DB0

data

Fig.12 3-line SPI bus protocol; transmission of several bytes.

instruction

instructiondisplay data string

DB7DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 DB6 DB5 DB4

MGW746

MGW747

2003 feb 10 14

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

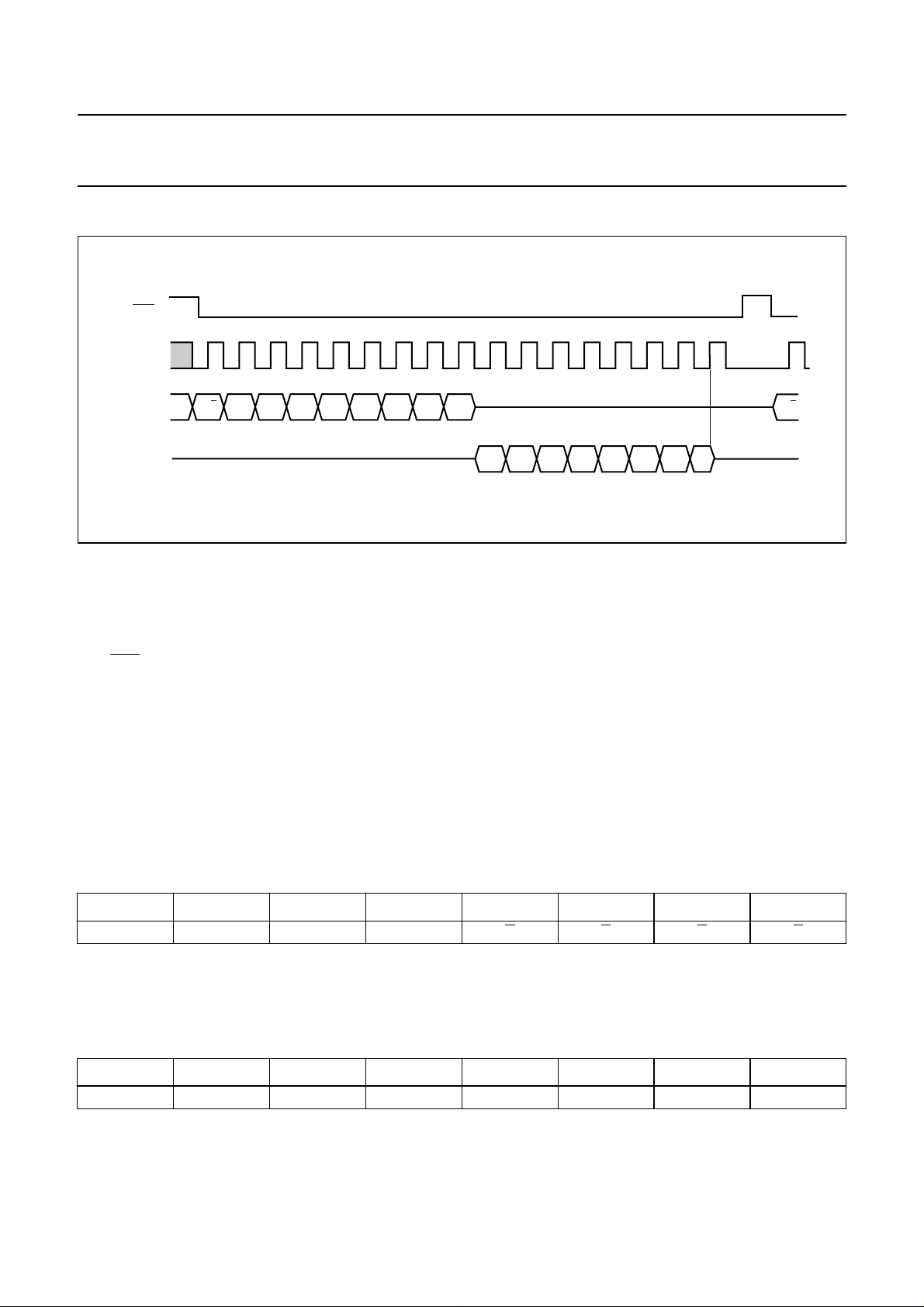

9.1.2 READ MODE

The read mode of the interface means that the

microcontroller reads data from the OM6208. To do so the

microcontroller first has to send a command, the read

status command, and then OM6208 will respond by

transmitting data on the SDO line. After that, SCE is

required to go HIGH (see Fig.14).

The OM6208 samples the SDATA data at rising SCLK

edges, but shifts SDO data at falling SCLK edges. Thus

handbook, full pagewidth

SCE

RES

SCLK

SDATA DB7 DB6 DB5 DB4 DB2DB3 DB1 DB0

the SDO data is available to be read by the microcontroller

at rising SCLK edges.

After the read status command has been sent, the SDATA

line must be set to 3-state (high-impedance) not later than

at the falling SCLK edge of the last bit (see Fig.14).

For the read data format, see Section 9.2.3; the serial

interface timing diagram is given in Chapter 15.

SDO

instruction

read out data

Fig.14 Read mode SPI 3- and 4-line interfaces.

DB2DB7 DB6 DB5 DB4 DB3 DB1 DB0

MGU629

2003 feb 10 15

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

9.2 Serial interface (3-line)

The serial interface is also a 3-line bidirectional interface

for communication between the microcontroller and the

LCD driver chip. The three lines are SCE (chip enable),

SCLK(serialclock) and SDATA (serialdata).TheOM6208

is connected to the SDA of the microcontroller by the

SDATA(datainput)andSDO (data output) pads which are

connected together.

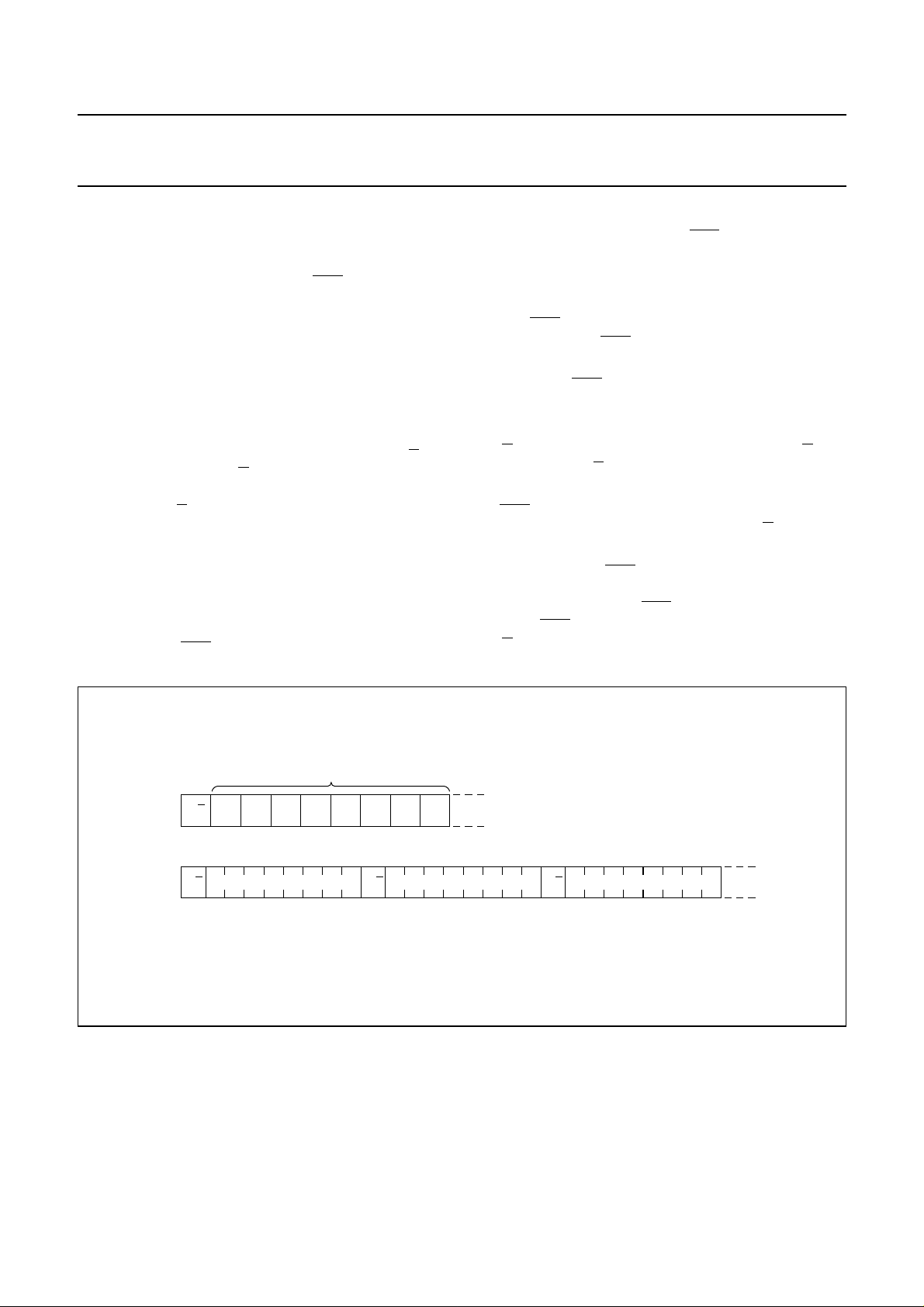

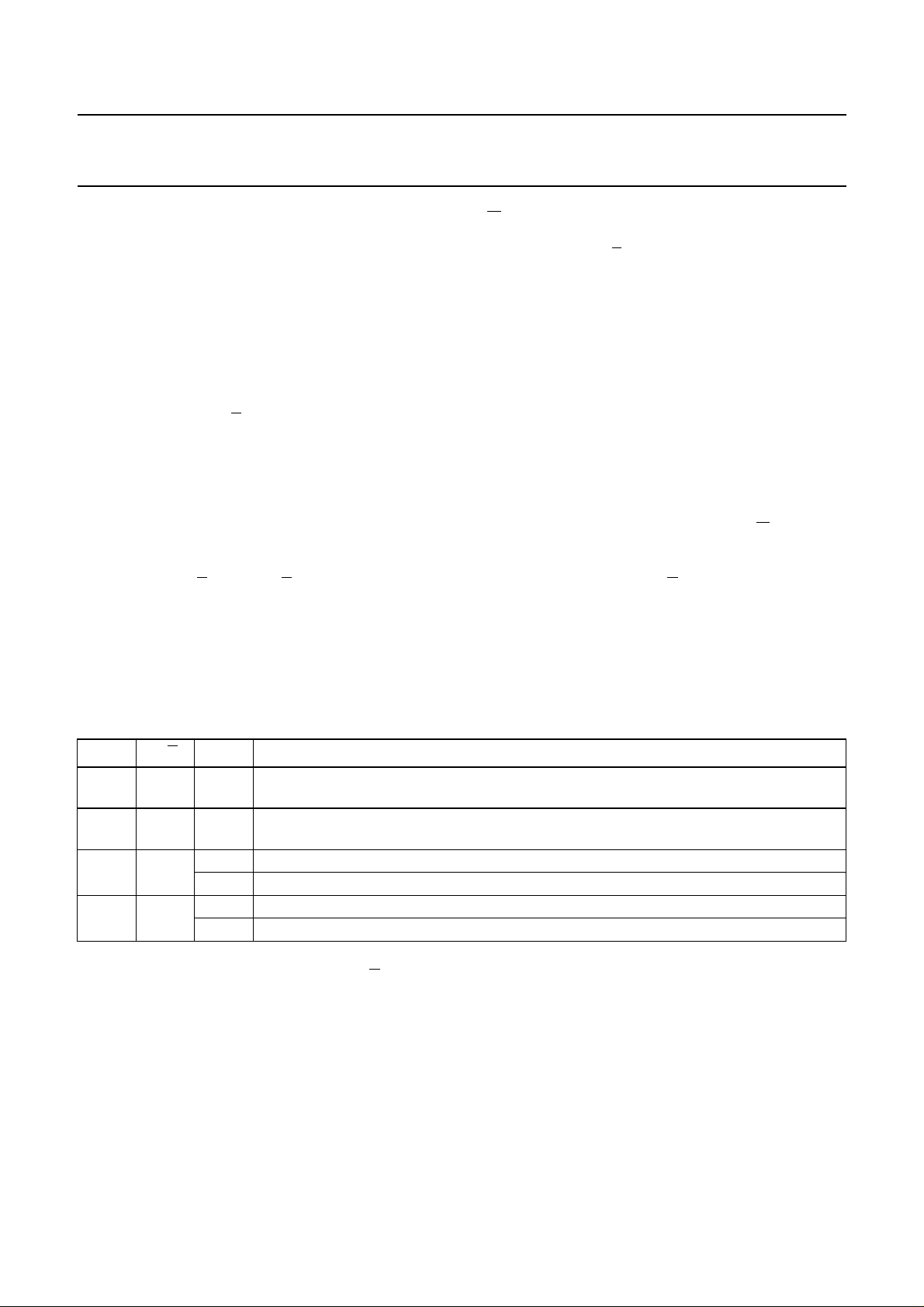

9.2.1 WRITE MODE

The write mode of the interface means that the

microcontroller writes instructions and data to the

OM6208. Each data packet contains a control bit D/C and

a transmission byte. If D/C is LOW, the following byte is

interpreted as command byte. The instruction set is given

in Table 7. If D/C is HIGH, the following byte is stored in

the display data RAM. After every data byte the address

counter is incremented automatically. The general format

of the write mode and the definition of the transmission

byte is shown in Fig.15.

Any instruction can be sent in any order to the OM6208.

The MSB is transmitted first. The serial interface is

initialized when SCE is HIGH. In this state, SCLK clock

pulses have no effect and no power is consumed by the

serial interface. A falling edge on SCE enables the serial

interface and indicates the start of data transmission.

Figures 16, 17 and 18 show the protocol of the write

mode:

• When SCE is HIGH, SCLK clocks are ignored. During

the HIGH time of SCE the serial interface is initialized

(see Fig.16)

• At the falling SCE edge, SCLK must be LOW

(see Fig.32)

• SDATA is sampled at the rising edge of SCLK

• D/C indicates whether the byte is a command (D/C=0)

or RAM data (D/C = 1) byte; it is sampled with the first

rising SCLK edge

• If SCE stays LOW after the last bit of a command/data

byte, the serial interface is ready for the D/C bit of the

next byte at the next rising edge of SCLK (see Fig.17)

• A reset pulse with RES interrupts the transmission. The

data being written into the RAM may be corrupted. The

registers are cleared. If SCE is LOW after the rising

edge of RES, the serial interface is ready to receive the

D/C bit of a command/data byte (see Fig.18).

D/C

(1)

transmission byte

handbook, full pagewidth

D7 D6 D5 D4 D3 D2 D1 D0

D/C

MSB LSB

D/C

(1) A transmission byte may be a command byte or a data byte.

transmission byte

transmission byte

Fig.15 Serial data stream, write mode.

2003 feb 10 16

D/C

transmission byte

MGW713

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

handbook, full pagewidth

SCE

SCLK

SDATA

D/C

DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

Fig.16 Write mode: a control bit followed by a transmission byte.

handbook, full pagewidth

SCE

SCLK

SDATA DB7D/C DB6 DB5 DB4 DB3 DB2

DB1 DB0

MGU630

DB7D/C DB6 DB5 DB4 DB3 DB2 DB1 DB0 D/C

transmission byte

transmission byte

Fig.17 Write mode: transmission of several bytes.

handbook, full pagewidth

SCE

RES

SCLK

SDATA DB7D/C DB6 DB5 DB4 DB7DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

Fig.18 Write mode: interrupted by reset (RES).

2003 feb 10 17

MGU631

DB6D/C D/C

MGU632

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

9.2.2 READ MODE

handbook, full pagewidth

SCE

SCLK

SDATA

SDO

DB7D/C DB6 DB5 DB4

DB3 DB2 DB1 DB0

Fig.19 Read mode serial interface 3-line.

The read mode of the interface means that the

microcontroller reads data from the OM6208. To do so the

microcontroller first has to send a command, the read

statuscommand,and then the followingbyteistransmitted

in the opposite direction using SDO (see Fig.19). After

that, SCE is required to go HIGH before a new command

is sent.

The OM6208 samples the SDATA data at rising SCLK

edges and shifts SDO data at falling SCLK edges. Thus

the SDO data is available for the microcontroller to read at

rising SCLK edges.

After the read status command has been sent, the SDATA

linemustbe set to 3-state not later then at the falling SCLK

edge of the last bit (see Fig.19).

D/C

DB7 DB6 DB5 DB4 DB3 DB2 DB1

DB0

MCE176

The 8th read bit is shorter than the others because it is

terminated by the rising SCLK edge (see Fig.35). The last

rising SCLK edge sets SDO to 3-state after the delay

time t4.

9.2.3 READ DATA FORMAT

Regardless of which serial interface is used there are five

bits that can be read (ID1 to ID4 and VM) and one

temperatureregister.For the bits, one bit istransmittedper

byte read and is selected by issuing the appropriate read

instruction from the instruction set. Bits ID1 and ID2 are

hard-wired so that ID1 always returns a logic 0 and ID2

always returns a logic 1. Bits ID3 and ID4 are the

identification bits and are set via ID3/SA0 and ID4/SA1

pads. The format for the read bit, B, is shown in Table 2.

Table 2 Read data format

D7 (MSB) D6 D5 D4 D3 D2 D1 D0 (LSB)

(1)

x

BBBBBBB

Note

1. x = undefined.

Table 3 Read temperature sensor

Sending the instruction to read back the temperature sensor data will select the following status byte.

D7 (MSB) D6 D5 D4 D3 D2 D1 D0 (LSB)

(1)

x

TD[6] TD[5] TD[4] TD[3] TD[2] TD[1] TD[0]

Note

1. x = undefined.

2003 feb 10 18

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

10 I2C-BUS INTERFACE

2

10.1 Characteristics of the I

C-bus (Hs-mode)

The I2C-bus Hs-mode is for bidirectional, two-line

communication between different ICs or modules with

speeds up to 3.4 MHz. The only difference between

Hs-modeslavedevicesandF/S-modeslavedevicesisthe

speed at which they operate, therefore the buffers on the

SDAH output have an open drain. This is the same for

2

C-bus master devices which have an open-drain SDAH

I

output and a combination of an open-drain pull-down and

current source pull-up circuits on the SCLH output. Only

the current source of one master is enabled at any one

time and only during Hs-mode. Both lines must be

connected to a positive supply via a pull-up resistor.

Data transfer may be initiated only when the bus is not

busy.

SDA

SCL

MASTER

TRANSMITTER/

RECEIVER

SLAVE

RECEIVER

TRANSMITTER/

RECEIVER

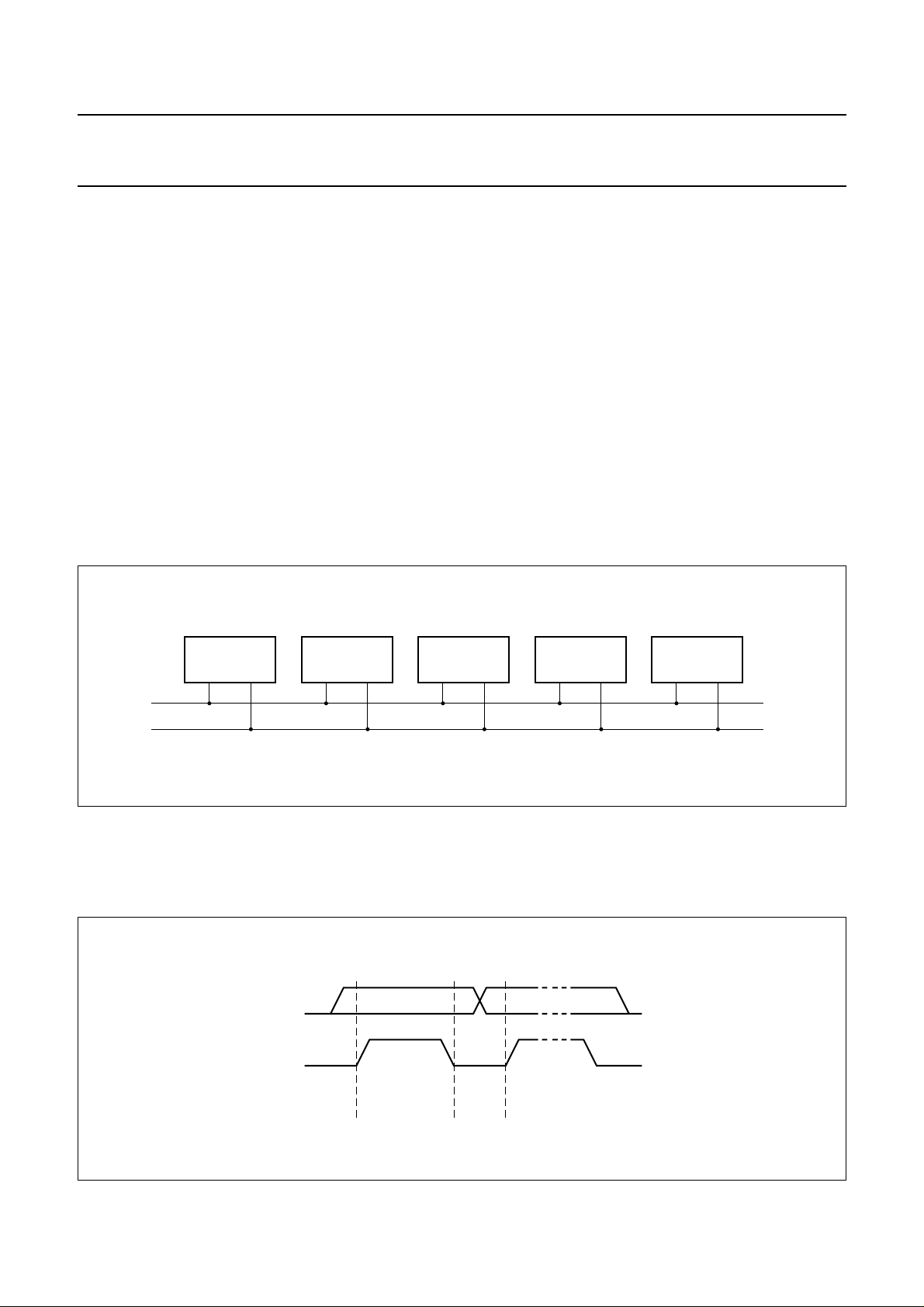

10.1.1 S

YSTEM CONFIGURATION

Definition (see Fig.20):

• Transmitter: the device that sends the data to the bus

• Receiver: the device that receives the data from the bus

• Master: the device that initiates a transfer, generates

clock signals and terminates a transfer

• Slave: the device addressed by a master

• Multi-master: more than one master can attempt to

control the bus at the same time without corrupting the

message

• Arbitration: procedure to ensure that, if more than one

master simultaneously tries to control the bus, only one

is allowed to do so and the message is not corrupted

• Synchronisation: procedure to synchronize the clock

signals of two or more devices.

SLAVE

MASTER

TRANSMITTER

MASTER

TRANSMITTER/

RECEIVER

MGA807

Fig.20 System configuration.

10.1.2 BIT TRANSFER

One data bit is transferred during each clock pulse (see

Fig.21). The data on the SDAH line must remain stable

handbook, full pagewidth

SDA

SCL

data line

stable;

data valid

Fig.21 Bit transfer.

2003 feb 10 19

during the HIGH period of the clock pulse as changes in

the data line at this time will be interpreted as a control

signal.

change

of data

allowed

MBC621

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

10.1.3 START AND STOP CONDITIONS

BothdataandclocklinesremainHIGHwhenthe bus is not

busy (see Fig.22). A HIGH-to-LOW transition of the data

handbook, full pagewidth

SDA

SCL

S

START condition

Fig.22 Definition of START and STOP conditions.

10.1.4 ACKNOWLEDGE

Each byte of 8 bits is followed by an acknowledge bit (see

Fig.23). The acknowledge bit is a HIGH signal put on the

bus by the transmitter during which time the master

generates an extra acknowledge related clock pulse.

A slave receiver which is addressed must generate an

acknowledge after the reception of each byte. Also a

master receiver must generate an acknowledge after the

reception of each byte that has been clocked out of the

line, while the clock is HIGH is defined as the START

condition (S). A LOW-to-HIGH transition of the data line

while the clock is HIGH is defined as the STOP

condition (P).

SDA

P

STOP condition

SCL

MBC622

slave transmitter. The device that acknowledges must

pull-down the SDA line during the acknowledge clock

pulse, so that the SDA line is stable LOW during the HIGH

period of the acknowledge related clock pulse (set-up and

hold times must be taken into consideration). A master

receiver must signal an end of data to the transmitter by

not generating an acknowledge on the last byte that has

been clocked out of the slave. In this event the transmitter

must leave the data line HIGH to enable the master to

generate a stop condition.

handbook, full pagewidth

DATA OUTPUT

BY TRANSMITTER

DATA OUTPUT

BY RECEIVER

SCL FROM

MASTER

S

START

condition

Fig.23 Acknowledge on the I2C-bus.

2003 feb 10 20

not acknowledge

acknowledge

acknowledgement

9821

clock pulse for

MBC602

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

R/

10.2 I2C-bus Hs-mode protocol

TheOM6208 is a slave receiver/transmitter. If data is to be

read from the device the SDAHOUT and SDAH pads must

be connected for acknowledge to be used (see Table 1,

note 6).

Hs-mode can only commence after the following

conditions.

• START condition (S)

• 8-bit master code (00001XXX)

• not-acknowledge bit (A).

The master code has two functions as shown in Figs 24

and 25, it allows arbitration and synchronization between

competing masters at F/S-mode speeds, resulting in one

winner.Also the master code indicates the beginning of an

Hs-mode transfer.

As no device is allowed to acknowledge the master code,

then a master code transmission must be followed by a

not-acknowledge (A). After this A bit, and the SCLH line

has been pulled up to a HIGH level, the active master

switches to Hs-mode and enables at tHthe current-source

pull-up circuit for the SCLH signal (see Fig.25).

The active master will then send a repeated START

condition (Sr) followed by a 7-bit slave address with a

W bit, and receives an acknowledge bit (A) from the

selected slave. After each acknowledge bit (A) or

not-acknowledge bit (A) the active master disables its

current-source pull-up circuit. The active master

re-enables its current source again when all devices have

released and the SCLH signal reaches a HIGH level. The

rising of the SCLH is done by a resistor pull-up and so is

slower, the last part of the SCLH rise time is speeded up

because the current source is enabled. Data transfer only

switches back to F/S-mode after a STOP (P) condition.

The write sequence that occurs after the Hs-mode is

selected is shown in Fig.26. The sequence is initiated with

a START (S) condition from the I2C-bus master which is

followed by the slave address. All slaves with the

corresponding address acknowledge in parallel, all the

others will ignore the I2C-bus transfer.

After an acknowledgement cycle of a write (W), one or

morecommandwordsfollowwhichdefinethestatusofthe

addressed slaves. A command word consists of a control

byte, which defines Co and D/C, plus a data byte (see

Fig.26 and Table 4).

The last control byte is tagged with a cleared most

significantbit,the continuation bit Co. Thecontrolanddata

bytes are also acknowledged by all addressed slaves on

the bus.

Table 4 Co and Sr definition

Co D/C R/W ACTION

0 −−

1 −−

− 0

− 1

Afterthelast control byte, dependingontheD/C bit setting,

a series of display data bytes or command data bytes may

follow. If the Sr bit was set to logic 1, these display bytes

are stored in the display RAM at the address specified by

the data pointer. The data pointer is automatically updated

and the data is directed to the intended OM6208 device.

If the Sr bit of the last control byte was set to logic 0, these

command bytes will be decoded and the setting of the

device will be changed according to the received

commands. The acknowledgement after each byte is

made only by the addressed OM6208. At the end of the

last control byte to be sent; only a stream of data bytes are allowed to follow; this stream

may only be terminated by a STOP or repeated START condition

another control byte will follow the data byte unless a STOP or repeated START condition

is received

0 data byte will be decoded and used to set up the device

1 data byte will return the status byte

0 data byte will be stored in the display RAM

1 RAM read back is not supported

transmission the I2C-bus master issues a STOP

condition (P) and switches back to F/S-mode, however, to

reduce the overhead of the master code, it i s possible that

a master links a number of Hs-mode transfers, separated

by repeated START conditions (Sr).

A read sequence (see Fig.27) follows after the Hs-mode is

selected. The OM6208 will immediately start to output the

requested data until a not acknowledge is transmitted by

the master. The write access should be terminated by a

repeated START condition so that the Hs-mode is not

disabled.

2003 feb 10 21

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

handbook, full pagewidth

handbook, full pagewidth

SDAH

SCLH

F/S-mode

S R/WMASTER CODE Sr SLAVE ADD.

Hs-mode (current-source for SCLH enabled)

Fig.24 Data transfer format in Hs-mode.

S

1 2 to 5

8-bit Master code 00001xxx

F/S-mode

AA A/ADATA

(n bytes + ack.)

6789

P

Hs-mode continues

SLAVE ADD.

Sr

MSC616

t

1

A

t

H

F/S mode

Sr

SDAH

SCLH

t

H

= MCS current source pull-up

= Rp resistor pull-up

7-bit SLA

16789 67891

2 to 5

R/W A

Hs-mode

Fig.25 Complete data transfer in Hs-mode.

2003 feb 10 22

n × (8-bit DATA + A/A)

2 to 5

Sr P

If P then

F/S mode

If Sr (dotted lines)

then Hs-mode

t

FS

MSC618

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

handbook, full pagewidth

Sr01111

slave address

handbook, full pagewidth

acknowledge

from OM6208

S

S

0A

A

A

0

1

R/W

1

D/C

from OM6208

control byte

acknowledge

A data byte data byte

2n ≥ 0 bytes

acknowledge

from OM6208

control byte

0A AP

A

D/C

CoCo

1 byte

Fig.26 Master transmits in Hs-mode to slave receiver; write mode.

NOT acknowledgement

from Master

P

STOP condition

MGW831

Sr01111

slave address

acknowledgement

from OM6208

S

S

A

1

A

0

(1)

status information A

1A

R/W

acknowledge

from OM6208

MSB . . . . . . . . . . . LSB

acknowledge

from OM6208

n ≥ 0 bytes

MGW830

(1) These bits are set by inputs ID3/SA0 and ID4/SA1.

Fig.27 Master receives from slave transmitter (status register is read); read mode.

10.3 Command decoder

The command decoder identifies command words that

arrive on the I2C-bus:

• Pairs of bytes

– firstbytedetermineswhether information is display or

instruction data

– 2nd byte contains information.

• Stream of information bytes after Co = 0; display or

instruction data depending on last D/C.

2003 feb 10 23

Themost-significantbitofa control byte is the continuation

bit Co. If this bit is logic 1, it indicates that only one byte,

either command or RAM-data, will follow. If this bit is

logic 0, it indicates that a series of bytes, either command

or RAM-data, may follow. The DB6 bit of a control byte is

the RAM-data/command bit D/C. When this bit is logic 1, it

indicates that a RAM-data byte will be transferred next.

If the bit is logic 0, it indicates that a command byte will be

transferred next.

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

10.4 Read mode

I2C-bus read mode operates differently from the other

interfaces. Two different status bytes can be read back

and are selected by first sending a ‘read’ instruction.

Sending the instruction to read ID1, ID2 and VM will select

the status byte shown in Table 5.

Sending the instruction to read back the temperature

sensor will select the status byte shown in Table 6.

A repeated START or STOP and START must then be

generated followed by the slave address with the R/W bit

set to read in order to read the status register.

Table 5 Read status byte ID1, ID2 and VM

D7 (MSB) D6 D5 D4 D3 D2 D1 D0 (LSB)

(1)

x

(1)

x

(1)

x

(1)

x

(1)

x

VM ID2

(2)

ID1

Notes

1. x = undefined.

2

2. Bits ID3 and ID4 are not available for I

C-bus because they are used to make up the two LSBs of the slave address.

Table 6 Read temperature sensor

D7 (MSB) D6 D5 D4 D3 D2 D1 D0 (LSB)

(1)

x

TD[6] TD[5] TD[4] TD[3] TD[2] TD[1] TD[0]

Note

1. x = undefined.

(2)

2003 feb 10 24

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

11 INSTRUCTIONS

The OM6208 may be interfaced via 3-line or 4-line Serial

PeripheralInterface (SPI), 3-line serialinterfaceor I2C-bus

interface. In all cases, processing of instructions is

asynchronous and does not require the internal/external

oscillator to be running.

Data transmission to OM6208 may be of two types, those

that define the operating mode of the device (commands)

and those that fill display RAM (data). Table 7 lists all

commands that are recognised by OM6208.

The Most Significant Bit (MSB) is sent first. The mode in

which the D/C bit is defined varies with the type of serial

D/C bit definitions:

• With 4-line SPI interface selected, the D/C bit is

implemented as hard-wired input at pad D/C

• With 3-line SPI interface selected, the D/C bit is not

implemented and all transmission are commands by

default unless preceded by the Display data length

command

• With3-lineserial and I2C-businterfaceselected, the D/C

bit is implemented through the interface protocol.

Commands can consist of one byte (single-byte) and two

bytes (double-byte). Unless otherwise specified,

commands may be executed in any order.

interface that is used.

Table 7 Instruction set

Instructions not expressly defined in this table and reserved instructions must not be used.

COMMAND BYTE

COMMAND NAME D/

C

(MSB) D6 D5 D4 D3 D2 D1

D

D

D

D

D

Write data 1 D

Horizontal addressing 0 0 0 0 0 X

Horizontal addressing 0 0 0 0 1 δ

7

6

5

4

3

3

(1)

Power control 0 0 0101PCδ

D

2

1

X

X

X

2

1

X

6

5

(1)

(LSB)

FUNCTION DESCRIPTION

D0

D

RAM data

0

X0set X address; lower 4 bits

X4set X address; upper 3 bits

(1)

δ

charge pump on/off

Charge pump control 0 0 011110 1set multiplication factor

(1)

0 δ

Set V

Set V

PR

PR

00 0100V

01 00V

Set bias 0 0 0110BS

(1)

(1)

(1)

(1)

δ

δ

δ

δ

pr4Vpr3Vpr2Vpr1

(1)

δ

pr7Vpr6

2BS1

S

1

S

0

V

write Vpr register

pr5

V

write Vpr register

pr0

BS0set bias

Display mode 0 1 010010DALall on/normal display

Display mode 0 1 010011 Enormal/inverse display

Display mode 0 1 010111DONdisplay ON/OFF

Data order 0 1 010100DORswap RAM MSB/LSB order

RAM addressing 0 1 010101 Vvertical or horizontal mode

Vertical addressing 0 1 0 1 1 Y

Vertical addressing 0 0 011111Y

Vertical mirroring 0 1 1 0 0 MY δ

ID read 0 1 101101 0identification: ID1

ID read 0 1 101101 1identification: ID2

ID read 0 1 101110 0identification: ID3

ID read 0 1 101110 1identification: ID4

Y

3

(1)

Y

2

δ

Y0set Yaddress

1

4

(1)

(1)

δ

set Yaddress

mirror Y

(2)(3)

(2)(3)

(2)

(2)

Temperature sense 0 1 101111 0temperature read back

VM read 0 1 101111 1voltage monitor

(3)(4)

Row control 0 1 110000BRSswap the bottom rows

2003 feb 10 25

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

COMMAND BYTE

COMMAND NAME D/C

(MSB) D6 D5 D4 D3 D2 D1

(LSB)

Software reset 0 1 110001 0internal reset

NOP 01 110001 1no operation

Display data length 0 1 110100 0display data length for 3-line

Temperature

compensation

Temperature

compensation

Frame frequency

range, oscillator tune

and mode

Temperature

0D

00 011100 0setTCslopes A and B (SLA

(1)

0 δ

00 011100 1setTC slopes C and D

(1)

0 δ

00 011110 0frame frequency range and

0 MOD T

01 110101TCEenable/disable temperature

D

7

6

D

5

SLB2SLB1SLB0δ

SLD2SLD1SLD0δ

T

2

1

D

4

T

0

D

D

3

2

(1)

SLA2SLA1SLA

(1)

SLC2SLC1SLC

(1)

δ

FR2FR1FR

D

1

compensation enable

Oscillator selection 0 0 011101ECexternal oscillator

OTP programming 0 1 11100OSECALMMenter calibration mode and

LOAD0 01 101100 0write0 to shift register

LOAD1 01 101100 1write1 to shift register

Select factory

01 110110SFDenable/disable defaults

defaults

N-line inversion and

super-frame inversion

01 010110 1N-line inversion and

0FINL

6NL5

00 1δ

01 01000δ

NL4NL3NL2NL

(1)

(1)

δ

(1)

δ

NL

1

(1)

δ

(1)

δ

(1)

01 010110 0reserved

(1)

01 1010δ

(1)

δ

01 110100 1reserved

01 11001δ

(1)

01 110111δ

(1)

(1)

(1)

δ

01 11101δ

01 1111δ

FUNCTION DESCRIPTION

D0

SPI

D

0

and SLB)

0

(SLC and SLD)

0

oscillator tune and working

0

mode

compensation

control programming

super-frame Inversion

0

(1)

δ

reserved

(1)

δ

reserved

(1)

δ

reserved

(1)

δ

reserved

(1)

reserved

(1)

δ

reserved for testing

(1)

δ

reserved for testing

Notes

1. δ = don’t care.

2. ID1, ID2, ID3, ID4 and VM are read back via interface as described in Section 9.2.3. Reading back with I2C-bus

interface is possible for temperature, ID1, ID2 and VM, as described in Section 10.4.

3. ID1 will always return to logic 0; ID2 will always return to logic 1. The VM bit is set to logic 1 when the charge pump

is running and logic 0 when the charge pump is not running.

4. If the Factory Defaults bit (MMFD) has been programmed to 1, then the SFD instruction is ignored and the device

will always use the OTP default data.

2003 feb 10 26

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

11.1 Description of command bits

Table 8 Bit descriptions

BIT 0 1 RESET STATE

DON display off display on 0

E normal display inverse video mode 0

DAL normal display all pixel on 1

MY no Y mirroring Y mirroring 0

PC charge pump off charge pump on 0

DOR normal data order MSB/LSB transposed for RAM data 0

V horizontal addressing vertical addressing 0

BRS bottom rows are not mirrored bottom rows are mirrored 0

EC internal oscillator is selected external clock to be used 0

(2)

(1)

(1)

0

0

0

(2)

(2)

(2)

(2)

(2)

(2)

(2)(3)

(2)(3)

(2)

(2)

(2)

CALMM exit OTP calibration mode enter OTP calibration mode

TCE disable temperature compensation enable temperature compensation 1

OSE disable OTP programmed voltage enable OTP programmed voltage

SFD use interface programmed data use OTP programmed data

MOD grey-scale mode is selected black-and-white mode is selected 0

SLA[2:0] select slope for segment A 000

SLB[2:0] select slope for segment B 000

SLC[2:0] select slope for segment C 000

SLD[2:0] select slope for segment D 000

X[6:0] sets X address (column) for writing in the RAM 0000000

Y[4:0] sets Yaddress (bank) for writing in the RAM 00000

S[1:0] charge pump multiplication factor (see Table 10) 0000

NL[6:0] sets N-line inversion (see Table 18) 0001101

FR[2:0] sets frame frequency range (see Table 11) 001

T[2:0] oscillator tune; sets frame frequency within a range (see Table 11) 110

D[7:0] display data length for 3-line SPI interface 00000000

VPR[7:0] V

register 00000000

PR

BS[2:0] bias setting level (see Table 13) 000

FI super-frame inversion 0

Notes

1. Calibration mode may not be entered if the SEAL bit has been set. Programming is only possible when in calibration

mode.

2. Thesevaluescanbe set by the module maker. If the factory defaults OTP bit (MMFD) has been set then these values

cannot be changed via the interface. Otherwise, the OTP data will only be used if bit SFD is set to 1.

3. FR[2:0] = 001 and T[2:0] = 110 gives 150 Hz as default frame frequency.

2003 feb 10 27

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

Table 9 Display and power mode bits DON, DAL and E

(1)

DON DAL

00X

(2)

E

(3)

display off; all row and column

DESCRIPTION

outputs at VSS; oscillator on;

HV generator enabled

(3)

01X

Power-downmode;displayoff;

all row and column outputs at

VSS; oscillator off;

HV generator disabled

1 0 0 normal display mode

1 0 1 inverse display mode

11X

(3)

all pixels on

Notes

1. The DAL bit has priority over the

E bit.

2. Refer also to Table 17.

3. X = don’t care.

Table 10 Multiplication settings for charge pump

S1 S0

VOLTAGE

MULTIPLIER

004×

015×

106×

117×

Table 11 Frame frequencies for f

FR2 FR1 FR0

DIVISION

RATIO

= 400 kHz

osc

f

frame

(Hz)

0 0 0 2448 163.4

0 0 1 3265 122.5

0 1 0 4082 98.0

0 1 1 4896 81.7

1 0 0 5714 70.0

1 0 1 7340 54.5

1 1 0 8968 44.6

1 1 1 11428 35.0

Oscillator tuning is controlled by the parameter T[2:0]. As

a result of oscillator tuning, f

is increased by

OSC

approximately 4% per step according to the equation

f

OSC

400 kHz 1 0.04 T×+()×=

(1)

where T is the decimal value of T[2:0].

Example. For the default values given in Table 8

(i.e. FR[2:0] = 001 and T[2:0] = 110) the selected frame

frequency is 122.5 Hz × (1 + 6 × 0.04) = 151.9 Hz.

Equation (1) shows the typical value of the oscillator

frequency. The accuracy of this parameter is defined in

Chapter 15. The frame frequency accuracy results directly

from the oscillator accuracy.

11.2 Frame frequency setting and oscillator tuning

Grey-scale mode and black-and-white mode require

different frame frequencies. The appropriate frame

frequency (f

(f

) using a presettable divider as shown in the equation

osc

) is derived from the oscillator frequency

frame

f

f

=

frame

OSC

--------------------------------division ratio

There are eight possible divider settings and these are

selected by the parameter FR[2:0], see Table 11.

2003 feb 10 28

11.3 Initialization

Immediately following power-on, all internal registers and

the RAM content are undefined. A reset pulse must be

applied to the

RES pad.

Reset is accomplished by applying an external reset pulse

(active LOW) to the RES input. When reset occurs within

the specified time, all internal registers are reset, however

the RAM remains undefined. The state after reset is

described in Section 11.4.

At power-on, the RES input must be ≤0.3V

reachesV

after V

DD1

pulse can be applied when V

(orhigher)within the maximum timet

DD(min)

going HIGH (see Fig.37). Alternatively a reset

is stable.

DD1

DD1

when V

DD1

VHRL

A reset can also be made by sending a reset command.

This command can be used during normal operation but

not to initialize the chip after power-on.

After power-off, the RES input must not be HIGH when

V

is not HIGH.

DD1

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

11.4 Reset function

After reset, the LCD driver is in Power-down mode, the

RAM is undefined and the internal registers have the

status shown in Table 8.

11.5 Power-down mode

In the Power-down mode:

• All LCD outputs (row and column outputs) are at V

SS

(display off)

• Bias generator and V

external V

supply can be applied or disconnected

LCD

generator are switched off;

LCD

• Oscillator is off (an external clock is possible)

• RAM contents are unchanged; RAM data can be written

• V

is discharged to VSS.

LCD

Power-down mode is active when the display is off

(DON = 0) and all the pixels are on (DAL = 1).

11.6 Display Control

The bits DON, E and DAL select the display mode (see

Table 9).

11.6.1 HORIZONTAL MIRRORING

When the MX input is at logic 0, the display RAM is written

from left to right (X = 0 is on the left side).

11.7 Set Yaddress of RAM

Y[4:0] defines the Y address of the display RAM.

Table 12 Yaddress range

Y4 Y3 Y2 Y1 Y0 DISPLAY RAM

0 0 0 0 0 bank 0

0 0 0 0 1 bank 1

0 0 0 1 0 bank 2

0 0 0 1 1 bank 3

0 0 1 0 0 bank 4

0 0 1 0 1 bank 5

0 0 1 1 0 bank 6

0 0 1 1 1 bank 7

0 1 0 0 0 bank 8

0 1 0 0 1 bank 9

0 1 0 1 0 bank 10

0 1 0 1 1 bank 11

0 1 1 0 0 bank 12

0 1 1 0 1 bank 13

0 1 1 1 0 bank 14

0 1 1 1 1 bank 15

1 0 0 0 1 bank 16

When the MX input is set to 1, the display RAM is written

from right to left (X = 0 is on the right side).

The MX input value has an impact on the way the RAM is

written: if a horizontal mirroring of the display is desired,

the RAM must be rewritten after changing the MX pad

value.

11.6.2 VERTICAL MIRRORING

When the MY bit is set to logic 1, the display is mirrored

vertically.

Achangeofthisbithasanimmediateeffect on the display,

it is not necessary to rewrite RAM for the effect to take

place.

11.8 Set X address of RAM

The X address points to the columns. The range of X is

0 to 95.

11.9 Bias levels

TheOM6208is a grey-scale driver able toprovidedifferent

bias voltage levels for rows and columns. The row voltage

values are V

LCD,VSS

and VC, generated using the resistor

chain shown in Fig.28.

The five levels used to drive the columns are shown in

Fig.28. These are V2L, V1L,VC, V1H and V2H, all of which

depend on the value of alpha. Table 13 shows all possible

combinations of alpha settable by programming the

BS[2:0] bits.

2003 feb 10 29

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

handbook, halfpage

F

α is in the range 0.0 to 1.05.

Table 13 Bias setting levels for p = 4

BS2 BS1 BS0 F/G α a

0 0 0 1.000 0.00 4.00

0 0 1 1.075 0.15 4.30

0 1 0 1.150 0.30 4.60

0 1 1 1.225 0.45 4.90

1 0 0 1.300 0.60 5.20

1 0 1 1.375 0.75 5.50

1 1 0 1.450 0.90 5.80

1 1 1 1.525 1.05 6.10

V

LCD

αR

V

2H

R

G

R

R

R

αR

V

1H

V

C

V

1L

V

2L

VSS = V

Fig.28 Bias system.

Because the voltage level of the row depends on the

programmed bias level, it can be seen that

The situation where F = G occurs only when BS[2:0] is

zero and alpha is zero. In this case αR = 0 and G = F;

therefore V

internal buffers are no longer needed and therefore are

switched off to reduce power consumption.

The relationship between F and G is defined by the

parameter a (indicated in Table 13) and p as follows

= V

row(max)

row(min)

MGW832

2H=VLCD

FG≥

and V2L=VSS, also two of the

F

a

=

----

-- -

G

p

Each of the eight possible values of alpha results in a

different set of five values for the column voltages.

Bias level F (see Fig.28) is half of the maximum row

voltage level as shown by the equation

V

LCD

F

=

------------ 2

Figure 28 also shows that G is used to define the

maximum column voltage level related to the V

C

level.

2003 feb 10 30

It can be seen from Fig.28 that

F

a

-- p

α 2+()

----------------- 2

---G

α

1

+== =

--2

or

a

α

--2

1+

p⋅= α

a

1–

-- -

p

2⋅=

The BS[2:0] bias bits can be selected by a command and

also can be programmed by OTP.

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

The relationship between the parameters F, p, a and N

(number of rows of the display) and the V

V

voltage values according to the typical LCD

off(rms)

on(rms)

and

properties of the pixel are shown in equations (2) and (3).

pa2N2a++()⋅

V

on(rms)

V

off(rms)

F

------------------------------------------ -⋅=

--a

pa2N2a–+()⋅

F

------------------------------------------⋅=

--a

N

N

(2)

(3)

11.10 LCD drive voltage

11.10.1 LCD

V

may be supplied externally or generated internally by

LCD

DRIVE VOLTAGE GENERATION

the on-chip capacitive charge pump. OM6208 features

on-chip capacitors resulting in a minimum of external

components required for operation (see Chapter 16).

The‘power control’ instruction may be used to switch V

LCD

generation on or off. The charge pump control instruction

may be used to select the required voltage multiplication

factor. The ‘set VPR’ instruction is used for programming

the LCD drive voltage V

The generation of V

This shows all factors that effect V

LCD.

in OM6208 is illustrated in Fig.29.

LCD

generation,

LCD

including the 6 bits of MMVOPCAL (from OTP) and the

7 bits resulting from the temperature compensation

mechanism. Equations summarizing all factors are

V

VPRMMVOPCAL V

OP

++=

T

(4)

Table 14 Parameters of V

LCD

SYMBOL VALUE UNIT

b 0.03 V

a3V

CAUTION

As the programming range for the internally generated

V

allows values above the maximum allowed V

LCD

(9 V), the user has to ensure, while setting the V

LCD

PR

register and selecting the temperature compensation,

that under all conditions and including all tolerances

V

remains below 9.0 V.

LCD

Also, because the programming range for the internally

generated V

allowed V

allows values below the minimum

LCD

(5 V), the user has to ensure, while setting

LCD

the VPR register and selecting the temperature

compensation, that under all conditions and including all

tolerances V

remains above 5.0 V.

LCD

and

LCD

VOPb⋅ a+=

(5)

V

Where:

[7:0] is set in the instruction decoder and is the

V

PR

programmed VPRregister value as an unsigned number

MMVOPCAL[5:0] is the value of the offset stored in the

OTP cells in twos complement format

VT[7:0] in twos complement format comes from the

temperature compensation block (see Table 16)

a and b are fixed constant values (see Table 14).

2003 feb 10 31

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

handbook, full pagewidth

TEMPERATURE

MEASUREMENT

Fig.29 V

measured temperature slopes

B C D

A

V

T

TD

7

−40

generation including the temperature compensation and OTP calibration.

LCD

0

TEMPERATURE COMPENSATION

+85

T (°C)

[

]

7:0

V

PR

V

8

T

]

8

8

V

OP

abMMVOPCAL[5:0

MGW833

V

LCD

handbook, full pagewidth

V

LCD

b

a

00 01 02

VPR[7:0] programming: 00 to FF (HEX).

Assuming MMVOPCAL = 0 and VT=0V.

03 04 05 06

Fig.30 V

. . . . . . FD FE FF

programming of OM6208 shown as plots of equations (4) and (5).

LCD

MGT847

V

OP

2003 feb 10 32

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

11.10.2 TEMPERATURE MEASUREMENT

The temperature measurement is repeated every

10 seconds. The measured value is provided as a 7-bit

digital value TD[6:0] which can be read back via the

interface. The temperature can be determined from

TD[6:0] using the equation

T 1.875 TD× 40–()°C=

(6)

11.10.3 TEMPERATURE COMPENSATION

Due to the temperature dependency of the liquid crystal’s

viscosity,the LCD controlling voltage V

mayhave to be

LCD

adjusted at different temperatures to maintain optimal

contrast.

Internal temperature compensation may be enabled via

the ‘temperature compensation enable’ instruction. When

the internal temperature compensation is applied (TCE bit

is set to 1) then according to Equation (4) the V

LCD

depends also on VT (the temperature compensation

component defined in Table 16), otherwise VT is

considered to be 0 V.

After the reset, the V

is fixed because the VPR is a

LCD

register that is reset to zero. The MMVOPCAL is also set

to zero because this comes from the registers of OTP that

are not refreshed yet, also VTis evaluated after the reset

because the temperature measurement block supplies a

TD value that is the default value stored in the register

after the reset.

The four temperature coefficients MA, MB, MC and MD

correspond to four equally spaced temperature regions.

Each coefficient can be selected from a choice of eight

different slopes, or multiplication factors. Each one of

these coefficients may be independently selected by the

user via the ‘temperature compensation enable’

instruction. The default for each slope register can be

stored in OTP.

Table 15 Temperature coefficients

Slopes of V

are calculated from equations (4), (5), (6)

LCD

and Table 16.

SLA, SLB, SLC

and SLD

MA, MB, MC

and MD

SLOPE

(mV/K)

111 3.00 −48

110 2.00 −32

101 1.25 −20

100 1.00 −16

011 0.75 −12

010 0.50 −8

001 0.25 −4

000 0.00 0

Temperature compensation is implemented by adding an

offset V

to the VPR value (additionally to the OTP

T

calibration offset MMVOPCAL).

The final result for V

calculation is an 8-bit positive

LCD

number as shown in equations (4) and (5). Care must be

taken by the user to ensure that the ranges of VPR,

MMVOPCAL and VT do not cause clipping and hence

undesired results. The adder stages will not permit

overflow or underflow and will clamp results to either end

of the range.

The temperature read-out generates a 7-bit result,

TD[6:0]. For temperatures below −40 °C, the value of TD

is zero. For temperatures above 79 °C, the value of TD is

higher than 63, but for VT calibration the value TD = 63 is

used.

The offset value VTmay be calculated from Table 16. The

effect on V

can be calculated by multiplying the offset

LCD

value with the value of b (from Table 14).

For example, if T = −10 °C, TD = 16 and MB = 1.25 then

V

LCDoffset

=30mV×(32 − 16) × 1.25 = 600 mV.

Table 16 Temperature compensation equations

TEMPERATURE RANGE (°C) TD RANGE EQUATION

−40 to −11 0 to 15 V

−10 to +19 16 to 31 V

+20 to +49 32 to 47 V

+50 to +79 48 to 63 V

= (16 × MB) + MA × (16 − TD)

T

= (32 − TD) × MB

T

= −(TD − 32) × MC

T

= −(16 × MC)+MD×(TD − 48)

T

2003 feb 10 33

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

handbook, full pagewidth

V

LCD

ACBD

Fig.31 Example of segmented temperature coefficients.

11.11 Grey-scale mode and black-and-white mode

It is possible to set via command the working mode of the

OM6208. This is by setting the MOD bit of the ‘frame

frequency’ instruction, oscillator tune and mode.

By default, the MOD bit is set to logic 0 and grey-scale

mode is selected. In that mode, grey-scales are generated

using Frame Rate Control (FRC). Three frames together

form a super-frame. The frame frequency is adjustable but

all three frames have the same duration. A grey-scale is

generated by selecting either 0, 1, 2 or all 3 frames (see

Table 17).

If the MOD bit is set to logic 1 black-and-white mode is

selected, meaning that only black-and-white levels are

generated and only one frame type is sent to the display.

Thus only the MSBs stored in the RAM are used for all

three frames. The LSBs are ignored. Thus the way the

data is stored in the RAM is the same as for grey-scale.

As all frames are identical the frame frequency may be

reduced (see Table 11).

MGW834

20 50 80−40 −10

T (°C)

Table 17 Grey-scale levels with FRC

GREY-SCALE

GS[1:0] SUPER-FRAME

(1)

LEVELS

Normal mode (E = 0)

0 0 000 white

0 1 001 light grey

1 0 110 dark grey

1 1 111 black

Inverse mode (E = 1)

0 0 111 black

0 1 110 dark grey

1 0 001 light grey

1 1 000 white

Note

1. The first and second frames in each super-frame are

related to the MSB of GS[1:0] (GS = 11); the third

frame is related to the LSB (GS = 00).

2003 feb 10 34

11.12 N-line inversion and frame inversion

N-line inversion can be set from 0 to 127 as shown in

Table 18.

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

Table 18 N-line inversion

INVERSION AFTER NL

NL

6

NL

5

NL

4

NL

3

NL

2

NL

1

FI

0

0-line inversion 0 0 0 0 0 0 0 0

1-line inversion 0 0 0 0 0 0 1 0

2-line inversion 0 0 0 0 0 1 0 0

3-line inversion 0 0 0 0 0 1 1 0

4-line inversion 0 0 0 0 1 0 0 0

5-line inversion 0 0 0 0 1 0 1 0

6-line inversion 0 0 0 0 1 1 0 0

7-line inversion 0 0 0 0 1 1 1 0

8-line inversion 0 0 0 1 0 0 0 0

: ::::::::

66-line inversion 1 0 0 0 0 1 0 0

67-line inversion 1 0 0 0 0 1 1 0

68-line inversion 1 0 0 0 1 0 0 0

: ::::::::

127-line inversion 0 1 0 0 0 0 0 0

0 only super-frame inversion 0 0 0 0 0 0 0 1

1-line inversion and super-frame inversion 0 0 0 0 0 0 1 1

2-line inversion and super-frame inversion 0 0 0 0 0 1 0 1

3-line inversion and super-frame inversion 0 0 0 0 0 1 1 1

4-line inversion and super-frame inversion 0 0 0 0 1 0 0 1

5-line inversion and super-frame inversion 0 0 0 0 1 0 1 1

6-line inversion and super-frame inversion 0 0 0 0 1 1 0 1

7-line inversion and super-frame inversion 0 0 0 0 1 1 1 1

8-line inversion and super-frame inversion 0 0 0 1 0 0 0 1

: ::::::::

66-line inversion and super-frame inversion 1 0 0 0 0 1 0 1

67-line inversion and super-frame inversion 1 0 0 0 0 1 1 1

68-line inversion and super-frame inversion 1 0 0 0 1 0 0 1

: ::::::::

127-line inversion and super-frame inversion 1 1 1 1 1 1 1 1

Notes

1. In grey-scale mode the super-frame inversion is performed if bit FI in the ‘N-line inversion and super-frame inversion’

instruction is set to logic 1. In black-and-white mode, the super-frame inversion continues in groups of three frames.

2. NL[6:0] may be set in the range 0 to 127. If NL = 0, then no line inversion is performed; if NL = MUX rate = 68 then

N-line inversion is equal to frame inversion.

3. With N-line inversion the output signal polarity changes every N row pulse periods (with p = 4 this means inversion

occurs after every 4 × NL rows of the display).

4. If after a super-frame FI = 1 and there is an inversion due to an N-line inversion, this inversion occurs only once.

2003 feb 10 35

Philips Semiconductors Product specification

65 x 96 pixels matrix grey-scale LCD driver OM6208

SUB

FRAME 3

SUB

FRAME 2

SUB

FRAME 1

SUB

FRAME 0

SUB

FRAME 3

SUB

FRAME 2

SUPER-FRAME 1

SUB

FRAME 1

SUB

FRAME 0

SUB

FRAME 3

SUB

FRAME 2

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

The example in Table 19 shows the first super-frame with the settings NL = 3, MUX = 20 and p = 4 applied; the super-frame contains three frames. The

next super-frame will be a repeat of the first super-frame if bit FI is set to logic 0 (no super-frame inversion), or will start with the first frame having the

opposite sign if bit FI is at logic 1 (super-frame inversion) and the N-line inversion counter will also restart.

2003 feb 10 36

FRAME 1 FRAME 2 FRAME 3

SUB

FRAME 1

−−+++−−−+++−

−−+++−−−+++−

−−+++−−−+++−

−−+++−−−+++−

−+++−−−+++−−

−+++−−−+++−−

−+++−−−+++−−

−+++−−−+++−−

+++−−−+++−−−

+++−−−+++−−−

+++−−−+++−−−

SUB

FRAME 0

+ −−−+++−−−++

Super-frame inversion requires that the state of the previous super-frame is remembered, i.e., if the previous super-frame started ‘+’, then the next

super-frame must start ‘−’. This has priority over inversions triggered by the counter, so that if the counter triggers an inversion at a super-frame