Philips N74F195N, N74F195D, N74F195AD, N74F195AN Datasheet

74F195A

4-bit parallel-access shift register

Product specification

IC15 Data Handbook

1996 Mar 12

INTEGRATED CIRCUITS

Philips Semiconductors Product specification

74F195A4-bit parallel-access shift register

2

1996 Mar 12 853-0024 16555

FEA TURES

•Shift right and parallel load capability

•J – K (D) inputs to first stage

•Complement output from last stage

•Asynchronous Master Reset

•Diode inputs

DESCRIPTION

The 74F195A is a 4-Bit Parallel Access Shift Register and its

functional characteristics are indicated in the Logic Diagram and

Function Table. This device is useful in a variety of shifting, counting

and storage applications. It performs serial, parallel, serial to

parallel, or parallel to serial data transfers at very high speeds.

The 74F195A operates in two primary modes: shift right (Q0→Q1)

and parallel load, which are controlled by the state of the Parallel

Enable (PE

) input. Serial data enters the first flip-flop (Q0) via the J

and K

inputs when the PE input is High, and is shifted one bit in the

direction Q0→Q1→Q2→Q3 following each Low-to-High clock

transition.

The J and K

inputs provide the flexibility of the J-K type input for

special applications, and by tying the two together the simple D-type

input is made for general applications.

The device appears as four common clocked D flip-flops when the

PE

input is Low. After the Low-to-High clock transition, data on the

parallel inputs (D0–D3) is transferred to the respective Q0–Q3

outputs. Shift left operation (Q3–Q2) can be achieved by tying the

Qn outputs to the Dn-1 inputs and holding the PE

input Low.

All parallel and serial data transfers are synchronous, occurring after

each Low-to-High clock transition. The 74F195A utilizes

edge-triggering, therefore there is no restriction on the activity of the

J, K

, Dn, and PE inputs for logic operation, other than the set-up and

hold time requirements.

A Low on the asynchronous Master Reset (MR

) input sets all Q

outputs Low, independent of any other input condition.

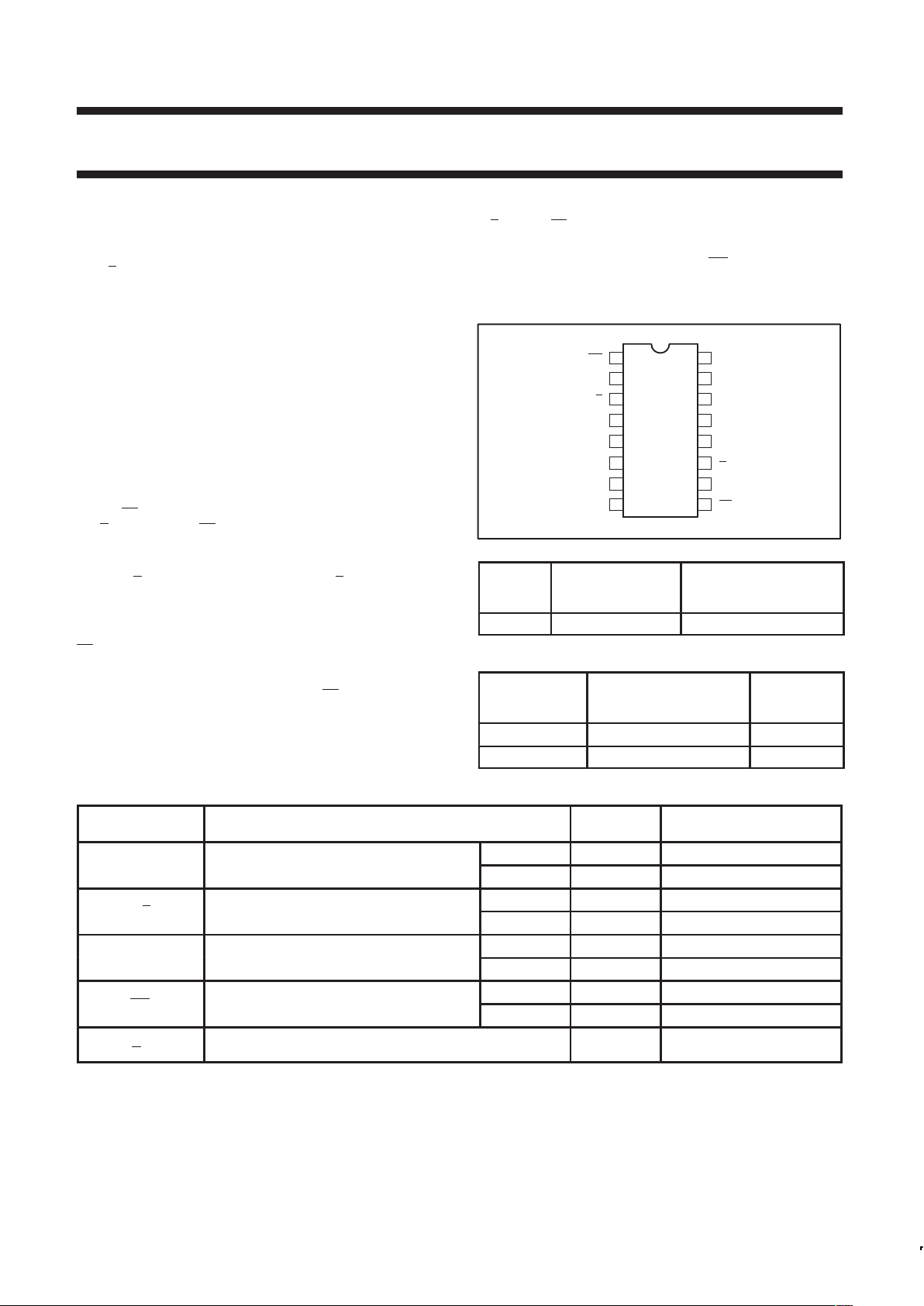

PIN CONFIGURATION

16

15

14

13

12

11

107

6

5

4

3

2

1

V

CC

Q3

CP

Q3

Q2

Q0

Q1

MR

J

D3

D0

D1

D2

98GND PE

SF00757

K

TYPE TYPICAL f

MAX

TYPICAL

SUPPLY CURRENT

(TOTAL)

74F195A 180MHz 40mA

ORDERING INFORMATION

DESCRIPTION

COMMERCIAL RANGE

VCC = 5V ±10%,

T

amb

= 0°C to +70°C

PKG. DWG. #

16-pin plastic DIP N74F195AN SOT 38-4

16-pin plastic SO N74F195AD SOT 109-1

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION

74F (U.L.)

HIGH/LOW

LOAD VALUE HIGH/LOW

p

74F195 1.0/0.033 20µA/20µA

D0–D3

Data inputs

74F195A 1.0/1.0 20µA/0.6mA

p

p

74F195 1.0/0.033 20µA/20µA

J, K

J-K or D type serial inputs

74F195A 1.0/1.0 20µA/0.6mA

p

74F195 1.0/0.033 20µA/20µA

CP

Clock Pulse input (active rising edge)

74F195A 1.0/1.0 20µA/0.6mA

p

74F195 2.0/0.066 40µA/40µA

MR

Master Reset input (active Low)

74F195A 1.0/1.0 20µA/0.6mA

Q0–Q3,

Q3

Data outputs 50/33 1.0mA/20mA

NOTE:

One (1.0) FAST unit load is defined as: 20µA in the High state and 0.6mA in the Low state.

Philips Semiconductors Product specification

74F195A4-bit parallel-access shift register

1996 Mar 12

3

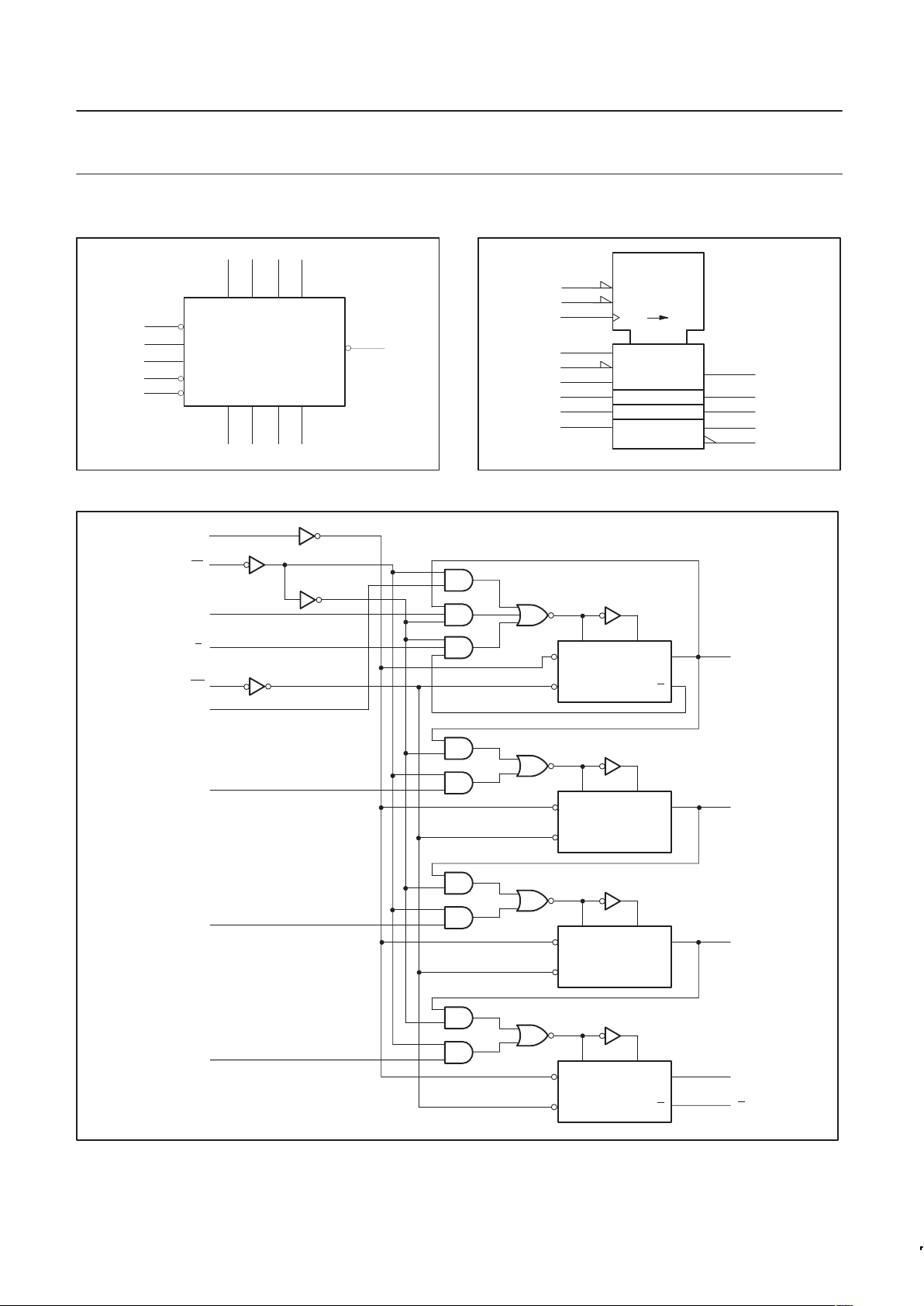

LOGIC SYMBOL

Q0 Q1

Q2 Q3

15 14

13 12

V

CC

= Pin 16

GND = Pin 8

9

2

10

3

PE

J

CP

K

D1 D2

56

SF00758

D3D0

4

7

1MR

11Q3

IEC/IEEE SYMBOL

SF00759

7

3

4

5

6

2

10

9

M1

SRG4

C2/1

1, 2J

1, 2K

1, 2D

15

13

1

R

14

1, 2D

12

11

LOGIC DIAGRAM

CP

10

PE

9

J

2

S

CP

R

Q0

15

SF00760

VCC = Pin 16

GND = Pin 8

R

D

Q

Q

3

K

MR

D0

D1

D2

D3

S

CP

R

Q1

14

R

D

Q

S

CP

R

Q2

13

R

D

Q

S

CP

R

Q3

12

R

D

Q

Q

Q3

11

1

4

5

6

7

Loading...

Loading...