Page 1

K9K2G08U0A

K9K2G08R0A

K9K2G08X0A

FLASH MEMORY

INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS,

AND IS SUBJECT TO CHANGE WITHOUT NOTICE.

NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE,

EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE,

TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL

INFORMATION IN THIS DOCUMENT IS PROVIDED

ON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.

1. For updates or additional information about Samsung products, contact your nearest Samsung office.

2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar

applications where Product failure could result in loss of life or personal or physical harm, or any military or

defense application, or any governmental procurement to which special terms or provisions may apply.

* Samsung Electronics reserves the right to change products or specification without notice.

1

Page 2

K9K2G08U0A

K9K2G08R0A

Document Title

256M x 8 Bit NAND Flash Memory

Revision History

FLASH MEMORY

Revision No

0.0

0.1

0.2

0.3

0.4

1.0

History

1. Initial issue

1. Technical note is changed

2. Notes of AC timing characteristics are added

3. The description of Copy-back program is changed

4. TSOP package is deleted

access time : 23ns->35ns (p.9)

1. CE

1. The value of tREA is changed. (18ns->20ns)

2. EDO mode is added.

1. The flow chart to creat the initial invalid block table is changed.

1. 1.8V FBGA spec is merged

2. 3.3V FBGA package is added

3. FBGA package size is changed to 9.5 x 12

4. Leaded part is deleted

Draft Date

May. 31. 2004

Oct. 25. 2004

Feb. 14. 2005

May 4 2005

May 6 2005

Feb. 1 2006

Remark

Advance

Preliminary

The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right

to change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions about device. If you have

any questions, please contact the SAMSUNG branch office near your office.

2

Page 3

K9K2G08U0A

K9K2G08R0A

FLASH MEMORY

256M x 8 Bit NAND Flash Memory

PRODUCT LIST

Part Number Vcc Range Organization PKG Type

K9K2G08U0A-F 2.7 ~ 3.6V X8 WSOP1

K9K2G08X0A-J 1.65 ~ 1.95V X8 FBGA

FEATURES

• Voltage Supply

- 2.7 V ~3.6 V

- 1.65V ~ 1.95V

• Organization

- Memory Cell Array

- (256M + 8,192K)bit x 8bit

- Data Register

- (2K + 64)bit x8bit

• Automatic Program and Erase

- Page Program

- (2K + 64)Byte

- Block Erase

- (128K + 4K)Byte

• Page Read Operation

- Page Size

- 2K-Byte

- Random Read : 25µs(Max.)

- Serial Access : 50ns(Min.)

• Fast Write Cycle Time

- Program time : 300µs(Typ.)

- Block Erase Time : 2ms(Typ.)

• Command/Address/Data Multiplexed I/O Port

• Hardware Data Protection

- Program/Erase Lockout During Power Transitions

• Reliable CMOS Floating-Gate Technology

- Endurance : 100K Program/Erase Cycles

- Data Retention : 10 Years

• Command Register Operation

• Unique ID for Copyright Protection

• Package :

- K9K2G08U0A-FIB0

48 - Pin WSOP I (12x17x0.7mm)- Pb-free Package

- K9K2G08X0A-JCB0/JIB0

63- Ball FBGA (9.5x12) - Pb-free Package

GENERAL DESCRIPTION

Offered in 256Mx8bit the K9K2G08X0A is 2G bit with spare 64M bit capacity. Its NAND cell provides the most cost-effective solution

for the solid state mass storage market. A program operation can be performed in typical 300µs on the 2112byte page and an erase

operation can be performed in typical 2ms on a 128K-byte block. Data in the data page can be read out at 50ns cycle time per byte.

The I/O pins serve as the ports for address and data input/output as well as command input. The on-chip write controller automates all

program and erase functions including pulse repetition, where required, and internal verification and margining of data. Even the

write-intensive systems can take advantage of the K9K2G08X0A′s extended reliability of 100K program/erase cycles by providing

ECC(Error Correcting Code) with real time mapping-out algorithm. The K9K2G08X0A is an optimum solution for large nonvolatile

storage applications such as solid state file storage and other portable applications requiring non-volatility.

3

Page 4

K9K2G08U0A

K9K2G08R0A

PIN CONFIGURATION (WSOP1)

K9K2G08U0A-FIB0

N.C

1

N.C

N.C

N.C

N.C

R/B

RE

CE

N.C

Vcc

Vss

N.C

CLE

ALE

WE

WP

N.C

N.C

N.C

N.C

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

DNU

DNU

DNU

DNU

PACKAGE DIMENSIONS

48-PIN LEAD PLASTIC VERY VERY THIN SMALL OUT-LINE PACKAGE TYPE (I)

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

FLASH MEMORY

N.C

N.C

DNU

N.C

I/O7

I/O6

I/O5

I/O4

N.C

DNU

N.C

Vcc

Vss

N.C

DNU

N.C

I/O3

I/O2

I/O1

I/O0

N.C

DNU

N.C

N.C

48 - WSOP1 - 1217F

#1

+0.07

-0.03

0.16

+0.07

-0.03

0.20

0.50TYP

(0.50±0.06)

#24

15.40±0.10

#48

#25

0.70 MAX

0.58±0.04

(0.01Min)

Unit :mm

12.00±0.10

12.40MAX

17.00±0.20

+0.075

-0.035

0.10

0

°

~

8

°

0.45~0.75

4

Page 5

K9K2G08U0A

PIN CONFIGURATION (FBGA)

K9K2G08R0A

K9F1G08X0A-JCB0/JIB0

3456 1 2

FLASH MEMORY

N.C N.C

N.C

A

B

C

D

E

F

G

H

N.C N.C

N.C

/RE CLE

NC

NC

NC

NC NC

NC NC NC

NC NC

NC

NC

NCNCNC

NC NC

NCNC I/O0

I/O1NC NC Vcc I/O5 I/O7

N.C N.C

N.C

N.C

R/B/WE/CEVssALE/WP

NC

NC

NC

NC

NCNC

NC

Vcc

VssI/O6I/O4I/O3I/O2Vss

N.C N.C

N.C

N.CN.C

Top View

5

Page 6

K9K2G08U0A

PACKAGE DEMENSIONS(FBGA)

K9K2G08R0A

FLASH MEMORY

#A1

Top V iew

9.50±0.10

Bottom View

#A1 INDEX MARK(OPTIONAL)

9.50±0.10

0.80 x 9= 7.20

0.80 x 5= 4.00

0.80

65

(Datum A)

A

B

(Datum B)

12.00±0.10

2.80

C

D

E

F

G

H

4321

A

B

0.80

12.00±0.10

0.80 x 7= 5.60

0.80 x 11= 8.80

0.10MAX

63-∅0.45±0.05

∅

0.20

M

A B

Side View

12.00±0.10

2.00

0.45±0.05

1.20(Max)

0.25(Min.)

6

Page 7

K9K2G08U0A

K9K2G08R0A

PIN DESCRIPTION

Pin Name Pin Function

DATA INPUTS/OUTPUTS

I/O0 ~ I/O7

CLE

The I/O pins are used to input command, address and data, and to output data during read operations. The

I/O pins float to high-z when the chip is deselected or when the outputs are disabled.

COMMAND LATCH ENABLE

The CLE input controls the activating path for commands sent to the command register. When active high,

commands are latched into the command register through the I/O ports on the rising edge of the WE

FLASH MEMORY

signal.

ALE

CE

RE

WE

WP

R/B

Vcc

Vss GROUND

ADDRESS LATCH ENABLE

The ALE input controls the activating path for address to the internal address registers. Addresses are

latched on the rising edge of WE

CHIP ENABLE

The CE

the device does not return to standby mode in program or erase opertion. Regarding CE

operation, refer to ’Page read’ section of Device operation .

READ ENABLE

The RE

tREA after the falling edge of RE

WRITE ENABLE

The WE

the WE

WRITE PROTECT

The WP

generator is reset when the WP

READY/BUSY OUTPUT

The R/B

random read operation is in process and returns to high state upon completion. It is an open drain output

and does not float to high-z condition when the chip is deselected or when outputs are disabled.

POWER

VCC is the power supply for device.

with ALE high.

input is the device selection control. When the device is in the Busy state, CE high is ignored, and

control during read

input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid

which also increments the internal column address counter by one.

input controls writes to the I/O port. Commands, address and data are latched on the rising edge of

pulse.

pin provides inadvertent write/erase protection during power transitions. The internal high voltage

pin is active low.

output indicates the status of the device operation. When low, it indicates that a program, erase or

N.C

NOTE:

1. Connect all VCC and VSS pins of each device to common power supply outputs.

2. Do not leave VCC or VSS disconnected.

NO CONNECTION

Lead is not internally connected.

7

Page 8

K9K2G08U0A

K9K2G08R0A

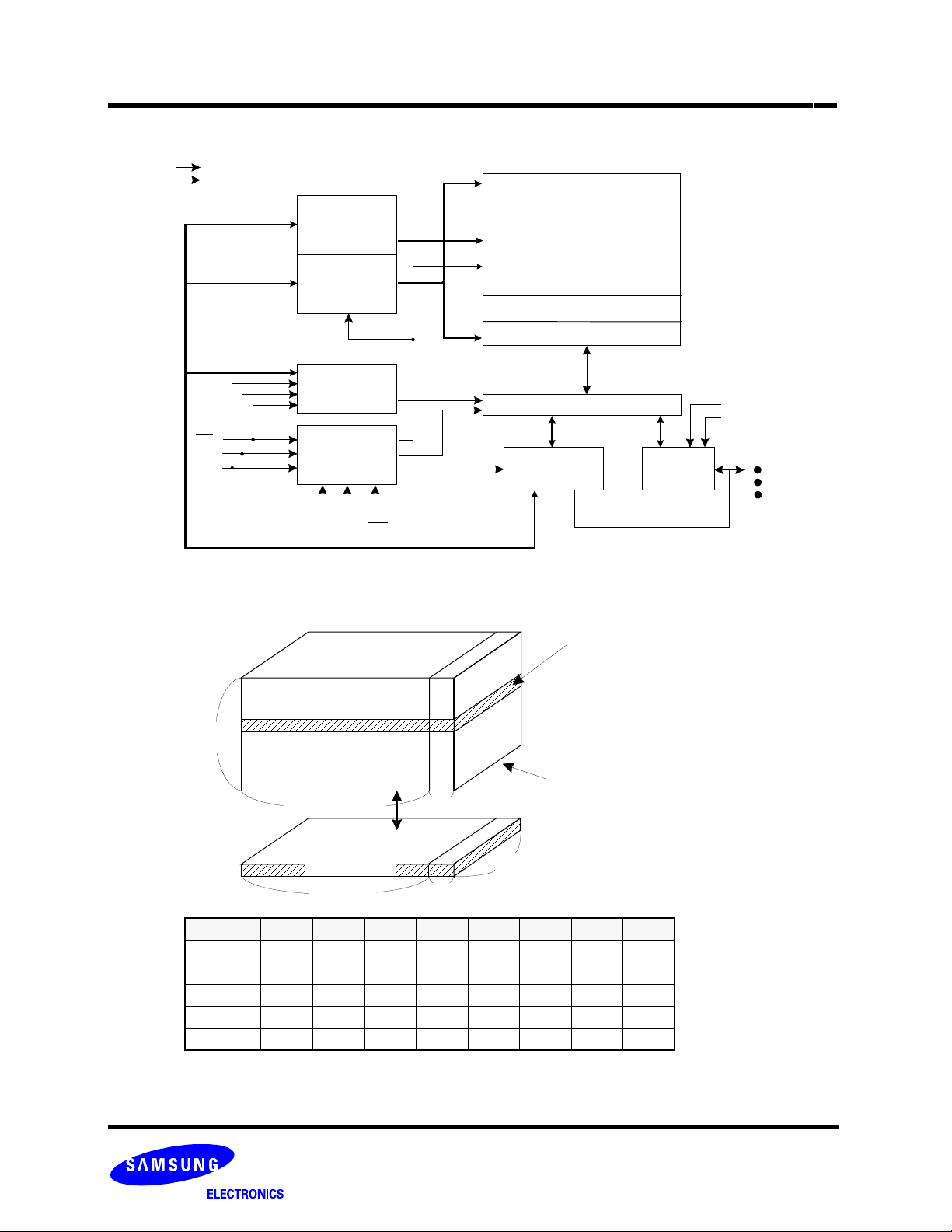

Figure 1. Functional Block Diagram

VCC

SS

V

FLASH MEMORY

A12 - A28

A0 - A11

Command

CE

RE

WE

X-Buffers

Latches

& Decoders

Y-B uff ers

Latches

& Decoders

Command

Control Logic

& High Voltage

Generator

CLE

Figure 2 Array Organization

Register

ALE

WP

2048M + 64M Bit

NAND Flash

ARRAY

(2048 + 64)Byte x 131072

Data Register & S/A

Y-G ati ng

I/O Buffers & Latches

Global Buffers

1 Block = 64 Pages

(128K + 4k) Byte

Output

Driver

VCC

VSS

I/0 0

I/0 7

128K Pages

(=2,048 Blocks)

2K Bytes 64 Bytes

Page Register

2K Bytes

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

1st Cycle A

2nd Cycle A8 A9 A10 A11 *L *L *L *L

3rd Cycle A

4th Cycle A20 A21 A22 A23 A24 A25 A26 A27

5th Cycle A28 *L *L *L *L *L *L *L

NOTE : Column Address : Starting Address of the Register.

* L must be set to "Low".

* The device ignores any additional input of address cycles than required.

0 A1 A2 A3 A4 A5 A6 A7

12 A13 A14 A15 A16 A17 A18 A19

1 Page = (2K + 64)Bytes

1 Block = (2K + 64)B x 64 Pages

= (128K + 4K) Bytes

1 Device = (2K+64)B x 64Pages x 2048 Blocks

= 2112 Mbits

8 bit

I/O 0 ~ I/O 7

64 Bytes

Column Address

Column Address

Row Address

Row Address

Row Address

8

Page 9

K9K2G08U0A

K9K2G08R0A

Product Introduction

The K9K2G08X0A is a 2112Mbit(2,214,592,512 bit) memory organized as 131,072 rows(pages) by 2112x8 columns. Spare 64 columns are located from column address of 2048~2111. A 2112-byte data register is connected to memory cell arrays for accommodating data transfer between the I/O buffers and memory cells during page read and page program operations. The memory array is

made up of 32 cells that are serially connected to form a NAND structure. Each of the 32 cells resides in a different page. A block

consists of two NAND structures. A NAND structure consists of 32 cells. Total 135,168 NAND cells reside in a block. The program and

read operations are executed on a page basis, while the erase operation is executed on a block basis. The memory array consists of

2048 separately erasable 128K-byte blocks. It indicates that the bit by bit erase operation is prohibited on the K9K2G08X0A.

The K9K2G08X0A has addresses multiplexed into 8 I/Os. This scheme dramatically reduces pin counts and allows system upgrades

to future densities by maintaining consistency in system board design. Command, address and data are all written through I/O's by

bringing WE

Enable(ALE) are used to multiplex command and address respectively, via the I/O pins. Some commands require one bus cycle. For

example, Reset Command, Status Read Command and etc require just one cycle bus. Some other commands, like Page Read, Block

Erase and Page Program, require two cycles: one cycle for setup and the other cycle for execution. The 264M byte physical space

requires 29 addresses, thereby requiring five cycles for addressing: 2 cycles of column address, 3 cycles of row address, in that order.

Page Read and Page Program need the same five address cycles following the required command input. In Block Erase operation,

however, only the three row address cycles are used. Device operations are selected by writing specific commands into the command

register. Table 1 defines the specific commands of the K9K2G08X0A.

to low while CE is low. Those are latched on the rising edge of WE. Command Latch Enable(CLE) and Address Latch

FLASH MEMORY

Table 1. Command Sets

Function 1st. Cycle 2nd. Cycle Acceptable Command during Busy

Read 00h 30h

Read for Copy Back 00h 35h

Read ID 90h -

Reset FFh - O

Page Program 80h 10h

Cache Program 80h 15h

Copy-Back Program 85h 10h

Block Erase 60h D0h

Random Data Input

Random Data Output

Read Status 70h O

NOTE : 1. Random Data Input/Output can be executed in a page.

2. Cache program and Copy-Back program are supported only with 3.3V device.

Caution : Any undefined command inputs are prohibited except for above command set of Table 1.

*1

*1

85h -

05h E0h

9

Page 10

K9K2G08U0A

K9K2G08R0A

ABSOLUTE MAXIMUM RATINGS

Parameter Symbol

Voltage on any pin relative to V

Temperature Under

Bias

Storage Temperature

K9K2G08X0A-XCB0

K9K2G08X0A-XIB0 -40 to +125

K9K2G08X0A-XCB0

K9K2G08X0A-XJIB0

SS

VIN/OUT -0.6 to + 2.45 -0.6 to + 4.6

V

CC -0.6 to + 2.45 -0.6 to + 4.6

T

BIAS

T

STG -65 to +150 °C

Short Circuit Current Ios 5 mA

NOTE :

1. Minimum DC voltage is -0.6V on input/output pins. During transitions, this level may undershoot to -2.0V for periods <30ns.

Maximum DC voltage on input/output pins is V

2. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions

as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

CC,+0.3V which, during transitions, may overshoot to VCC+2.0V for periods <20ns.

1.8V DEVICE 3.3V DEVICE

-10 to +125

RECOMMENDED OPERATING CONDITIONS

(Voltage reference to GND, :TA=0 to 70°C, K9K2G08X0A-XIB0:TA=-40 to 85°C)

Parameter Symbol

Supply Voltage V

Supply Voltage V

CC 1.65 1.8 1.95 2.7 3.3 3.6 V

SS 000000V

K9K2G08R0A(1.8V) K9K2G08U0A(3.3V)

Min Typ . Max Min Ty p. Max

FLASH MEMORY

Rating

Unit

V

°C

Unit

DC AND OPERATING CHARACTERISTICS(Recommended operating conditions otherwise noted.)

Parameter Symbol Test Conditions

Operat-

Current

Page Read with

Serial Access

ing

Program I

Erase I

Stand-by Current(TTL) I

Stand-by Current(CMOS) I

Input Leakage Current I

Output Leakage Current I

Input High Voltage V

Input Low Voltage, All

inputs

Output High Voltage

Level

Output Low Voltage Level V

Output Low Current(R/B

)IOL(R/B)

tRC=50ns, (30ns with 3.3V device)

I

CC1

CE=VIL

IOUT=0mA

CC2 - - 10 20 - 10 30

CC3 - - 10 20 - 10 30

SB1CE=VIH, WP=0V/VCC -- 1 --1

CE

SB2

LI VIN=0 to Vcc(max) - - ±20 - - ±10

LO VOUT=0 to Vcc(max) - - ±20 - - ±10

IH - 0.8xVcc - Vcc+0.3 0.8xVcc - Vcc+0.3

V

IL - -0.3 - 0.2xVcc -0.3 - 0.2xVcc

OH

V

OL

=VCC-0.2,

=0V/VCC

WP

K9K2G08R0A: IOH=-100µA

K9K2G08U0A: I

K9K2G08R0A: IOL=100mA

K9K2G08U0A: I

K9K2G08R0A: V

K9K2G08U0A: V

OH=-400µA

OL=2.1mA

OL=0.1V

OL=0.4V

K9K2G08R0A(1.8V) K9K2G08U0A(3.3V)

Min Typ Max Min Typ Max

- 10 20 - 10 30

- 20 100 - 20 100

Vcc-0.1 - - 2.4 - -

--0.1 --0.4

34 - 810-mA

Unit

mA

µA

V

10

Page 11

K9K2G08U0A

K9K2G08R0A

VALID BLOCK

Parameter Symbol Min Ty p. Max Unit

Valid Block Number N

NOTE :

1. The

K9K2G08X0A may include invalid blocks when first shipped. Additional invalid blocks may develop while being used. The number of valid

blocks is presented with both cases of invalid blocks considered. Invalid blocks are defined as blocks that contain one or more bad bits

or program factory-marked bad blocks.

2. The 1st block, which is placed on 00h block address, is fully guaranteed to be a valid block and does not require Error Correction up to 1K Program/

Earase cycles..

VB 2008 - 2048 Blocks

Refer to the attached technical notes for appropriate management of invalid blocks.

AC TEST CONDITION

(K9K2G08X0A-XCB0 :TA=0 to 70°C, K9K2G08X0A-XIB0:TA=-40 to 85°C

K9K2G08R0A : Vcc=1.65V~1.95V, K9K2G08U0A : Vcc=2.7V~3.6Vunless otherwise noted)

Parameter K9K2G08R0A K9K2G08U0A

Input Pulse Levels 0V to Vcc 0V to Vcc

Input Rise and Fall Times 5ns 5ns

Input and Output Timing Levels Vcc/2 Vcc/2

Output Load 1 TTL GATE and CL=30pF 1 TTL GATE and CL=50pF

CAPACITANCE(TA=25C, VCC=1.8V/3.3V, f=1.0MHz)

Item Symbol Test Condition Min Max Unit

Input/Output Capacitance C

Input Capacitance C

NOTE : Capacitance is periodically sampled and not 100% tested.

I/O VIL=0V - 20 pF

IN VIN=0V - 20 pF

FLASH MEMORY

. Do not erase

MODE SELECTION

CLE ALE CE WE RE WP Mode

HLL HX

Read Mode

Command Input

L H L H X Address Input(5clock)

HLL HH

Write Mode

Command Input

L H L H H Address Input(5clock)

L L L H H Data Input

LLLH X Data Output

X X X X H X During Read(Busy)

XXXXXH During Program(Busy)

XXXXXH During Erase(Busy)

X

XXHXX

NOTE : 1. X can be VIL or VIH.

2. WP should be biased to CMOS high or CMOS low for standby.

(1)

X

X X X L Write Protect

(2)

CC

Stand-by

0V/V

Program / Erase Characteristics

Parameter Symbol Min Typ Max Unit

Program Time

Dummy Busy Time for Cache Program

Number of Partial Program Cycles

in the Same Page

Main Array

Spare Array - - 4 cycles

Block Erase Time t

NOTE : 1.Typical program time is defined as the time within which more than 50% of whole pages are programmed at Vcc of 3.3V and 25°C

2. Max. time of tCBSY depends on timing between internal program completion and data in

*1

PROG

t

*2

t

CBSY

Nop

BERS -23ms

- 200 700 µs

3700

--4cycles

µs

11

Page 12

K9K2G08U0A

K9K2G08R0A

AC Timing Characteristics for Command / Address / Data Input

Parameter Symbol

CLE setup Time

CLE Hold Time t

setup Time

CE

CE

Hold Time tCH 10 5 - - ns

WE

Pulse Width tWP 25 15 - - ns

ALE setup Time

ALE Hold Time t

Data setup Time

Data Hold Time t

Write Cycle Time t

WE

High Hold Time tWH 15 10 - - ns

Address to Data Loading Time

CLS

t

CLH 10 5 - - ns

CS

t

t

ALS

ALH 10 5 - - ns

DS

t

DH 10 5 - - ns

WC 45 30 - - ns

ADL

t

K9K2G08R0A K9K2G08U0A K9K2G08R0A K9K2G08U0A

*1

*1

*1

*1

*2

25 15 - - ns

35 20 - - ns

25 15 - - ns

20 15 - - ns

100

Min Max

*2

100

*2

FLASH MEMORY

--ns

Unit

NOTE : 1. The transition of the corresponding control pins must occur only once while WE is held low.

2. tADL is the time from the WE

3. For cache program operation, the whole AC Charcateristics must be same as that of K9K2G08R0A.

rising edge of final address cycle to the WE rising edge of first data cycle.

AC Characteristics for Operation

Parameter Symbol

K9K2G08R0A K9K2G08U0A K9K2G08R0A K9K2G08U0A

Data Transfer from Cell to Register tR - - 25 25 µs

ALE to RE

CLE to RE

Ready to RE

RE Pulse Width t

WE High to Busy t

Read Cycle Time t

RE

CE

RE

CE

RE

RE

Output Hi-Z to RE

WE

Device Resetting Time (Read/Program/Erase) t

Delay tAR 10 10 - - ns

Delay tCLR 10 10 - - ns

Low tRR 20 20 - - ns

RP 25 15 - - ns

WB - - 100 100 ns

RC 50 30 - - ns

Access Time tREA - - 30 20 ns

Access Time tCEA - - 45 35 ns

High to Output Hi-Z tRHZ - - 30 30 ns

High to Output Hi-Z tCHZ - - 20 20 ns

or CE High to Output hold tOH 15 15 - - ns

High Hold Time tREH 15 10 - - ns

Low tIR 00 - -ns

High to RE Low tWHR 60 60 - - ns

RST --

Min Max

5/10/500

*1

5/10/500

*1

Unit

µs

NOTE: 1. If reset command(FFh) is written at Ready state, the device goes into Busy for maximum 5us.

2. For cache program operation, the whole AC Charcateristics must be same as that of K9K2G08R0A.

12

Page 13

K9K2G08U0A

K9K2G08R0A

NAND Flash Technical Notes

Initial Invalid Block(s)

Initial invalid blocks are defined as blocks that contain one or more initial invalid bits whose reliability is not guaranteed by Samsung.

The information regarding the initial invalid block(s) is so called as the initial invalid block information. Devices with initial invalid

block(s) have the same quality level as devices with all valid blocks and have the same AC and DC characteristics. An initial invalid

block(s) does not affect the performance of valid block(s) because it is isolated from the bit line and the common source line by a

select transistor. The system design must be able to mask out the initial invalid block(s) via address mapping. The 1st block, which is

placed on 00h block address, is fully guaranteed to be a valid block, does not require Error Correction up to 1K Program/Erase

cycles.

Identifying Initial Invalid Block(s)

All device locations are erased except locations where the initial invalid block(s) information is written prior to shipping. The initial

invalid block(s) status is defined by the 1st byte in the spare area. Samsung makes sure that either the 1st or 2nd page of every initial

invalid block has non-FFh data at the column address of 2048. Since the initial invalid block information is also erasable in most

cases, it is impossible to recover the information once it has been erased. Therefore, the system must be able to recognize the initial

invalid block(s) based on the initial invalid block information and create the initial invalid block table via the following suggested flow

chart(Figure 3). Any intentional erasure of the initial invalid block information is prohibited.

Start

FLASH MEMORY

Increment Block Address

Create (or update)

Initial Invalid Block(s) Table

Figure 3. Flow chart to create initial invalid block table.

Set Block Address = 0

No

No

Check "FFh ?

Yes

Last Block ?

Yes

End

Check "FFh" at the column address

2048 of the 1st and 2nd page in the block

*

13

Page 14

K9K2G08U0A

K9K2G08R0A

NAND Flash Technical Notes (Continued)

Error in write or read operation

Within its life time, additional invalid blocks may develop with NAND Flash memory. Refer to the qualification report for the block failure rate.The following possible failure modes should be considered to implement a highly reliable system. In the case of status read

failure after erase or program, block replacement should be done. Because program status fail during a page program does not affect

the data of the other pages in the same block, block replacement can be executed with a page-sized buffer by finding an erased

empty block and reprogramming the current target data and copying the rest of the replaced block. In case of Read, ECC must be

employed. To improve the efficiency of memory space, it is recommended that the read failure due to single bit error should be

reclaimed by ECC without any block replacement. The block failure rate in the qualification report does not include those reclaimed

blocks.

Failure Mode Detection and Countermeasure sequence

Write

Read Single Bit Failure Verify ECC -> ECC Correction

Erase Failure Status Read after Erase --> Block Replacement

Program Failure Status Read after Program --> Block Replacement

FLASH MEMORY

ECC

Program Flow Chart

: Error Correcting Code --> Hamming Code etc.

Example) 1bit correction & 2bit detection

Start

Write 80h

Write Address

Write Data

Write 10h

Read Status Register

I/O 6 = 1 ?

or R/B = 1 ?

No

*

Program Error

No

I/O 0 = 0 ?

P

rogram Completed

Yes

Yes

: If program operation results in an error, map out

*

the block including the page in error and copy the

target data to another block.

14

Page 15

K9K2G08U0A

K9K2G08R0A

NAND Flash Technical Notes (Continued)

FLASH MEMORY

Erase Flow Chart

*

Erase Error

No

Start

Write 60h

Write Block Address

Write D0h

Read Status Register

I/O 6 = 1 ?

or R/B = 1 ?

Yes

I/O 0 = 0 ?

Yes

No

Read Flow Chart

Reclaim the Error

Start

Write 00h

Write Address

Write 30h

Read Data

ECC Generation

No

Verify ECC

Yes

Page Read Completed

Erase Completed

: If erase operation results in an error, map out

*

the failing block and replace it with another block.

Block Replacement

Block A

1st

∼

{

(n-1)th

nth

(page)

1st

∼

(n-1)th

nth

(page)

* Step1

When an error happens in the nth page of the Block ’A’ during erase or program operation.

* Step2

Copy the data in the 1st ~ (n-1)th page to the same location of another free block. (Block ’B’)

* Step3

Then, copy the nth page data of the Block ’A’ in the buffer memory to the nth page of the Block ’B’.

* Step4

Do not erase or program to Block ’A’ by creating an ’invalid Block’ table or other appropriate scheme.

an error occurs.

Block B

{

1

Buffer memory of the controller.

2

15

Page 16

K9K2G08U0A

K9K2G08R0A

NAND Flash Technical Notes (Continued)

Addressing for program operation

Within a block, the pages must be programmed consecutively from the LSB (least significant bit) page of the block to MSB (most significant bit) pages of the block. Random page address programming is prohibited.

FLASH MEMORY

Page 63

Page 31

Page 2

Page 1

Page 0

From the LSB page to MSB page

DATA IN: Data (1)

(64)

:

(32)

:

(3)

(2)

(1)

Data register

Data (64)

Page 63

Page 31

Page 2

Page 1

Page 0

Ex.) Random page program (Prohibition)

DATA IN: Data (1)

(64)

:

(1)

:

(3)

(32)

(2)

Data register

Data (64)

16

Page 17

K9K2G08U0A

K9K2G08R0A

System Interface Using CE don’t-care.

For an easier system interface, CE may be inactive during the data-loading or serial access as shown below. The internal 2112byte

data registers are utilized as separate buffers for this operation and the system design gets more flexible. In addition, for voice or

audio applications which use slow cycle time on the order of µ-seconds, de-activating CE

would provide significant savings in power consumption.

Figure 4. Program Operation with CE don’t-care.

CLE

CE don’t-care

CE

FLASH MEMORY

during the data-loading and serial access

WE

ALE

I/Ox

CE

WE

80h Data Input

Address(5Cycles)

tCS

tWP

tCH

Figure 5. Read Operation with CE don’t-care.

CLE

CE

≈

CE

RE

I/O0~7

tCEA

tREA

CE

don’t-care

≈

Data Input

out

10h

RE

ALE

R/B

WE

I/Ox

≈

tR

Address(5Cycle)00h

30h

17

Data Output(serial access)

Page 18

K9K2G08U0A

K9K2G08R0A

NOTE

Device

K9K2G08X0A I/O 0 ~ I/O 7 ~2112byte A0~A7 A8~A11 A12~A19 A20~A27 A28

I/O DATA ADDRESS

I/Ox Data In/Out Col. Add1 Col. Add2 Row Add1 Row Add2 Row Add3

Command Latch Cycle

FLASH MEMORY

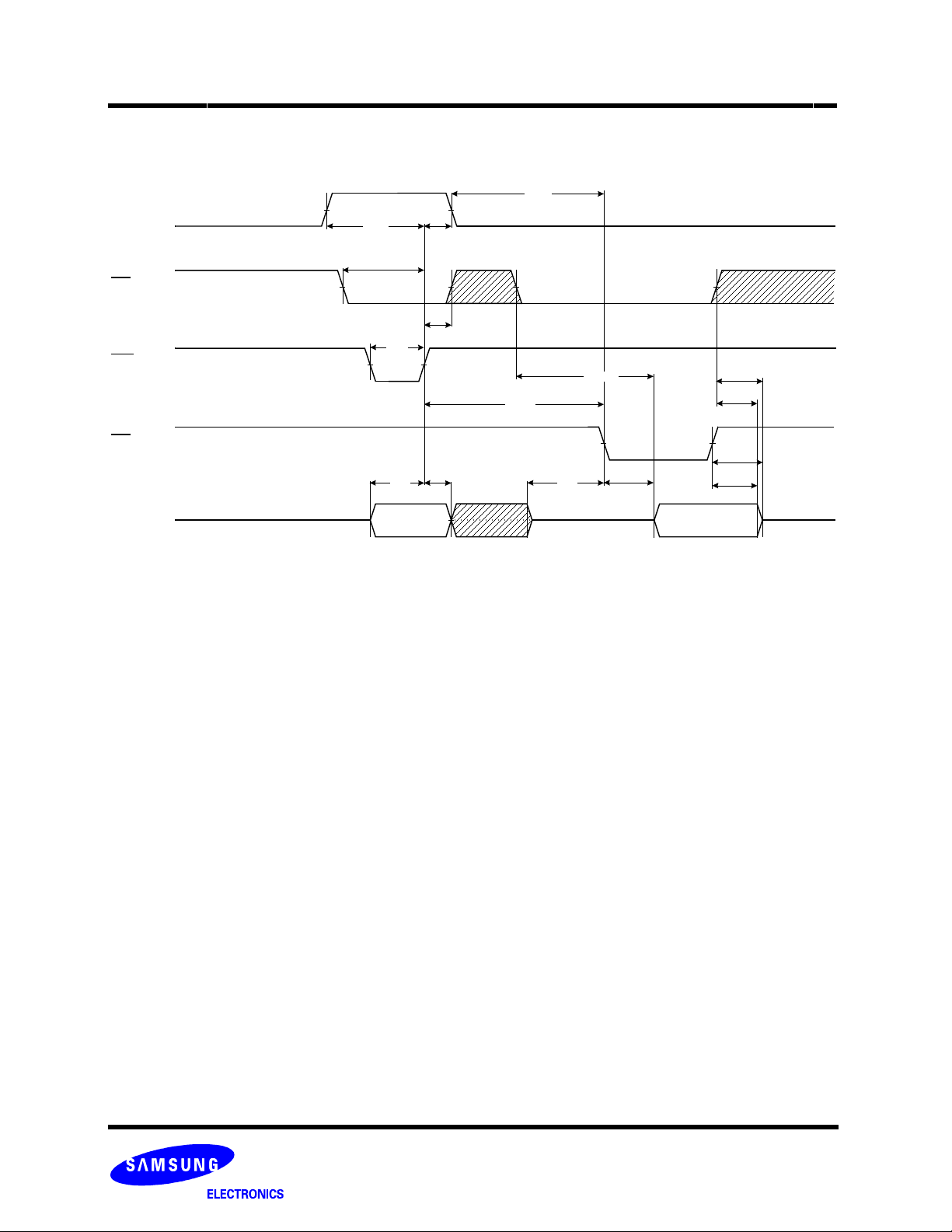

CLE

CE

WE

ALE

I/Ox

Address Latch Cycle

CLE

tCLS

tCLS

tCS

tALS

tWP

tDS

Command

tCLH

tCH

tALH

tDH

CE

WE

ALE

I/Ox

tCS

tALS

tWP

tDS

Col. Add1

tWC

tALH

tDH

tWH

tWP

tALS

18

tWC

tALH

tDH

tDS

Col. Add2

tWH

tWP

tALS

Row Add1

tDS

tWC

tALH

tDH

tWH

tWP

tALS

tDS

Row Add2

tALH

tDH

Page 19

K9K2G08U0A

Input Data Latch Cycle

CLE

CE

K9K2G08R0A

FLASH MEMORY

tCLH

≈

tCH

≈

ALE

WE

I/Ox

tALS

tWP

tWC

tWH

tDH

tDS

DIN 0

NOTES : DIN final means 2112

tWP

tDS

DIN 1

tDH

Serial Access Cycle after Read(CLE=L, WE=H, ALE=L)

CE

RE

tCEA

tREA

tREH

tREA

≈

≈

tWP

≈

≈

tDH

tDS

DIN final*

≈≈≈≈

tREA

tCHZ*

tOH

I/Ox

R/B

tRHZ*

Dout

tRR

NOTES : Transition is measured ±200mV from steady state voltage with load.

This parameter is sampled and not 100% tested.

tRC

Dout

19

tRHZ*

tOH

Dout

Page 20

K9K2G08U0A

Status Read Cycle

CLE

CE

WE

RE

I/Ox

K9K2G08R0A

tCLS

tCS

tWP

tDS

70h

tCLH

tCH

tDH

tWHR

tCLR

tIR*

tCEA

FLASH MEMORY

tCHZ*

tOH

tREA

Status Output

tRHZ*

tOH

20

Page 21

K9K2G08U0A

Read Operation

CLE

CE

tWC

WE

ALE

K9K2G08R0A

FLASH MEMORY

tCLR

tWB

tAR

tR

tRC

tRHZ

RE

I/Ox

00h

Col. Add1

Col. Add2

Column Address

Row Add1

R/B

Read Operation(Intercepted by CE)

CLE

CE

WE

ALE

Row Add2

Row Address

Row Add3

30h

tRR

Busy

tWB

tAR

Dout N

Dout N+1

≈

tCHZ

tOH

≈≈

Dout M

RE

I/Ox

R/B

00h

Col. Add1

Column Address

Col. Add2 Row Add1

Row Address

Row Add2

Row Add3

21

30h

tR

tRR

Busy

Dout N

tRC

Dout N+1

Dout N+2

Page 22

K9K2G08U0A

K9K2G08R0A

Dout M+1

FLASH MEMORY

tCLR

B

W

t

tWHR

tAR

tREA

C

R

t

tR

tRR

Dout M

E0h

Col Add2

Col Add1

Column Address

Dout N Dout N+1

30h 05h

Busy

Random Data Output In a Page

CLE

CE

WE

ALE

22

RE

Row Add3

Row Add2

Row Address

Row Add1

Col. Add2

Col. Add1

Column Address

00h

I/Ox

R/B

Page 23

K9K2G08U0A

Page Program Operation

CLE

CE

tWC

WE

ALE

RE

I/Ox

R/B

80h

SerialData

Input Command

Co.l Add1 Col. Add2 Row Add1 Row Add 2 Row Add3

Column Address Row Address

tWC

K9K2G08R0A

FLASH MEMORY

tWC

≈

tPROG

tADL

1 up to m Byte

≈

Din

N

≈

Serial Input

m = 2112byte

Din

M

tWB

10h

Program

Command

70h I/O

Read Status

Command

≈

I/O

0

=0 Successful Program

I/O

0

=1 Error in Program

0

NOTES : tADL is the time from the WE rising edge of final address cycle to the WE rising edge of first data cycle.

23

Page 24

K9K2G08U0A

K9K2G08R0A

0

Read Status

Command

FLASH MEMORY

≈

tPROG

tWB

10h

Program

Command

K

Din

≈

≈

tADL

≈

Din

Serial Input

J

tWC

tWC

Col. Add2

Column Address

Col. Add1

85h

Random Data

Input Command

M

Din

≈

≈≈

N

Din

Serial Input

tADL

Row Add3

rising edge of final address cycle to the WE rising edge of first data cycle.

Row Add2

Row Add1

Col. Add2

Column Address Row Address

Col. Add1

Page Program Operation with Random Data Input

CLE

CE

tWC

WE

ALE

RE

24

80h 70h I/O

I/Ox

Serial Data

Input Command

NOTES : tADL is the time from the WE

R/B

Page 25

K9K2G08U0A

K9K2G08R0A

0

Read Status

Command

tPROG

≈

Busy

=0 Successful Program

=1 Error in Program

0

0

I/O

I/O

FLASH MEMORY

tWB

10h

Data N

≈ ≈

Data 1

tADL

Row Add3

Row Add2

Row Address

Row Add1

tWC

tWB

Col Add2

Col Add1

Column Address

85h

≈

Copy-Back Data

Input Command

tR

35h

Row Add3

Row Add2

Row Address

Row Add1

Col Add2

Col Add1

Column Address

00h 70h I/O

Busy

rising edge of final address cycle to the WE rising edge of first data cycle.

NOTES : tADL is the time from the WE

Copy-Back Program Operation With Random Data Input

CLE

CE

WE

ALE

RE

I/Ox

R/B

25

Page 26

K9K2G08U0A

K9K2G08R0A

FLASH MEMORY

≈

tCPROG

tWB

I/O

70h

tPROG

70h

10h

≈

Address &

Data Input

10h

(True)

Command

Program Confirm

M

Din

80h

≈≈

N

Din

tADL

Row Add3

Row Add2

Row Add1

Col Add2

Col Add1

80h

Last Page Input & Program

tCBSY

tCBSY

15h

Address &

Data Input

80h

15h

Cache Program Operation(available only within a block)

CLE

CE

Address &

≈

tCBSY

tWB

15h

Program

Command

(Dummy)

M

Din

tADL

RE

≈≈

N

Din

Row Add3

Row Add2

Row Add1

Col Add2

Col Add1

80h

I/Ox

Serial Input

Row Address

Column Address

Serial Data

Input Command

Max. 63 times repeatable

R/B

≈

tWC

WE

ALE

CBSY :

max. 700us

t

tCBSY

Ex.) Cache Program

NOTES : tADL is the time from the WE rising edge of final address cycle to the WE rising edge of first data cycle.

R/B

Data Input

80h

15h

Address &

Data Input

Col Add1,2 & Row Add1,2

80h

I/Ox

Data

26

Page 27

K9K2G08U0A

Block Erase Operation

CLE

CE

tWC

WE

ALE

RE

K9K2G08R0A

tWB

tBERS

FLASH MEMORY

I/Ox

R/B

Row Add1

60h

Auto Block Erase

Setup Command

Row Add2 Row Add3

Row Address

D0h 70h I/O 0

Busy

Erase Command

≈

Read Status

Command

I/O0=0 Successful Erase

I/O

0

=1 Error in Erase

27

Page 28

K9K2G08U0A

Read ID Operation

CLE

CE

WE

K9K2G08R0A

FLASH MEMORY

ALE

RE

I/Ox

Read ID Command Maker Code

90h

Address. 1cycle

Device Device Code*(2nd Cycle) 4th Cycle*

K9K2G08R0A AAh 15h

K9K2G08U0A DAh 15h

ID Defintition Table

90 ID : Access command = 90H

tAR

tREA

00h ECh

Device

Code*

Device Code

XXh

4th cyc.*

st

1

nd

2

rd

3

th

4

Byte

Byte

Byte

Byte

Description

Maker Code

Device Code

Don’t care

Page Size, Block Size, Spare Size, Organization

28

Page 29

K9K2G08U0A

4th ID Data

Page Size

(w/o redundant area )

Blcok Size

(w/o redundant area )

Redundant Area Size

( byte/512byte)

Organization

Serial AccessMinimum

K9K2G08R0A

Description I/O7 I/O6 I/O5 I/O4 I/O3 I/O2 I/O1 I/O0

1KB

2KB

Reserved

Reserved

64KB

128KB

256KB

Reserved

8

16

x8

x16

50ns

Reserved

Reserved

Reserved

0

1

0

1

0 0

0 1

1 0

1 1

0

1

FLASH MEMORY

0 0

0 1

1 0

1 1

0

1

0

0

1

1

29

Page 30

K9K2G08U0A

K9K2G08R0A

Device Operation

PAG E R EA D

Page read is initiated by writing 00h-30h to the command register along with five address cycles. After initial power up, 00h command

is latched. Therefore only five address cycles and 30h command initiates that operation after initial power up. The 2,112 bytes of data

within the selected page are transferred to the data registers in less than 25µs(t

this data transfer(tR) by analyzing the output of R/B

out in 50ns cycle time by sequentially pulsing RE

data starting from the selected column address up to the last column address.

The device may output random data in a page instead of the consecutive sequential data by writing random data output command.

The column address of next data, which is going to be out, may be changed to the address which follows random data output command. Random data output can be operated multiple times regardless of how many times it is done in a page.

pin. Once the data in a page is loaded into the data registers, they may be read

. The repetitive high to low transitions of the RE clock make the device output the

R). The system controller can detect the completion of

Figure 6. Read Operation

CLE

CE

FLASH MEMORY

WE

ALE

R/B

RE

I/Ox

Address(5Cycle)00h

Col Add1,2 & Row Add1,2,3

tR

30h

Data Field Spare Field

Data Output(Serial Access)

30

Page 31

K9K2G08U0A

K9K2G08R0A

Figure 7. Random Data Output In a Page

FLASH MEMORY

R/B

tR

RE

I/Ox

00h

Address

5Cycles

Col Add1,2 & Row Add1,2,3

30h

Data Field

Data Output

Spare Field

05h

Address

2Cycles

E0h

Data Field

Data Output

Spare Field

PAGE PROGRAM

The device is programmed basically on a page basis, but it does allow multiple partial page programing of a word or consecutive

bytes up to 2112, in a single page program cycle. The number of consecutive partial page programming operation within the same

page without an intervening erase operation must not exceed 4 times for main array(1time/512byte) and 4 times for spare array(

1time/16byte). The addressing should be done in sequential order in a block. A page program cycle consists of a serial data loading

period in which up to 2112bytes of data may be loaded into the data register, followed by a non-volatile programming period where the

loaded data is programmed into the appropriate cell.

The serial data loading period begins by inputting the Serial Data Input command(80h), followed by the five cycle address inputs and

then serial data loading. The words other than those to be programmed do not need to be loaded. The device supports random data

input in a page. The column address for the next data, which will be entered, may be changed to the address which follows random

data input command(85h). Random data input may be operated multiple times regardless of how many times it is done in a page.

The Page Program confirm command(10h) initiates the programming process. Writing 10h alone without previously entering the serial

data will not initiate the programming process. The internal write state controller automatically executes the algorithms and timings

necessary for program and verify, thereby freeing the system controller for other tasks. Once the program process starts, the Read

Status Register command may be entered to read the status register. The system controller can detect the completion of a program

cycle by monitoring the R/B

mand are valid while programming is in progress. When the Page Program is complete, the Write Status Bit(I/O 0) may be

checked(Figure 8). The internal write verify detects only errors for "1"s that are not successfully programmed to "0"s. The command

register remains in Read Status command mode until another valid command is written to the command register.

output, or the Status bit(I/O 6) of the Status Register. Only the Read Status command and Reset com-

Figure 8. Program & Read Status Operation

R/B

I/Ox

80h

Address & Data Input

Col Add1,2 & Row Add1,2,3

Data

10h 70h

31

tPROG

I/O0

Fail

"0"

Pass

"1"

Page 32

K9K2G08U0A

K9K2G08R0A

Figure 9. Random Data Input In a Page

FLASH MEMORY

R/B

tPROG

"0"

I/Ox

80h

Address & Data Input

Col Add1,2 & Row Add1,2,3

Data

85h

Address & Data Input

Col Add1,2

Data

10h

70h

I/O0

"1"

Fail

Pass

Cache Program

Cache Program is an extension of Page Program, which is executed with 2112byte data registers, and is available only within a block.

Since the device has 1 page of cache memory, serial data input may be executed while data stored in data register are programmed

into memory cell.

After writing the first set of data up to 2112byte into the selected cache registers, Cache Program command (15h) instead of actual

Page Program (10h) is inputted to make cache registers free and to start internal program operation. To transfer data from cache registers to data registers, the device remains in Busy state for a short period of time(tCBSY) and has its cache registers ready for the

next data-input while the internal programming gets started with the data loaded into data registers. Read Status command (70h) may

be issued to find out when cache registers become ready by polling the Cache-Busy status bit(I/O 6). Pass/fail status of only the previouse page is available upon the return to Ready state. When the next set of data is inputted with the Cache Program command,

tCBSY is affected by the progress of pending internal programming. The programming of the cache registers is initiated only when the

pending program cycle is finished and the data registers are available for the transfer of data from cache registers. The status bit(I/

O5) for internal Ready/Busy may be polled to identify the completion of internal programming. If the system monitors the progress of

programming only with R/B

mand (10h). If the Cache Program command (15h) is used instead, status bit (I/O5) must be polled to find out when the last programming is actually finished before starting other operations such as read. Pass/fail status is available in two steps. I/O 1 returns with the

status of the previous page upon Ready or I/O6 status bit changing to "1", and later I/O 0 with the status of current page upon true

Ready (returning from internal programming) or I/O 5 status bit changing to "1". I/O 1 may be read together when I/O 0 is checked.

, the last page of the target programming sequence must be progammed with actual Page Program com-

Figure 10. Cache Program(available only within a block)

R/B

R/B

I/Ox

tCBSY

Address &

80h

Data Input*

Col Add1,2 & Row Add1,2,3 Col Add1,2 & Row Add1,2,3

Data Data

15h

80h

Address &

Data Input

tCBSY

Address &

80h

Data Input

Col Add1,2 & Row Add1,2,3

Data

70h

output

Status

15h

80h

Col Add1,2 & Row Add1,2,3

Status

70h

output

Address &

Data Input

Data

15h

tCBSY

15h

Address &

80h

Data Input

Col Add1,2 & Row Add1,2,3

Data

tCBSY

Address &

80h

Data Input

Col Add1,2 & Row Add1,2,3

Data

tCBSY

15h

70h

Status

output

Check I/O1 for pass/fail

70h

tCBSY

Address &

80h

15h

Status

output

Status

output

Check I/O5 for internal ready/busy

Check I/O0,1 for pass/fail

Data Input

Col Add1,2 & Row Add1,2,3

Data

Address &

80h

Data Input

Col Add1,2 & Row Add1,2,3

Data

10h

tPROG

70h

tCBSY

15h

32

Page 33

K9K2G08U0A

K9K2G08R0A

NOTE : Since programming the last page does not employ caching, the program time has to be that of Page Program. However, if the

previous program cycle with the cache data has not finished, the actual program cycle of the last page is initiated only after completion of the previous cycle, which can be expressed as the following formula.

tPROG= Program time for the last page+ Program time for the ( last -1 )th page

- (Program command cycle time + Last page data loading time)

Copy-Back Program

The copy-back program is configured to quickly and efficiently rewrite data stored in one page without utilizing an external memory.

Since the time-consuming cycles of serial access and re-loading cycles are removed, the system performance is improved. The benefit is especially obvious when a portion of a block is updated and the rest of the block also need to be copied to the newly assigned

free block. The operation for performing a copy-back program is a sequential execution of page-read without serial access and copying-program with the address of destination page. A read operation with "35h" command and the address of the source page moves

the whole 2112byte data into the internal data buffer. As soon as the device returns to Ready state, Page-Copy Data-input command

(85h) with the address cycles of destination page followed may be written. The Program Confirm command (10h) is required to actually begin the programming operation. Copy-Back Program operation is allowed only within the same memory plane. Once the CopyBack Program is finished, any additional partial page programming into the copied pages is prohibited before erase. A27 must be the

same between source and target page. Data input cycle for modifying a portion or multiple distant portions of the source page is

allowed as shown in Figure 11. "When there is a program-failure at Copy-Back operation, error is reported by pass/fail status.

But if the soure page has an error bit by charge loss, accumulated copy-back operations could also accumulate bit errors. In

this case, verifying the source page for a bit error is recommended before Copy-back program"

Figure 11. Page Copy-Back program Operation

FLASH MEMORY

tR

tPROG

R/B

Add.(5Cycles)

I/Ox

NOTE: It’s prohibited to operate Copy-Back program from an odd address page(source page) to an even address page(target page) or from an even

address page(source page) to an odd address page(target page). Therefore, the Copy-Back program is permitted just between odd address pages or

even address pages.

00h

Col. Add1,2 & Row Add1,2,3

Source Address

35h

85h 70h

Add.(5Cycles)

Col. Add1,2 & Row Add1,2,3

Destination Address

10h

I/O0

Fail

Pass

Figure 12. Page Copy-Back program Operation with Random Data Input

10h

tPROG

70h

R/B

I/Ox

Add.(5Cycles)

00h

Col. Add1,2 & Row Add1,2,3

Source Address

35h

tR

Add.(5Cycles)

85h

Col. Add1,2 & Row Add1,2,3

Destination Address

Data

There is no limitation for the number of repetition.

85h

Add.(2Cycles)

Col Add1,2

Data

33

Page 34

K9K2G08U0A

K9K2G08R0A

BLOCK ERASE

The Erase operation is done on a block basis. Block address loading is accomplished in three cycles initiated by an Erase Setup

command(60h). Only address A

address loading initiates the internal erasing process. This two-step sequence of setup followed by execution command ensures that

memory contents are not accidentally erased due to external noise conditions.

At the rising edge of WE

the erase operation is completed, the Write Status Bit(I/O 0) may be checked. Figure 13 details the sequence.

18 to A28 is valid while A12 to A17 is ignored. The Erase Confirm command(D0h) following the block

after the erase confirm command input, the internal write controller handles erase and erase-verify. When

Figure 13. Block Erase Operation

FLASH MEMORY

R/B

tBERS

"0"

I/Ox

60h

Address Input(3Cycle)

Row Add. : A12 ~ A28

D0h

70h

I/O0

"1"

Fail

Pass

READ STATUS

The device contains a Status Register which may be read to find out whether program or erase operation is completed, and whether

the program or erase operation is completed successfully. After writing 70h command to the command register, a read cycle outputs

the content of the Status Register to the I/O pins on the falling edge of CE

the system to poll the progress of each device in multiple memory connections even when R/B

does not need to be toggled for updated status. Refer to table 2 for specific Status Register definitions. The command register

remains in Status Read mode until further commands are issued to it. Therefore, if the status register is read during a random read

cycle, the read command(00h) should be given before starting read cycles.

or RE, whichever occurs last. This two line control allows

pins are common-wired. RE or CE

Table2. Read Staus Register Definition

I/O No. Page Program Block Erase Cache Prorgam Read Definition

I/O 0 Pass/Fail Pass/Fail Pass/Fail(N) Not use Pass : "0" Fail : "1"

I/O 1 Not use Not use Pass/Fail(N-1) Not use Pass : "0" Fail : "1"

I/O 2 Not use Not use Not use Not use Don’t -cared

I/O 3 Not Use Not Use Not Use Not Use Don’t -cared

I/O 4 Not Use Not Use Not Use Not Use Don’t -cared

I/O 5 Ready/Busy Ready/Busy True Ready/Busy Ready/Busy Busy : "0" Ready : "1"

I/O 6 Ready/Busy Ready/Busy Ready/Busy Ready/Busy Busy : "0" Ready : "1"

I/O 7 Write Protect Write Protect Write Protect Write Protect Protected : "0" Not Protected

NOTE : 1. True Ready/Busy represents internal program operation status which is being executed in cache program mode.

2. I/Os defined ’Not use’ are recommended to be masked out when Read Status is being executed.

34

Page 35

K9K2G08U0A

K9K2G08R0A

Read ID

The device contains a product identification mode, initiated by writing 90h to the command register, followed by an address input of

00h. Five read cycles sequentially output the manufacturer code(ECh), and the device code and XXh, 4th cycle ID, 15h respectively.

The command register remains in Read ID mode until further commands are issued to it. Figure 11 shows the operation sequence.

Figure 14. Read ID Operation

FLASH MEMORY

CLE

tCLR

tCEA

CE

WE

tAR1

ALE

RE

I/OX

90h

00h

Address. 1cycle

K9K2G08R0A AAh 15h

K9K2G08U0A DAh 15h

tWHR

Device Device Code*(2nd Cycle) 4th Cycle*

tREA

ECh

Maker code

Device

Code*

Device code

XXh 4th Cyc.*

RESET

The device offers a reset feature, executed by writing FFh to the command register. When the device is in Busy state during random

read, program or erase mode, the reset operation will abort these operations. The contents of memory cells being altered are no

longer valid, as the data will be partially programmed or erased. The command register is cleared to wait for the next command, and

the Status Register is cleared to value C0h when WP

already in reset state a new reset command will be accepted by the command register. The R/B

the Reset command is written. Refer to Figure 12 below.

is high. Refer to table 3 for device status after reset operation. If the device is

pin transitions to low for tRST after

Figure 15. RESET Operation

R/B

I/OX

FFh

tRST

Table3. Device Status

After Power-up After Reset

Operation Mode 00h command is latched Waiting for next command

35

Page 36

K9K2G08U0A

K9K2G08R0A

READY/BUSY

The device has a R/B output that provides a hardware method of indicating the completion of a page program, erase and random

read. The R/B

dom read is started after address loading. It returns to high when the internal controller has finished the operation. The pin is an opendrain driver thereby allowing two or more R/B

drain during busy(ibusy) , an appropriate value can be obtained with the following reference chart(Fig 13). Its value can be determined by the following guidance.

VCC

pin is normally high but transitions to low after program or erase command is written to the command register or ran-

outputs to be Or-tied. Because pull-up resistor value is related to tr(R/B) and current

Rp

ibusy

FLASH MEMORY

Ready Vcc

R/B

open drain output

CL

GND

Device

Figure 16. Rp vs tr ,tf & Rp vs ibusy

@ Vcc = 1.8V, Ta = 25°C , CL = 30pF

300n 3m

Ibusy

200n

100n

tr,tf [s]

1.70

30

1.70

0.85

60

tr

1.70

tf

90

1K 2K 3K

Rp(ohm)

1.70

0.57

120

0.43

1.70

4K

VOL : 0.1V, VOH : VCC-0.1V

VOL : 0.4V, VOH : 2.4V

VOL

Busy

tf

@ Vcc = 3.3V, Ta = 25°C , C

Ibusy [A]

2.4

300n 3m

tr,tf [s]

200n

2m

100n

1m

Ibusy

1.2

100

tr

50

1.8

1K 2K 3K

1.8

tf

Rp(ohm)

150

0.8

1.8

tr

= 50pF

L

VOH

200

0.6

1.8

4K

2m

1m

Ibusy [A]

Rp value guidance

V

Rp(min, 1.8V part) =

Rp(min, 3.3V part) =

where I

Rp(max) is determined by maximum permissible limit of tr

CC(Max.) - VOL(Max.)

IOL + ΣIL

V

CC(Max.) - VOL(Max.)

IOL + ΣIL

L is the sum of the input currents of all devices tied to the R/B pin.

=

3mA

+ ΣIL

3.2V

1.85V

=

8mA

+ ΣIL

36

Page 37

K9K2G08U0A

K9K2G08R0A

Data Protection & Power up sequence

The device is designed to offer protection from any involuntary program/erase during power-transitions. An internal voltage detector

disables all functions whenever Vcc is below about 1.1V(1.8V device) and 2V(3.3V device). WP

is recommended to be kept at V

cuit gets ready for any command sequences as shown in Figure 14. The two step command sequence for program/erase provides

additional software protection.

IL during power-up and power-down. A recovery time of minimum 10µs is required before internal cir-

Figure 17. AC Waveforms for Power Transition

FLASH MEMORY

pin provides hardware protection and

VCC

WP

WE

1.8V device: ~ 1.5V

3.3V device: ~ 2.5V

10µs

High

≈

1.8V device: ~ 1.5V

3.3V device: ~ 2.5V

≈

≈≈

37

Page 38

K9K2G08U0A

K9K2G08R0A

Extended Data Out Mode

For the EDO mode, the device should hold the data on the system memory bus until the beginning of the next cycle, so that controller

could fetch the data at the falling edge. However NAND flash dosen’t support the EDO mode exactly.

The device stops the data input into the I/O bus after RE

O data seems like Figure 18 and the system can access serially the data with EDO mode. tRLOH which is the parameter for fetching

data at RE falling time is necessary. Its appropriate value can be obtained with the reference chart as shown in Figure 19. The tRHOH

value depands on output load(C

L) and I/O bus Pull-up resistor (Rp).

rising edge. But since the previous data remains in the I/O bus, the flow of I/

Figure 18. Serial Access Cycle after Read(EDO Type, CLE=L, WE=H, ALE=L)

CE

≈

≈

RE

tRP

tRC

tREH

FLASH MEMORY

I/Ox

R/B

VCC

GND

tRR

I/O Drive

tREA

tCEA

tREA

tRLOH

≈

Dout Dout

tRHOH

≈

≈

NOTES : Transition is measured at ±200mV from steady state voltage with load.

This parameter is sampled and not 100% tested.

Figure 19. Rp vs tRHOH vs CL

Rp

@ Vcc = 3.3V, Ta = 25

tRHOH

600n

500n

360

180

36

18

30p 50p 70p

Device

CL

400n

300n

200n

100n

50n

tRLOH / tRHOH value guidance

600

300

60

Rp = 100k

30

°C

425

85

tRHOH

600

Rp = 50k

120

Rp = 10k

Rp = 5k

100p

60

C

(F)

L

42

tRHOH = CL * VOL * Rp / Vcc

tRLOH(min, 3.3V part) = tRHOH - tREH

38

Page 39

®

ISL6294

Data Sheet February 18, 2005

High Input Voltage Charger

The ISL6294 is a cost-effective, fully integrated high input

voltage single-cell Li-ion battery charger. The charger uses a

CC/CV charge profile required by Li-ion batteries. The

charger accepts an input voltage up to 28V but is disabled

when the input voltage exceeds the OVP threshold, typically

6.8V, to prevent excessive power dissipation. The 28V rating

eliminates the overvoltage protection circuit required in a low

input voltage charger.

The charge current and the end-of-charge (EOC) current are

programmable with external resistors. When the battery

voltage is lower than typically 2.55V, the charger

preconditions the battery with typically 20% of the

programmed charge current. When the charge current

reduces to the programmable EOC current level during the

CV charge phase, an EOC indication is provided by the CHG

pin, which is an open-drain output. An internal thermal

foldback function protects the charger from any thermal

failure.

Two indication pins (PPR and CHG) allow simple interface to

a microprocessor or LEDs. When no adapter is attached or

when disabled, the charger draws less than 1µA leakage

current from the battery.

FN9174.0

Features

• Complete Charger for Single-Cell Li-ion/Polymer Batteries

• Integrated Pass Element and Current Sensor

• No External Blocking Diode Required

• Low Component Count and Cost

• 1% Voltage Accuracy

• Programmable Charge Current

• Programmable End-of-Charge Current

• Charge Current Thermal Foldback for Thermal

Protection

• Trickle Charge for Fully Discharged Batteries

• 28V Maximum Voltage for the Power Input

• Power Presence and Charge Indications

• Less Than 1µA Leakage Current off the Battery When No

Input Power Attached or Charger Disabled

• Ambient Temperature Range: -40°C to 85°C

• 2x3 DFN-8 Packages

• Pb-Free Available (RoHS Compliant)

Ordering Information

PART

NUMBER

ISL6294IRZ (Note) -40 to 85 8 Ld 2x3 DFN

ISL6294IRZ-T (Note) -40 to 85 8 Ld 2x3 DFN

NOTE: Intersil Pb-free products employ special Pb-free material

sets; molding compounds/die attach materials and 100% matte tin

plate termination finish, which are RoHS compliant and compatible

with both SnPb and Pb-free soldering operations. Intersil Pb-free

products are MSL classified at Pb-free peak reflow temperatures that

meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

TEMP.

RANGE (°C) PACKAGE

(Pb-free)

(Pb-free)

PKG.

DWG. #

L8.2x3

L8.2x3

Applications

• Mobile Phones

• Blue-Tooth Devices

•PDAs

• MP3 Players

• Stand-Alone Chargers

• Other Handheld Devices

Pinout

DFN 8 LEAD

VIN

1

PPR

2

CHG

3

EN

4

TOP VIEW

BAT

8

IREF

7

IMIN

6

GND

5

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-352-6832

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

All other trademarks mentioned are the property of their respective owners.

Copyright Intersil Americas Inc. 2005. All Rights Reserved

Page 40

ISL6294

Absolute Maximum Ratings (Reference to GND) Thermal Information

VIN. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to 30V

IMIN, IREF, BAT, CHG, EN, PPR . . . . . . . . . . . . . . . . . . . -0.3V to 7V

ESD Rating

Human Body Model (Per EIA JESD22 Method A114-B) . . . . .3kV

Machine Model (Per EIA JED-4701 Method C-111) . . . . . . . . 200V

Recommended Operating Conditions

Ambient Temperature Range . . . . . . . . . . . . . . . . . . . .-40°C to 85°C

Maximum Supply Voltage (VIN Pin). . . . . . . . . . . . . . . . . . . . . . 28V

Operating Supply Voltage (VIN Pin). . . . . . . . . . . . . . . . 4.5V to 6.5V

Programmed Charge Current . . . . . . . . . . . . . . . . 100mA to 700mA

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

is measured in free air with the component mounted on a high effective thermal conductivity test board with “direct attach” features. See

1. θ

JA

Tech Brief TB379.

2. For θ

, the “case temp” location is the center of the exposed metal pad on the package underside.

JC

Electrical Specifications Typical Values Are Tested at VIN = 5V and the Ambient Temperature at 25°C. All Maximum and Minimum

Values Are Guaranteed Under the Recommended Operating Supply Voltage Range and Ambient Temperature

Range, Unless Otherwise Noted.

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

POWER-ON RESET

Rising POR Threshold V

Falling POR Threshold V

VIN-BAT OFFSET VOLTAGE

Rising Edge V

Falling Edge V

OVER VOLTAGE PROTECTION

Over Voltage Protection Threshold V

OVP Threshold Hysteresis 100 240 400 mV

STANDBY CURRENT

BAT Pin Sink Current I

VIN Pin Supply Current I

VIN Pin Supply Current I

VOLTAGE REGULATION

Output Voltage V

PMOS On Resistance r

CHARGE CURRENT (Note 5)

IREF Pin Output Voltage I

Constant Charge Current I

Trickle Charge Current I

End-of-Charge Current I

EOC Rising Threshold R

PRECONDITIONING CHARGE THRESHOLD

Preconditioning Charge Threshold Voltage V

Preconditioning Voltage Hysteresis V

POR

POR

OVP

VBAT = 3.0V, use PPR to indicate the

comparator output.

OS

V

comparator output (Note 3)

OS

(Note 4)

Use PPR to indicate the comparator output

STANDBY

VIN

VIN

DS(ON)VBAT

IREF

CHG

TRK

MIN

MIN

MINHYS

Charger disabled or the input is floating - - 1.0 µA

Charger disabled - 300 400 µA

Charger enabled - 400 600 µA

4.3V < V

CH

V

R

R

R

= 4.0V, use CHG pin to indicate the

BAT

IN

= 3.8V, charge current = 0.5A - 0.6 - Ω

= 3.8V 1.18 1.22 1.26 V

BAT

= 24.3kΩ, V

IREF

= 24.3kΩ, V

IREF

= 243kΩ 33 45 57 mA

IMIN

= 243kΩ 325 380 415 mA

IMIN

Thermal Resistance θ

(°C/W) θJC (°C/W)

JA

DFN Package (Notes 1, 2) . . . . . . . . . . 78 11

Maximum Junction Temperature (Plastic Package) . . . . . . . . 150°C

Maximum Storage Temperature Range . . . . . . . . . . . -65°C to 150°C

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300°C

3.3 3.9 4.3 V

3.1 3.6 4.15 V

- 90 150 mV

10 50 - mV

6.5 6.8 7.1 V

< 6.5V, charge current = 20mA 4.158 4.20 4.242 V

= 2.8V - 4.0V 450 500 550 mA

BAT

= 2.4V 70 95 130 mA

BAT

2.45 2.55 2.65 V

40 100 150 mV

2

FN9174.0

February 18, 2005

Page 41

ISL6294

Electrical Specifications Typical Values Are Tested at VIN = 5V and the Ambient Temperature at 25°C. All Maximum and Minimum

Values Are Guaranteed Under the Recommended Operating Supply Voltage Range and Ambient Temperature

Range, Unless Otherwise Noted. (Continued)

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

INTERNAL TEMPERATURE MONITORING

Charge Current Foldback Threshold

(Note 6)

LOGIC INPUT AND OUTPUTS

EN Pin Logic Input High 1.3 - - V

EN Pin Logic Input Low --0.5V

EN Pin Internal Pull Down Resistance 100 200 400 kΩ

CHG Sink Current when LOW Pin Voltage = 1V 10 20 - mA

CHG Leakage Current When HIGH V

PPR Sink Current when LOW Pin Voltage = 1V 10 20 - mA

PPR Leakage Current When HIGH V

NOTES:

3. The 4.0V V

than the POR threshold, no output pin can be used for indication.

4. For junction temperature below 100 °C.

5. The charge current can be affected by the thermal foldback function if the IC under the test setup cannot dissipate the heat.

6. This parameter is guaranteed by design, not tested.

is selected so that the CHG output can be used as the indication for the offset comparator output indication. If the V

BAT

T

FOLD

100 115 130 °C

= 6.5V - - 1 µA

CHG

6= 6.5V - - 1 µA

PPR

BAT

is lower

Pin Descriptions

VIN - Power input. The absolute maximum input voltage is

28V. A 0.47µF or larger value X5R ceramic capacitor is

recommended to be placed very close to the input pin for

decoupling purpose. Additional capacitance may be required

to provide a stable input voltage.

PPR - Open-drain power presence indication. The opendrain MOSFET turns on when the input voltage is above the

POR threshold but below the OVP threshold and off

otherwise. This pin is capable to sink 10mA (minimum)

current to drive an LED. The maximum voltage rating for this

pin is 7V. This pin is independent on the EN-pin input.

CHG - Open-drain charge indication pin. This pin outputs a

logic LOW when a charge cycle starts and turns to HIGH

when the end-of-charge (EOC) condition is qualified. This

pin is capable to sink 10mA min. current to drive an LED.

When the charger is disabled, the CHG outputs high

impedance.

EN - Enable input. This is a logic input pin to disable or

enable the charger. Drive to HIGH to disable the charger.

When this pin is driven to LOW or left floating, the charger is

enabled. This pin has an internal 200kΩ pull-down resistor.

current. The EOC current IMIN can be programmed by the

following equation:

11000

----------------

I

MIN

Where R

R

IMIN

is in kΩ. The programmable range covers 5%

IMIN

mA()=

(or 10mA, whichever is higher) to 50% of IREF. When

programmed to less than 5% or 10mA, the stability is not

guaranteed.

IREF - Charge-current program and monitoring pin. Connect

a resistor between this pin and the GND pin to set the

charge current limit determined by the following equation:

I

REF

Where R

-----------------

R

IREF

is in kΩ. The IREF pin voltage also monitors

IREF

mA()=

12089

the actual charge current during the entire charge cycle,

including the trickle, constant-current, and constant-voltage

phases. When disabled, VIREF = 0V.

BAT - Charger output pin. Connect this pin to the battery. A

1µF or larger X5R ceramic capacitor is recommended for

decoupling and stability purposes. When the EN pin is pulled

to logic HIGH, the BAT output is disabled.

GND - System ground.

IMIN - End-of-charge (EOC) current program pin. Connect a

resistor between this pin and the GND pin to set the EOC

3

EPAD - Exposed pad. Connect as much as possible copper

to this pad either on the component layer or other layers

through thermal vias to enhance the thermal performance.

FN9174.0

February 18, 2005

Page 42

Typical Applications

ISL6294

TO INPUT

C

1

OFF

ON

VIN

EN

FIGURE 1. TYPICAL APPLICATION CIRCUIT INTERFACING TO INDICATION LEDs

COMPONENT DESCRIPTION FOR FIGURE 1

PART DESCRIPTION

C

C

R

IREF

R

IMIN

R1, R

D

, D

1

1

2

1µF X5R ceramic cap

1µF X5R ceramic cap

24.3kΩ, 1%, for 500mA charge current

243kΩ, 1%, for 45mA EOC current

300Ω, 5%

2

LEDs for indication

2

ISL6294

BAT

IREF

IMIN

CHG

PPR

GND

TO BATTERY

R

R

IREF

IMIN

R

R

1

2

C

2

D

D

1

2

COMPONENT DESCRIPTION FOR FIGURE 2

PART DESCRIPTION

C

C

R

IREF

R

IMIN

R1, R

1

2

1µF X5R ceramic cap

1µF X5R ceramic cap

24.3kΩ, 1%, for 500mA charge current

243kΩ, 1%, for 45mA EOC current

100kΩ, 5%

2

TO INPUT

C

1

ON

OFF

VIN

EN

GND

ISL6294

BAT

IREF

IMIN

CHG

PPR

R

R

IREF

IMIN

R

1

TO BATTERY

VCC

R

2

C

2

TO MCU

FIGURE 2. TYPICAL APPLICATION CIRCUIT WITH THE INDICATION SIGNALS INTERFACING TO A MCU

4

FN9174.0

February 18, 2005

Page 43

ISL6294

VIN

PPR

EN

GND

BAT

V

OS

V

REF

POR

PRE

REG

200K

VCC

IMIN IREF

CHG

BAT

CHARGE

CONTROL

EN

VCC

V

REF

DIE

TEMP

115°C

FIGURE 3. BLOCK DIAGRAM

TRICKLE CC CV

4.2V

I

REF

CHARGE

VOLTAGE

2.55V

19%I

REF

CHG

FIGURE 4. TYPICAL CHARGE PROFILE

Description

The ISL6294 charges a Li-ion battery using a CC/CV profile.

The constant current I

R

(See Figure 1) and the constant voltage is fixed at

IREF

4.2V. If the battery voltage is below a typical 2.55V tricklecharge threshold, the ISL6294 charges the battery with a

trickle current of 19% of I

above the trickle charge threshold. Fast charge CC mode is

maintained at the rate determined by programming I

the cell voltage rises to 4.2V. When the battery voltage

is set with the external resistor

REF

until the battery voltage rises

REF

REF

until

76%I

REF

CHARGE

CURRENT

I

MIN

CHG

INDICATION

TIME

reaches 4.2V, the charger enters a CV mode and regulates

the battery voltage at 4.2V to fully charge the battery without

the risk of over charge. Upon reaching an end-of-charge

(EOC) current, the charger indicates the charge completion

with the CHG pin, but the charger continues to output the

4.2V voltage. Figure 4 shows the typical charge waveforms

after the power is on.

The EOC current level IMIN is programmable with the

external resistor R

(See Figure 1). The CHG signal turns

IMIN

5

FN9174.0

February 18, 2005

Page 44

ISL6294

to LOW when the trickle charge starts and rises to HIGH at

the EOC. After the EOC is reached, the charge current has

to rise to typically 76% I

again, as shown in Figure 4. The current surge after EOC

can be caused by a load connected to the battery.

A thermal foldback function reduces the charge current

anytime when the die temperature reaches typically 115°C.

This function guarantees safe operation when the printedcircuit board (PCB) is not capable of dissipating the heat

generated by the linear charger. The ISL6294 accepts an

input voltage up to 28V but disables charging when the input

voltage exceeds the OVP threshold, typically 6.8V, to protect

against unqualified or faulty ac adapters.

for the CHG signal to turn on

REF

PPR Indication

The PPR pin is an open-drain output to indicate the

presence of the ac adapter. Whenever the input voltage is

higher than the POR threshold, the PPR pin turns on the

internal open-drain MOSFET to indicate a logic LOW signal,

independent on the EN-pin input. When the internal opendrain FET is turned off, the PPR pin should leak less than

1µA current. When turned on, the PPR pin should be able to

sink at least 10mA current under all operating conditions.

The PPR pin can be used to drive an LED (see Figure 1) or

to interface with a microprocessor.

Power-Good Range

The power-good range is defined by the following three

conditions:

1. VIN > VPOR

2. VIN - VBAT > VOS

3. VIN < VOVP

where the VOS is the offset voltage for the input and output

voltage comparator, discussed shortly, and the VOVP is the