Philips HEF4059BU, HEF4059BT, HEF4059BPB, HEF4059BP, HEF4059BD Datasheet

DATA SH EET

Product specification

File under Integrated Circuits, IC04

January 1995

INTEGRATED CIRCUITS

HEF4059B

LSI

Programmable divide-by-n counter

For a complete data sheet, please also download:

•The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

•The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

January 1995 2

Philips Semiconductors Product specification

Programmable divide-by-n counter

HEF4059B

LSI

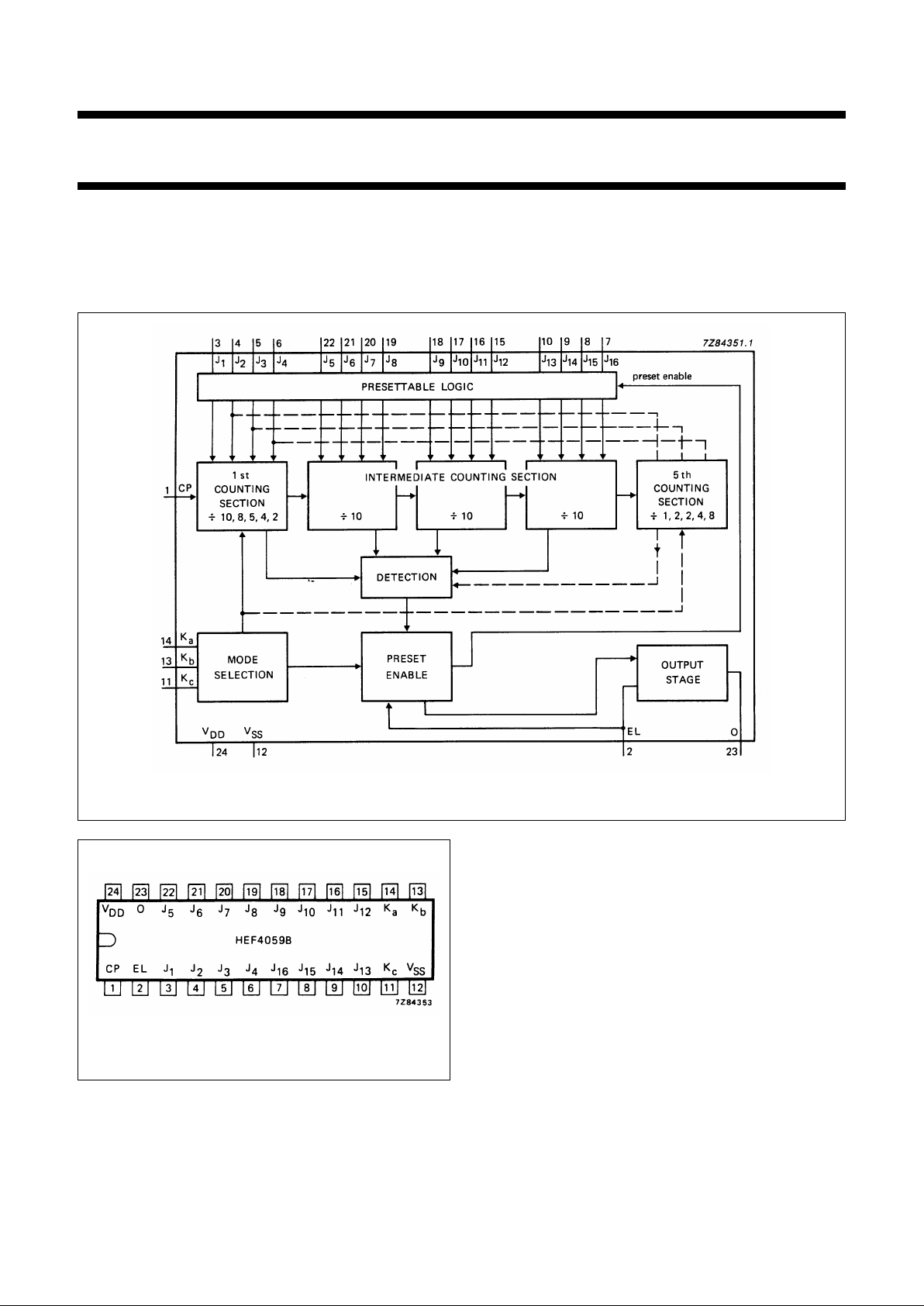

DESCRIPTION

The HEF4059B is a divide-by-n counter which can be

programmed to divide an input frequency by any number

n

from 3 to 15 999. The output signal is a one clock-cycle

wide pulse and occurs at a rate equal to the input

frequency divided by

n

. The single output (O) has TTL

drive capability. The down counter is preset by means of

16 jam inputs (J1 to J16); continued on next page.

Fig.1 Functional block diagram.

FAMILY DATA, IDDLIMITS category LSI

See Family Specifications

Fig.2 Pinning diagram.

PINNING

CP clock input

K

a

, Kb, K

c

mode select inputs

J

1

to J

16

programmable jam inputs (BCD)

EL latch enable input

O divide-by-n output

HEF4059BP(N): 24-lead DIL; plastic (SOT101-1)

HEF4059BD(F): 24-lead DIL; ceramic (cerdip) (SOT94)

HEF4059BT(D): 24-lead SO; plastic (SOT137-1)

( ): Package Designator North America

Loading...

Loading...