Page 1

Compact disc recorder CDR775

/00

OPEN / CLOSE

OPEN / CLOSE

OPEN / CLOSE

PLAY / PAUSE

PLAY / PAUSE

PLAY / PAUSE

STOP

STOP

STOP

AUDIO CD RECORDABLE/REWRITABLE

AUDIO CD RECORDABLE/REWRITABLE

AUDIO CD RECORDABLE/REWRITABLE

ON / OFF

REC

RECORD

TYPE

EXT

EXT

FINALIZE

ERASEFINALIZE

ERASE

SOURCE

SOURCE

R

e

c

o

r

d

a

b

l

e

DOUBLE SPEED

EASY JOG

EASY JOG

STORE/

STORE/

5

CDR

REM

REC

TIME

TRACK

TOTAL

REM

T

RACK

2

3

MANUAL

I

I

SHUFFLE

4

567

CD

R

W

8

9

1011

12

13

RECORD

CHANGER

CDR775 AUDIO CD RECORDER

DISPLAY

SCROLL

TIME

14

15

16

17

CD

RW

DJ MODE

REPEAT

1

SYNC

DIGITAL

OPTICAL

ANALOG

PROG

5

CD

STEP

18

19

20

+

PROG

A-B

SHUFFLE

ALL

REPEAT

S

CAN

TRACK

PHONES

CANCEL/

CANCEL/

6

J

6

J

K

K

MENU

PLAY/PAUSE

MENU

PLAY/PAUSE

DELETE

DELETE

STOP

STOP

OPEN/CLOSE

AUDIO CD PLAYBACK

AUDIO CD PLAYBACK

IR SENSOR

OPEN/CLOSE

CL 96532086_000.eps

080999

ENTER

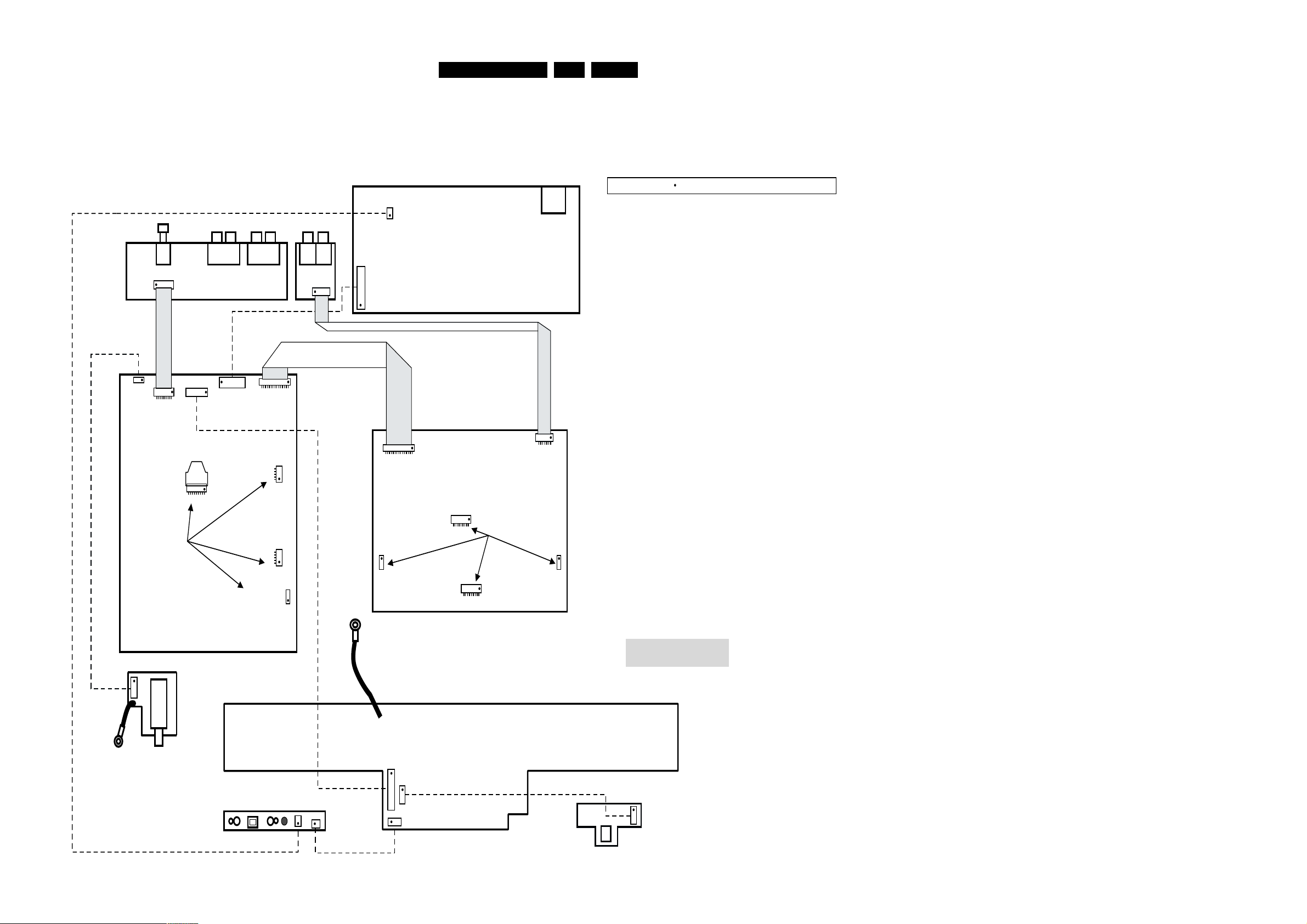

SERVICING

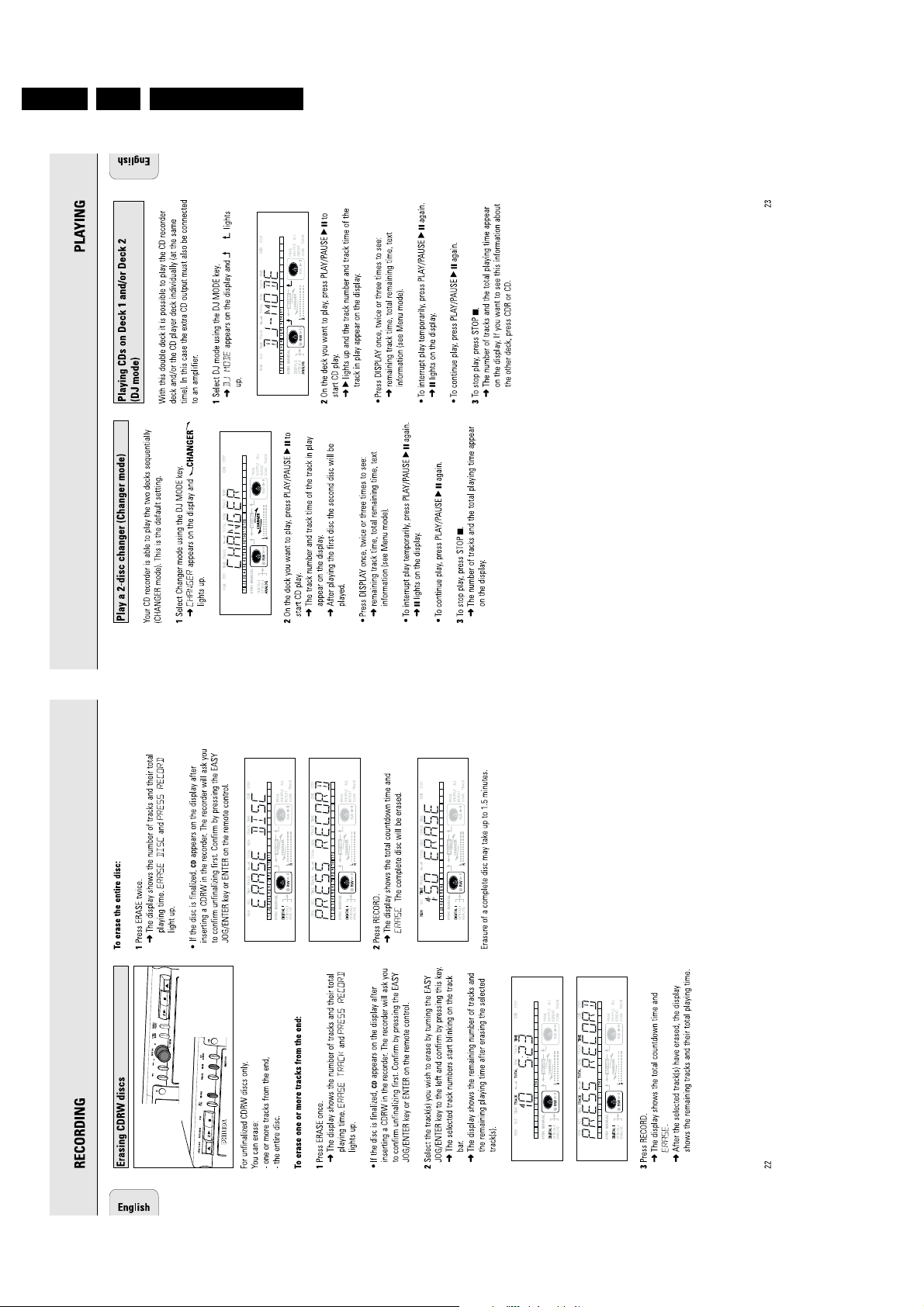

For servicing CDR775, the set can divided into three parts.

1. The display board (partly) 1 002, the I/O board 1004, the

headphone board (partly) 1002, the IR board (partly) 1002, the ON/

OFF & Standby LED board (partly) 1002 and the CD-out board

(partly) 1002 have to be repaired at component level. The power

supply unit 1003 is available as spare part, but can also be repaired

at component level.

2. The CDR module (containing the CDR loader 81, CDR main board

1001 and loader bracket 82, 83) will be exchanged completely in

case of failure. This complete CDR module is available as spare

part. Defective modules have to be returned for central repair.

3. The CD module (containing the CD loader 131, CD main board

1005 and loader bracket 132) is a new module with VAL1250

loader assy but also a separate CDM and separate loader parts will

be available via service stock. The CD main board can be repaired

at component level.

Also available: Circuit Description " The Basics of Compact Disc

Recordable/Rewriteable". Service code number 4822 725 25242.

Contents Page

1. Technical Specifications 2

2. Warning and Servicing Hints 4

3. User Instructions 7

4. Mechanical Instructions 19

Wiring Diagram CDR 19

Wiring Diagram CD loader 20

Exploded View CDR 21

Exploded View CD loader 22

Dismantling Instructions 23

5. Electrical and Circuit Diagrams

Diagram PWB

Overall Blockdiagram 24

Display Board 26 26

IR / On/Off &Standby LED Board 27 27

Headphone / CD-out Board 28 28

I/O Board 29 30

Power supply unit 31 32

CD-Mainboard 1A 33 37/38

CD-Mainboard 1B 34 37/38

CD-Mainboard 1C 35 37/38

CD-Mainboard 2 36 37/38

6. Diagnostic Software 39

7. Faultfinding Trees 43

8. Faultfinding Guide 49

9. List of Abbreviations 65

10. Partslist (mechanical and electrical) 71

©

Copyright reserved 1999 Philips Consumer Electronics B.V. Eindhoven, The

Netherlands. All rights reserved. No part of this publication may be reproduced,

stored in a retrieval system or transmitted, in any form or by any means, electronic,

mechanical, photocopying, or otherwise without the prior permission of Philips.

Published by RH 9969 Service DPS Hasselt Printed in the Netherlands Subject to modification 5 3104 125 40030

Page 2

GB 2 CDR7751.

Technical Specifications CDR775

1. Technical Specifications CDR775

1.1 General

Mains voltage : all range version 84-

230V (/00, /01C, /06, /

13, /14)

: USA version 117V/

60Hz (/17)

Mains frequency : 50-60 Hz

Power consumption : 12W

DC output : +5V ± 10%, 50mA

max.

1.2 Input/output

1.2.1 Line output (CDR & CD)

Output level\ : 2Vrms at 0dB

Output resistance : 200

1.2.2 Line input

Input sensitivity : 500mVrms

Input impedance : 50k

Max. input voltage : 2.5Vrms

1.2.3 Digital output (CDR & CD)

Format : AES/EBU format

according IEC958

(consumer format)

Sampling frequency : 44.1kHz

Output resistance : 75

1.2.4 Digital input

Format : AES/EBU format

according IEC958

(consumer format)

Sampling frequency : 32 to 48kHz

Input resistance : 75

1.2.5 Optical input

Format : AES/EBU format

according IEC958

(consumer format)

Sampling frequency : 32 to 48kHz

1.3 Audio performance

1.3.1 Cinch analog output (CDR play-back)

Output voltage : 2Vrms ± 2dB (0dB

signal)

Frequency range F.R. : 20Hz < F.R.< 20kHz

Amplitude linearity :± 0.3dB (typical ±

0.1dB)

Channel unbalance : < 0.3dB at 1kHz

(typical ± 0.2dB)

Output resistance : 200

Phase non-linearity : < 0.2 deg at 1kHz

Outband attenuation : 50dB above 30kHz

Channel separation : > 90dB at 1kHz

(typical 110dB),

>85dB between 20Hz

and 20kHz (typical

S/N-ratio A-weighted : > 98dB (typical

S/N-ratio unweighted : > 95dB (typical 98dB)

Dynamic range : > 92dB at 1kHz

THD+N : >85dB between 20Hz

1.3.2 Cinch analog input/output (monitor path CDR)

Measured with Audio precision system one.

Input voltage is 1Vrms.

Output voltage : 2Vrms ± 2dB (0dB

Ω

Ω

Ω

Ω

Ω

Frequency range F.R. : 20Hz < F.R.< 20kHz

Amplitude linearity :± 0.3dB (typical ±

Channel unbalance : < 0.3dB at 1kHz

Output resistance : 200

Phase non-linearity : < 0.2 deg at 1kHz

Outband attenuation : 50dB above 30kHz

Channel separation : > 90dB at 1kHz

S/N-ratio A-weighted : > 90dB (typical 88dB)

Dynamic range : > 85dB at 1kHz

THD+N : > 80dB between 20Hz

Intermodulation THD : > 80dB

1.3.3 Cinch analog output (CD play-back)

Output voltage : 2Vrms ± 2dB (0dB

Frequency range F.R. : 20Hz < F.R.< 20kHz

Amplitude linearity :± 0.3dB (typical ±

Channel unbalance : < 0.3dB at 1kHz

Output resistance : 200

Phase non-linearity : < 0.2 deg at 1kHz

Outband attenuation : 50dB above 30kHz

Channel separation : > 90dB at 1kHz

S/N-ratio A-weighted : > 98dB (typical

S/N-ratio unweighted : > 94dB (typical 98dB)

Dynamic range : > 92dB at 1kHz

THD+N : > 82dB between 20Hz

>93dB)

100dB)

(typical 96dB), > 90dB

between 20Hz and

20kHz (typical 96dB)

and 20kHz (typical

91dB)

signal)

0.1dB)

(typical ± 0.2dB)

Ω

(typical 98dB), > 85dB

between 20Hz and

20kHz (typical >92dB)

(typical 90dB)

and 20kHz (typical

82dB)

signal)

0.1dB)

(typical ± 0.2dB)

Ω

(typical 100dB),

>85dB between 20Hz

and 20kHz (typical

>93dB)

100dB)

(typical 96dB), > 90dB

between 20Hz and

20kHz (typical 96dB)

and 20kHz (typical

85dB)

Page 3

Technical Specifications CDR775

1.3.4 Headphone output (all functions)

GB 3CDR775 1.

Output voltage : 3Vrms (0dB)/8-2000

S/N : > 80dB

THD+N : > 78dB

Channel separation : > 60dB between 20Hz

and 20kHz

1.4 Laser device

Material : GaAlAs

Wave length : between 780 and

800nm (at 25°C)

Laser output : 1mW max. during

reading, 20mW max.

during writing

Class : 3B

1.5 Dimensions and weight

Number and height of feet : 4x11mm foiled

Apparatus tray closed (WxDxH) : 435x305x75mm

(without feet)

Weight without packaging : 3.2kg

Weight with packaging : 4.2kg

Ω

Page 4

GB 4 CDR7752.

Warnings and Servicing Hints

2. Warnings and Servicing Hints

GB

WARNING

All ICs and many other semi-conductors are

susceptible to electrostatic discharges (ESD).

Careless handling during repair can reduce

life drastically.

When repairing, make sure that you are

connected with the same potential as the

mass of the set via a wrist wrap with

resistance.

Keep components and tools also at this

potential.

F

ATTENTION

Tous les IC et beaucoup d'autres semiconducteurs sont sensibles aux décharges

statiques (ESD).

Leur longévité pourrait être considérablement

écourtée par le fait qu'aucune précaution

n'est prise a leur manipulation.

Lors de réparations, s'assurer de bien être

relié au même potentiel que la masse de

l'appareil et enfiler le bracelet serti d'une

résistance de sécurité.

Veiller a ce que les composants ainsi que les

outils que l'on utilise soient également a ce

potentiel.

D

Alle IC und viele andere Halbleiter sind

empfindlich gegen elektrostatische

Entladungen (ESD).

Unsorgfältige Behandlung bei der Reparatur

kann die Lebensdauer drastisch vermindern.

Sorgen sie dafür, das Sie im Reparaturfall

über ein Pulsarmband mit Widerstand mit

dem Massepotential des Gerätes verbunden

sind.

Halten Sie Bauteile und Hilfsmittel ebenfalls

auf diesem Potential.

GB

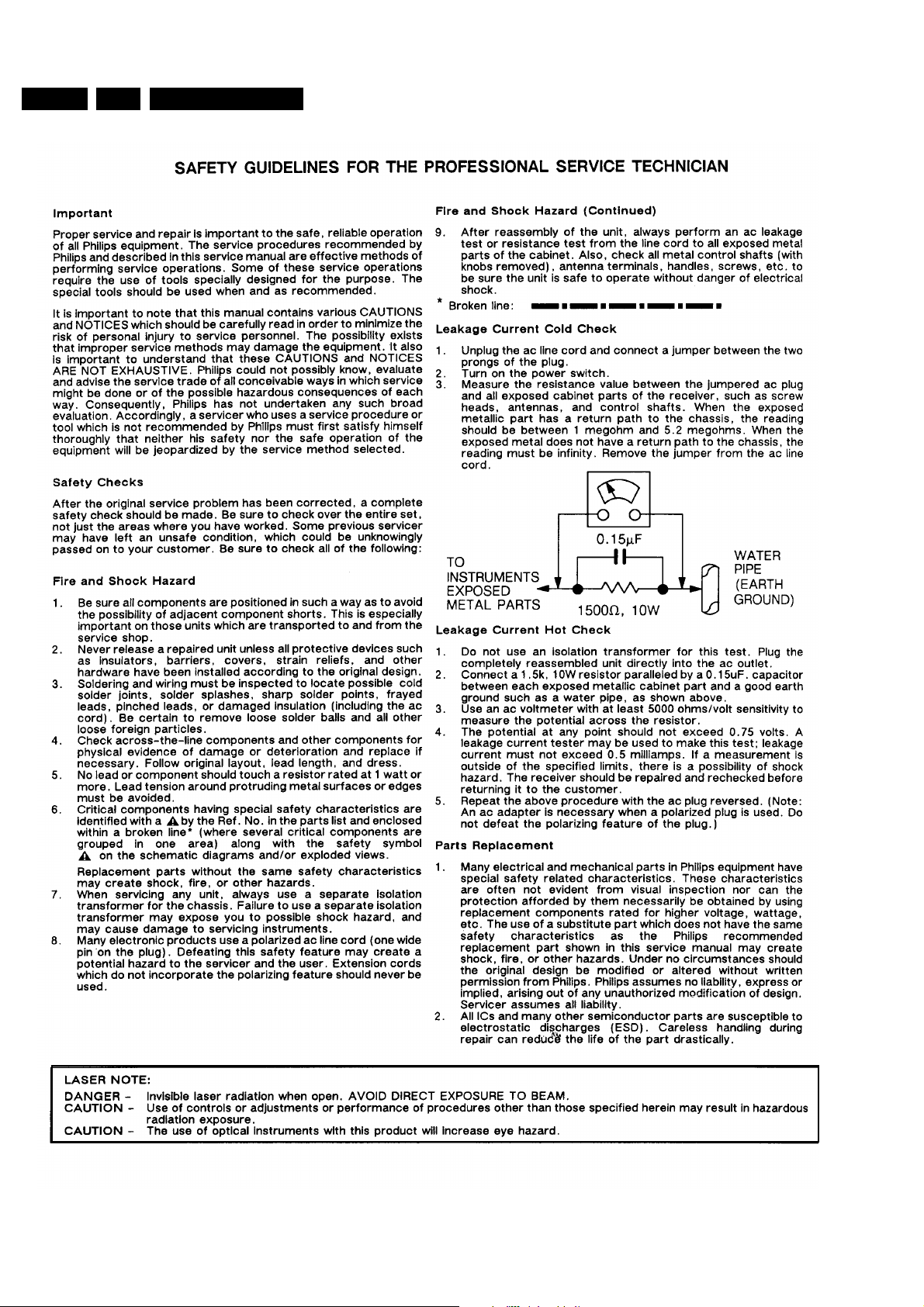

Safety regulations require that the set be restored to its original condition

and that parts which are identical with those specified be used.

NL

Veiligheidsbepalingen vereisen, dat het apparaat in zijn oorspronkelijke

toestand wordt terug gebracht en dat onderdelen, identiek aan de

gespecifieerde worden toegepast.

F

Les normes de sécurité exigent que l'appareil soit remis a l'état d'origine et

que soient utilisées les pièces de rechange identiques à celles spécifiées.

WARNUNG

NL

WAARSCHUWING

Alle IC's en vele andere halfgeleiders zijn

gevoelig voor elektrostatische ontladingen

(ESD).

Onzorgvuldig behandelen tijdens reparatie

kan de levensduur drastisch doen

verminderen.

Zorg ervoor dat u tijdens reparatie via een

polsband met weerstand verbonden bent met

hetzelfde potentiaal als de massa van het

apparaat.

Houd componenten en hulpmiddelen ook op

ditzelfde potentiaal.

I

AVVERTIMENTO

Tutti IC e parecchi semi-conduttori sono

sensibili alle scariche statiche (ESD).

La loro longevita potrebbe essere fortemente

ridatta in caso di non osservazione della piu

grande cauzione alla loro manipolazione.

Durante le riparazioni occorre quindi essere

collegato allo stesso potenziale che quello

della massa dell'apparecchio tramite un

braccialetto a resistenza.

Assicurarsi che i componenti e anche gli

utensili con quali si lavora siano anche a

questo potenziale.

D

Bei jeder Reparatur sind die geltenden Sicherheitsvorschriften zu beachten.

Der Originalzustand des Gerats darf nicht verandert werden.

Fur Reparaturen sind Original-Ersatzteile zu verwenden.

I

Le norme di sicurezza esigono che l'apparecchio venga rimesso nelle

condizioni originali e che siano utilizzati pezzi di ricambiago idetici a quelli

specificati.

SHOCK, FIRE HAZARD SERVICE TEST:

CAUTION: After servicing this appliance and prior to returning to customer, measure the resistance between

either primary AC cord connector pins (with unit NOT connected to AC mains and its Power switch ON), and the

face or Front Panel of product and controls and chassis bottom,

Any resistance measurement less than 1 Megohms should cause unit to be repaired or corrected before AC

power is applied, and verified before return to user/customer.

Ref.UL Standard NO.1492.

NOTE ON SAFETY:

Symbol

: Fire or electrical shock hazard. Only original parts should be used to replace any part with symbol

Any other component substitution(other than original type), may increase risk or fire or electrical shock hazard.

“Pour votre sécurité, ces documents

doivent être utilisés par des

spécialistes agrées, seuls habilités à

réparer votre appareil en panne.”

CL 96532086_021.eps

080999

Page 5

Warnings and Servicing Hints

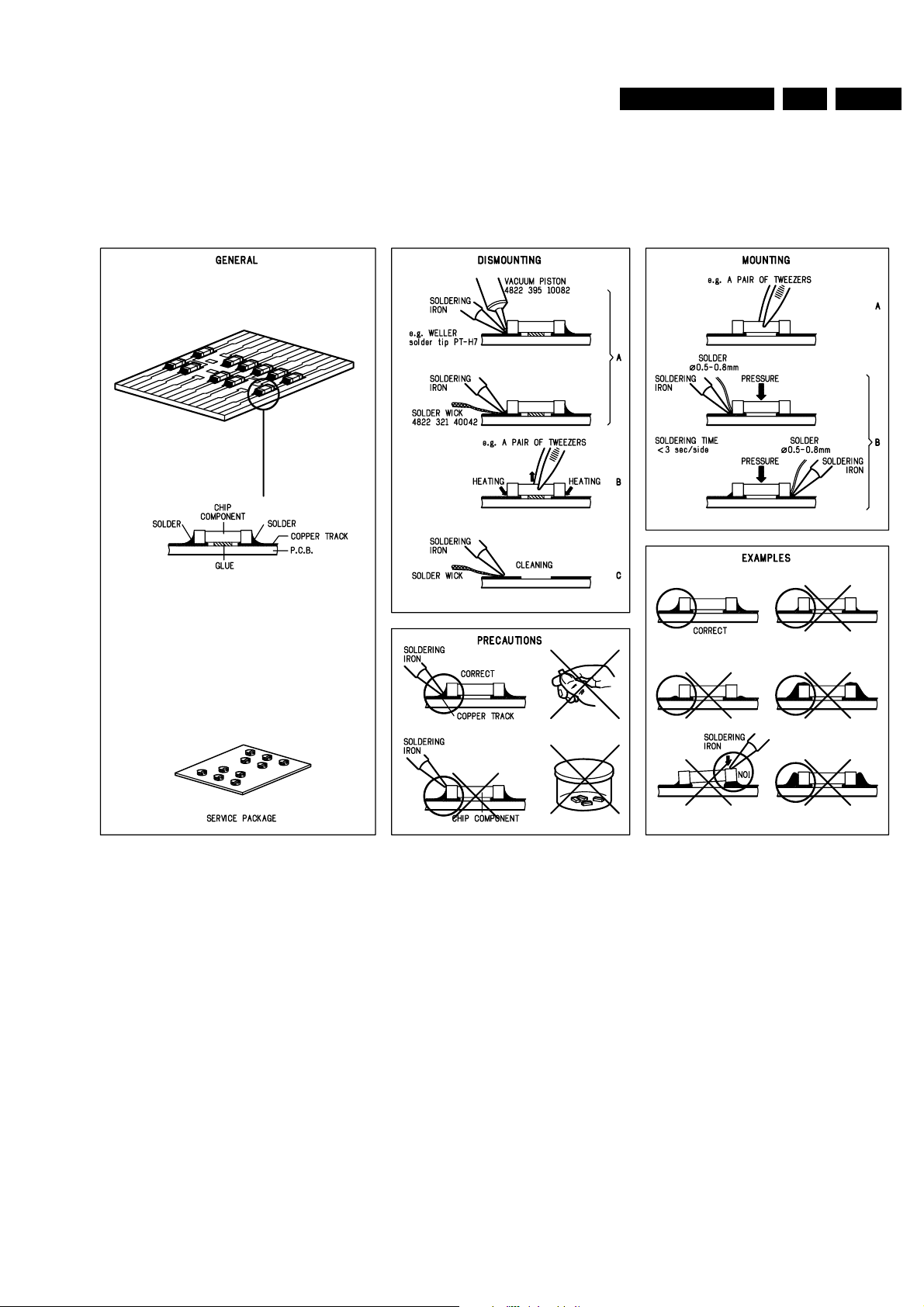

SERVICING HINTS

In the set, chip components have been applied. For disassembly and assembly check the figure below.

GB 5CDR775 2.

CL 96532086_022.eps

080999

Page 6

GB 6 CDR7752.

Warnings and Servicing Hints

CL 96532086_023.eps

080999

Page 7

User instructions

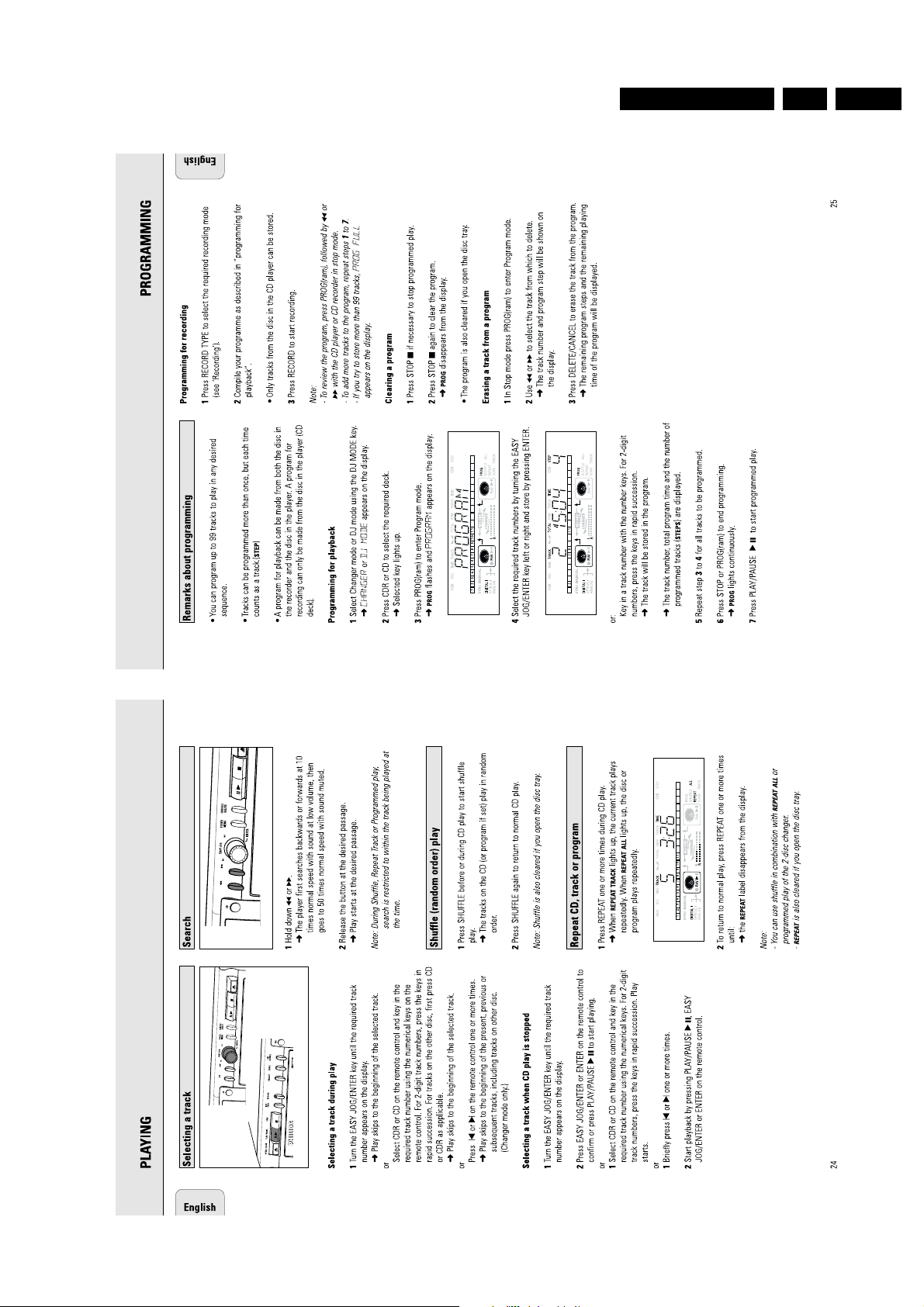

3. User instructions

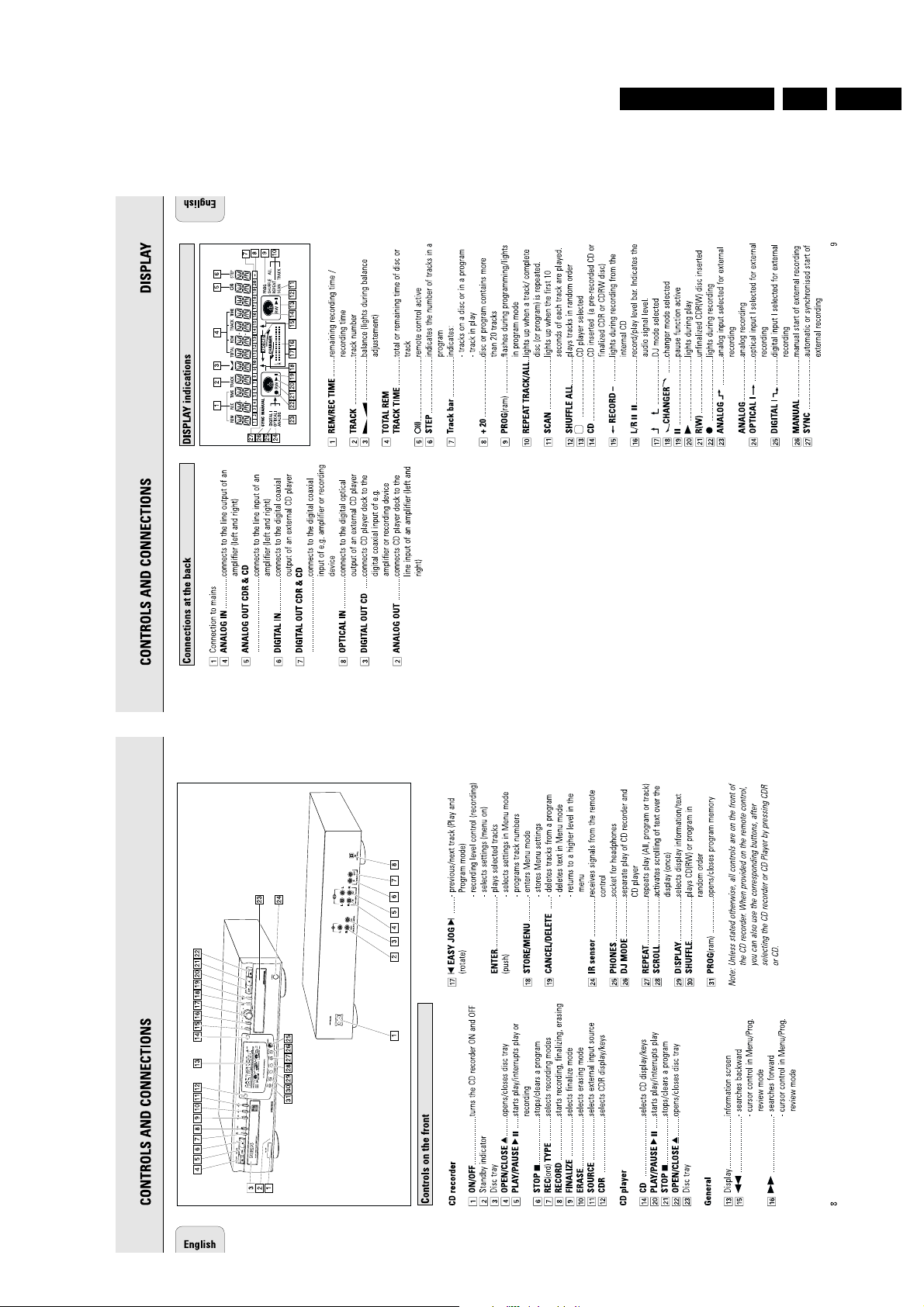

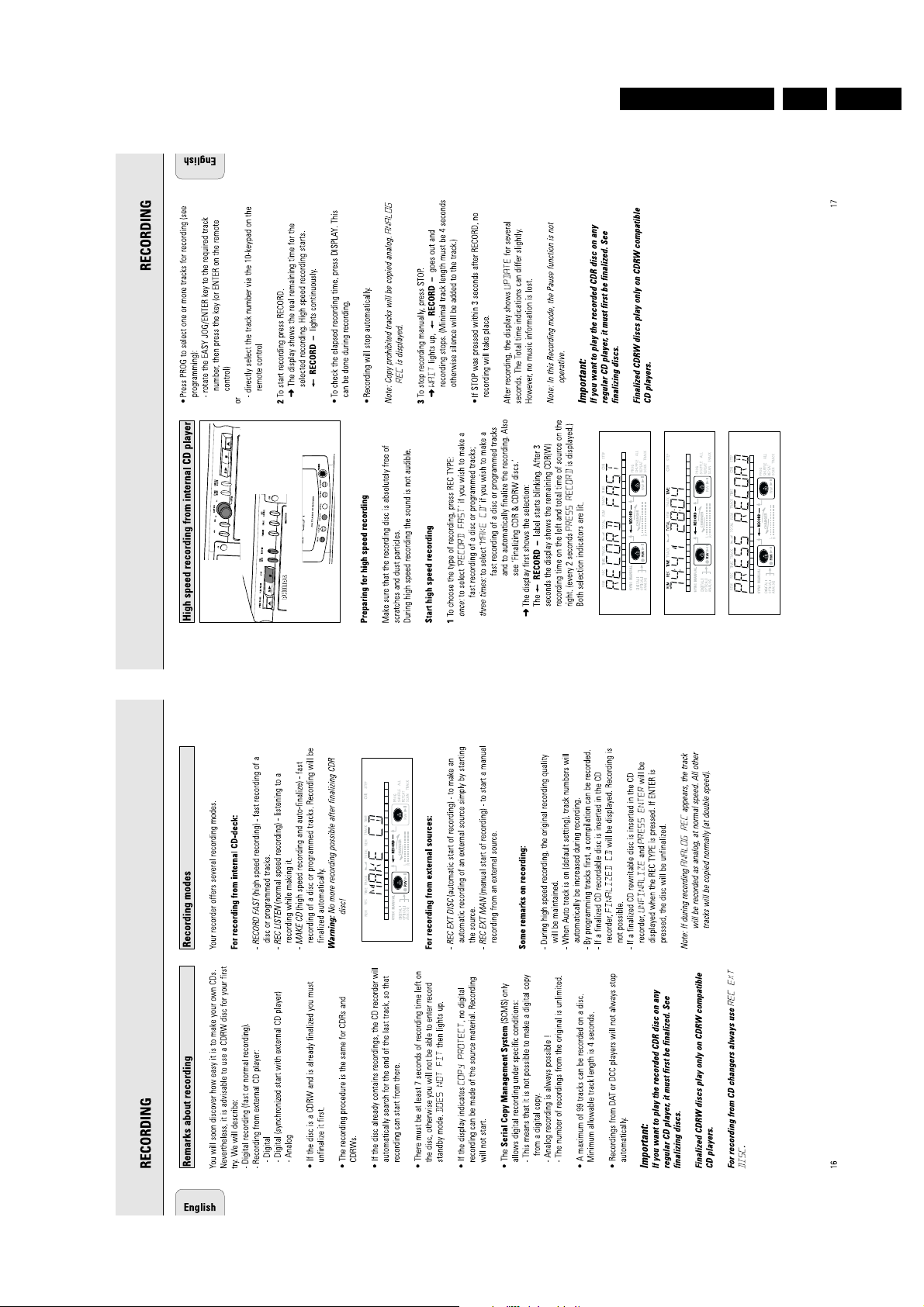

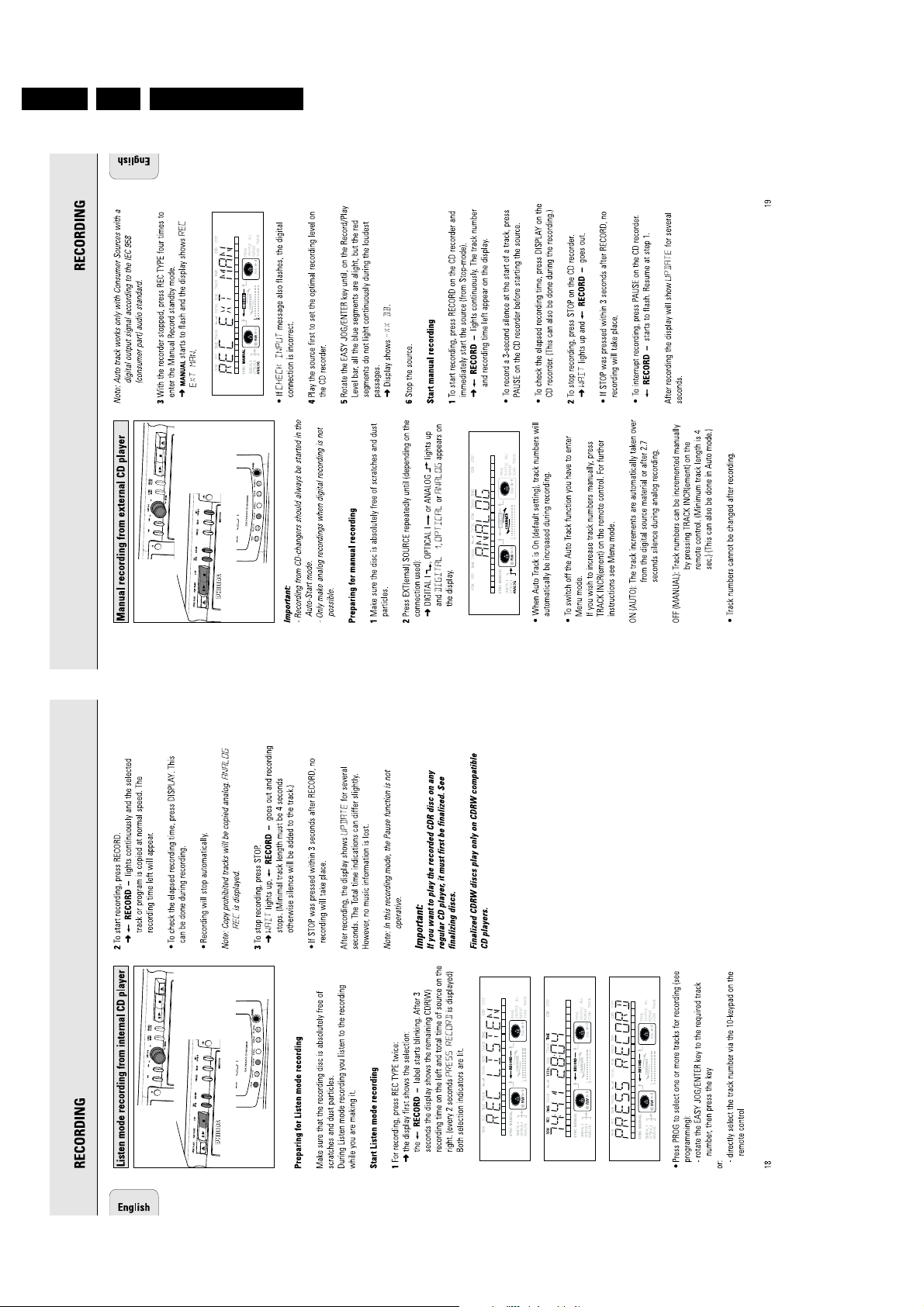

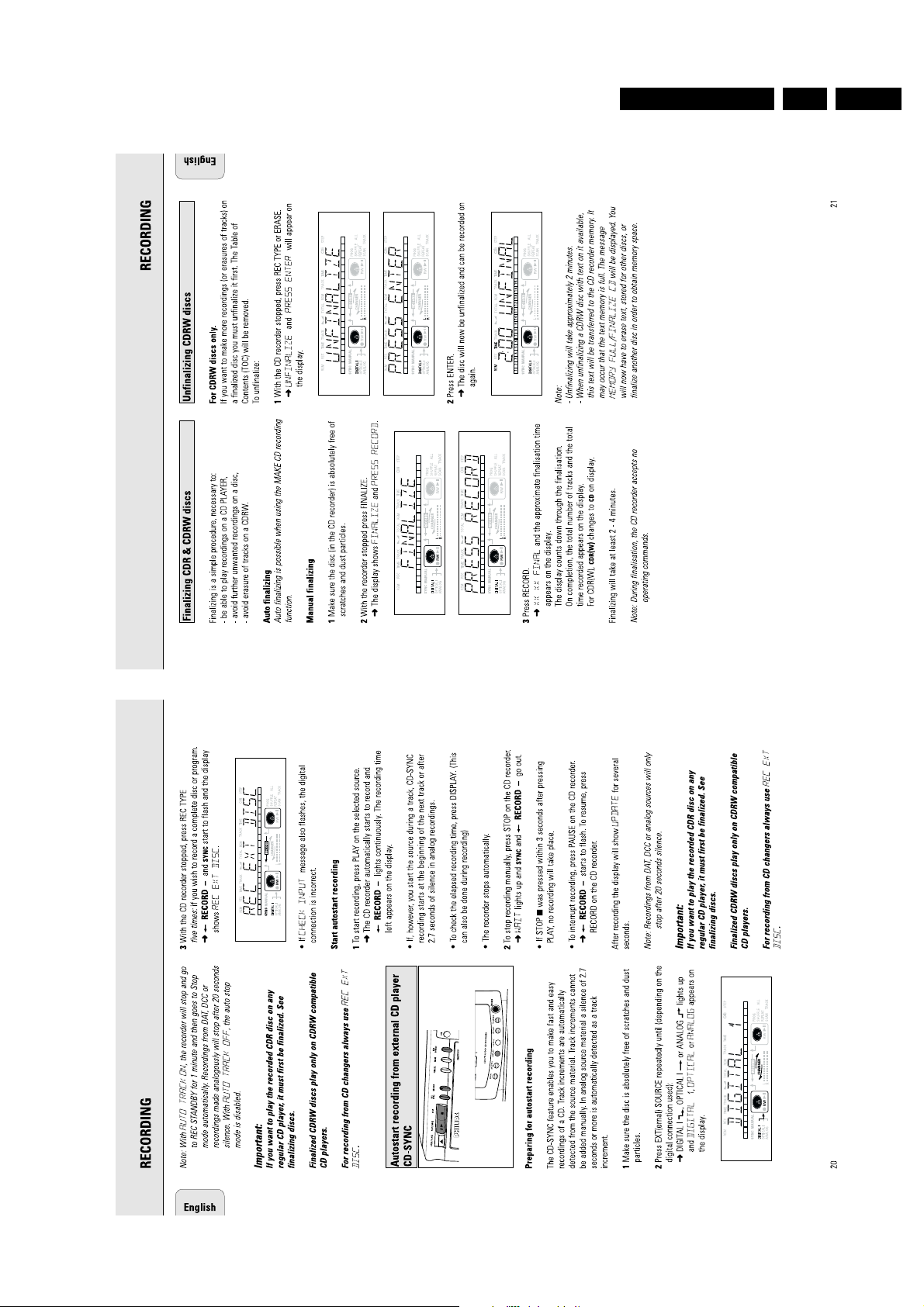

GB 7CDR775 3.

Page 8

GB 8 CDR7753.

User instructions

Page 9

User instructions

GB 9CDR775 3.

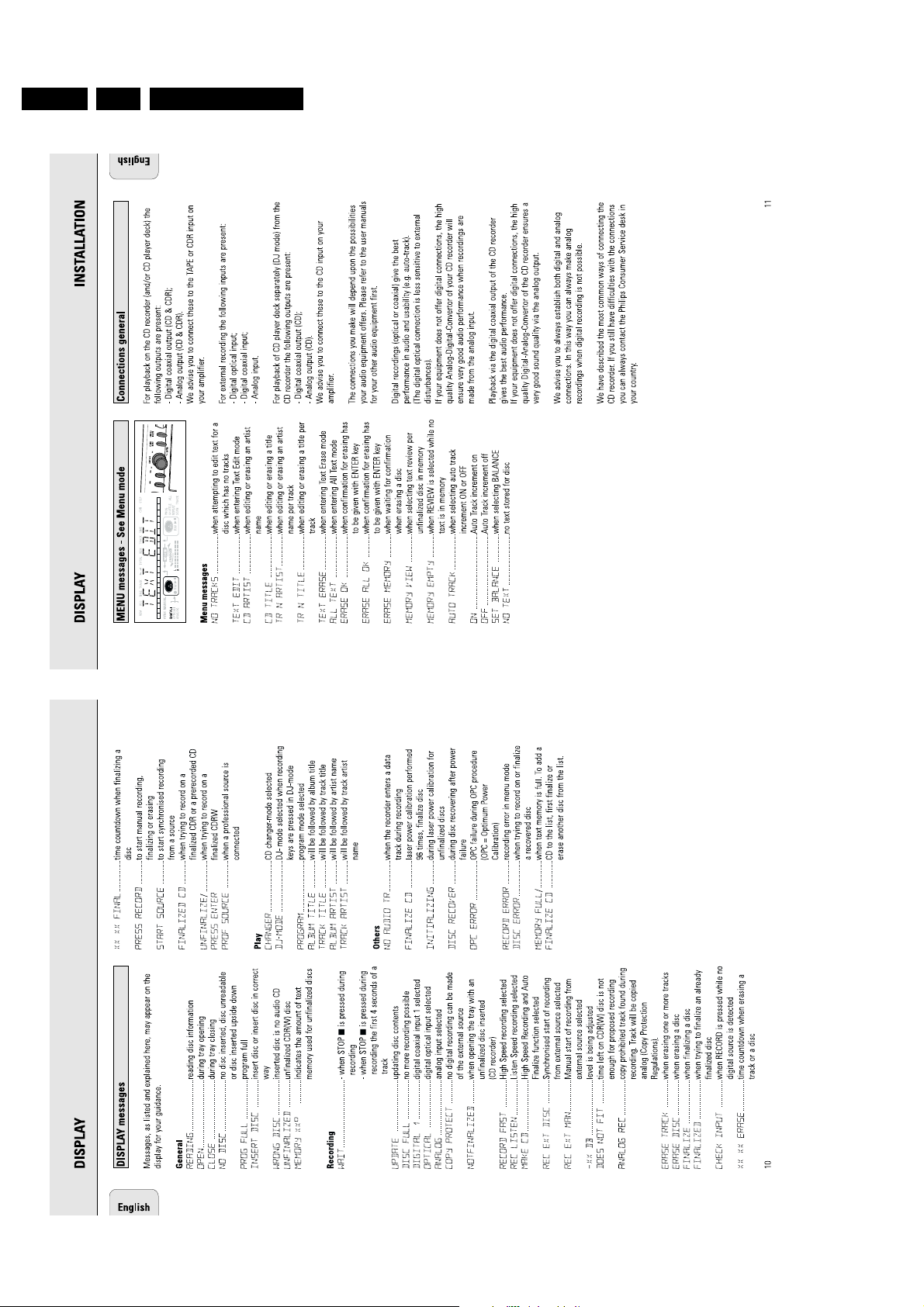

Page 10

GB 10 CDR7753.

User instructions

Page 11

User instructions

GB 11CDR775 3.

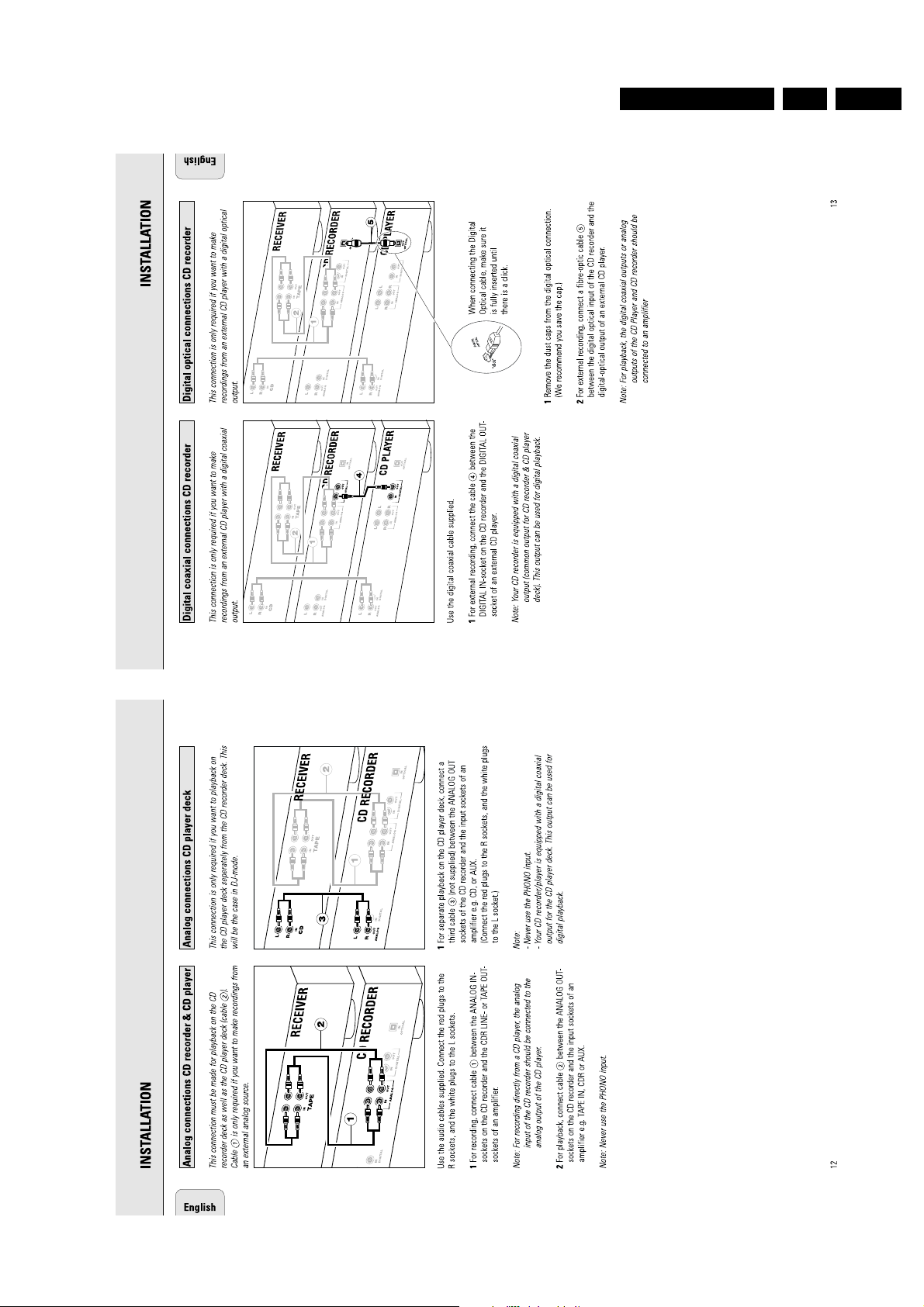

Page 12

GB 12 CDR7753.

User instructions

Page 13

User instructions

GB 13CDR775 3.

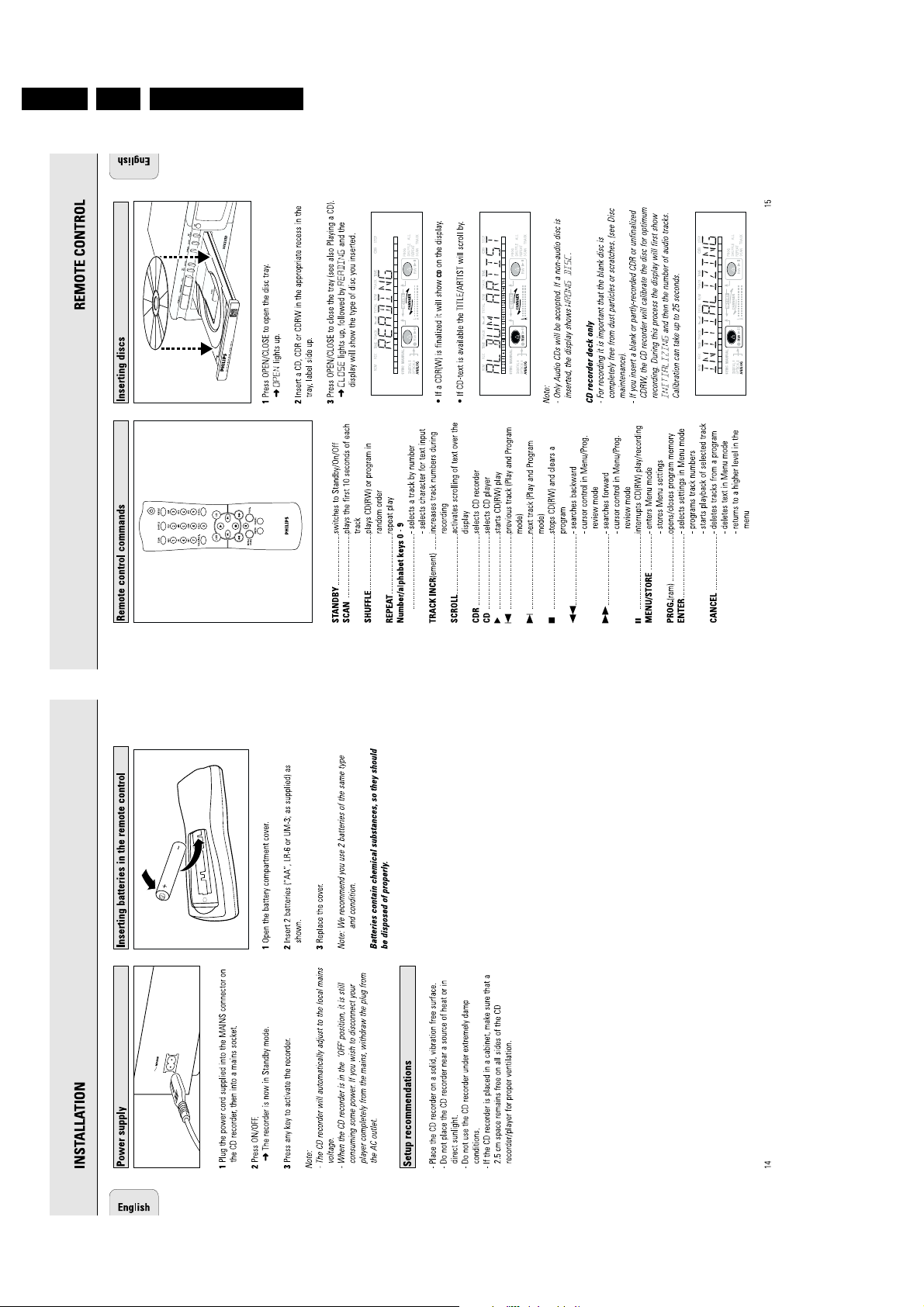

Page 14

GB 14 CDR7753.

User instructions

Page 15

User instructions

GB 15CDR775 3.

Page 16

GB 16 CDR7753.

User instructions

Page 17

User instructions

GB 17CDR775 3.

Personal notes:

Page 18

GB 18 CDR7753.

Personal notes:

User instructions

Page 19

Mechanical instructions

4. Mechanical instructions

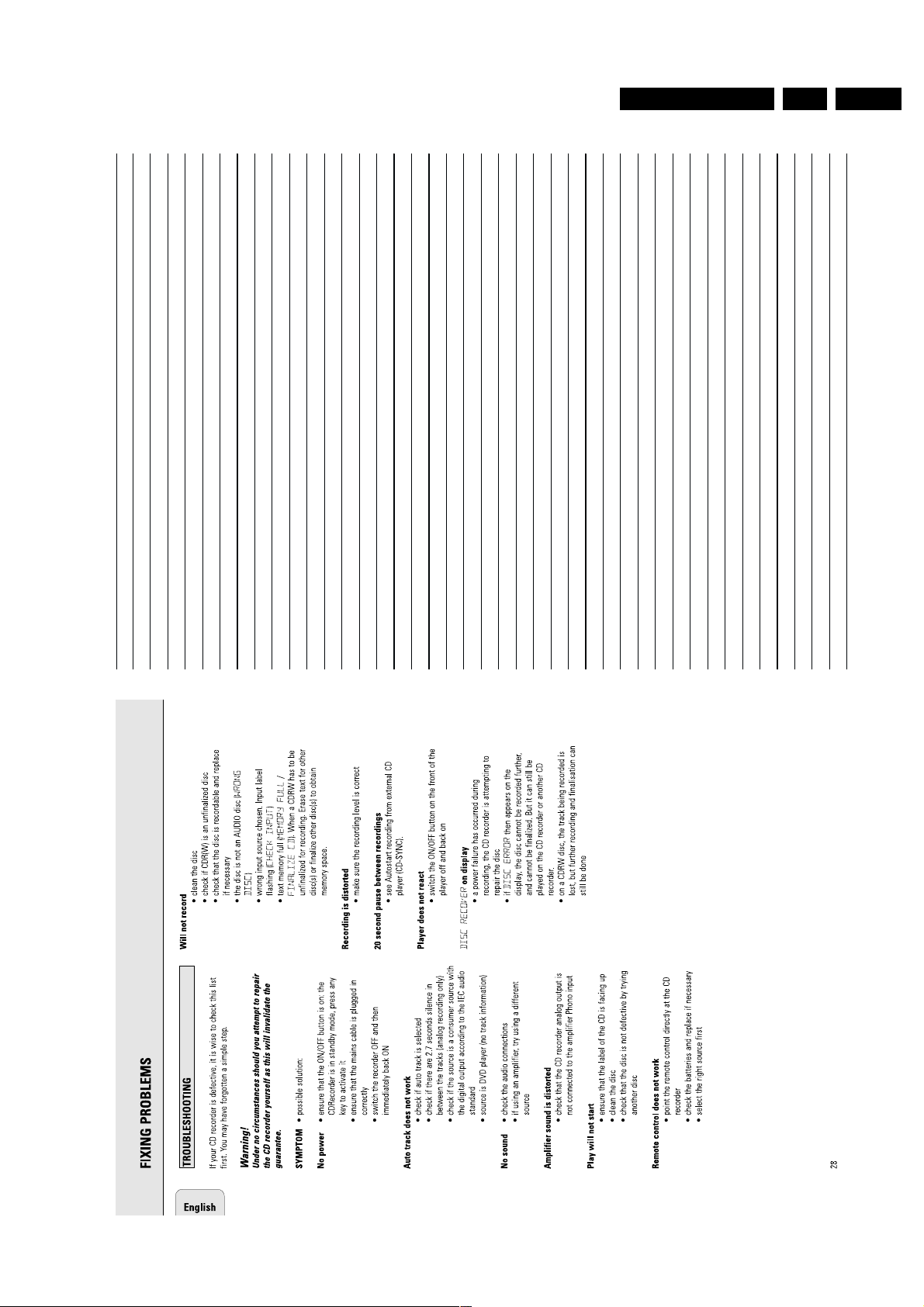

Wiring diagram

WIRING DIAGRAM CDR775

8006

3104 157 1099

1000

114

8001

3104 157 1124

I/O BOARD

3104 128 0599

8002

3104 157 10962

CD OUT

3104 128 0590

17

1502

11

0205

1

GB 19CDR775 4.

Pin 1 indicated by All Wires are 1/1, except flex 8001, 8005 and 8007

2

0206

1

POWER SUPPLY UNIT

8007

3104 157 1129

0101

8001 (at conn. 1400

of CDR main board)

1 GROUND

2 DIG_OUT_C

3 GROUND

4 EXT_DIG_IN

5 EXT_OPT_IN

6 GROUND

7D5V

8KILL

9LEFT_IN

10 GROUND

11 RIGHT_IN

12 RIGHT_OUT

13 GROUND

14 LEFT_OUT

8002

1 VDC2

2VFTD

3

VDC1

4 GROUND

5+5V

6+5V

7 GROUND

8 GROUND

9 GROUND

10 +12V

11 -8V

8003 (at conn. F934

of CDR main board)

1 VDC2

2

VFTD

3 VDC1

4 SYS_RESET

5IIC_DATA

6 GROUND

7IIC_CLK

8 DISPL_INT

9 GROUND

10 D5V

8004

3104 157 11002

13

1410

Connections delivered

with CDR-loader assy

114

1400

Flex connected

to CDM

F934

1000

130

MAIN BOARD CDR

3104 128 0586

1

3

1400

1

110

1500

11

1708

Flex connected

to sledge motor

Flex connected

to turn table motor

Cable connected

to tray switch and

tray motor

10

1

11

1

4

1

1220

1330

1200

122

8005

3104 157 1123

8003

3104 157 1122

1208

1

4

1002

Cable connected

to tray switch and

tray motor

122

MAIN BOARD CD

3104 128 0598

Flex connected

to CDM panel

1000

116

Connections delivered

with CD-loader assy

111

Flex connected

1006

to turn table motor

17

1209

1001

Cable connected

to sledge motor

8004

1 LEFT_HP_OUT

2 GROUND

8006

1 ON!

2 OFF!

8009

1LED_ON

2 GROUND

3 RIGHT_HP_OUT

8008

1+5V

2

IR_IN

3 GROUND

8007 (at conn. 1209

of CD main board)

1 RIGHT_CD

2 GND

3 LEFT_CD

4 GND

5 DOBM_CD

6 GROUND

1

4

7 KILL

8005 (at conn. 1708

of CDR main board)

1 GROUND

2 DSA_DATA_CD

3 GROUND

4 DSA_STR_CD

5 DSA_ACK_CD

6 GROUND

7 D5V

8 12V_CD

9 GROUND

10 IIS_DATA_CD

11 IIS_WS_CD

12 GROUND

13 IIS_BCLK_CD

14 GROUND

15 DOBM_CD

TO FRAME

Texture indicates text on flex.

16 SYS-RESET

17 LEFT_IN_CD

18 GROUND

19 RIGHT_IN_CD

20 KILL

21 SYS_CLK_8W

22 GROUND

TO FRAME

HEADPHONE BOARD

3104 128 0590

ON/OFF & STBY LED

3104 128 0590

1302

2

1300

12

1

8009

3104 157 03881

1

1119

10

112

DISPLAY BOARD

3104 128 0590

1122

3

1121

8008

3104 157 11281

1200

1

3

IR BOARD

3104 128 0590

CL 96532086_001.eps

080999

Page 20

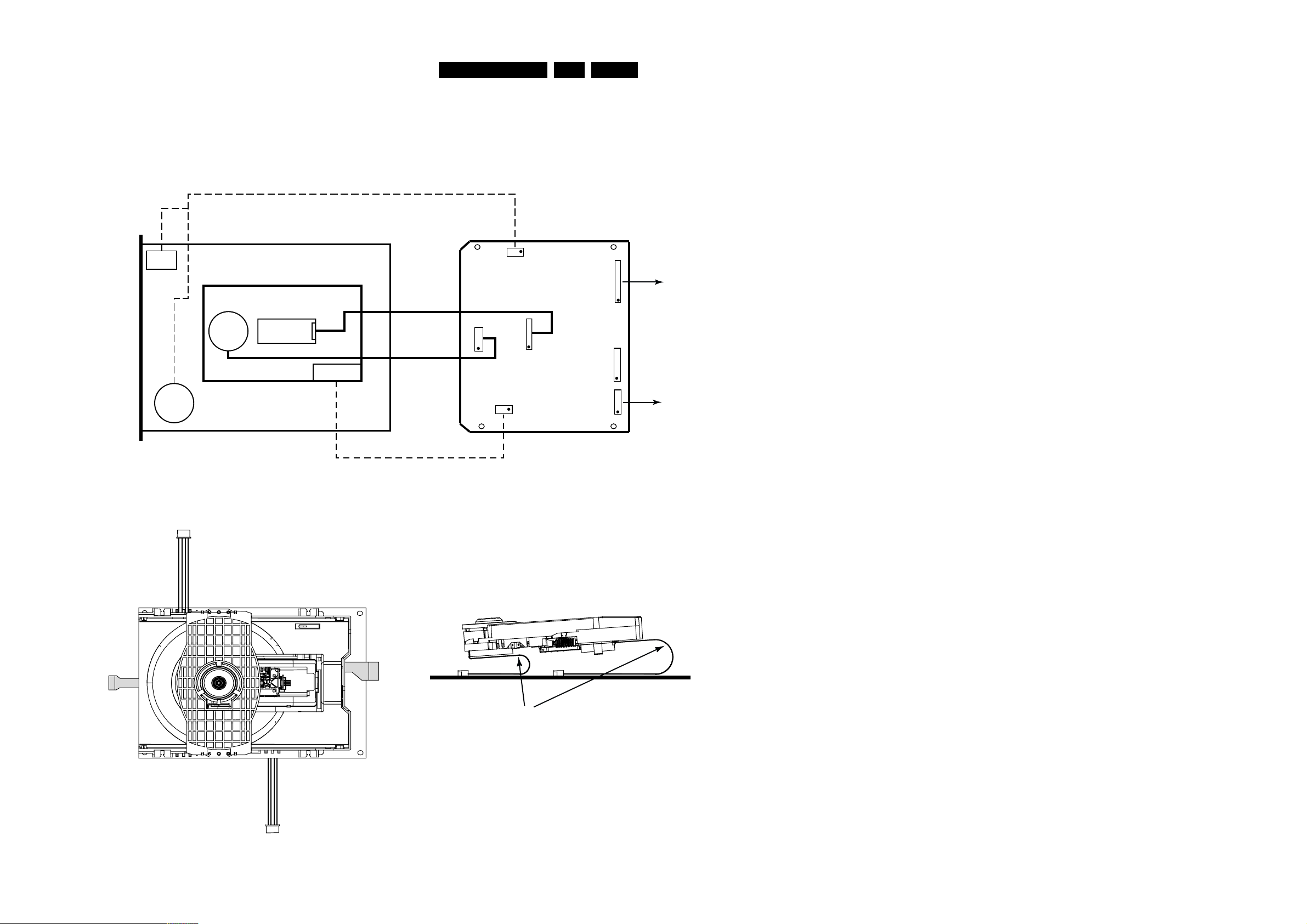

Mechanical instructions

Wiring CD

WIRING DIAGRAM CD LOADER VAL1250

GB 20CDR775 4.

Flex from

turn table motor

Tray

switch

Turn table

motor

Tray motor

Connector from tray motor

and tray switch

Connection tray motor

and tray switch

LOADER VAL1250

CDM VAM1250

OPU

LOADER VAL1250

Sledge motor

and switch

Flex from OPU

Flex from

turn table motor

Connection sledge motor

and sledge switch

Flex from OPU

1002

11

1006

1

MAIN BOARD CD

1001

14

16

1000

1

14

CDM VAM1250

22

1208

1

16

1210

1

7

1209

1

MAIN BOARD CD

To main board CDR

To CD out board

CONNECTOR 1006

1 HALL +

2 W3 W+

4 V+

5 HALL6 U+

7 V8 U9 UCOIL

10 VCOIL

11 WCOIL

CONNECTOR 1000

1 VSUB

2 HFGND

3 VDD

4 RF

5 LDON

6 R2

7 R1

8 D4/D3

9 D2

10 D1

11 FTC

12 RW

13 FOC+

14 FOC15 RAD+

16 RAD-

CONNECTOR 1002

1 HOMESW

2 SGND

3 TRAY+

4 TRAY-

CONNECTOR 1001

1 HOMESW

2 SGND

3 SL4 SL+

CONNECTOR 1209

1 AUDIO R (RIGHT_CD)

2 GND

3 AUDIO L (LEFT_CD)

4 GND

5 DOBM5_CD (DOBM_CD)

6 GND

7 KILL

CONNECTOR 1208

1 GND

2 CRIN (SYS_CLK_8W)

3 KILL

4 AUDIO R (RIGHT_IN_CD)

5 GND

6 AUDIO L (LEFT_IN_CD)

7 DSA_RST (SYS_RESET)

8 DOBM (DOBM_CD)

9 GND

10 SCLK (I2S_BCLK_CD)

11 GND

12 WCLK (I2S_WS_CD)

13 DATA (I2S_DATA_CD)

14 GND

15 +12V

16 +5V

17 GND

18 DSA_ACK (DSA_ACK_CD)

19 DSA_STROBE (DSA_STR_CD)

20 GND

21 DSA_DATA (DSA_DATA_CD)

22 GND

Connector from sledge motor

and sledge switch

POSITION OF FLEX CONNECTIONS

CL 96532086_002.eps

080999

Page 21

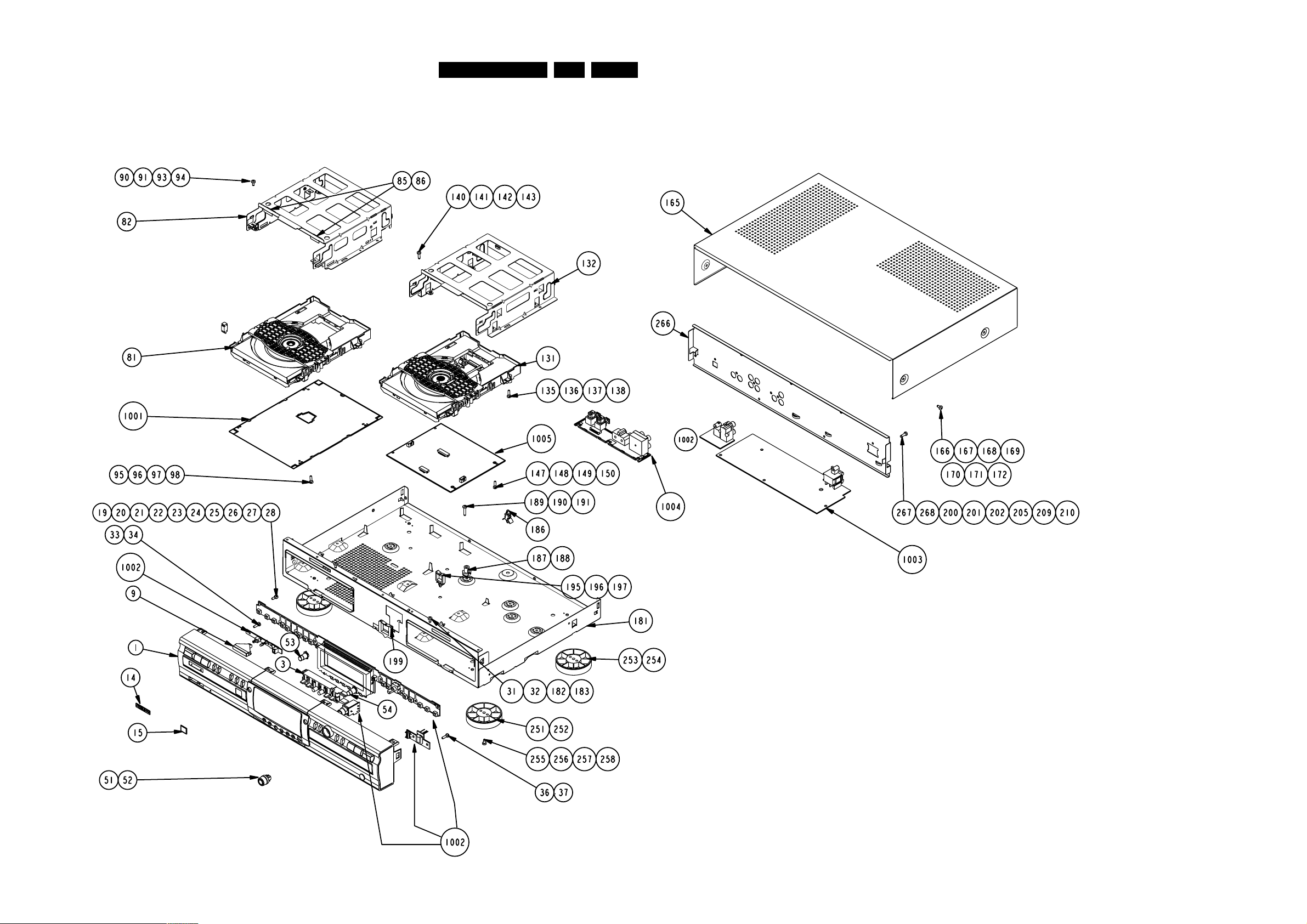

Mechanical instructions

Exploded view CDR775

EXPLODED VIEW CDR775

GB 21CDR775 4.

ON/OFF

& STBY LED

LOADER ASSY CDR

MAIN BOARD CDR

MAIN BOARD

CD

LOADER ASSY CD

CD OUT

BOARD

I/O BOARD

POWER SUPPLY UNIT

HEADPHONE

BOARD

IR

BOARD

DISPLAY

BOARD

DISPLAY ASSY

CL 96532086_003.eps

080999

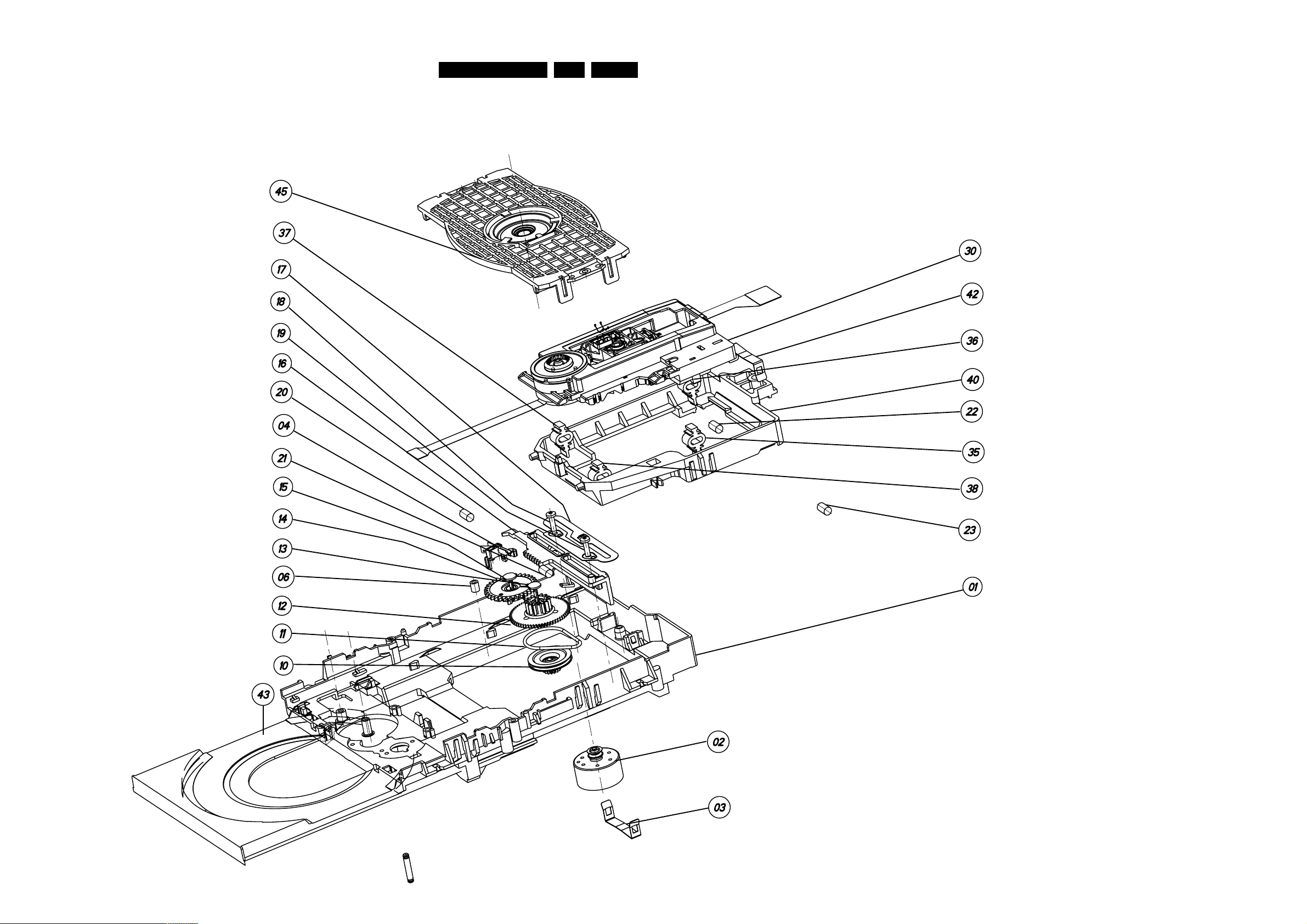

Page 22

Mechanical instructions

Exploded view CD

EXPLODED VIEW CD LOADER VAL1250

CLAMPER ASSY

SUSPENSION

RACK SPRING

GB 22CDR775 4.

CDM VAM1250

SCREW

SCREW

RACK

RUBBER

SWITCH

RUBBER

PLUG

TRAY GEARWHEEL

PLUG

TULE

RACK GEARWHEEL

MOTORSPRING

SUSPENSION

SUB CHASSIS

RUBBER

SUSPENSION

SUSPENSION

RUBBER

CHASSIS ASSY VAL1250

PULLEY WHEEL

TRAY HORIZONTAL

BELT

TRAY MOTOR ASSY

MOTORSPRING

CL 96532086_004.eps

080999

Page 23

Mechanical instructions

Dismantling 775

DISMANTLING INSTRUCTIONS CDR775

See exploded views for item numbers

GB 23CDR775 4.

Cover 165

⇒

Remove 7 screws 166 → 172,

2 at each side and 3 at rear side.

Lift cover at rear side to remove.

⇒

assembling

↑

↓

disassembling

CDR module includes :

Loader 81

CDR main board 1001

Loader bracket 82

⇒

Put the CDR player's rear side facing you.

Undo the 3 wire connections on the CDR

⇒

main board 1001.

⇒

Undo the 2 flex connections on CDR main board.

⇒ Remove 4 screws 90,91,93,94

(loader bracket 82 → frame 181).

⇒

Lift CDR module at rear side to remove.

Attention : flexes are not part of the CDR module

and have to stay with CDR player in case

of CDR module exchange !

CD module includes :

Loader 131

CD main board 1005

Loader bracket 132

⇒

Put the CDR player's rear side facing you.

⇒ Remove 4 screws 140 → 143

(loader bracket 132 → frame 181).

⇒

Lift CD module at rear side to remove.

⇒

Undo the 2 flex connections on CD main board.

Attention : flexes are not part of the CD module

and have to stay with CDR player in case

of CD module exchange !

CD main board 1005

⇒ Remove 4 screws 147 → 150

(CD main board → loader bracket 132).

Undo 2 flex and 2 wire connections

⇒

on CD main board.

⇒

Remove board.

CD loader assy 131

⇒ Remove 4 screws 135 → 138

(CD loader → loader bracket 132).

⇒

Remove loader.

CDM VAM1250

Remove clamper assy 45 by releasing 4 snaps

⇒

(2 on left 2 on right side) on chassis assy 1.

⇒

Open tray 43 by unlocking rack 16.

⇒

Undo wires of CDM VAM1250 from

wire retainers on sub chassis 40.

⇒ Unlock suspensions 35 → 38 from sub chassis 40.

⇒ Remove CDM VAM1250.

CD out board 1002

⇒

Put CDR player's rear side facing you.

⇒

Undo flex connection to CD main board 1005.

⇒ Remove 2 screws 209, 210 connecting

the 2 I/O sockets to back plate 266.

⇒

Remove board.

Attention : flex is not part of the CD out board

and has to stay with CDR player in case

of CD out board exchange !

I/O board 1004 Power supply unit 1003

⇒

Put CDR player's rear side facing you.

⇒

Undo flex connection to CDR main board 1001.

⇒

Remove 3 screws 200 → 202, connecting

the 3 I/O sockets to back plate 266.

⇒

Remove board.

Attention : flex is not part of the I/O board

and has to stay with CDR player in case

of I/O board exchange !

IR board 1002

Remove 2 screws 36 and 37

⇒

⇒

⇒

→ front assy 1).

(IR board

Undo wire connection on board.

Remove board.

⇒

Put the CDR player's rear side facing you.

⇒

Undo the 2 wire connections on PSU.

⇒ Remove screw 205

(mains connector → back plate 266).

Remove 3 screws 189 → 191

⇒

(PSU board → frame 181).

⇒

Unlock snap on spacer 186.

⇒

Remove PSU.

WARNING: POSSIBILITY OF HIGH

VOLTAGE (300V) ON HEAT SINK,

EVEN AFTER REMOUNTING OF

PCB. DISCHARGE ELCAP 2121.

Display board 1002

⇒

Remove easy jog knob 51 pulling it forward.

⇒

Remove 11 screws 19

(display board → front assy 1).

⇒

Release 2 snaps (1 on left and 1 on right side)

⇒

Undo the 3 wire connections on display board.

⇒

Remove display board.

Attention : when reassembling make sure

the wiring from display board to IR board is

positioned between FTD display and

middle key assy 3 !

→ 29

Headphone board 1002

⇒

Pull board out of front assy 1.

⇒

Slide board out of middle key assy 3.

⇒

Undo wire connection on board.

⇒

Remove board.

Front assy 1

⇒

Put the CDR player's front side facing you.

⇒

Remove 2 screws 31, 32

(ground wires

⇒

Remove 2 screws 182, 183

(front assy 1

Unlock front assy from frame by releasing 7 snaps :

⇒

start with 2 on the top and two on the sides

and end with 3 at the bottom.

⇒

After disassembly put in front of the set (service position).

→ frame 181).

→ frame 181).

On/Off & Stby LED board 1002

⇒ Remove 2 screws 33 and 34

(on/off switch

⇒

Undo the 2 wire connections on board.

⇒

Remove power button 9 from on/off switch.

⇒

Remove board.

→ front assy 1).

CL 96532086_005.eps

080999

Page 24

Electrical and circuit diagrams

5. Electrical and circuit diagrams

Blockdiagram 775

OVERALL BLOCK DIAGRAM CDR775

GB 24CDR775 5.

CDL 4009

LOADER ASSY

CDM3800

M

TURN

TABLE

LASER

&

FORWARD

SENSE

PHOTO

DIODES

RADIAL

FOCUS

M

SLEDGE

M

TRAY

TRAY

SWITCH

FLEX 11P

FLEX 30P

FLEX 10P

2 WIRES

2 WIRES

CDR MAIN BOARD

1330

DRIVE, HALL FEEDBACK

1000

IR, IW, IE

CAHF

A1LF, A2LF, B1LF, B2LF

C1LF - C4LF

RAD+, RADFOC+, FOC-

PCS PRE-AMP

NE532D

1220

SIN+, SINCOS+, COS-

1200

SL+, SL-

TR+, TR-

TRAYSW

POWER

DRIVER

BA5938FM

EFMTIM3

LO9805

EFM TIMING

GENERATOR

CONTROL

LINES

LASER

CONTROL

CONTROL

LINES

AEGER

TZA1020

ANALOG

ERROR SIGNAL

GENERATOR

FOR

RECORDABLE

7225

7240

RAD

FOCUS

SLEDGE

TRAY

7008

EFMDATA, EFMCLK, LWRT

CONTROL

LINES

7016

CONTROL

LINES

XDAC

M62364

CONTROL

LINES

7010

I2C BUS

ALPHA0

A1, A2, CALF

TLN, MIRN, FEN, REN, RE

REFSIN, SINPHI, REFCOS, COSPHI

VRA, VFO, VSL

TRAYIN, TRAYOUT

TRAYSWF

HALL

MOTOR

DRIVER

BA6856FP

7330

HIN WOBBLE

HF AMP

FILTER

I2C

EEPROM

M24C08

CDR60

SAA7392

DECODER

ENCODER

MOTOR CONTROL

OFFTRACK

LLP

CDR60PLL

7207

MACE2

SAA7399

BASIC ENGINE

PROCESSOR

ATIPSYNC

SYS-CLK-BE

(8.4672 Mhz)

7300

CONTROL

LINES

MAD0 - MAD7

MA8 - MA17

7270

ADDRESS

BUS

DOBM-CDR

SUBCODE BUS

I2S BUS 1

DATA

BUS

DSA-CDR

FLASH

EPROM

DEMUX

FLASH

ROM

DRAM

A1 - A20 D16 - D31

DASP

MCF5244

DIGITAL AUDIO

SIGNAL

PROCESSOR

7802

33.8688 MHz

RAM

7208

7209

7703

7702

1707

ADDRESS

BUS

7701

DATA

BUS

INT-COPY-ANA

SEL-HP-OUT

SYS-CLK-11W

I2S BUS 2/4

L3 BUS

EXT-DIG-IN

DIG-OUT-C

EXT-OPT-IN

SYS-CLK-16W (16.9344 Mhz)

SYS-CLK-BE

(8.4672 Mhz)

DIGITAL

POT

DS1807

7405

CODEC

UDA1341TS

ADC / DAC

DSA-CD

I2S BUS 3-CD

DOBM-CD

/2

74F74D

7801

ANALOG

IN

7406

7706A

SYS-RESET

I2C BUS

ANALOG

OUT

ANA-OUT

CD-ANA-OUT

7409

7401

EXT-ANA-IN

CD-ANA-OUT

7407 7408

SYS-RESET

SYS-CLK-8W (8.4672 Mhz)

+5V

+12V

-8V

VDC1, VDC2, VFTD

D5V

1500

11 WIRES

F934

10 WIRES

1410

3 WIRES

1400 1000

FLEX 14P

1708

FLEX 22P

1119

1208

ON/OFF

0205

POWER SUPPLY

UNIT

DISPLAY ASSY

DISPLAY

15-BT-60GNK

SLAVE DISPLAY

CONTROLLER

TMP87CH74F

KEYS

1400

EASY

JOG

HEADPHONE

I/O BOARD

CD PLAYER

7309

DAC

UDA1320

7207

uP

S87C654

7000

DECODER

SAA7324

1209

FLEX

7P

1502

CD

ANALOG OUT

CD

DIGITAL OUT

CD OUT

1302

2 WIRES

0206

1113

7104

RC5

1050

EXTERNAL

ANALOG IN

ANALOG OUT

COMMON

EXTERNAL

DIGITAL IN

DIGITAL OUT

COMMON

EXTERNAL

OPTICAL IN

CD

DRIVE

CL 96532086_006.eps

080999

Page 25

Electrical and circuit diagrams

Display 775

GB 25CDR775 5.

DISPLAY BOARD CDR775 - CIRCUIT DIAGRAM

A

V13

B

C

V14

D

E

V15

F

+5V

VFTD

+5V

VFTD

+5V

VFTD

7203

BC847B

3122

82K

7204

BC847B

3124

82K

7100

BC847B

3106

82K

F101

F102

F142

VFTD

GNDA

2101

100n

VDC2

GNDA

7104

TMP87CH74F

F127

F128

F129

F131

F134

F136

F139

F140

F143

F145

F147

F149

F174

F152

F153

G

TO ON/OFF &

STBY LED BOARD

1

2

H

I

12345

1113

15-BT-60GNK

REM REC

12 34 567 8 9 1011121314151617181920

SYNC MANUAL

DIGITAL ||

OPTICAL||

ANALOG

1F+

47

F100

65

V24

66

V25

V26

67

68

V27

V28

69

V29

70

V30

71

V31

72

V32

73

V33

74

V34

75

76

V35

77

V36

VKK

78

-SCK1

79

SI1

GNDA

F159

F166

1121

PH-B

GNDA

2F+

3F+

46

45

F114

F115

V23

V22

8-Bit h. breakdown v.

5-Bit h. breakd. v.

8-Bit Input/Output

(tri-state)

P03

SO1

1

3109

560R

5

671234

TIME TRACK TOTAL REM TRACK TIME FADE STEP

CD

P9

F110

V7

TC2

F167

+5V

3113

10K

F123

V6

-DV0

10P511P612P713P814

F111

V5

8-Bit A/D

Converter

P1

TC4

3114

10K

F168

PROG A-B

SHUFFLE ALL

REPEAT DISC

SCAN TRACK

P4

8P39

F124

V4

80k pull down80k pull down

TC1

BA

1G

2G

42

41

403G394G385G376G367G358G34

F103

F116

V21

V20

80k pull

down

out. port w. latch P9

source open

drain 80k p.d.

out w. latch PD

P04

P05

4

3

F170

F171

F164

GNDA

CD

RW

9G

F104

F105

F117

V18

V19

8-Bit h. break. v.

80k pull down

P0

P06

P07

7

GNDA

CDRLED

CDLED

3112

39K

1110

2109

22p

GNDA

RECORD

CHANGER

L

R

P2026P21

NC

10G3211G3112G3013G2914G2815G

33

F118

V16

V17

VFT driver circuit (automatic display)

25

27

V13

V15

V14

F119

V14

F108

F107

F120

5354555657585966061626364

V11

V12

V13

P6-P9 source open drain

F106

V15

8-Bit high breakdown voltage 8-Bit high breakdown v.

output port with latch output port with latchout w. latch P8

ROMRAM

F121

V10

F109

V9

Program

Counter

F122

V8

RW

P1016P1117P1218P1319P1420P1521P1622P1723P1824P19

15

CPU

3-Bit In/Output

with latch P2

XTIN

XTOUT

F157

GNDA

2102

22n

GNDA

TEST

drain

-STOP

F158

INTERRUPT

8-Bit Input/Output

(tri state)

-INT0

-INT1

sink open

XIN

VSS

XOUT

-RESET

8809

10 11 12 13 14 15 16 17 18 19220 21 22

F162

RESETN

2110

22p

GNDA

67

+

P1

P2

1F-

2F-

3F-

6

7

1

2

3

F165

F113

F112

F125

4142434445464748495505152

V1

V0

V2

V3

3-B. I/O P3

sink o.drain

INT2

VDD

VAREF

P6P7

VASS

AIN13

AIN12

AIN11

AIN10

4-Bit In/Output

(tri-state) P5

AIN7

P4

AIN6

AIN5

AIN4

AIN3

8-Bit Input/Output

AIN2

(tri-state)

AIN1

AIN0

-SCKO

INT4

SCA

SCL

23 24

1050

54

3

MT16MT2

GNDA

8

VFTD

6100

BZX284-C3V3

VDC1

3125

3K3

GNDA

+5V

F126

2100

40

100n

3107

4K7

B

A

GNDA

3108

100R

3111

100R

GNDA

2111

100n

+5V

+5V

39

F130

38

F132

37

F135

36

F137

35

34

F141

33

F144

32

F146

31

F148

30

F150

29

F151

28

27

F154

26

25

F155

F161

F163

1

27

8

910

+5V

1114

EVQ21

REC.

START

1111

EVQ21

EXT.

SOURCE

1120

EVQ21

REPEAT

1115

EVQ21

MENU

2106

22p

2104

22p

4K7

F160

3101

B

A

1

2

3

1101

EVQ21

PLAY /

PAUSE

1109

EVQ21

ERASE

1117

EVQ21

SCROLL

F138

F133

1122

EH-B

3100

4K7

GNDA

GNDA

TO IR BOARD

GNDAGNDA

910

F172

CD SELECT

1131-A

3115

560R

0100

EVQ21

STOP

1131-B

SKHQ

EVQ21

MODE

EVQ21

CANC /

F156

1

GND WIRE

GNDA

1105

SKHQ

CDRLED

1125

DJ

1118

DEL

VDC2

VFTD

VDC1

RESETN

IIC_DATA

IIC_CLK

INTERRUPT

11 12 13

1106

EVQ21

OPEN/

CLOSE

1103

EVQ21

PROG

1130-B

SKHQ

CD SELECT

SKHQ

CDLED

1126

EVQ21

PLAY

CD

1

2

F169

3

4

5

6

7

8

9

10

11

+5V+5V

GNDA

1119

EH-B

3103

4K7

1107

EVQ21

REC.

TYPE

1102

EVQ21

SHUFFLE

1104

EVQ21

PREV

1127

EVQ21

STOP

CD

+5V

3104

4K7

TO CDR MAIN BOARD

12

+5V

+5V

3102

4K7

GNDA

GNDA

F173

1130-A

3116

560R

1108

EVQ21

FINALIZE

1116

EVQ21

DISPLAY

1112

EVQ21

NEXT

1128

EVQ21

O / C

CD

+5V

3105

4K7

PB DISPLAY - 4230

CDR 775

3104 123 4230

13

A

B

C

D

E

F

G

H

I

0100 G10

1050 H7

1101 B9

1102 C12

1103 C11

1104 C12

1105 B10

1106 B11

1107 B12

1108 B13

1109 C9

1110 G4

1111 C10

1112 C13

1113 A3

1114 B10

1115 D10

1116 C13

1117 C9

1118 D10

1119 F11

1120 C10

1121 G3

1122 H9

1125 C10

1126 D11

1127 D12

1128 D13

1130-A D11

1130-B C11

1131-A C10

1131-B B10

2100 D8

2101 F2

2102 G5

2104 G10

2106 G10

2109 H4

2110 H5

2111 H8

3100 B9

3101 B10

3102 B11

3103 B11

3104 B12

3105 B13

3106 E2

3107 F8

3108 F8

3109 G4

3111 G8

3112 G4

3113 G6

3114 G6

3115 C10

3116 D11

3122 B2

3124 C2

3125 C8

6100 B8

7100 E1

7104 D3

7203 A1

7204 C1

F100 C3

F101 B2

F102 C2

F103 D4

F104 D4

F105 D4

F106 D5

F107 D5

F108 D5

F109 D6

F110 D6

F111 D6

F112 D6

F113 D7

F114 D4

F115 D4

F116 D4

F117 D4

F118 D5

F119 D5

F120 D5

F121 D5

F122 D6

F123 D6

F124 D6

F125 D7

F126 D7

F127 D3

F128 D3

F129 D3

F130 D7

F131 D3

F132 D7

F133 E9

F134 E3

F135 E7

F136 E3

F137 E7

F138 D9

F139 E3

F140 E3

F141 E7

F142 E2

F143 E3

F144 E7

F145 E3

CL 96532086_007.eps

F146 E7

F147 E3

F148 E7

F149 F3

F150 F7

F151 F7

F152 F3

F153 F3

F154 F7

F155 F7

F156 G10

F157 G5

F158 G6

F159 G3

F160 G10

F161 G7

F162 G5

F163 H7

F164 G4

F165 C7

F166 G4

F167 H6

F168 H6

F169 G11

F170 G4

F171 G4

F172 B10

F173 C11

F174 F3

080999

Page 26

Electrical and circuit diagrams

Display 775

DISPLAY BOARD CDR775 - FRONT VIEW

GB 26CDR775 5.

DISPLAY BOARD CDR775 - BACK VIEW

CL 96532086_008.eps

080999

Page 27

Electrical and circuit diagrams

R on/off

IR BOARD CDR775 - CIRCUIT DIAGRAM

123

1200 A1

6200 A3

F200 A2

F201 A2

F202 A2

GB 27CDR775 5.

IR BOARD - FRONT VIEW

1200

EH-S

AA

1

2

3

F200

F201

F202

2

VS

3

OUT

1

GND

6200

TSOP1736

IR BOARD - BACK VIEW

TO DISPLAY

BOARD

12

GNDB

3

PB DISPLAY - 4230

CDR 775

3104 123 4230

ON/OFF & STBY LED BOARD CDR775 - CIRCUIT DIAGRAM

123

1300 A3

1301 C3

1302 B1

6300 A1

F300 A2

A

6300

LTL-1CHPE

F300

F301

F301 A2

F302 B2

A

F303 B2

1

1300

PH-B

2

TO DISPLAY

BOARD

ON/OFF & STBY LED BOARD - FRONT VIEW

B

C

TO PSU

1302

EH-B

1

2

F302

F303

4

6

1301

SPPH23

251

3

PB DISPLAY - 4230

CDR 775

3104 123 4230

123

B

C

ON/OFF & STBY LED BOARD - BACK VIEW

CL 96532086_009.eps

080999

Page 28

Electrical and circuit diagrams

HPCD out

HEADPHONE BOARD CDR775 - CIRCUIT DIAGRAM

123

F401

2400

1n

GND WIRE

GNDC

2401

1n

GNDC

GNDC

0400

1

F400

GNDC

F402

A

1400

PH-B

TO CDR MAIN

BOARD

3

2

1

B

HLJ1540

1

3

2

1401

PB DISPLAY - 4230

CDR 775

3104 123 4230

A

B

0400 A2

1400 A1

1401 A3

2400 A2

2401 B2

F400 A2

F401 A1

F402 B2

GB 28CDR775 5.

HEADPHONE BOARD - TOP VIEW

HEADPHONE BOARD - BOTTOM VIEW

123

CD OUT BOARD CDR775 - CIRCUIT DIAGRAM

52044

A

52044 4

52044

TO CD MAIN BOARD

B

52044

52044

C

52044 1

52044 5

D

12

GNDD

2500

10u

F502

GNDD GNDD

3501

180R

F508

3502

2K2

3503

180R

F509

3504

2K2

1502-3

3

1502-4

1502-2

2

1502-7

7

1502-6

6

1502-1

1502-5

F500

DIGININT

F501

F505

RIGHT2

GNDD

F506

KILL

F507

LEFT2

5500

7CHA

DIGOUTCOIL

34

2

1

78

GNDD

7500

BC847B

GNDD

7501

BC847B

34

F503

F504

6

F510

2503

220p

GNDD

F511

2504

220p

3500

68R

2501

33n

GNDD

GNDD

2502

33n

GNDD

1

2

3

1500

YKC21-3416

DIGITAL OUT CD

ANALOG OUT CD

1501

YKC21-3613

3

2

1

CD OUT BOARD - TOP VIEW

1500 A4

1501 C4

1502 A1

1502 A1

1502 A1

1502 C1

1502 C1

A

1502 C1

1502 D1

2500 A2

2501 A3

2502 A4

2503 C3

2504 D3

3500 A3

3501 C2

3502 C2

B

3503 D2

3504 D2

5500 A2

7500 C2

7501 D2

F500 A1

F501 A1

F502 A2

F503 A3

F504 A3

F505 C1

F506 C1

F507 D1

F508 C2

F509 D2

F510 C3

F511 D3

CD OUT BOARD - BOTTOM VIEW

C

D

GNDD GNDD

12

PB DISPLAY - 4230

CDR 775

3104 123 4230

34

CL 96532086_010.eps

080999

Page 29

Electrical and circuit diagrams

I/O board

I/O BOARD - CIRCUIT DIAGRAM

1

3025

+5VDS

F100 F101

4R7

A

1000-8

B

+5V

DIGOUT

1001-B

YKC21-3421

DIGITAL INPUT

8

1000-13

13

5

+5VDS

F108

3

4

C

1002-B

YKC21-3699

5

1000-3

3

1000-2

2

1000-7

7

1000-1

1

6

4

F115

F117

F119

F120

INPUT RIGHT

D

INPUT LEFT

RIGHTOUT

E

KILL

LEFTOUT

F

GB 29CDR775 5.

23456789

1

2

DRIVER

3

2015

33p

2030

33p

2026

100p

2027

100p

GP1F32T

7010

3023

100R

F105

3029

75R

2025

150p

3030

100K

3031

100K

2017

2020

22n

22n

F107

3032

100R

3034

2K2

3036

100R

3038

2K2

3021

3024

7005

74HCU04D

1A

1

2A

3

3A

5

4A

9

5A

11

6A

13

3026

2023

3027

F116

3K3

3K3

VCC

GND

3K3

22n

3K3

7006

BC847B

14

1Y

2Y

3Y

4Y

5Y

6Y

7

F121

7008

BC847B

2

4

6

8

10

12

2018

22n

F113

F114

3033

100R

3035

2K2

3037

100R

3039

2K2

F106

+5VDS

+5VDS

5002

BLM21

2016

22n

7007

BC847B

7009

BC847B

2019

10u

3028

4R7

5001

7CHA

34

2

1

78

F110

2024

22n

GP1F32R

6000

F102 F103

6

F122

2028

33p

2021

33n

1

3

IR

2

F118

2029

33p

2022

33n

3020

68R

F111

F112

F104

1

2

5

F109

1000-12

1000-11

1000-10

1000-14

1002-A

YKC21-3699

2

3

1

1001-A

YKC21-3421

DIGITAL OUTPUT

1000-9

9

12

DIGIN

11

OPTIN

10

14

1000-4

RIGHTIN

4

1000-5

5

1000-6

LEFTIN

6

OUTPUT RIGHT

OUTPUT LEFT

A

B

C

D

E

F

1000-1 F1

1000-10 C9

1000-11 C9

1000-12 B9

1000-13 B1

1000-14 C9

1000-2 E1

1000-3 E1

1000-4 D9

1000-5 D9

1000-6 D9

1000-7 E1

1000-8 B1

1000-9 B9

1001-A A9

1001-B B1

1002-A E9

1002-B D1

2015 A2

2016 A5

2017 B3

2018 B4

2019 B6

2020 B3

2021 B7

2022 B7

2023 C4

2024 C6

2025 C3

2026 D2

2027 D2

2028 F7

2029 F7

2030 B2

3020 A8

3021 A4

3023 A2

3024 A4

3025 A1

3026 C4

3027 C4

3028 C6

3029 C3

3030 D3

3031 D3

3032 E3

3033 E5

3034 E3

3035 E5

3036 F3

3037 F5

3038 F3

3039 F5

3999 F9

5001 B6

5002 A5

6000 C7

7005 A4

7006 E4

7007 E5

7008 F4

7009 F5

7010 A2

PB AUDIO-I/O CDR99

3104_123_4239

123456789

CL 96532086_011.eps

080999

Page 30

Electrical and circuit diagrams

I/O board

I/O BOARD - TOP VIEW

GB 30CDR775 5.

I/O BOARD - BOTTOM VIEW

CL 96532086_012.eps

080999

Page 31

Electrical and circuit diagrams

PSU 99

GB 31CDR775 5.

0101 A 1

0101 B 1

0125 C 8

0205 F15

0205 E15

0205 G15

0205 G15

0205 A15

0205 A15

0205 G15

0205 H15

0205 H15

0205 C15

0205 D15

0206 J15

0206 J15

0207 I16

0207 C16

0207 I16

0207 B16

0207 J16

0207 D16

0208 H14

0210 B11

1120 B 2

1125 A 3

2101 G 2

2102 H 2

2103 H 2

2104 I 3

2106 K 2

2107 J 3

2109 J 4

2110 J 5

2111 G 7

2113 H 8

2114 I 7

2120 B 3

2121 C 6

2125 A 5

2126 B 5

2127 C 9

2129 E 5

2131 A 9

2133 E 8

2201 H12

2202 I11

2210 B11

4561 7 8 9 101112131415 1623

POWER SUPPLY UNIT 20PS317 - CIRCUIT DIAGRAM

3124

A

0101

TP1 TP2

3122

1R5

2120

385V

330nF

TP3 TP4

B

0101

3120

1120

T2.0AL250V

C

D

E

F

82K

G

3101

2101

82pF

2102

820pF

15

22K

H

I

3102

3103

3105

15K

8K2

2103

470pF

15K

3104

2104

12

14

13

J

*

1K

2106

K

3106

1125

7110

MC44603AP

DEMAGNETIZATION

DETECT

8

DEMAGNETISATION

MANAGEMENT

iref

SYNC INPUT

9

CT

10

RF

STANDBY

RP

STANDBY

(reduced frequency)

2.5V

ERROR

AMP

VOLTAGE

FEEDBACK

4.7nF

E/A OUT

FOLDBACK

*

2107

3108

220R

5120

OSCILLATOR

Vstby

STANDBY

VSB OUT

FOLDBACK

CURRENT

INPUT

SENSE INPUT

5

18K

2109

180K

3107

3110

10K

CURRENT

SENSE

7

1.5nF

16

reference

VOSC PROT

VOSC

SOFT-START

CONTROL

3109

330R

Vref iref

block

=1

2125

2.2nF/400V

2126

2.2nF/400V

Dmax &

SOFT START

& DMAX

11

2110

TP27

3123

3134

TP28

2129

Vref enable

initialization block

Set

LATCH

Reset

THERMAL

SHUTDOWN

iref

UVL01

Vref

2.2uF/50V

2213 B15

2220 F11

2221 G10

2222 F14

2223 F15

2230 C11

6102

SINB80

TP25

@

18K

18K

Q

2121

TP26

@ ITEM 2121

110V 220uF/200V

Wide Range 100uF/400V

Euro 47uF/400V

3129

10K

6129

4.7uF/50V

BZX84-C24

supply

UVL01

BUFFER

Vref Voc

OVER

VOLTAGE

MANAGEMENT

TP32

TP33

3111

1

OVER

VOLTAGE

PROTECT

2233 C15

2240 D11

2242 D14

2243 D15

2250 E11

2251 D11

22R

VC

OUT

GND

2

3

4

6

TP29

3116

6106

6107

2111

100R

910R

180R

BYD33J

BYD33J

100nF

3112

6113

3115

2252 E15

2260 I14

3101 G 3

3102 H 2

3103 H 2

3104 I 2

3113

15R

*

TP21

2114

TP22

100nF

3105 I 2

3106 K 2

3107 J 4

3108 J 3

3109 J 4

3110 G 4

STP5NB60FI

2133

2113

2.2nF

6114

BYD33D

7125

10K

3125

3126

6132

BYD33J

100uF/25V

3111 F 6

3112 H 7

3113 H 7

3115 I 7

3116 I 7

3120 B 2

0125

1R

3127

5132

10uH

5125

1R5

TP30

BEAD

2127

3128

3122 A 3

3123 C 5

3124 A 4

3125 C 8

3126 D 8

3127 D 9

2

5

470pF/1KV

1R5

7

9

CQY80NG

5

4

2131

2.2nF

5131

CT296F

7200

3203

3128 D 9

3129 E 6

3134 D 5

3201 G12

3202 H11

3203 J10

2

100R

17

15

11

13

10

14

16

18

1

TP23

TP24

7201

PBYR1060F

BYW98-200

5255

1uH

2221

47nF

TL431

3204 I11

3205 J11

3206 I11

3221 G13

3222 F13

3230 C13

6211

SB360

6210

6232

6230

BYW29F

6240

BYD33D

2251

6250

BYD33J

6220

BYD33D

2202

22nF

0210

*

3204

2210

2230

2240

2250

2220

1K8

3232 E13

3233 E14

3234 F14

5120 A 4

5125 B 9

5131 A 9

2200uF/10V

1000uF/16V

220uF/16V

10uF/50V

330uF/16V

3K3

3202

3K

3206

150R

3205

5132 E 9

5210 B14

5220 F14

5225 F12

5226 G12

5230 C13

10R

3201

2201

100nF

5240 D14

5250 E14

5255 E10

6102 A 6

6106 B 7

6107 C 7

BZX284-C6V8

7251

BC847

7252

BC857

5225

4.7uH

5226

*

9226

5230

2u2

6113 H 7

6114 I 8

6129 E 5

6132 E 8

6201 E14

6210 B11

3230

1K

6211 A11

6220 E11

6230 C11

6231 C14

6232 B11

6240 D11

6231

1N4006G

7249

L7908

2242

6251

3232

11K

BZX84-B20

6201

3233

10K

3234

10K

100uF/10V

7221

LM317T

240R

3222

2222

3221

470R

100uF/6V3

0208

2260

1nF

FRAME

* = RESERVED ITEM NUMBER

5210

6.8uH

5240

10uH

5250

10uH

5220

*

9220

1

2

3

6250 E11

6251 D13

7110 G 3

7125 C 8

7200 G10

7201 I10

TP5 TP6

*

TP7 TP8

*

TP9 TP10

TP11 TP12

TP13 TP14

TP15 TP16

TP17 TP18

TP19 TP20

TP31

2213

2233

*

2243

2252

*

2223

7221 F13

7249 D13

7251 E12

7252 E12

9220 F14

9226 G12

0205

5

0205

6

0205

10

0205

11

0205

2

220uF/50V

0205

1

0205

3

0205

4

0205

7

0205

8

0205

9

0206

1

0206

2

+5V

+5V

0207

+12V

0207

-8V

0207

VFTD

VDC2

VDC1

GND

GND

GND

GND

0207

0207

0207

20PS317

3122 427 21150

4

2

6

1

3

5

+5V

+12V

-8V

GND

GND

GND

A

B

C

D

E

F

G

H

I

J

K

4561 7 8 9 101112131415 1623

CL 96532086_013.eps

080999

Page 32

Electrical and circuit diagrams

PSU 99

POWER SUPPLY UNIT 20PS317 - COMPONENT SIDE

0101 D 2

0125 B 5

0205 B 11

0206 D 9

0207 D 11

0208 A 11

0210 A 10

1120 C 2

1125 A 2

2110 C 5

2120 C 1

2121 A 5

2121a A 5

2125 A 4

2126 B 4

1234567891011

2127 B 7

2129 C 4

2131 C 8

2133 C 7

2210 B 10

2213 B 11

2220 A 9

2222 A 10

2223 A 10

2230 C 9

2233 C 11

2240 C 8

2242 C 10

2243 C 11

2250 B 9

2251 B 9

2252 B 11

2260 A 11

3101 C 6

3115 C 6

3120 B 2

3122 B 2

3123 C 4

3124 A 3

3125 C 6

3126 B 6

3127 B 6

3128 B 6

3129 D 5

3134 D 4

3201 D 9

3202 D 9

3203 D 8

3230 D 10

5120 A 3

5120a A 3

5125 B 7

5131 B 8

5132 C 7

5210 B 10

5220 A 10

5225 A 9

5226 A 9

5230 C 10

5240 C 10

5250 C 10

5255 B 9

6102 A 4

6106 B 7

6107 C 6

6113 D 6

6114 D 6

6132 D 6

6210 B 9

6211 B 9

6220 A 8

6230 C 9

6231 C 10

6232 C 9

6240 C 8

GB 32CDR775 5.

6250 B 9

7110 C 5

7125 B 5

7200 D 8

7201 D 8

7221 A 9

7249 C 10

9208 B 11

9210 B 8

9214 D 11

9215 D 11

9220 A 10

9226 A 9

1125

3124

2125

A

_

3122

B

3120

5120a

+

2126

6102

0125

5120

T2.0AE 250V

2110

C

2120

D

1120

0101

2129

3123

UL-LOGO

3122 423 30443

CAUTION:

RISK OF FIRE REPLACE ONLY

WITH SAME TYPE OF FUSE.

ATTENTION:

UTILISER UN FUSIBLE

DE RECHANGE DE MEME TYPE

3134

3129

1234567891011

POWER SUPPLY UNIT 20PS317 - SOLDERING SIDE

7125

7110

5131

2121

3128

31273115

3126

2121a

6106

5125

2127

3125

1

3

1

2

2240

7200

6113

5132

2133

6107

3101

6114

6132

6220

9210

6240

3203

7201

3202

2220

6211

6250

6230

2251

3201

2250

9226

6232

2230

7221

5225

0208

2223

2222

A

B

7249

5226

6210

5255

2210

9220

5220

5210

5250

5240

2213

0210

2252

2260

0205

9208

2243

C

5230

2242

2233

6231

9214

0206

3230

9215

0207

D

A

B

C

D

2101 B 5

2102 C 5

2103 C 5

2104 C 5

2106 D 5

2107 C 6

2109 C 6

2111 D 5

2113 C 6

2114 C 7

2201 D 8

2202 D 8

2221 A 8

3102 D 5

3103 C 5

3104 C 5

3234

7252

3105 C 5

3109 C 6

3113 C 6

3206 D 8

3233 B 10

6251 B 9

TP2 D 2

TP6 C 11

TP10 D 11

TP14 A 11

TP18 B 11

TP22 B 7

TP26 B 5

3106 D 5

3107 C 6

3108 C 6

3110 D 5

3111 C 7

3112 D 5

3116 C 5

3204 D 8

3205 D 8

3221 A 10

3222 A 10

3232 B 10

3234 B 10

6129 C 4

6201 B 10

7251 B 10

7252 B 10

TP1 D 2

TP3 D 3

TP4 C 2

TP5 B 11

TP7 C 11

TP8 D 11

TP9 C 11

TP11 A 11

TP12 B 11

TP13 A 10

TP15 A 11

TP16 A 11

TP17 B 10

TP19 C 9

TP20 D 9

TP21 C 7

TP23 D 8

TP24 D 8

TP25 A 5

TP27 C 4

TP28 C 5

TP29 C 5

TP30 B 7

TP31 D 9

TP32 A 4

TP33 B 5

1234567891011

3221

3222

2221

A

B

6201

3233

3232

7251

6251

3116

2101

2109

3112

2111

2102

2104

3103

3104

2103

3105

3102

3110

6129

2106

3106

UL-LOGO

3122 423 30443

CL 96532086_014.eps

C

D

080999

2113

3109

2114

3111

3205

3206

2202

2201

3204

3113

3108

3107

2107

1234567891011

Page 33

Electrical and circuit diagrams

CD Diagram 1A

GB 33CDR775 5.

A

B

C

D

CD-DA, CD-R : 5V

CD-RW : 0V

8

F

G

H

1000-1 C1

1000-11 G1

1000-12 D1

1000-2 E1

1000-3 B1

1000-4 E1

1000-5 A1

1000-6 H1

1000-7 H1

1000-8 H1

1000-9 H1

1003 F7

1004 G9

1009 C15

1010 C15

1011 C15

1012 C15

1021 G10

1022 G11

1023 G11

1028 B2

1029 B3

1050-1 G1

1050-2 G1

2128 B12

12345

CD MAIN BOARD - CIRCUIT DIAGRAM 1A

DECODER & SERVO PROCESSOR PART

CONN. 1000 : TO CDM VAM1250

F147

100n

3179

1K

4u7

RW

1

HFGND

2135

HFGND

F155

2174

22u

22n

2175

HFGND

F146

+5VHF

2156

HFGND

3198

47R

1028

7008

BFS20

47u

1

1

+5VHF

47u

HFGND HFGND

+5VHF

LDON

1000-5

5

VDD

1000-3

3

2133

HFGND

VSUB

1000-1

1

2147

HFGND

RW

1000-12

12

RF

1000-4

4

HFGND

F173

1000-2

2

HFGND

F177

+5V

FTC

1000-11

11

1

1050-1

2

1050-2

1000-10

10

1000-9

9

1000-8

8

1000-7

7

1000-6

6

PB CD MAIN 4236

CDR99

3104 123 4236

2134

470n

HFGND

F154

2148

470n

HFGND

F160

47n

2159

HFGND

2163

F170

33n

3208

4R7

F180

12345

3177

3182

3187

3201

TDA1308T

2

2130 B6

2131 B12

2132 B11

2133 B1

2134 B1

2135 B1

2137 B8

2138 B8

3279

1R

1R

390R

390R

7011

BFS20

1K2

7311-A

1

V4

61V462

60

MOTO2

MOTOR

CONTROL

DEMOD

CONTROL

FUNCTION

PRE-

PROCESSING

VNEG21VPOS

20

2178

100n

2186

47u

F324

3225

+3V3

DIG.

PLL

EFM

3282 G11

3283 G123168 B12

3285 H13

3286 H13

3287 H133173 B4

7000 C93176 C14

3172

100R

F303

59

MOTO1

22RN23

2286

1n5

1

1022

2R2

7006 D3

7007 E7

7008 E2

7009 D5

7010 E6

7011 E2

7023 B5

7024 F6

7025 B7

+3V3

2R2

3162

2132

3273

3276

47u

2139

100n

58

VSSD3

ADDR

PROCESSOR

RP

1

100R

4

5

F305

F304

F308

57

56

55

SL

FO

VDDD2C

OUTPUT

STAGES

SRAM

AUDIO

SELPLL

TEST1

CL16

25 31

26

24

F184

10K

10K

3220

3282

1023

+3V3

F191

3274

100R

100R

6

F306

54

RA

ERROR

CORR.

SER. DATA

INTERFACE

DATA

27

7130 H15

7131 H14

7132 H13

7311-A G2

F139 A12

F143 A13

F146 A23193 D7

F147 B1

F149 B13

3275

100R

53

CFLG

INTERF.

PEAK

DET.

WCLK

28

+3V3

3161

F302

VDDD1P

EBU

SCLK

52

29

F151 C13

F154 C1

F155 C2

F156 C8

F157 C3

F159 C9

F160 D13202 E2

F162 D7

F163 D14

F139

2R2

2128

47u

2131

100n

3168

100R

51

DOEM

SUBCODE

MICROCONTROLLER

SER. DATA

LOOPBACK

INTERF.

VERSAT.

KILL

INTERF.

EF

30

F318

F321

F322

F183

3283

F164 D7

F165 D133206 E8

F166 E7

F167 E143211 F6

F168 E14

F170 E1

F171 E7

F172 E14

F173 E1

13 14

+5V

49

CL11|4

SBSY

SFSY

SUB

RCK

TEST3

STATUS

SILD

RAB

SCL

SDA

RESETn

SCLI

SDI

WCLI

V2|V3

VSSD1

KILL

32

F182

3219-D

3219-B

+5VHF +5VHF

10K

3286

150K

47K

3287

HFGND

47R

47R

F149

48

47

46

45

F311

44

43

42

41

40

39

38

37

36

35

34

33

HFGND

3171

10K

50

VSSD2

PROCESSOR

INTERFACE

TEST2

2232

100n

+5V

F315

F181

3219-C

47R

3219-A

47R

3285

3267

F143

F151

3284

0R

F165

VPROC

4K7

2233

1n5

7132

BC848B

1K

3280

F174 E7

F175 E7

F177 F1

F178 F9

F180 G1

F181 F13

F182 G13

F183 G12

F184 G11

F163

F167

F168

F172

10K

2280

100n

+5VHF

3268

F190

7005-B

74HCT08D

4

5

+5V

3185

SCLK_IN

DATA_IN

WCLK_IN

+5VHF

3269

100K

1K

HFGND

F190 H14

F191 H11

F192 H143273 B11

F302 B12

F303 B11

F304 B11

F305 B11

F306 B12

F308 B11

+5VY

14

7

3176

100R

10

11.2896MHz

+5V

4K7

4K7

3186

3214

0R

100R

BC858B

7131

6003

BAS216

3266

HFGND

6

F192

2230

4n7

3164

47R

3265

100K

2167

F309 C9

F310 C9

F311 D133284 D13

F312 D9

F313 D7

F314 D9

F315 D136003 H14

F318 G12

F319 G97005-B B14

DOBM5_CD

DOBM5_CD

100n

+5VHF

3270

7130

BC848B

HFGND

1

1

1

1

CL11

SCLK

WCLK

DATA

CL16

10K

MUTE

EF

1009

1010

1011

1012

RESET

SL

FO

RA

V4

MOT1

CFLG

SILD

SCL

SDA

HFDET

F321 G12

F322 G12

F324 G10

A

B

C

D

EE

F

G

H

3183

3202

10K

22K

+5VHF

100R

8

4

1029

HFGND

3213

1

2151

2166

2139 B11

2140 C4

2141 C6

2142 C9

2143 C4

2145 C9

2146 C6

2147 C1

+5VHF

2182

3

2

2148 C1

2149 C6

2150 C9

2151 D3

2152 D3

2155 D9

2156 D2

2157 D8

2159 D1

2160 D6

2161 D6

2162 E4

2163 E1

2166 E3

2167 E14

2168 F8

2170 F81000-10 G1

2172 F9

2173 F9

2174 F1

2175 F2

2178 G10

2182 F3

2183 F3

2184 G9

2185 G9

2186 G10

2189 G9

2191 H9

2200 H4

2201 H4

2230 H14

2232 H131020 G10

2236 F6

2280 F14

2285 G10

2286 G11

3160 A9

3161 B12

3162 B11

3164 B15

3169 B5

3171 B13

3172 B11

3174 B4

3177 C2

3178 C8

3179 C1

3180 C5

3181 C9

3182 D2

3183 D2

3184 D8

3185 D14

3186 D14

3187 D2

3188 D5

3189 D7

3190 D9

3191 D4

3192 D42154 D9

3194 D8

3195 E8

3196 E6

3197 E8

3198 E2

3199 E3

3200 E8

3201 E22164 E4

3203 E5

3204 E8

3205 E72169 F8

3208 F12171 F9

3212 F9

3213 F3

3214 F14

3219-A G13

3219-B G13

3219-C G13

3219-D G13

3220 G11

3225 H10

3229 H9

3265 H15

3266 H14

3267 H13

3268 H14

3269 H14

3270 H152233 H13

3274 B12

3275 B12

3276 B11

3279 B2

3280 F13

3281 F6

6 7 8 9 10 11 12 15

4

6

5

eyepattern

PULSE DENSITY MODULATION

+5VHF

2.5V

0,5us/DIV

3173

3174

430R

430R

2140

HFGND

2

3192

430R

2164

180p

2201

HFGND

2143

330p

2162

HFGND

1n5

F157

47u

47n

100n

2152

HFGND

7006

BFS20

3191

430R

1K5

3199

HFGNDHFGND

10u

2183

100n

180p

100p

2200

HFGND

+5VHF

3188

3203

560p

2K7

7009

BFS20

2K7

HFGND

>800mVpp

+5VHF

2K7

3169

7023

BFS20

2K7

3180

HFGND

HFGND

HFGND

390p

2149

680p

BF824

7024

HFGND

2130

100n

HFGND

2141

2n2

2146

1n5

BC848B

HFGND

7010

+5VHF

22n

3281

16

7

8

1

5

2

4

12

14

15

11

2160

HFGND

HFGND

+12V

3211

3

74HCT4052D

VCC

VEE

GND

0

1

2

3

+5VHF

47u

1K

3196

BC858B

2R2

2236

1K

HFGND

HFGND

2161

7007

HFGND

7025

10

0

0

4x

9

3

1

6

G4

HFGND

3

13

22n

HFGND

F156

9

3189

3193

3205

100n

1003

1

2

F313

390R

180R

10K

+3V3

F162

F164

F166

F171

F174

F175

2137

HFGND

3194

10K

3195

10K

3197

10K

3200

10K

3204

10K

3206

10K

22n

S1

S2

2138

3178

HFGND

1K

HFGND

HFGND

3184

100n

2R2

2157

2169

220p

2168

220p

8.4672MHz

2170

2142

22n

F310

2150

47n

F312

HFGND

220p

HFGND

CRIN

7

2171

47u

3190

220p

F178

30K

2172

33p

2184

47p

2145

3181

22K

2155

2154

2173

220p

3212

1M

1004

CX-5F

8M4672

HFGND

F309

F159

100n

F314

220p

7000

SAA7324

LDON

1

HFREF

2

HFIN

3

ISLICE

4

VSSA1

5

VDDA1

6

IREF

7

VRIN

8

D1

9

D2

10

D3

11

D4

12

R1

R2

13

VSSA2

14

15

CROUT

CRIN

16

33p

2185

2189

100n

2191

47u

3160

VDDA2

F319

3229

10K

63

64

V1

VERSATILE

INTERFACE

VREF GEN.

ADC

TIMING

LN19LP

17

18

1

1020

2R2

+3V3

FRONT

END

2285

1n5

V5

BITSTREAM DAC

1

1021

13 14 156789101112

9

eyepattern

2.5V

0,5us/DIV

CL 96532086_015.eps

080999

Page 34

Electrical and circuit diagrams

CD diagram 1B

GB 34CDR775 5.

123456

789

10 11

CD MAIN BOARD - CIRCUIT DIAGRAM 1B

SERVO DRIVERS PART

1002

A

TO TRAY

SWITCH

& MOTOR

B

TO SLEDGE

SWITCH

HOMESW

SGND

TRAY+

TRAY-

HOMESW

SGND

SL-

SL+

1001

& MOTOR

C

RAD+

1000-15

WCOIL

VCOIL

UCOIL

2113

V+

V-

W+

W-

1000-16

1000-14

1000-13

BC858B

7019

3102

47R

3117

47R

F114

100n

PGND

2112

RAD-

FOC-

FOC+

F116

PGND

F120

F123

F124

F125

F129

F132

+5V

100n

15

16

14

13

PGND

F113

2111

PGND

D

TO CDM

VAM1250

E

1006-1

F101

1

F

11

12

G

13

14

15

H

16

17

18

19

I

HALL+

F106

5

HALL-

1006-5

1006-11

11

1006-10

10

9

1006-9

1006-6

U+

6

U-

8

1006-8

1006-4

4

7

1006-7

1006-3

3

2

1006-2

TO TURN TABLE

MOTOR

PB CD MAIN 4236

CDR99

3104 123 4236

1

100n

F103

PH-B

1

2

SGND

3

4

PH-B

1

2

SGND

3

4

F112

TRAYSW

F107

F109

HOMESW

F115

F117

SGND

5V8

SGND

5V8

5V8

TDA7073A

16

3

14

13

12

4

10

9

5V8

TDA7073A

F133

F136

F138

F145

+5V

22K

3100

3101

22K

7020

3

A3

A2

5

A1

7

1

NC1

2

NC2

H1+

9

10

H1-

4

NC3

6

NC4

11

H2+

12

H2-

15

NC5

13

H3+

14

H3-

DRIVER

GAIN

CONTROL

+

-

+

-

+

-

+

-

+

-

+

GND

+5V

VCC

8

PGND

3148

0R

3152

0R

3155

0R

3159

0R

47u

PGND PGND

25

-+

H BIAS

MT1

5V8

SGND

5V8

5V8

SGND

5V8

F100

100n

2105

BA6856FB

RNF

VM2

VM1

REV

REV

PS

PS

EC

+

ECR

-

CNF

VH

FG1

FG2

FG3

MT2

29 30

PGNDPGND

16

14

13

12

10

2104

3

4

9

28

27

26

24

PGND

23

22

F300

21

F301

20

19

18

17

16

F118

100K

PGND

1008

1

1R

3135

3146

F131

VDD

PGND

100n

PGND

7021

-

+

+

-

1V6

1V6

VDD

F104

1R

3134

6002

BYG50D

2119

3107

560R

15

11

+3V3

7022

-

+

+

-

PH-B

100n

PGND

7031

BC847B

10n

1

2

5

6

7

8

1

2

15

11

6

7

1

2

3

4

5V

5V

1V6

1V6

3142

270R

5

1V6

1V6

8

1005

6001

BYG50D

2118

PGND

3106

180R

2282

2100

100n

100n

2102

3103

F111

3138

330p

330p

3140

0R

7030

BC847B

10n

3137

270R

F137

3104

180R

2281

3116

+3V3

47K

47K

SGND

3151

12K

3157

12K

PGND

F126

2106

SGND

SGND

47u

100n

2107

3132

22K

2110

100n

F134

RA

SGND

1024

1025

1

47u

2125

100n

2124

1321

PH-B

1

2

3

4

3113

7301

BC848B

T1

F121

3139

10K

22n

2117

3154

2114

100n

11

1

1R

+5V+5V

1K

10K

3110

3130

10K

2220

100n

+5V

3278

100R

7005-D

74HCT08D

14

12

13

7

F141

+12V

FO

+5V

F108

F122

+5VX

+5VY

+5V

STBY

2108

100n

F110

6

100R

7110-B

14

74HCT00D

7

3277

SL

+5VX

7110-C

74HCT00D

14

9

8

10

11

7

+5VX

7110-A

74HCT00D

3141

14

1

3

2

7

0R

4

5

1n

2103

22n

3136

2109

3145

270R

2120

F128

22u

2121

100n

12n

2122

3149

F135

F140

10n

3158

2126

+12V

6000

BYG50D

F119

47K

47K

3144

3143

+5V

F130

1K2

100n

+3V3

3114

3147

1K

1K2

T2

F127

2115

3156

12K

8K2

2116

150K

3150

12K

3115

4K7

22u

3105

560R

270R

2123

2127

1026

1

3131

1R

+5VX +5V

7110-D

14

74HCT00D

7

MOT1

F102

F105

12

13

100n

1027

10K

2221

TRAYIN

TRAYOUT

1

+12V

SL

RA

FO

MOT_UP

3129

MOT_SW

MOT1

234567891011

1000-13 E1

1000-14 E1

1000-15 D1