Philips BLF175 Datasheet

DISCRETE SEMICONDUCTORS

DATA SH EET

BLF175

HF/VHF power MOS transistor

Product specification

September 1992

Philips Semiconductors Product specification

HF/VHF power MOS transistor BLF175

FEATURES

• High power gain

• Low intermodulation distortion

• Easy power control

• Good thermal stability

• Withstands full load mismatch

• Gold metallization ensures

excellent reliability.

DESCRIPTION

Silicon N-channel enhancement

mode vertical D-MOS transistor

designed for large signal amplifier

applications in the HF/VHF frequency

range.

The transistor has a 4-lead, SOT123

flange envelope, with a ceramic cap.

All leads are isolated from the flange.

A marking code, showing gate-source

voltage (V

) information is provided

GS

for matched pair applications. Refer

to the 'General' section for further

information.

PIN CONFIGURATION

ok, halfpage

1

23

4

MSB057

g

MBB072

d

s

Fig.1 Simplified outline and symbol.

CAUTION

The device is supplied in an antistatic package. The gate-source input must

be protected against static charge during transport and handling.

WARNING

PINNING - SOT123

PIN DESCRIPTION

1 drain

2 source

3 gate

4 source

Product and environmental safety - toxic materials

This product contains beryllium oxide. The product is entirely safe provided

that the BeO disc is not damaged. All persons who handle, use or dispose of

this product should be aware of its nature and of the necessary safety

precautions. After use, dispose of as chemical or special waste according to

the regulations applying at the location of the user. It must never be thrown

out with the general or domestic waste.

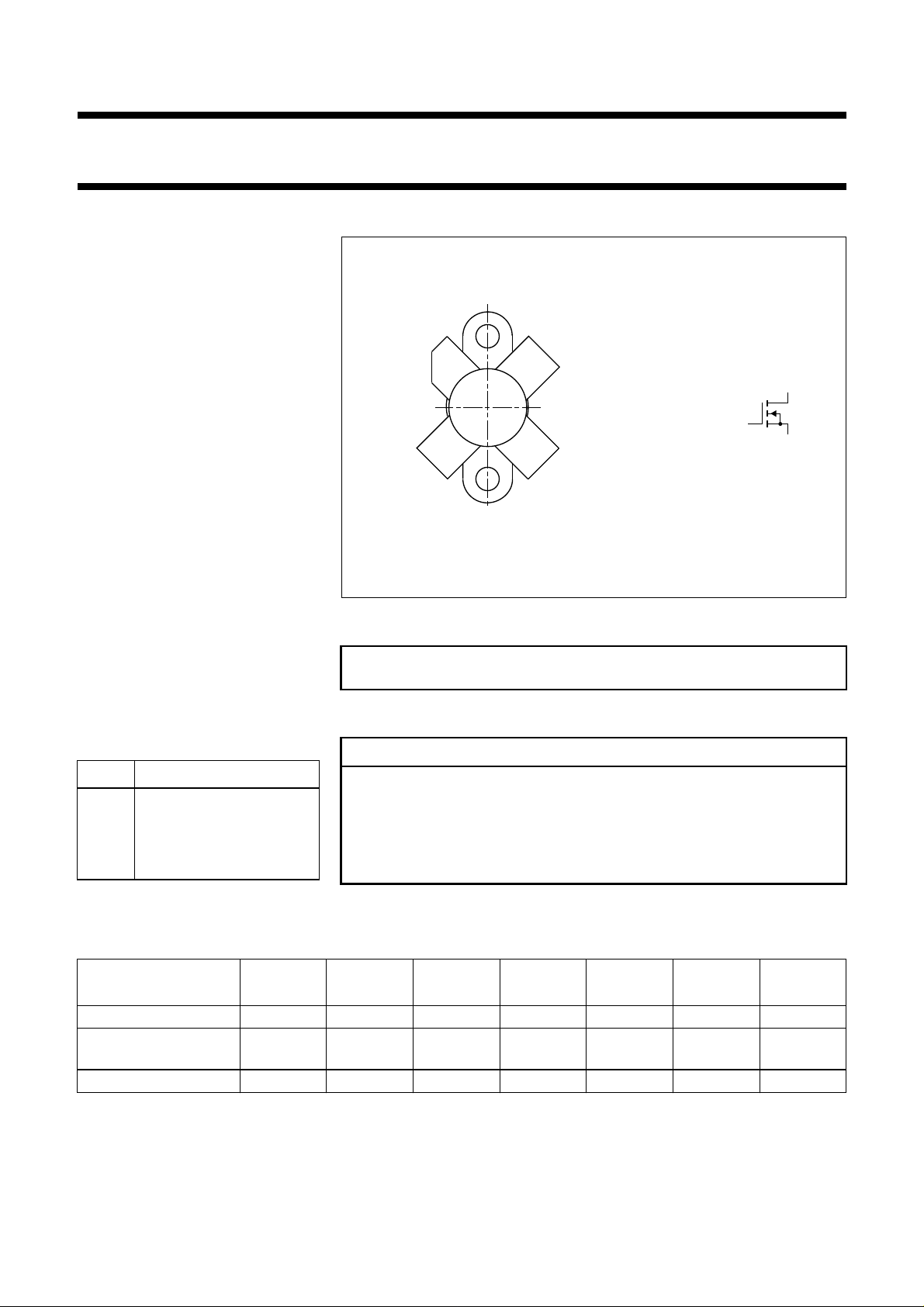

QUICK REFERENCE DATA

RF performance at T

MODE OF

OPERATION

= 25 °C in a common source test circuit.

h

(MH

f

)

Z

V

(V)

DS

I

DQ

(mA)

P

(W)

L

G

P

(dB)

η

(%)

D

d

(dB)

class-A 28 50 800 8 (PEP) > 24 −<−40

class-AB 28 50 150 30 (PEP) typ. 24 typ. 40

typ. −35

(note 1)

CW, class-B 108 50 30 30 typ. 20 typ. 65 −

Note

1. 2-tone efficiency.

3

September 1992 2

Philips Semiconductors Product specification

HF/VHF power MOS transistor BLF175

LIMITING VALUES

In accordance with the Absolute Maximum System (IEC 134).

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

DS

±V

GS

I

D

P

tot

T

stg

T

j

THERMAL RESISTANCE

drain-source voltage − 110 V

gate-source voltage − 20 V

DC drain current − 4A

total power dissipation up to Tmb = 25 °C − 68 W

storage temperature −65 150 °C

junction temperature − 200 °C

SYMBOL PARAMETER CONDITIONS

R

th j-mb

R

th mb-h

10

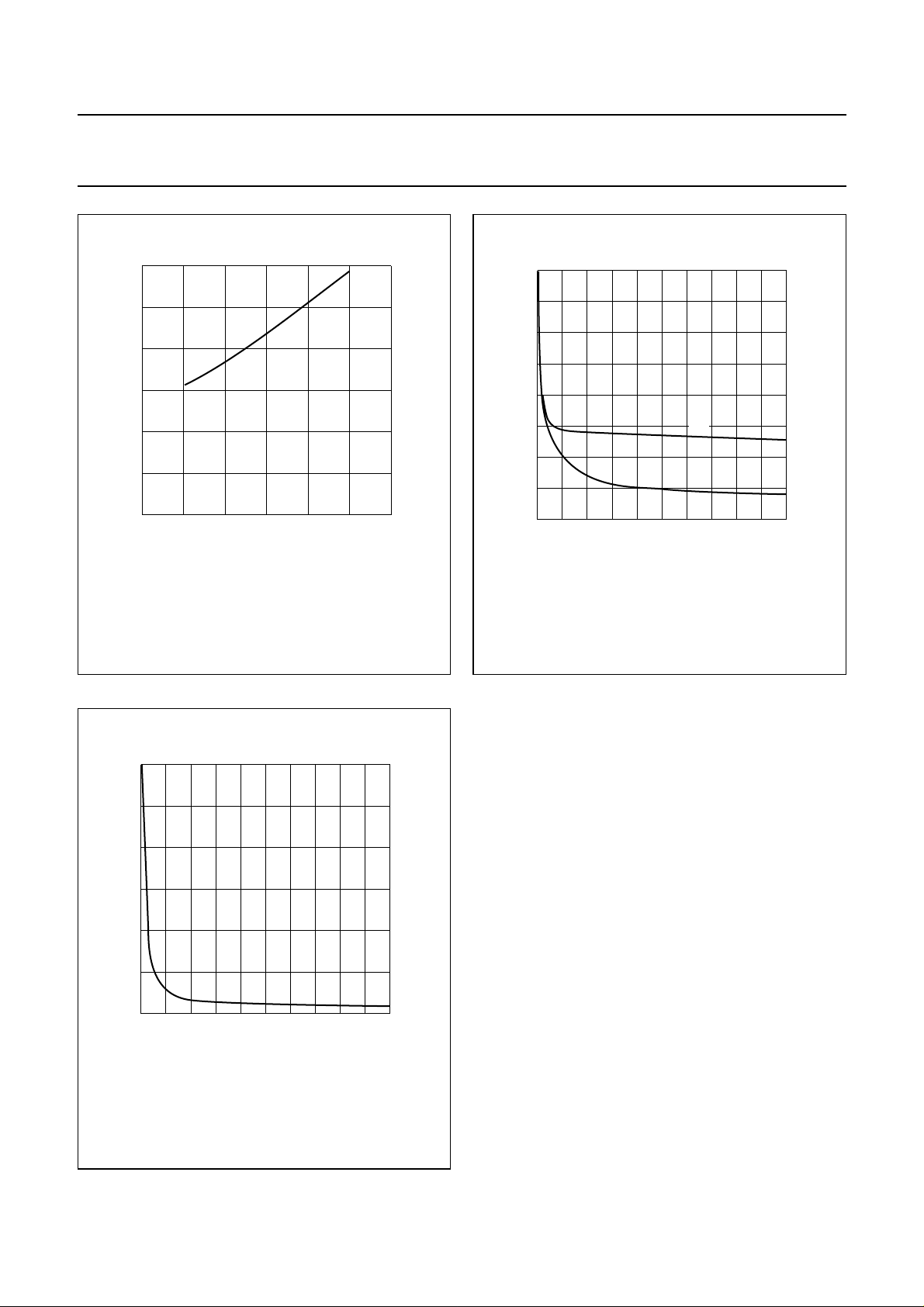

handbook, halfpage

I

D

(A)

1

−1

10

thermal resistance from junction to mounting base Tmb = 25 °C; P

thermal resistance from mounting base to heatsink Tmb = 25 °C; P

MRA905

(1)

110

(2)

VDS (V)

2

10

100

handbook, halfpage

P

tot

(W)

80

60

40

20

0

0 40 80 160

(2)

(1)

THERMAL

RESISTANCE

= 68 W 2.6 K/W

tot

= 68 W 0.3 K/W

tot

MGP063

120

T

(°C)

h

(1) Current is this area may be limited by R

(2) Tmb = 25 °C.

DS(on)

.

Fig.2 DC SOAR.

September 1992 3

(1) Continuous operation.

(2) Short-time operation during mismatch.

Fig.3 Power/temperature derating curves.

Philips Semiconductors Product specification

HF/VHF power MOS transistor BLF175

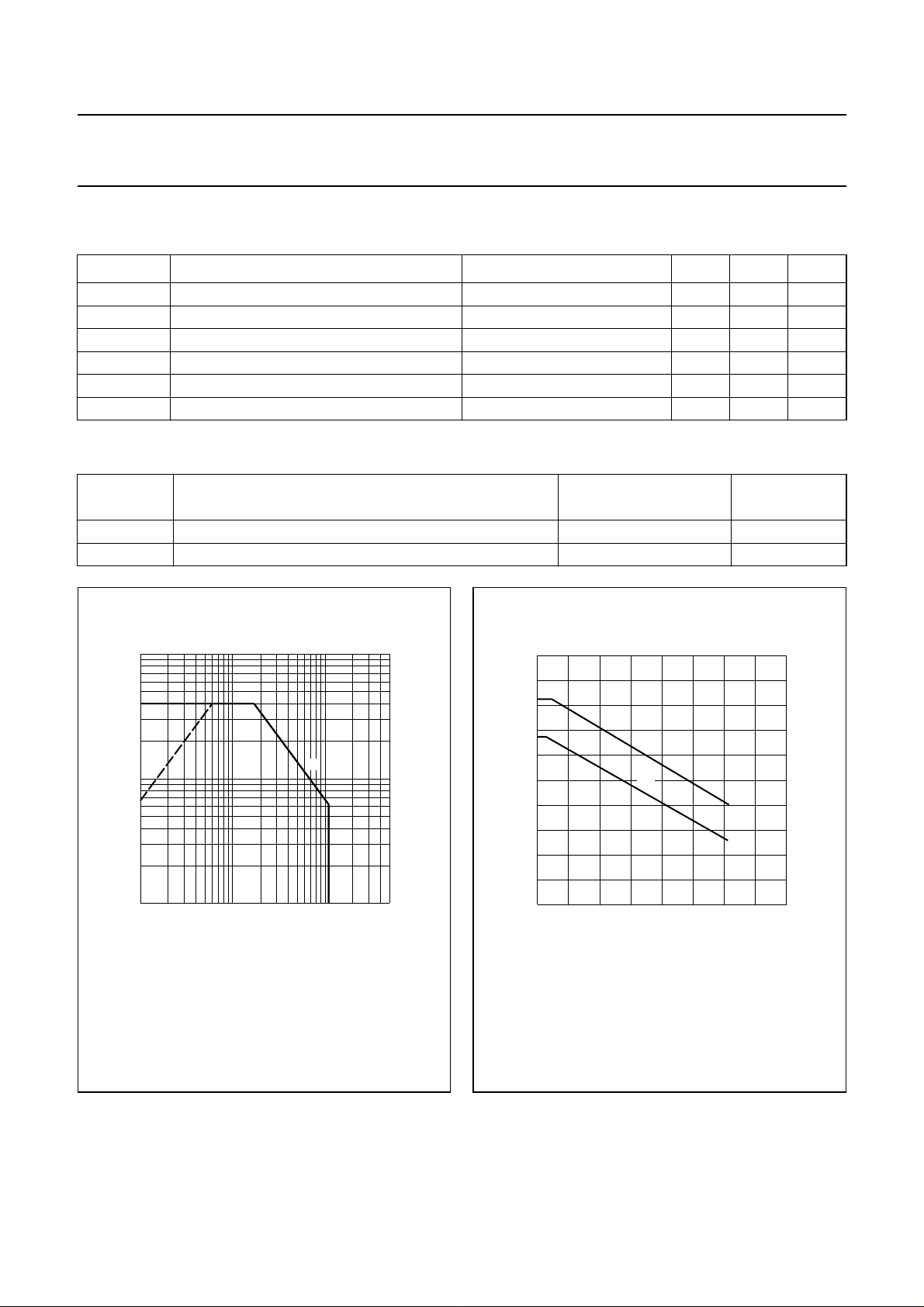

CHARACTERISTICS

T

= 25 °C unless otherwise specified.

j

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

(BR)DSS

I

DSS

I

GSS

V

GS(th)

∆V

GS

g

fs

R

DS(on)

I

DSX

C

is

C

os

C

rs

drain-source breakdown voltage ID = 10 mA; VGS = 0 110 −− V

drain-source leakage current VGS = 0; VDS = 50 V −−100 µA

gate-source leakage current ±VGS = 20 V; VDS = 0 −−1µA

gate-source threshold voltage ID = 10 mA; VDS = 10 V 2 − 4.5 V

gate-source voltage difference of

ID = 10 mA; VDS = 10 V −−100 mV

matched pairs

forward transconductance ID = 1 A; VDS = 10 V 1.1 1.6 − S

drain-source on-state resistance ID = 1 A; VGS = 10 V − 0.75 1.5 Ω

on-state drain current VGS = 10 V; VDS = 10 V − 5.5 − A

input capacitance VGS = 0; VDS = 50 V; f = 1 MHz − 130 − pF

output capacitance VGS = 0; VDS = 50 V; f = 1 MHz − 36 − pF

feedback capacitance VGS = 0; VDS = 50 V; f = 1 MHz − 3.7 − pF

handbook, halfpage

0

T.C.

(mV/K)

−1

−2

−3

−4

−5

10

VDS= 10 V.

−2

−1

10

ID (A)

Fig.4 Temperature coefficient of gate-source

voltage as a function of drain current, typical

values.

MGP064

GS

MGP065

(V)

handbook, halfpage

1

6

I

D

(A)

4

2

0

0

VDS= 10 V; Tj=25°C.

510

V

Fig.5 Drain current as a function of gate-source

voltage, typical values.

September 1992 4

Philips Semiconductors Product specification

HF/VHF power MOS transistor BLF175

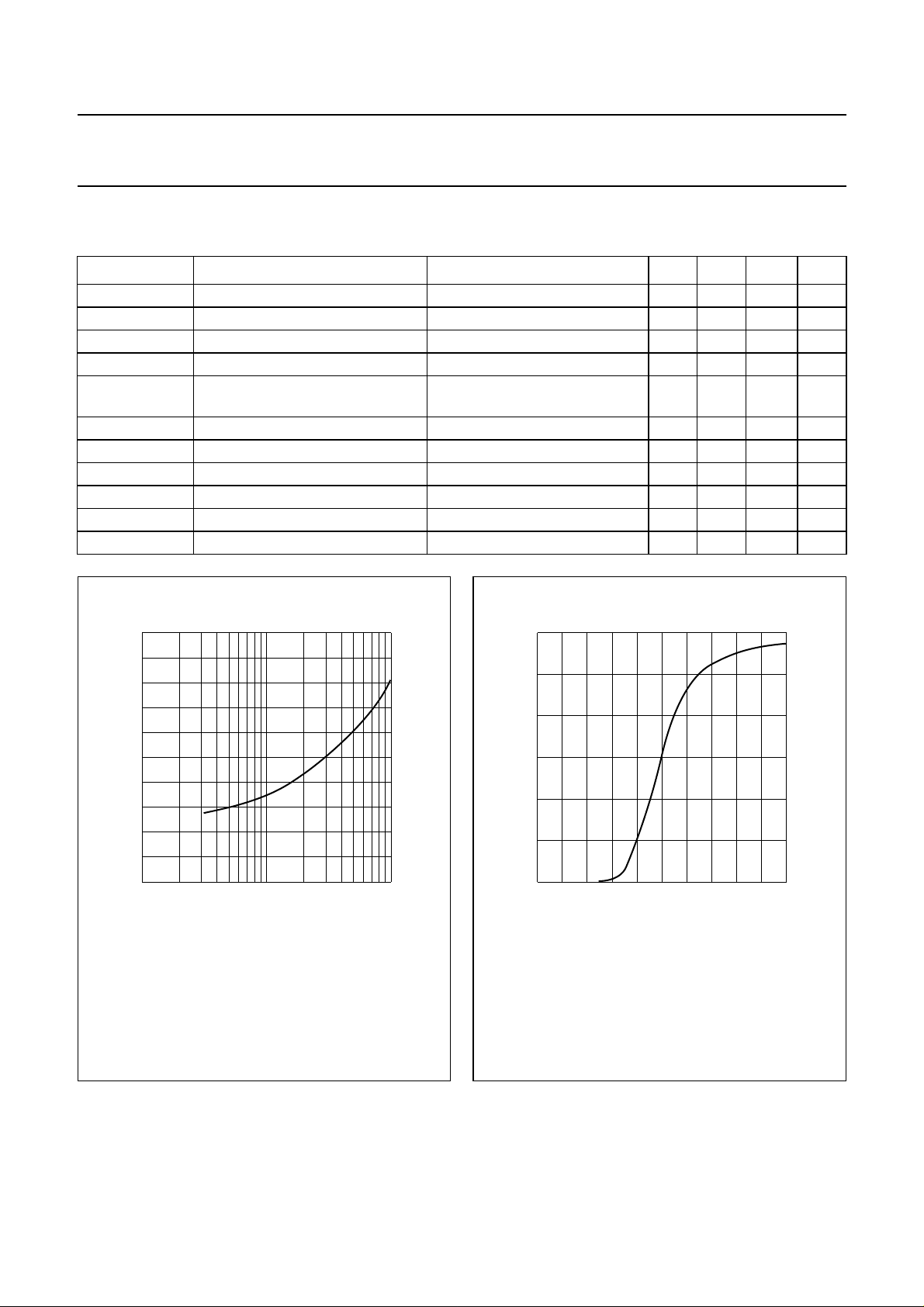

1.5

handbook, halfpage

R

DS(on)

(Ω)

1

0.5

0

0 50 100 150

ID= 1 A; VGS= 10 V.

Tj (°C)

Fig.6 Drain-source on-state resistance as a

function of junction temperature, typical

values.

MGP066

400

handbook, halfpage

C

(pF)

300

200

100

0

0

VGS= 0; f = 1 MHz.

C

is

C

os

10 50

20 30 40

MGP067

VDS (V)

Fig.7 Input and output capacitance as functions

of drain-source voltage, typical values.

150

handbook, halfpage

C

rs

(pF)

100

50

0

0

VGS= 0; f = 1 MHz.

10 50

20 30 40

V

Fig.8 Feedback capacitance as a function of

drain-source voltage, typical values.

MGP068

DS

(V)

September 1992 5

Philips Semiconductors Product specification

HF/VHF power MOS transistor BLF175

APPLICATION INFORMATION FOR CLASS-A OPERATION

T

= 25 °C; R

h

RF performance in SSB operation in a common source circuit.

f

= 28.000 MHz; f2 = 28.001 MHz.

1

= 0.3 K/W; unless otherwise specified.

th mb-h

P

(W)

L

f

(MHz)

V

(V)

DS

I

DQ

(mA)

G

(dB)

0 to 8 (PEP) 28 50 800 > 24

typ. 28

d

P

3

(dB)

(note 1)

>−40

typ. −44

d

5

(dB)

(note 1)

<−40

typ. −64

R

(Ω)

24

24

GS

Note

1. Stated figures are maximum values encountered at any driving level between the specified value of PEP and are

referred to the according level of either the equal amplified tones. Related to the according peak envelope power

these figures should be decreased by 6 dB.

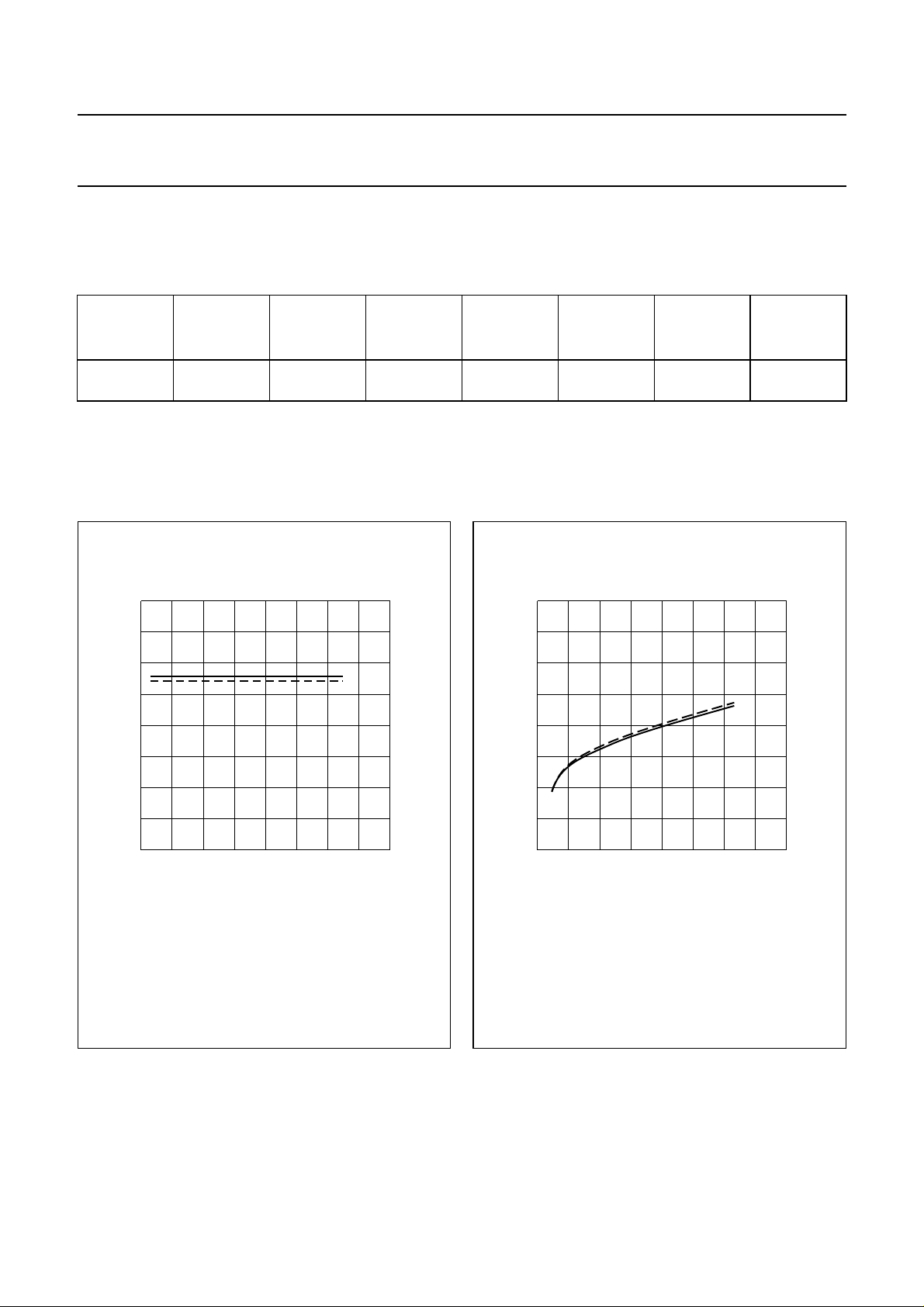

40

handbook, halfpage

G

p

(dB)

30

20

MGP069

d

(dB)

−20

−40

0

3

handbook, halfpage

MGP070

10

0

0 5 10 20

Class-A operation; VDS = 50 V; IDQ = 0.8 A;

RGS = 24 Ω;f1 = 28.000 MHz; f2 = 28.001 MHz.

solid line: Th = 25 °C.

dotted line: Th = 70 °C.

15

PL (W) PEP

Fig.9 Power gain as a function of load power,

typical values.

September 1992 6

−60

−80

0 5 10 20

Class-A operation; VDS = 50 V; IDQ = 0.8 A;

RGS = 24 Ω;f1 = 28.000 MHz; f2 = 28.001 MHz.

solid line: Th = 25 °C.

dotted line: Th = 70 °C.

15

PL (W) PEP

Fig.10 Third order intermodulation distortion as a

function of load power, typical values.

Loading...

Loading...