Page 1

DISCRETE SEMICONDUCTORS

DATA SH EET

BF904; BF904R

N-channel dual gate MOS-FETs

Product specification

File under Discrete Semiconductors, SC07

Philips Semiconductors

1995 Apr 25

Page 2

Philips Semiconductors Product specification

N-channel dual gate MOS-FETs BF904; BF904R

FEATURES

• Specially designed for use at 5 V supply voltage

• Short channel transistor with high transfer admittance to

input capacitance ratio

• Low noise gain controlled amplifier up to 1 GHz

• Superior cross-modulation performance during AGC.

APPLICATIONS

• VHF and UHF applications with 3 to 7 V supply voltage

such as television tuners and professional

communications equipment.

DESCRIPTION

Enhancement type field-effect transistor in a plastic

microminiature SOT143 and SOT143R package. The

handbook, halfpage

43

d

transistor consists of an amplifier MOS-FET with source

and substrate interconnected and an internal bias circuit to

ensure good cross-modulation performance during AGC.

CAUTION

The device is supplied in an antistatic package. The

gate-source input must be protected against static

discharge during transport or handling.

PINNING

PIN SYMBOL DESCRIPTION

1 s, b source

2 d drain

3g

4g

handbook, halfpage

34

gate 2

2

gate 1

1

d

g

2

g

1

21

Top view

BF904 marking code: M04.

MAM124

Fig.1 Simplified outline (SOT143) and symbol.

s,b

12

Top view

BF904R marking code: M06.

MAM125 - 1

Fig.2 Simplified outline (SOT143R) and symbol.

g

2

g

1

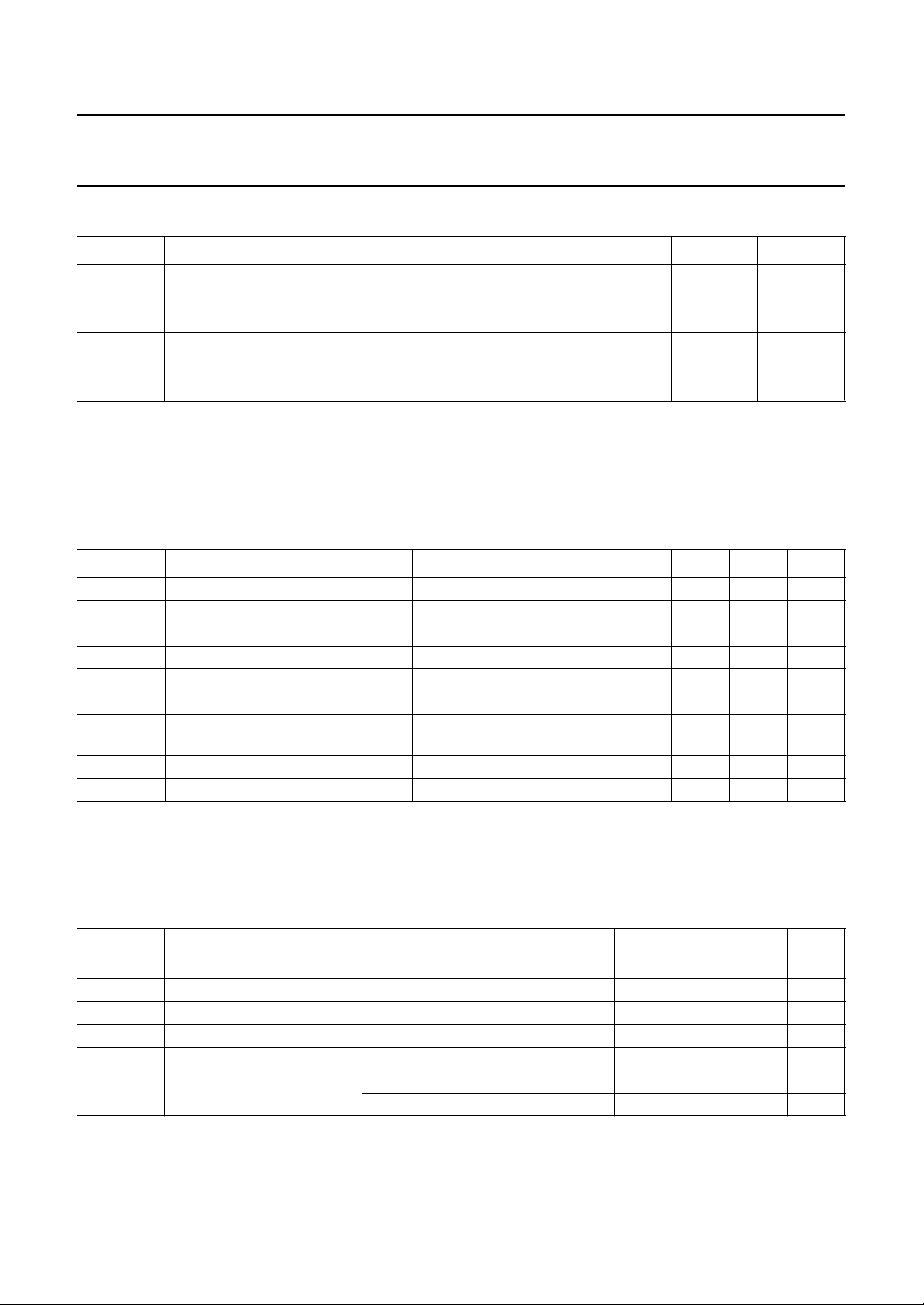

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

DS

I

D

P

tot

T

j

y

forward transfer admittance 22 25 30 mS

fs

C

ig1-s

C

rs

drain-source voltage −−7V

drain current −−30 mA

total power dissipation −−200 mW

operating junction temperature −−150 °C

input capacitance at gate 1 − 2.2 2.6 pF

reverse transfer capacitance f = 1 MHz − 25 35 fF

F noise figure f = 800 MHz − 2 − dB

s,b

1995 Apr 25 2

Page 3

Philips Semiconductors Product specification

N-channel dual gate MOS-FETs BF904; BF904R

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

DS

I

D

I

G1

I

G2

P

tot

T

stg

T

j

Note

1. Device mounted on a printed-circuit board.

drain-source voltage − 7V

drain current − 30 mA

gate 1 current −±10 mA

gate 2 current −±10 mA

total power dissipation see Fig.3

BF904 up to T

BF904R up to T

=50°C; note 1 − 200 mW

amb

=40°C; note 1 − 200 mW

amb

storage temperature −65 +150 °C

operating junction temperature − 150 °C

250

handbook, halfpage

P

tot

(mW)

200

150

100

50

0

0 50 100 150 200

BF904

BF904R

T

Fig.3 Power derating curves.

amb

MRA770

o

( C)

1995 Apr 25 3

Page 4

Philips Semiconductors Product specification

N-channel dual gate MOS-FETs BF904; BF904R

THERMAL CHARACTERISTICS

SYMBOL PARAMETER CONDITIONS VALUE UNIT

R

th j-a

R

th j-s

Notes

1. Device mounted on a printed-circuit board.

is the temperature at the soldering point of the source lead.

2. T

s

STATIC CHARACTERISTICS

=25°C; unless otherwise specified.

T

j

thermal resistance from junction to ambient note 1

BF904 500 K/W

BF904R 550 K/W

thermal resistance from junction to soldering point note 2

BF904 T

BF904R T

=92°C 290 K/W

s

=78°C 360 K/W

s

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

(BR)G1-SS

V

(BR)G2-SS

V

(F)S-G1

V

(F)S-G2

V

G1-S(th)

V

G2-S(th)

I

DSX

gate 1-source breakdown voltage V

gate 2-source breakdown voltage V

forward source-gate 1 voltage V

forward source-gate 2 voltage V

gate 1-source threshold voltage V

gate 2-source threshold voltage V

drain-source current V

G2-S=VDS

G1-S=VDS

G2-S=VDS

G1-S=VDS

G2-S

G1-S=VDS

G2-S

= 0; I

= 0; I

= 0; I

= 0; I

=4V; VDS=5V; ID=20µA 0.3 1 V

=5V; ID=20µA 0.3 1.2 V

=4V; VDS=5V;

= 10 mA 6 15 V

G1-S

= 10 mA 6 15 V

G2-S

= 10 mA 0.5 1.5 V

S-G1

= 10 mA 0.5 1.5 V

S-G2

813mA

RG1= 120 kΩ; note 1

I

G1-SS

I

G2-SS

gate 1 cut-off current V

gate 2 cut-off current V

G2-S=VDS

G1-S=VDS

= 0; V

= 0; V

=5V − 50 nA

G1-S

=5V − 50 nA

G2-S

Note

1. R

connects gate 1 to VGG= 5 V; see Fig.20.

G

DYNAMIC CHARACTERISTICS

Common source; T

=25°C; VDS= 5 V; V

amb

= 4 V; ID= 10 mA; unless otherwise specified.

G2-S

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

y

forward transfer admittance pulsed; Tj=25°C 222530mS

fs

C

ig1-s

C

ig2-s

C

os

C

rs

F noise figure f = 200 MHz; G

input capacitance at gate 1 f = 1 MHz − 2.2 2.6 pF

input capacitance at gate 2 f = 1 MHz 1 1.5 2 pF

drain-source capacitance f = 1 MHz 1 1.3 1.6 pF

reverse transfer capacitance f = 1 MHz − 25 35 fF

f = 800 MHz; G

= 2 mS; BS=B

S

S=GSopt

; BS=B

− 1 1.5 dB

Sopt

− 2 2.8 dB

Sopt

1995 Apr 25 4

Page 5

Philips Semiconductors Product specification

N-channel dual gate MOS-FETs BF904; BF904R

100

MLD268

o

T ( C)

j

40

Y

fs

(mS)

30

20

10

0

50 0 50 150

Fig.4 Transfer admittance as a function of the

junction temperature; typical values.

gain

(dB)

10

20

30

40

50

f =50 MHz.

0

01234

handbook, halfpage

reduction

Fig.5 Typical gain reduction as a function of

the AGC voltage.

MRA769

V (V)

AGC

120

handbook, halfpage

V

unw

(dB V)

µ

110

100

90

80

0 1020304050

VDS= 5 V; VGG= 5 V; fw= 50 MHz.

f

= 60 MHz; T

unw

=25°C; RG1= 120 kΩ.

amb

gain reduction (dB)

MRA771

Fig.6 Unwanted voltage for 1% cross-modulation

as a function of gain reduction; typical

values; see Fig.20.

20

I

D

(mA)

15

10

VDS=5V.

Tj=25°C.

5

0

0

0.4 2.0

V = 4 V

G2 S

0.8 1.2 1.6

3 V 2.5 V

V (V)

Fig.7 Transfer characteristics; typical values.

MLD270

2 V

1.5 V

1 V

G1 S

1995 Apr 25 5

Page 6

Philips Semiconductors Product specification

N-channel dual gate MOS-FETs BF904; BF904R

20

handbook, halfpage

I

D

(mA)

16

12

8

4

0

0

VDS=5V.

V

=4V.

G2-S

Tj=25°C.

210

V = 1.4 V

G1 S

1.3 V

1.2 V

1.1 V

1.0 V

0.9 V

468

Fig.8 Output characteristics; typical values.

MLD269

V (V)

DS

150

handbook, halfpage

I

G1

(µA)

100

50

0

0

VDS=5V.

Tj=25°C.

0.5 2.5

1.0 1.5 2.0

V = 4 V

G2 S

Fig.9 Gate 1 current as a function of gate 1

voltage; typical values.

MLD271

3.5 V

3 V

2.5 V

2 V

V (V)

G1 S

40

handbook, halfpage

y

fs

(mS)

30

20

10

0

0

VDS=5V.

Tj=25°C.

4 8 12 16 20

Fig.10 Forward transfer admittance as a

function of drain current; typical values.

MLD272

V = 4 V

G2 S

3.5 V

3 V

2.5 V

2 V

I (mA)

D

16

handbook, halfpage

I

D

(mA)

12

8

4

0

0

VDS=5V.

V

=4V.

G2-S

Tj=25°C.

10 50

20 30 40

MLD273

I (µA)

G1

Fig.11 Drain current as a function of gate 1 current;

typical values.

1995 Apr 25 6

Page 7

Philips Semiconductors Product specification

N-channel dual gate MOS-FETs BF904; BF904R

12

handbook, halfpage

I

D

(mA)

8

4

0

0

VDS= 5 V; V

RG1= 120 kΩ (connected to VGG); Tj=25°C.

15

=4V.

G2-S

234

Fig.12 Drain current as a function of gate 1

supply voltage (= VGG); typical values;

see Fig.20.

MLD275

V (V)

GG

20

handbook, halfpage

I

D

(mA)

15

10

5

0

0

VDS= 5 V; V

RG1 connected to VGG; Tj=25°C.

G2-S

R = 47 kΩ

24 8

=4V.

G1

68 kΩ

V = V (V)

GG DS

Fig.13 Drain current as a function of gate 1

(= VGG) and drain supply voltage;

typical values; see Fig.20.

MLD274

82 kΩ

100 kΩ

120 kΩ

150 kΩ

180 kΩ

220 kΩ

6

12

handbook, halfpage

I

D

(mA)

8

4

0

0246

VDS= 5 V; Tj=25°C.

RG1= 120 kΩ (connected to VGG).

V = 5 V

GG

4.5 V

4 V

3.5 V

3 V

V (V)

G2 S

MLD276

Fig.14 Drain current as a function of gate 2 voltage;

typical values; see Fig.20.

40

handbook, halfpage

I

G1

(µA)

30

20

10

0

0246

VDS= 5 V; Tj=25°C.

RG1= 120 kΩ (connected to VGG).

V = 5 V

GG

V (V)

Fig.15 Gate 1 current as a function of gate 2

voltage; typical values; see Fig.20.

MLB945

4.5 V

4 V

3.5 V

3 V

G2 S

1995 Apr 25 7

Page 8

Philips Semiconductors Product specification

N-channel dual gate MOS-FETs BF904; BF904R

2

10

handbook, halfpage

y

is

MLD277

(mS)

10

b

is

1

g

is

1

10

10

2

10

f (MHz)

VDS= 5 V; VG2=4V.

ID= 15 mA; T

amb

=25°C.

Fig.16 Input admittance as a function of frequency;

typical values.

f (MHz)

MLD278

3

10

ϕ

rs

(deg)

2

10

10

1

3

10

3

10

y

rs

(µS)

ϕ

2

10

rs

y

rs

10

3

10

1

10

2

10

VDS= 5 V; VG2=4V.

ID= 15 mA; T

amb

=25°C.

Fig.17 Reverse transfer admittance and phase as

a function of frequency; typical values.

MLD279

3

10

y

(mS)

2

10

fs

10

1

10

y

fs

ϕ

fs

2

10

f (MHz)

VDS= 5 V; VG2=4V.

ID= 15 mA; T

amb

=25°C.

Fig.18 Forward transfer admittance and phase as

a function of frequency; typical values.

10

ϕ

(deg)

10

1

2

fs

10

handbook, halfpage

y

os

(mS)

b

os

MLD280

1

g

1

10

2

10

10

os

2

10

f (MHz)

3

10

VDS= 5 V; VG2=4V.

ID= 15 mA; T

amb

=25°C.

Fig.19 Output admittance as a function of

frequency; typical values.

1995 Apr 25 8

Page 9

Philips Semiconductors Product specification

N-channel dual gate MOS-FETs BF904; BF904R

V

AGC

R1

10 kΩ

C1

R

GEN

50

V

4.7 nF

C2

4.7 nF

R2

50

Ω

I

Ω

R

G1

V

GG

DUT

V

DS

C3 12 pF

L1

450 nH

≈

C4

4.7 nF

R

50 Ω

MLD171

L

Fig.20 Cross-modulation test set-up.

1995 Apr 25 9

Page 10

Philips Semiconductors Product specification

N-channel dual gate MOS-FETs BF904; BF904R

Table 1 Scattering parameters: VDS=5 V; V

s

f

(MHz)

MAGNITUDE

(ratio)

11

ANGLE

(deg)

MAGNITUDE

(ratio)

= 4 V; ID=10mA

G2-S

s

21

ANGLE

(deg)

s

MAGNITUDE

(ratio)

12

ANGLE

(deg)

s

22

MAGNITUDE

(ratio)

ANGLE

(deg)

40 0.989 −3.4 2.420 175.7 0.000 79.9 0.993 −1.6

100 0.985 −8.3 2.414 169.1 0.001 78.3 0.992 −3.9

200 0.976 −16.4 2.368 158.8 0.003 80.3 0.987 −7.8

300 0.958 −24.1 2.301 148.5 0.004 73.7 0.980 −11.4

400 0.942 −32.0 2.251 138.8 0.005 70.7 0.974 −15.2

500 0.918 −39.3 2.170 129.5 0.005 67.2 0.966 −18.7

600 0.899 −46.0 2.080 120.7 0.005 67.8 0.958 −22.2

700 0.876 −52.6 2.001 112.1 0.005 68.6 0.951 −25.5

800 0.852 −58.8 1.924 103.2 0.005 72.9 0.944 −28.9

900 0.823 −64.9 1.829 94.7 0.005 78.7 0.937 −32.1

1000 0.800 −70.9 1.747 86.5 0.005 88.3 0.933 −35.2

1200 0.750 −82.4 1.621 70.7 0.005 120.5 0.928 −41.7

1400 0.719 −92.7 1.535 54.6 0.008 139.8 0.930 −48.4

1600 0.682 −102.5 1.424 39.4 0.010 137.8 0.924 −54.9

1800 0.642 −109.8 1.349 22.5 0.013 156.8 0.928 −62.9

2000 0.602 −116.5 1.283 1.1 0.018 175.1 0.928 −73.1

2200 0.547 −124.9 1.130 −15.1 0.014 172.6 0.887 −81.0

2400 0.596 −128.7 1.018 −49.1 0.040 −163.9 0.837 −95.8

2600 0.682 −132.6 0.979 −79.4 0.077 −164.0 0.778 −109.6

2800 0.771 −142.5 0.804 −116.2 0.120 178.8 0.629 −119.5

3000 0.793 −157.5 0.541 −153.5 0.149 158.3 0.479 −119.9

Table 2 Noise data: V

f

(MHz)

DS

= 5 V; V

= 4 V; ID=10mA

G2-S

F

min

(dB)

800 2.00 o.686 49.6 50.40

1995 Apr 25 10

Γ

opt

(ratio) (deg)

r

n

Page 11

Philips Semiconductors Product specification

N-channel dual gate MOS-FETs BF904; BF904R

PACKAGE OUTLINES

handbook, full pagewidth

Dimensions in mm.

10

max

3.0

0.150

30

max

0.090

0.1

max

10

max

o

o

0.88

0.75

0.60

o

1.1

max

2.8

1.9

43

2

1

0

0.1

TOP VIEW

0.48

1.7

0

0.1

B

A

1.4

1.2

M0.1 AB

2.5

max

0.2

MBC845

M

AB

Fig.21 SOT143.

handbook, full pagewidth

Dimensions in mm.

0.40

0.25

10

max

3.0

0.150

0.090

30

max

o

0.1

max

10

max

o

0.48

0.38

o

1.1

max

2.8

1.9

34

2

1

0.88

0.78

1.7

M0.1 B

TOP VIEW

B

A

1.4

1.2

MBC844

2.5

max

0.2

A

M

Fig.22 SOT143R.

1995 Apr 25 11

Page 12

Philips Semiconductors Product specification

N-channel dual gate MOS-FETs BF904; BF904R

DEFINITIONS

Data Sheet Status

Objective specification This data sheet contains target or goal specifications for product development.

Preliminary specification This data sheet contains preliminary data; supplementary data may be published later.

Product specification This data sheet contains final product specifications.

Limiting values

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or

more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation

of the device at these or at any other conditions above those given in the Characteristics sections of the specification

is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information

Where application information is given, it is advisory and does not form part of the specification.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these

products can reasonably be expected to result in personal injury. Philips customers using or selling these products for

use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such

improper use or sale.

1995 Apr 25 12

Loading...

Loading...