Philips BF1105 Service manual

DISCRETE SEMICONDUCTORS

DATA SH EET

BF1105; BF1105R; BF1105WR

N-channel dual-gate MOS-FETs

Product specification

Supersedes data of 1997 Dec 01

File under Discrete Semiconductors, SC07

1997 Dec 02

Philips Semiconductors Product specification

N-channel dual-gate MOS-FETs BF1105; BF1105R; BF1105WR

FEATURES

• Short channel transistor with high

forward transfer admittance to input

capacitance ratio

• Low noise gain controlled amplifier

up to 1 GHz.

• Internal self-biasing circuit to

ensure good cross-modulation

performance during AGC and good

DC stabilization.

APPLICATIONS

• VHF and UHF applications with 5 V

supply voltage, such as television

tuners and professional

communications equipment.

DESCRIPTION

Enhancement type N-channel

field-effect transistor with source and

substrate interconnected. Integrated

diodes between gates and source

protect against excessive input

voltage surges. The BF1105,

BF1105R and BF1105WR are

encapsulated in the SOT143B,

SOT143R and SOT343R plastic

packages respectively.

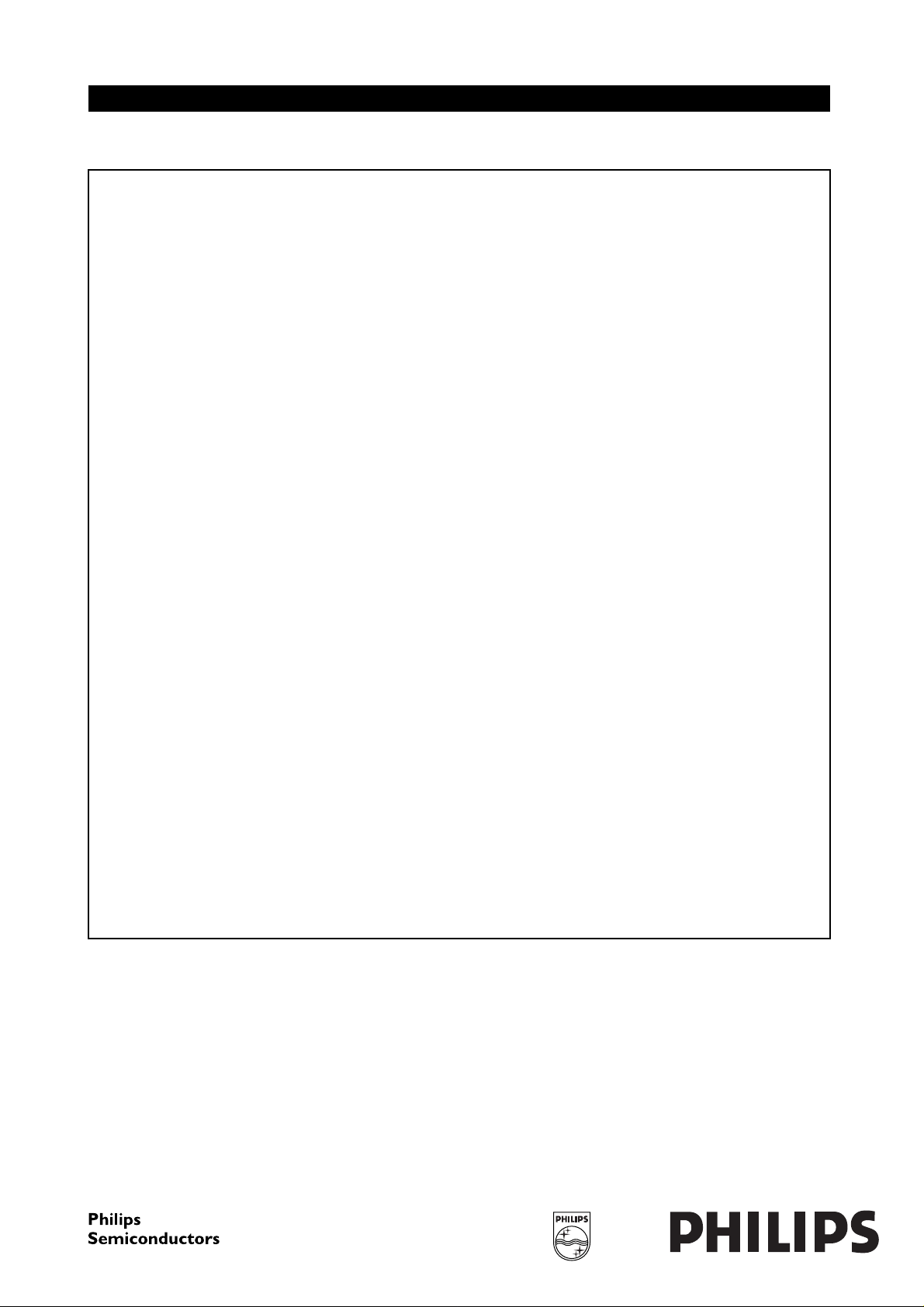

PINNING

PIN DESCRIPTION

1 source

2 drain

3 gate 2

4 gate 1

page

Top view

BF1105 marking code: NEp.

Fig.1 Simplified outline

(SOT143B).

MSB014

handbook, 2 columns

Top view

BF1105R marking code: NAp.

43

12

MSB035

Fig.2 Simplified outline

(SOT143R).

34

21

fpage

21

Top view

BF1105WR marking code: NA.

43

MSB842

Fig.3 Simplified outline

(SOT343R).

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

DS

I

D

P

tot

forward transfer admittance 25 31 − mS

y

fs

C

ig1-ss

C

rss

drain-source voltage −−7V

drain current −−30 mA

total power dissipation T

≤ 80 °C −−200 mW

amb

input capacitance at gate 1 − 2.2 2.7 pF

reverse transfer capacitance f = 1 MHz − 25 40 fF

F noise figure f = 800 MHz − 1.7 2.5 dB

X

mod

T

j

cross-modulation input level for k = 1% at 40 dB AGC 100 −−dBµV

operating junction temperature −−150 °C

CAUTION

This product is supplied in anti-static packing to prevent damage caused by electrostatic discharge during transport

and handling. For further information, refer to Philips specs.: SNW-EQ-608, SNW-FQ-302A and SNW-FQ-302B.

1997 Dec 02 2

Philips Semiconductors Product specification

N-channel dual-gate MOS-FETs BF1105; BF1105R; BF1105WR

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

DS

I

D

I

G1

I

G2

P

tot

T

stg

T

j

Note

1. Device mounted on a printed-circuit board.

drain-source voltage − 7V

drain current − 30 mA

gate 1 current −±10 mA

gate 2 current −±10 mA

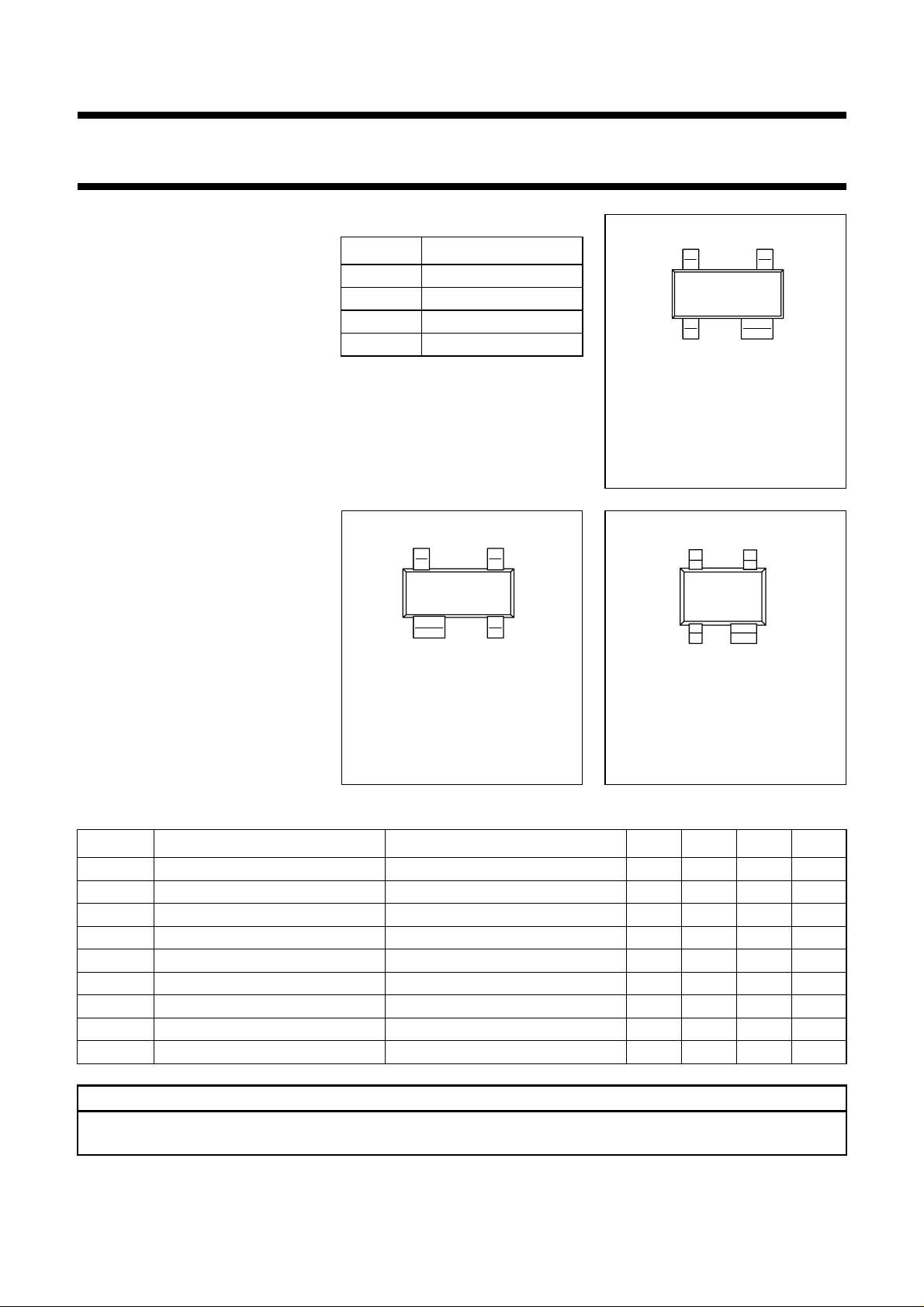

total power dissipation T

≤ 80 °C; note 1; see Fig.4 − 200 mW

amb

storage temperature −65 +150 °C

operating junction temperature − +150 °C

250

handbook, halfpage

P

tot

(mW)

200

150

100

50

0

0 40 80 160

120

T

amb

Fig.4 Power derating curve.

MGM243

(°C)

1997 Dec 02 3

Philips Semiconductors Product specification

N-channel dual-gate MOS-FETs BF1105; BF1105R; BF1105WR

THERMAL CHARACTERISTICS

SYMBOL PARAMETER CONDITIONS VALUE UNIT

R

th j-a

R

th j-s

Note

1. Device mounted on a printed-circuit board.

STATIC CHARACTERISTICS

=25°C unless otherwise specified.

T

j

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

(BR)DSS

V

(BR)G1-SS

V

(BR)G2-SS

V

G2-S (th)

I

DSX

I

G1-SS

I

G2-SS

thermal resistance from junction to ambient in free air note 1 350 K/W

thermal resistance from junction to soldering point 200 K/W

drain-source breakdown voltage V

gate 1-source breakdown voltage V

gate 2-source breakdown voltage V

gate 2-source threshold voltage V

self-biasing drain current V

gate 1 cut-off current V

gate 2 cut-off current V

G1-S=VG2-S

= 0; ID= 0; I

G2-S

G1-S=VDS

=5V; VDS=5V; ID=20µA 0.3 0.8 1.2 V

G1-S

=4V; VDS=5V 8 − 16 mA

G2-S

=5V; V

G1-S

G1-S=VDS

= 0; ID=10µA7−−V

=10µA7 −−V

G1-S

= 0; I

G2-S

= 0; V

=10µA7−−V

G2-S

= 0; ID=0 −−50 nA

=4V −−20 nA

G2-S

DYNAMIC CHARACTERISTICS

Common source; T

=25°C; V

amb

= 4 V; VDS= 5 V; self-biasing current; unless otherwise specified.

G2-S

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

y

forward transfer admittance pulsed; Tj=25°C2531−mS

fs

C

ig1-ss

C

ig2-ss

C

oss

C

rss

F noise figure f = 800 MHz; Y

G

p

X

mod

input capacitance at gate 1 f = 1 MHz − 2.2 2.7 pF

input capacitance at gate 2 f = 1 MHz − 1.6 − pF

output capacitance f = 1 MHz − 1.2 − pF

reverse transfer capacitance f = 1 MHz − 25 40 fF

S=YS opt

power gain GS= 2 mS; BS=B

BL=B

G

S

BL=B

; f = 200 MHz; see Fig.16

L opt

= 3.3 mS; BS=B

; f = 800 MHz; see Fig.17

L opt

; GL= 0.5 mS;

S opt

; GL= 1 mS;

S opt

cross-modulation input level for k = 1% at 0 dB AGC;

fw= 50 MHz; f

= 60 MHz; see Fig.18

unw

input level for k = 1% at 40 dB AGC;

f

= 50 MHz; f

w

= 60 MHz; see Fig.18

unw

− 1.7 2.5 dB

− 38 − dB

− 20 − dB

85 −−dBµV

100 −−dBµV

1997 Dec 02 4

Philips Semiconductors Product specification

N-channel dual-gate MOS-FETs BF1105; BF1105R; BF1105WR

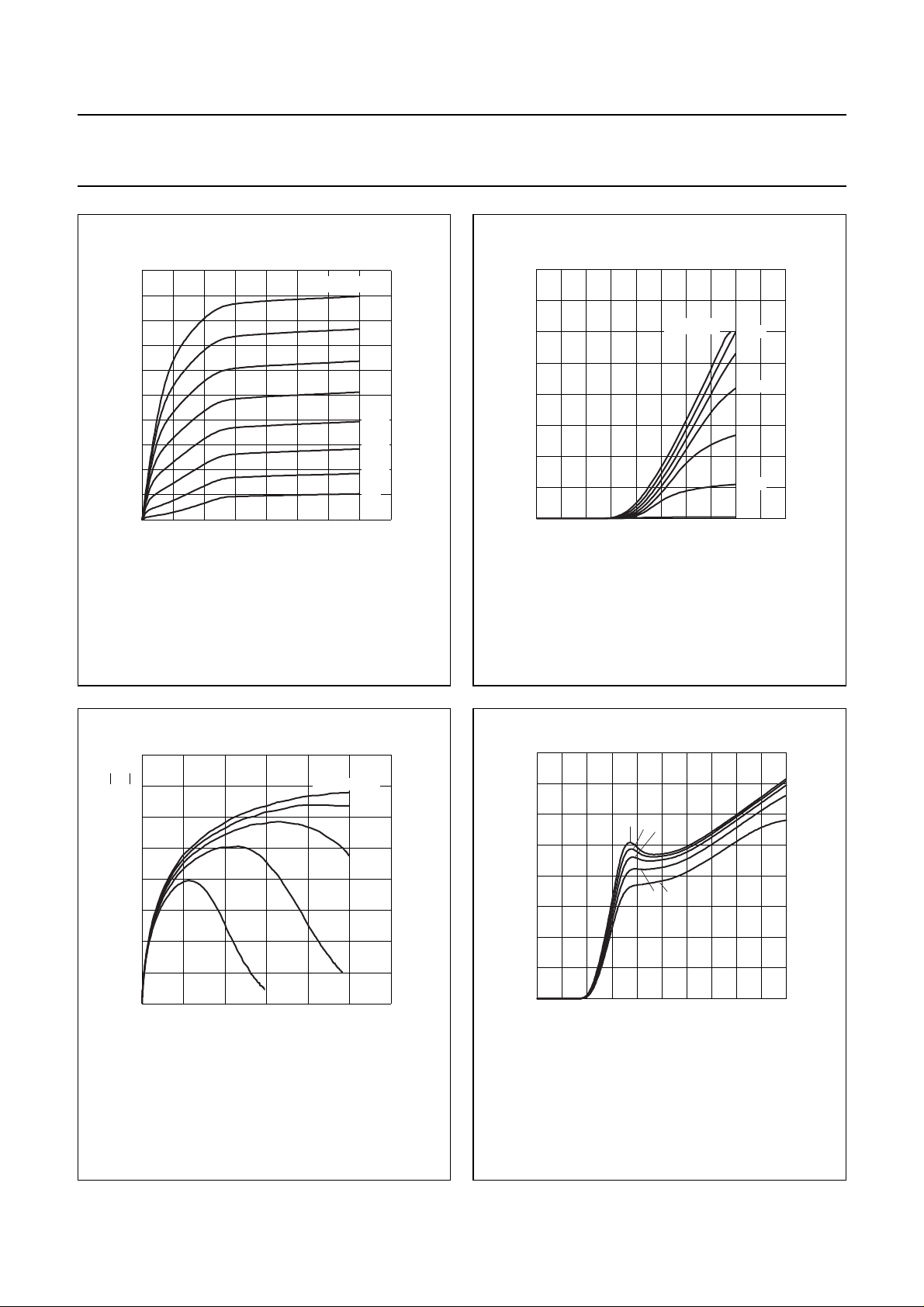

25

handbook, halfpage

I

D

(mA)

20

15

10

5

0

024 8

V

=4V.

G2-S

Tj=25°C.

Fig.5 Output characteristics; typical values.

V

G1

6

MGM244

= 1.7 V

1.6 V

1.5 V

1.4 V

1.3 V

1.2 V

1.1 V

1 V

VDS (V)

40

handbook, halfpage

I

D

(mA)

V

= 4 V

30

20

10

0

0

VDS=5V.

Tj=25°C.

0.5 2.5

G2-S

1 1.5 2

Fig.6 Transfer characteristics; typical values.

MGM245

3.5 V

3 V

2.5 V

2 V

1.5 V

1 V

VG1 (V)

V

G2-S

2.5 V

I

D (mA)

MGM246

= 4 V

3.5 V

3 V

40

handbook, halfpage

y

fs

(mS)

30

20

10

0

0 102030

VDS=5V.

Tj=25°C.

2 V

Fig.7 Forward transfer admittance as a function

of drain current; typical values.

16

handbook, halfpage

I

D

(mA)

12

8

4

0

0

(1) VDS=5V.

(2) VDS= 4.5V.

(3) VDS=4V.

(1)

(2)

(3)

(4) (5)

15

234

(4) VDS= 3.5 V.

(5) VDS=3V.

Fig.8 Drain current as a function of gate 2

voltage; typical values.

V

MGM247

G2-S

(V)

1997 Dec 02 5

Loading...

Loading...