Philips 74F109 Technical data

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I74F109D |

INTEGRATED CIRCUITS |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

74F109

Positive J-K positive edge-triggered flip-flops

Product specification |

1990 Oct 23 |

IC15 Data Handbook

m n r

Philips Semiconductors |

Product specification |

|||

|

|

|

|

|

|

|

|

|

|

Postive J- |

|

positive edge-triggered flip-flops |

74F109 |

|

K |

||||

|

|

|

|

|

|

|

|

|

|

FEATURE

•Industrial temperature range available (±40°C to +85°C)

DESCRIPTION

The 74F109 is a dual positive edge-triggered JK-type flip-flop

featuring individual J, K, clock, set, and reset inputs; also true and complementary outputs. Set (SD) and reset (RD) are asynchronous active low inputs and operate independently of the clock (CP) input.

The J and K are edge-triggered inputs which control the state changes of the flip-flops as described in the function table. Clock triggering occurs at a voltage level and is not directly related to the transition time of the positive-going pulse. The J and K inputs must be stable just one setup time prior to the low-to-high transition of the clock for predictable operation. The JK design allows operation as a D flip-flop by tying J and K inputs together. Although the clock input is level sensitive, the positive transition of the clock pulse between the 0.8V and 2.0V levels should be equal to or less than the clock to output delay time for reliable operation.

TYPE |

TYPICAL fmax |

TYPICAL SUPPLY CURRENT |

|

|

(TOTAL) |

|

|

|

74F109 |

125MHz |

12.3mA |

PIN CONFIGURATION

|

|

|

|

|

|

|

|

|

|

|

|

|

RD0 |

1 |

|

16 |

VCC |

||||||

|

|

|

|

J0 |

|

|

|

|

|

|

|

|

|

|

|

2 |

|

15 |

|

RD1 |

|||

|

|

|

|

|

|

|

|

|

J1 |

||

|

|

|

|

K0 |

3 |

|

14 |

||||

|

CP0 |

|

|

|

|

|

|

||||

|

4 |

|

13 |

|

K1 |

||||||

|

|

|

|

|

|

|

|

|

CP1 |

||

|

SD0 |

5 |

|

12 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q0 |

6 |

|

11 |

|

SD1 |

||||

|

|

|

|

|

|

|

|

|

Q1 |

||

|

|

Q0 |

7 |

|

10 |

||||||

GND |

|

|

|

|

|

|

|||||

8 |

|

9 |

|

Q1 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SF00135 |

||||

ORDERING INFORMATION

|

ORDER CODE |

|

||

DESCRIPTION |

|

|

PKG DWG # |

|

COMMERCIAL RANGE |

INDUSTRIAL RANGE |

|||

|

|

|||

|

VCC = 5V ±10%, Tamb = 0°C to +70°C |

VCC = 5V ±10%, Tamb = ±40°C to +85°C |

|

|

16-pin plastic DIP |

N74F109N |

I74F109N |

SOT38-4 |

|

|

|

|

|

|

16-pin plastic SO |

N74F109D |

I74F109D |

SOT109-1 |

|

|

|

|

|

|

INPUT AND OUTPUT LOADING AND FAN OUT TABLE

|

|

|

PINS |

DESCRIPTION |

74F (U.L.) HIGH/LOW |

LOAD VALUE HIGH/LOW |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

J0, |

J1 |

J inputs |

1.0/1.0 |

20μA/0.6mA |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

K inputs |

1.0/1.0 |

20μA/0.6mA |

K0, |

K1 |

||||||||||

|

CP0, |

CP1 |

Clock inputs (active rising edge) |

1.0/1.0 |

20μA/0.6mA |

||||||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

Set inputs (active Low) |

1.0/3.0 |

20μA/1.8mA |

|

SD0, |

SD1 |

|||||||||

|

|

|

|

|

|

|

|

|

Reset inputs (active Low) |

1.0/3.0 |

20μA/1.8mA |

|

RD0, |

RD1 |

|||||||||

Q0, Q1, |

|

|

|

|

Data outputs |

50/33 |

1.0mA/20mA |

||||

Q0, Q1 |

|||||||||||

NOTE: One (1.0) FAST unit load is defined as: 20μA in the High state and 0.6mA in the Low state. |

|

||||||||||

LOGIC SYMBOL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IEC/IEEE SYMBOL |

|

|

|

||

|

|

|

2 |

14 |

3 |

|

13 |

|

|

|

|

|

2 |

|

6 |

|

||||

|

|

|

|

|

|

|

|

1J |

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C1 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

||

4 |

|

CP0 |

J0 |

|

J1 |

K0 |

K1 |

|

|

1K |

7 |

|

||||||||

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

||||||||||||||

5 |

|

SD0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

1 |

|

RD0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

5 |

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

12 |

|

CP1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

14 |

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2J |

|

|||||

11 |

|

SD1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

15 |

|

RD1 |

Q0 |

Q0 |

Q1 Q1 |

|

|

C2 |

|

|

||||||||||

|

|

|

|

13 |

9 |

|

||||||||||||||

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2K |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11 |

|

|

||

VCC = Pin 16 |

|

6 |

7 |

10 |

|

9 |

|

|

S |

|

|

|||||||||

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

GND = Pin 8 |

|

|

|

|

|

|

|

SF00136 |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

SF00137 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

October 23, 1990 |

2 |

853±0337 00783 |

Philips Semiconductors |

Product specification |

|||

|

|

|

|

|

Postive J- |

|

positive edge-triggered flip-flops |

74F109 |

|

K |

||||

|

|

|

|

|

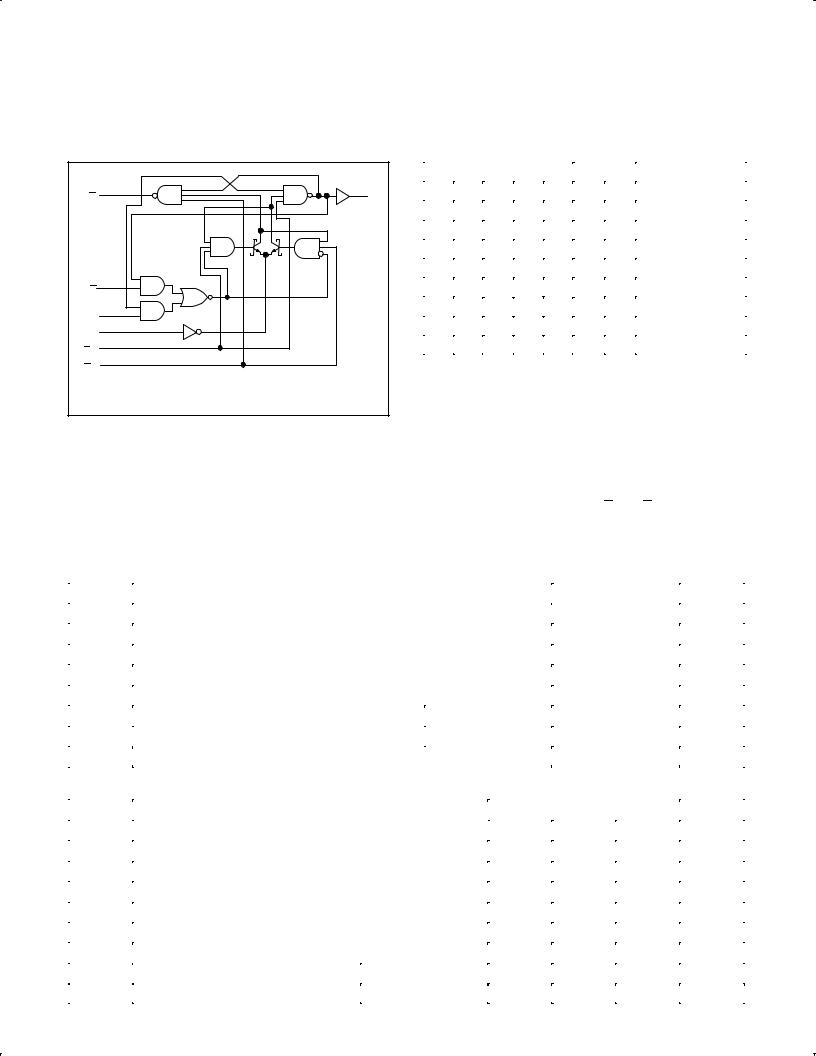

LOGIC DIAGRAM

Q |

7, 9 |

6, 10 |

|

Q |

|

|

3, 13 |

|

K |

|

|

J |

2, 14 |

|

4, 12 |

|

|

CP |

|

|

|

|

|

SD |

5, 11 |

|

|

|

|

RD |

1, 15 |

|

|

|

|

VCC = Pin 16 |

|

|

GND = Pin 8 |

|

|

|

|

SF00138 |

FUNCTION TABLE

|

|

|

|

|

|

INPUTS |

|

|

|

|

OUTPUTS |

OPERATING MODE |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SD |

|

RD |

|

CP |

|

J |

|

K |

|

Q |

|

Q |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

L |

|

H |

|

X |

|

X |

|

X |

H |

|

|

L |

Asynchronous set |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

H |

|

L |

|

X |

|

X |

|

X |

|

L |

|

H |

Asynchronous reset |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

L |

|

L |

|

X |

|

X |

|

X |

H |

|

H |

Undetermined* |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

H |

|

H |

|

↑ |

|

X |

|

X |

|

q |

|

|

|

|

|

Hold |

|||||

|

|

|

|

|

|

q |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

H |

|

H |

|

↑ |

|

h |

|

l |

|

|

|

|

q |

Toggle |

|||||||

|

|

|

|

|

|

q |

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

H |

|

H |

|

↑ |

|

h |

|

h |

H |

|

L |

Load º1º (set) |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

H |

|

H |

|

↑ |

|

l |

|

l |

|

L |

|

H |

Load º0º (reset) |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

H |

|

H |

|

↑ |

|

l |

|

h |

|

q |

|

|

|

|

|

Hold 'no changeº |

|||||

|

|

|

|

|

|

|

q |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTES: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

H |

= |

High-voltage level |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

h |

= |

High-voltage level one setup time prior to low-to-high |

||||||||||||||||||||

|

|

|

|

|

clock transition |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

L |

= |

Low-voltage level |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

l |

= |

Low-voltage level one setup time prior to low-to-high |

||||||||||||||||||||

|

|

|

|

|

clock transition |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

q |

= |

Lower case indicate the state of the referenced output |

||||||||||||||||||||

|

|

|

|

|

prior to the low-to-high clock transition |

|||||||||||||||||

X |

= |

Don't care |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

↑= Low-to-high clock transition

↑= Not low-to-high clock transition

* = Both outputs will be high if both SD and RD go low simultaneously

ABSOLUTE MAXIMUM RATINGS

(Operation beyond the limit set forth in this table may impair the useful life of the device. Unless otherwise noted these limits are over the operating free air temperature range.)

SYMBOL |

PARAMETER |

RATING |

UNIT |

||

|

|

|

|

|

|

VCC |

Supply voltage |

±0.5 to +7.0 |

V |

||

VIN |

Input voltage |

±0.5 to +7.0 |

V |

||

IIN |

Input current |

±30 to +5 |

mA |

||

VOUT |

Voltage applied to output in High output state |

±0.5 to VCC |

V |

||

IOUT |

Current applied to output in Low output state |

40 |

mA |

||

Tamb |

Operating free-air temperature range |

Commercial range |

0 to +70 |

°C |

|

|

|

|

|||

Industrial range |

±40 to +85 |

°C |

|||

|

|

||||

|

|

|

|

|

|

Tstg |

Storage temperature range |

±65 to +150 |

°C |

||

RECOMMENDED OPERATING CONDITIONS

SYMBOL |

PARAMETER |

|

LIMITS |

|

UNIT |

||

|

|

|

|||||

MIN |

NOM |

MAX |

|||||

|

|

|

|

||||

|

|

|

|

|

|

|

|

VCC |

Supply voltage |

4.5 |

5.0 |

5.5 |

V |

||

VIN |

High-level input voltage |

2.0 |

|

|

V |

||

VIL |

Low-level input voltage |

|

|

0.8 |

V |

||

IIK |

Input clamp current |

|

|

±18 |

mA |

||

IOH |

High-level output current |

|

|

±1 |

mA |

||

IOL |

Low-level output current |

|

|

20 |

mA |

||

Tamb |

Operating free-air temperature range |

Commercial range |

0 |

|

+70 |

°C |

|

|

|

|

|

|

|||

Industrial range |

±40 |

|

+85 |

°C |

|||

|

|

|

|||||

|

|

|

|

|

|

|

|

October 23, 1990 |

3 |

Loading...

Loading...