2N7002TB

60V N-CHANNEL ENHANCEMENT MODE MOSFET

FEA TURES

• R

, VGS@10V,IDS@500mA=5Ω

DS(ON)

• R

, VGS@4.5V,IDS@50mA=7.5Ω

DS(ON)

• Advanced Trench Process Technology

• High Density Cell Design For Ultra Low On-Resistance

• Specially Designed for Battery Operated Systems, Solid-State

Relays Drivers : Relays, Displays, Lamps, Solenoids, Memories, etc.

• Lead free in comply with EU RoHS 2002/95/EC directives.

• Green molding compound as per IEC61249 Std. . (Halogen Free)

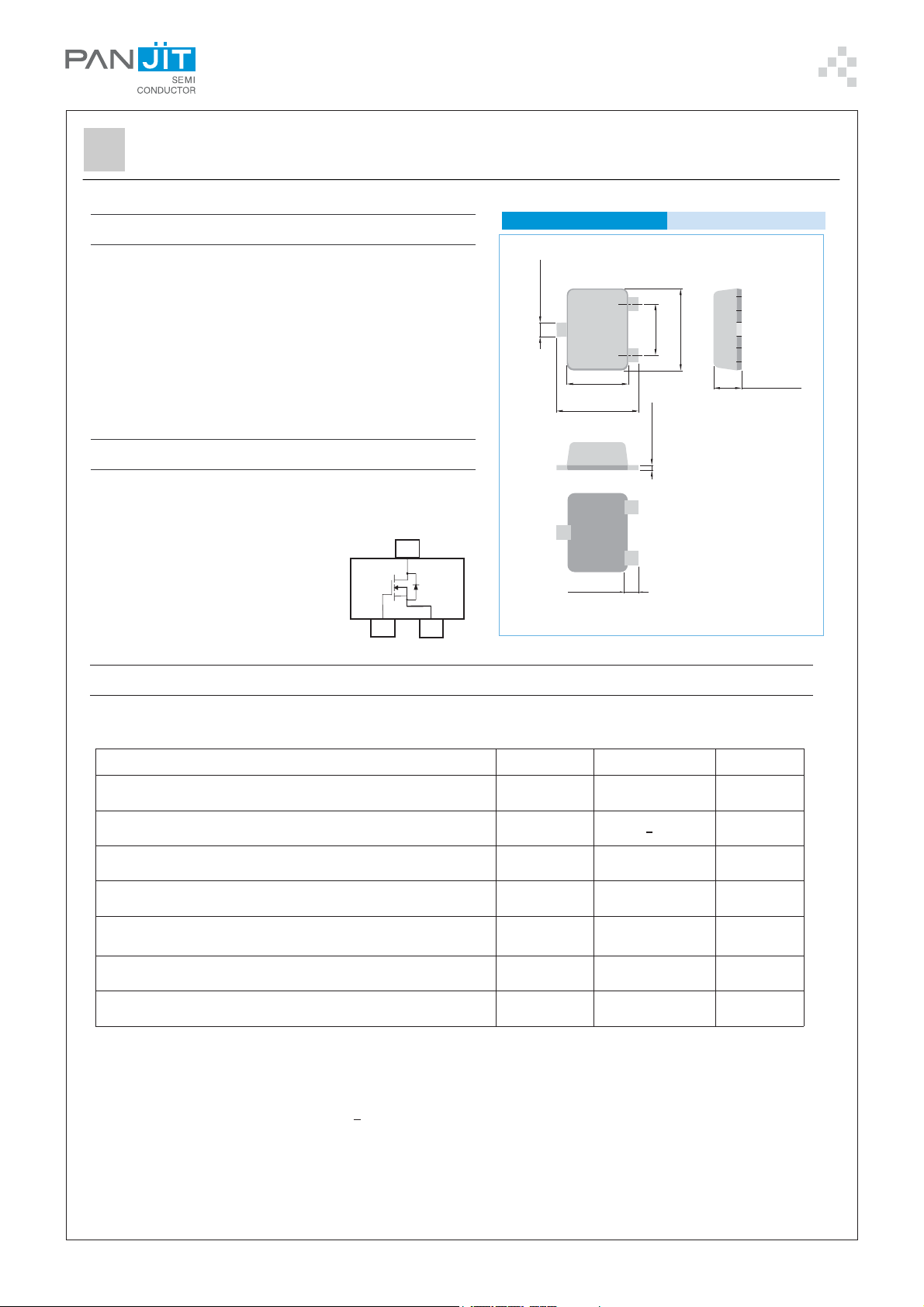

MECHANICAL DA T A

• Case: SOT-523, Plastic

• Terminals: Solderable per MIL-STD-750, Method 2026

• Approx. Weight: 0.002 grams

• Marking: 72

3

D

SOT-523

0.013(0.33)

0.009(0.23)

0.052(1.30)

0.043(1.10)

0.067(1.70)

0.059(1.50)

0.012(0.30)

0.004(0.10)

0.044(1.10)

0.035(0.90)

0.067(1.70)

0.007(0.17)

0.002(0.07)

0.059(1.50)

Unit inch(mm):

0.024(0.60)

0.019(0.50)

G

1

S

2

Maximum Ratings and Thermal Characteristics (TA=25OC unless otherwise noted )

RETEMARAPLOBMYSTIMILSTINU

egatloVecruoS-niarD V

egatloVecruoS-staG V

tnerruCniarDsuonitnoC I

)1(

tnerruCniarDdesluP

T

A

noitapissiDrewoPmumixaM

2

)detnuomBCP(ecnatsiseRlamrehTtneibmAot-noitcnuJ

egnaRerutarepmeTegarotSdnanoitcnuJgnitarepO T

52=oC

T

A

57=oC

DS

GS

D

I

DM

D

P

R

Θ

JA

JT,STG

06V

+ 02V

511Am

008Am

051

09

338

051ot55-

Wm

o

W/C

o

C

Note 1 : Maximum DC current limited by the package

2 : Surface mounted on FR4 board,t<10 sec

PAN JIT RESERVES THE RIGHT TO IMPROVE PRODUCT DSEIGN, FUNCTIONS AND RELIABILITY WITHOUT NOTICE

REV.0.1-FEB.10.2009

PAGE . 1

2N7002TB

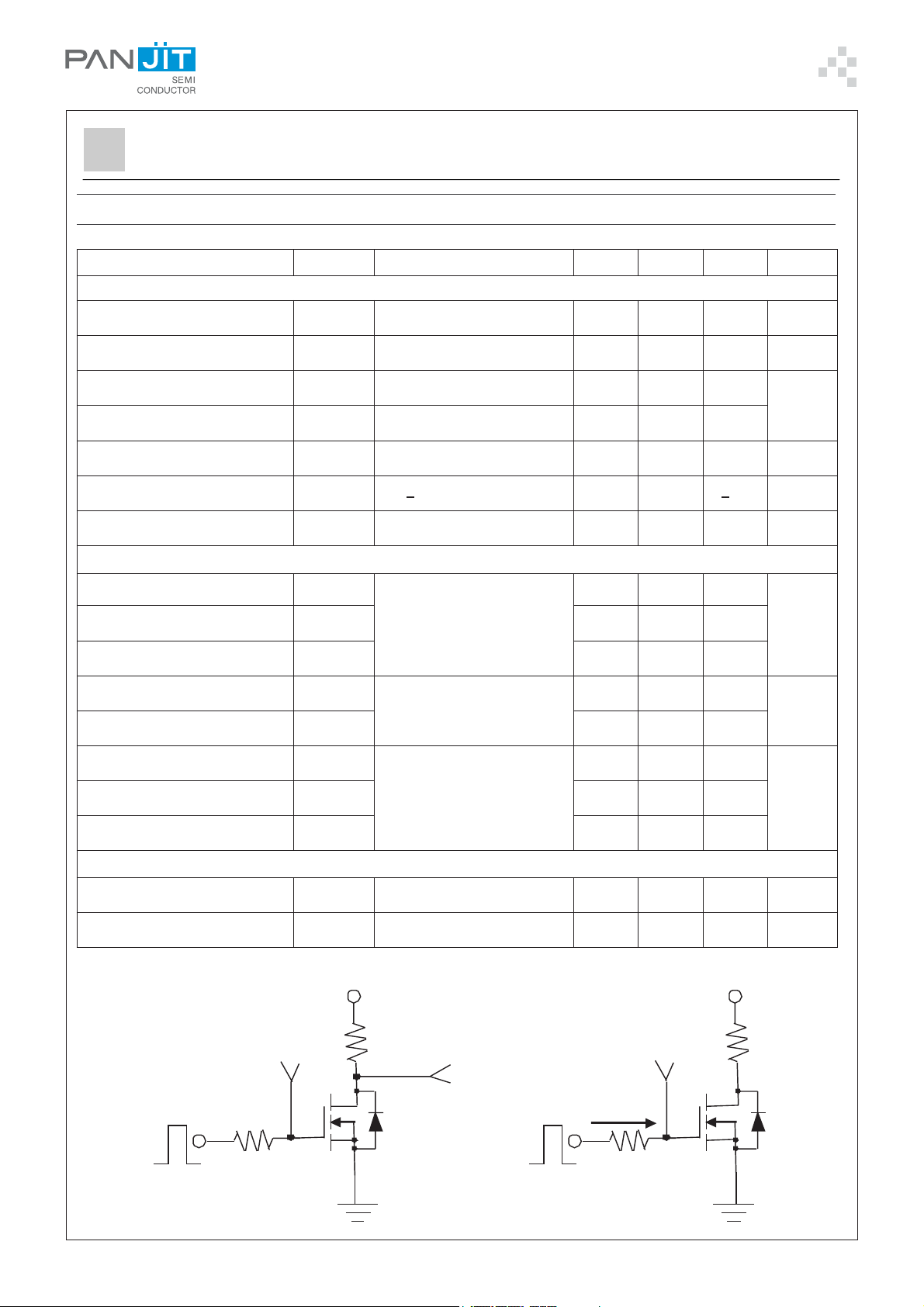

ELECTRICAL CHARACTERISTICS

RETEMARAPLOBMYSNOITIDNOCTSET.NIM.PYT.XAMSTINU

citatS

egatloVnwodkaerBecruoS-niarDVB DSS V GS I,V0= D 01= µA06--V

egatloVdlohserhTetaGV

tnerruCniarDegatloVetaGoreZI

egakaeLydoBetaGI

ecnatcudnocsnarTdrawroFg

GS( ht ) VDS V= GS I, D 052= µA1-5.2V

ecnatsiseRetatS-nOecruoS-niarDR

DS(ON) V GS I,V5.4= D Am05=--5.7

DS(ON) V GS I,V01= D Am005=--5

ecnatsiseRetatS-nOecruoS-niarDR

DSS V DS 06=,VVGS V0=--1

GSS V GS=+ V,V02 DS 0=V - - + 001An

FS V DS I,V51= D Am052=001--Sm

cimanyD

egrahCetaGlatoTQG

egrahCecruoS-etaGQ

egrahCniarD-etaGQ

emiTyaleDnO-nruTt

emiTyaleDffO-nruTt

ecnaticapaCtupnIC

GS -1.0-

V DS I,V51= D V,Am005= GS V5.4=

GD -80.0-

ON

OFF -1262

V DD R,V01= L 02= Ω

I

ISS

V DS V,V52= G

D V,Am005= GEN R,V01= G 01= Ω

S

Ω

µA

-6.07.0

Cn

-9 51

sn

-- 05

zHM0.1=f,V0=

FpecnaticapaCtuptuOCOSS -- 52

Switching

Test Circuit

REV.0.1-FEB.10.2009

ecnaticapaCrefsnarTesreveRC

RSS --5

edoiDniarD-ecruoS

tnerruCdrawroFedoiD.xaMIS ---052Am

egatloVdraeroFedoiDV

SD I S V,Am052= GS V0=-39.02.1

V

DD

Gate Charge

Test Circuit

R

V

IN

R

G

L

V

OUT

V

GS

1mA

R

G

V

DD

R

L

PAGE . 2

2N7002TB

MOUNTING PAD LAYOUT

SOT-523

0.053

(1.35)

0.019

(0.50)

0.016

(0.40)

0.019

(0.50)

0.017

(0.45)

Unit inch(mm):

ORDER INFORMATION

• Packing information

T/R - 4K per 7" plastic Reel

REV.0.1-FEB.10.2009

PAGE . 3

2N7002TB

Part No_packing code_Version

2N7002TB_R1_00001

For example :

RB500V-40_R2_00001

Serial number

Part No.

Version code means HF

Packing size code means 13"

Packing type means T/R

Packing Code XX Version Code XXXXX

Packing

type

1st Code

Packing

size code

2nd Code HF or RoHS 1st Code 2nd~5

th

T/B A N/A 0 HF 0 serial number

T/R R 7" 1 RoHS 1 serial number

B/P B 13" 2

T/P T 26mm X

TRR S 52mm Y

TRL L PBCU U

FORMING F PBCD D

Code

REV.0.1-FEB.10.2009

PAGE . 4

2N7002TB

Disclaimer

z Reproducing and modifying information of the document is prohibited without

permission from Panjit International Inc..

z Panjit International Inc. reserves the rights to make changes of the content herein the

document anytime without notification. Please refer to our website for the latest

document.

z Panjit International Inc. disclaims any and all liability arising out of the application or

use of any product including damages incidentally and consequentially occurred.

z Panjit International Inc. does not assume any and all implied warranties, including

warranties of fitness for particular purpose, non-infringement and merchantability.

z Applications shown on the herein document are examples of standard use and

operation. Customers are responsible in comprehending the suitable use in particular

applications. Panjit International Inc. makes no representation or warranty that such

applications will be suitable for the specified use without further testing or modification.

z The products shown herein are not designed and authorized for equipments requiring

high level of reliability or relating to human life and for any applications concerning

life-saving or life-sustaining, such as medical instruments, transportation equipment,

aerospace machinery et cetera. Customers using or selling these products for use in

such applications do so at their own risk and agree to fully indemnify Panjit

International Inc. for any damages resulting from such improper use or sale.

REV.0.1-FEB.10.2009

PAGE . 5

Loading...

Loading...