Panjit 2N7002DW Schematic [ru]

2N7002DW

60V N-Channel Enhancement Mode MOSFET

FEATURES

• R

, VGS@10V,IDS@500mA=5Ω

DS(ON)

• R

, VGS@4.5V,IDS@75mA=7.5Ω

DS(ON)

• Advanced Trench Process Technology

• High Density Cell Design For Ultra Low On-Resistance

• Specially Designed for Battery Operated Systems, Solid-State Relays

Drivers : Relays, Displays, Lamps, Solenoids, Memories, etc.

• /HDGIUHHLQFRPSO\ZLWK(85R+6(&GLUHFWLYHV

*UHHQPROGLQJFRPSRXQGDVSHU,(&6WG+DORJHQ)UHH

MECHANICAL DATA

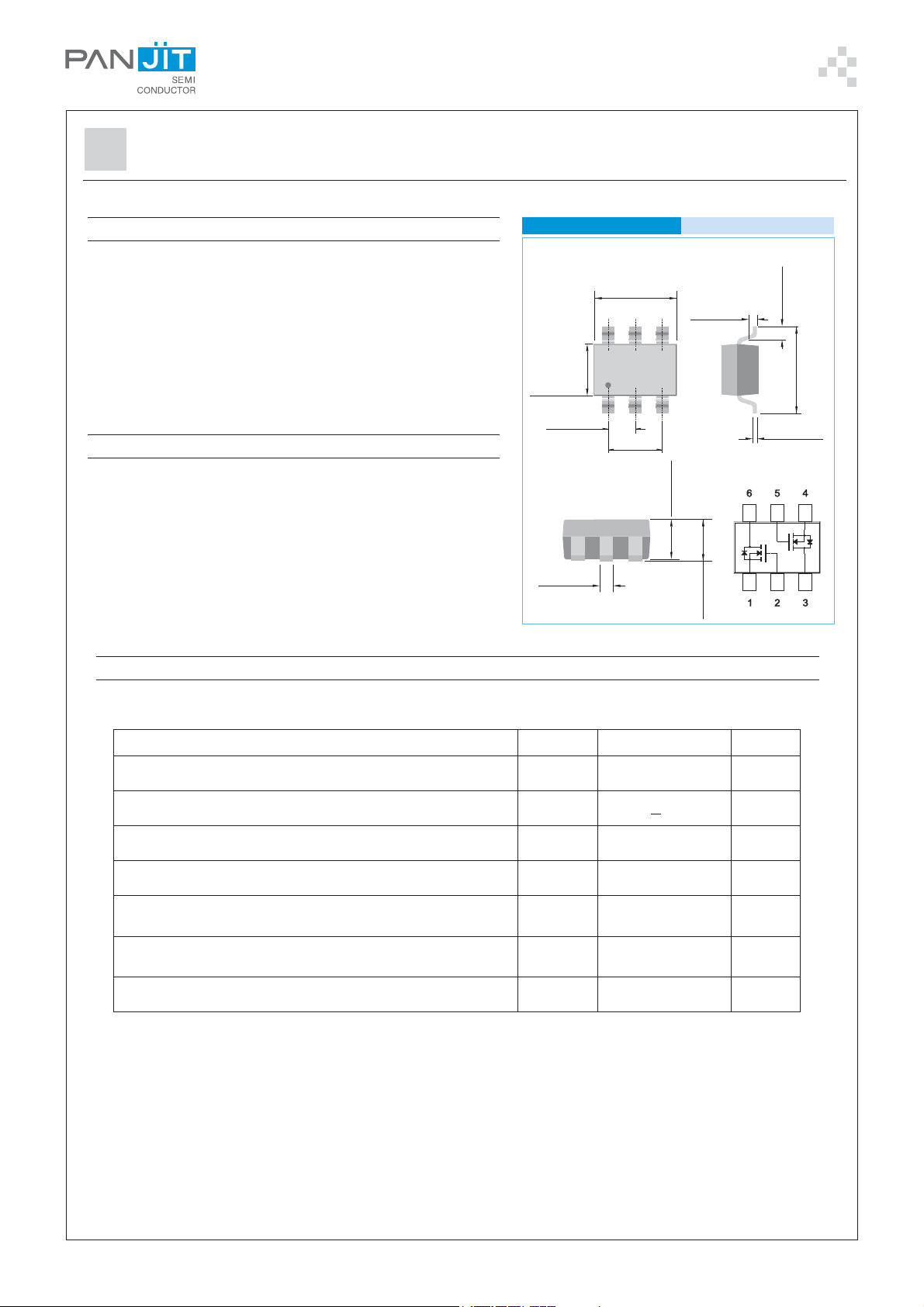

• Case: SOT-363 Package

• Terminals : Solderable per MIL-STD-750,Method 2026

• Apporx. Weight: 0.0002 ounces , 0.006grams

• Marking : 702

SOT-363

0.054(1.35)

0.045(1.15)

0.030(0.75)

0.021(0.55)

0.012(0.30)

0.005(0.15)

0.087(2.20)

0.074(1.90)

0.056(1.40)

0.047(1.20)

0.010(0.25)

040(1.00)

031(0.80)

0.

0.

MAX.

0.044(1.10)

Unit inch(mm):

0.018(0.45)

0.006(0.15)

0.087(2.20)

0.010(0.25)

0.003(0.08)

0.078(2.00)

Maximum RATINGS and Thermal Characteristics (TA=25OC unless otherwise noted )

RETEMARAPlobmyStimiLstinU

egatloVecruoS-niarDV

egatloVecruoS-etaGV

tnerruCniarDsuounitnoCI

)1

tnerruCniarDdesluP

noitapissiDrewoPmumixaM

egnaR

Note: 1. Maximum DC current limited by the package

2. Surface mounted on FR4 board, t < 10 sec

52=OC

T

A

TA57=OC

erutarepmeTegarotSdnanoitcnuJgnitarepO

2

)detnuomBCP(ecnatsiseRlamrehTtneibmAot-noitcnuJ

T

D

I

P

JT,GTS

R

θ AJ

SD

SG

MD

D

06V

+ 02V

511Am

008Am

002

021

051+ot55-

526

Wm

O

C

O

W/C

PAN JIT RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE

PAGE . 1REV.0.0-AUG.4.2008

2N7002DW

ELECTRICAL CHARACTERISTICS

retemaraPlobmySnoitidnoCtseT.niM.pyT.xaMstinU

citatS

nwodkaerBecruoS-niarD

egatloV

VB

SSD

V

SG

I,V0=

Au01=06--V

D

egatloVdlohserhTetaGV

etatS-nOecruoS-niarD

ecnatsiseR

etatS-nOecruoS-niarD

ecnatsiseR

tnerruC

egakaeLydoBetaGI

ecnatcudnocsnarTdrawroFg

R

R

niarDegatloVetaGoreZ

I

SSD

SSG

Sf

)ht(SG

)no(SD

)no(SD

VSDV=

V

SG

V

SG

V

SD

VSG=+ V,V02

V

SD

SGI,D

I,V01=

Au052=1-5.2V

I,V5.4=

D

I,V51=

D

Am57=--5.7

D

Am005=--5

V,V06=

V0=--1Au

SG

V0=--+001An

SD

Am052=002--Sm

Ω

cimanyD

egrahCetaGlatoTQ

g

V

SD

I,V51=

D

VSGV5=

egrahCniarD-etaGQ

emiTyaleDnO-nruTt

emiTyaleDffO-nruTt

ecnaticapaCtupnIC

ecnaticapaCtuptuOC

refsnarTesreveR

ecnaticapaC

dg

V

no

ffo

ssi

sso

C

ssr

DD

I

D

V

SD

R,V01=

L

V,Am005=

R

01= Ω

G

V,V52=

HM0.1=f

Am005=

02= Ω

V01=

NEG

V0=

SG

Z

-6.07.0

CnegrahCecruoS-etaGQsg-1.0-

-80.0-

-951

sn

-1262

--05

--52

Fp

--5

tnerruC

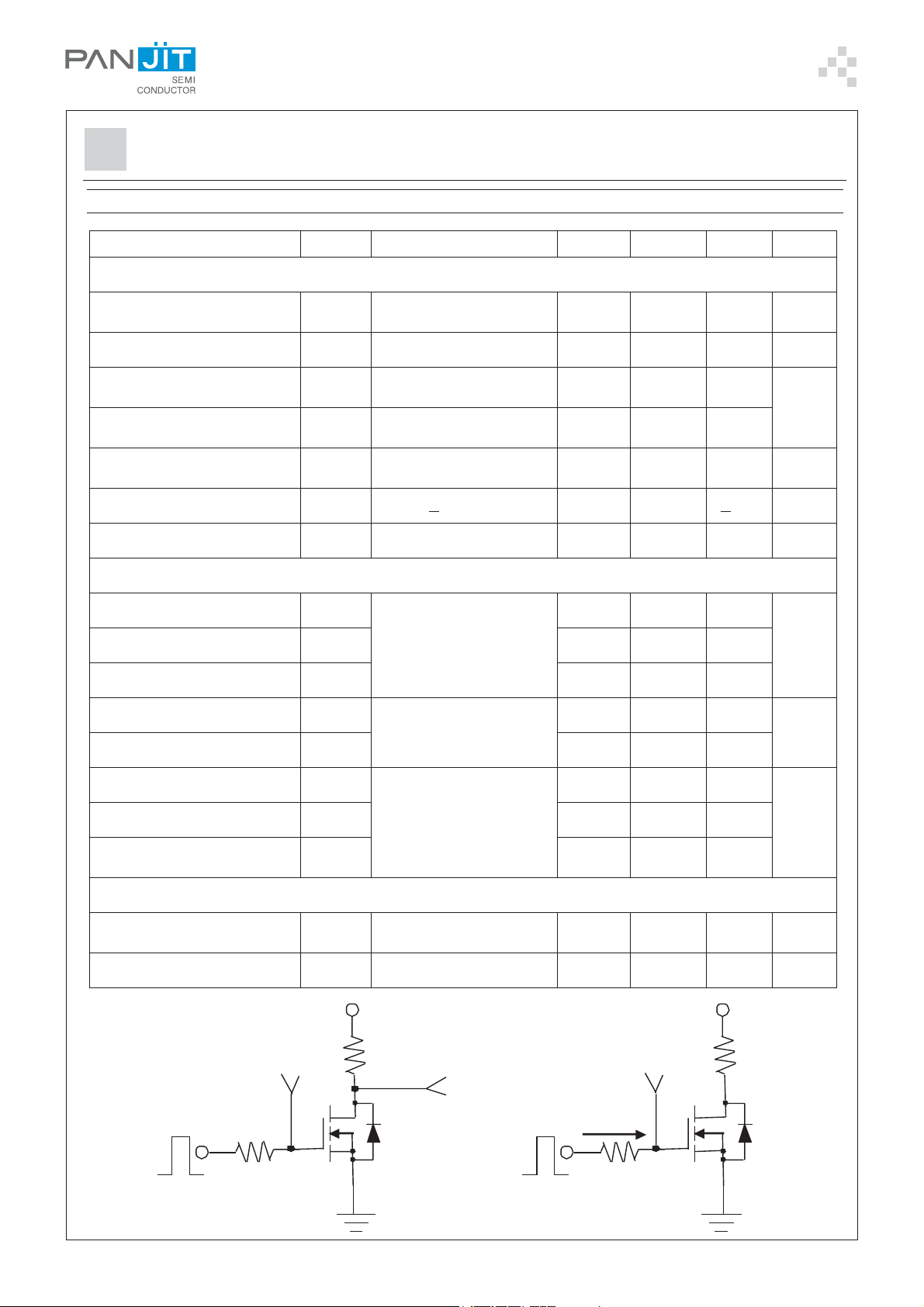

Switching

Test Circuit

edoiDniarD-ecruoS

drawroFedoiD.xaM

egatloVdrawroFedoiDV

I

s

DS

I

S

V

DD

---052Am

V,Am052=

SG

Gate Charge

Test Circuit

R

V

IN

R

G

L

V

OUT

V0=- 39.02.1V

V

DD

R

L

PAGE . 2REV.0.0-AUG.4.2008

1mA

R

V

GS

G

Loading...

Loading...