Page 1

This product complies with the RoHS Directive (EU 2002/95/EC).

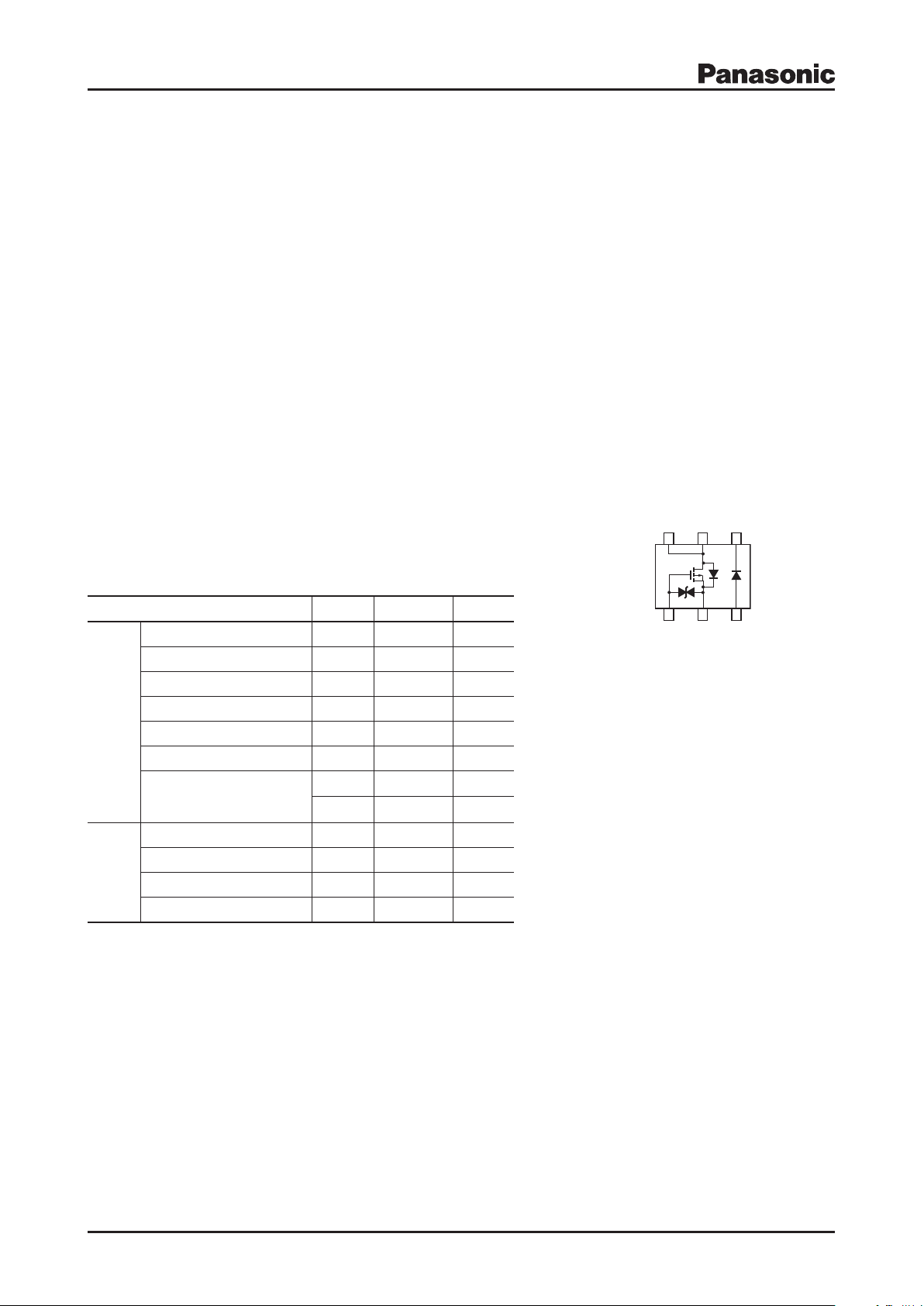

1

(G)2(S)3(A)

(K)

4

(D)

5

(D)

6

Multi Chip Discrete

MTM86628

Silicon P-channel MOS FET (FET)

Silicon epitaxial planar type (SBD)

For DC-DC converter

For switching circuits

Overview

MTM86628 is the composite MOS FET (P-channel MOS FET and Schottky

Barrier Diode) that is highly suitable for DC-DC converter and other switching

circuits.

Features

Built-in schottky barrier diode: VR = 15 V, IF = 700 mA

Low on-resistance: Ron = 300 mW (VGS = –4.0 V)

Low short-circuit input capacitance (Common source): C

Small surface mounting halogen-free package: WSSMini6-F1 (1.6 mm × 1.6

mm × 0.5 mm)

= 80 pF

iss

Package

Code

WSSMini6-F1

Pin Name

1: Gate 4: Cathode

2: Source 5: Drain

3: Anode 6: Drain

Marking Symbol: PL

Internal Connection

Absolute Maximum Ratings Ta = 25°C

Parameter Symbol Rating Unit

Drain-source surrender voltage V

Gate-source surrender voltage V

Drain current I

1

*

FET

Peak drain current

Channel temperature

Storage temperature T

Total power dissipation

Reverse voltage V

Forward current (Average) I

SBD

Junction temperature T

Storage temperature T

Note) *1: t = 10 µs, Duty Cycle < 1%

2: Glass epoxy board: 25.4 mm × 25.4 mm × 0.8 mm

*

Copper foil of the drain portion should have a area of 300 mm2 or more

3: Stand-alone (without the board)

*

P

P

F(AV)

I

T

D1

D2

DSS

GSS

D

DP

ch

stg

stg

2

*

3

*

R

j

–20 V

±12

–1.0 A

–4.0 A

150

–55 to +150

540 mW

150 mW

15 V

700 mA

125

–55 to +125

V

°C

°C

°C

°C

Publication date: November 2008 SJF00111AED 1

Page 2

This product complies with the RoHS Directive (EU 2002/95/EC).

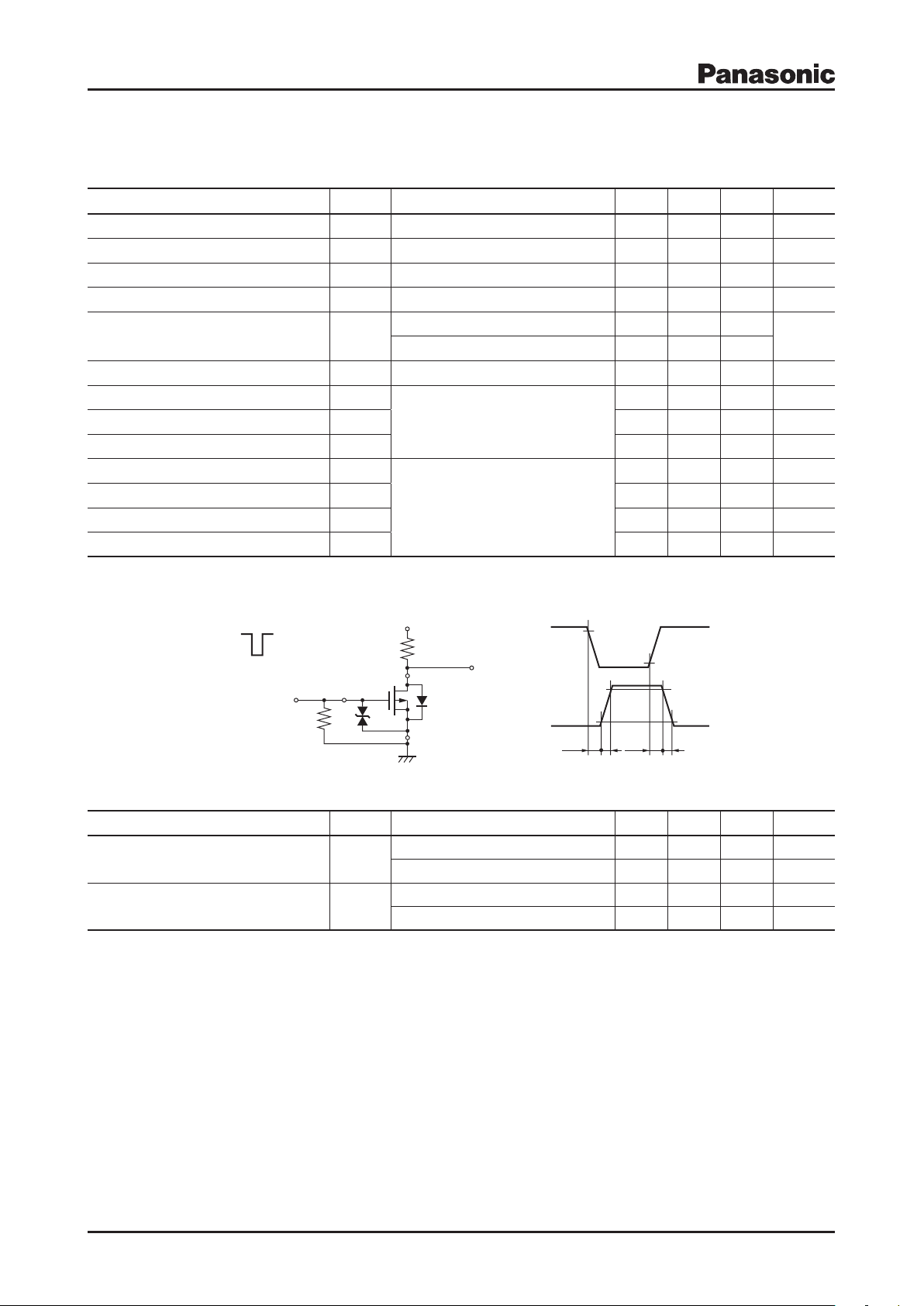

VDD = −15 V

PW = 10 µs

Duty Cycle ≤ 1%

ID = − 0.5 A

RL = 30 Ω

V

OUT

V

IN

D

G

S

V

IN

50 Ω

t

d(on)

t

d(off)

0 V

−4 V

V

IN

V

OUT

10%

90%

90%

10%

t

r

t

f

MTM86628

Electrical Characteristics Ta = 25°C±3°C

FET

Parameter Symbol Conditions Min Typ Max Unit

Drain-source surrender voltage V

Drain-source cutoff current

Gate-source cutoff current

Gate threshold voltage V

Drain-source ON resistance R

Forward transfer admittance

Short-circuit input capacitance (Common source)

Short-circuit output capacitance (Common source)

Reverse transfer capacitance (Common source)

Turn-on delay time

Rise time

*

Turn-off delay time

Fall time

Note) 1. Measuring methods are based on JAPANESE INDUSTRIAL STANDARD JIS C 7030 measuring methods for transistors.

2. *: ton , t

*

*

*

measurement circuit

off

DSSID

I

DSS

I

GSS

THID

DS(on)

Yfs

C

iss

C

oss

C

rss

t

d(on)

t

r

t

d(off)

t

f

= –1.0 mA, VGS = 0 –20 V

VDS = –20 V, VGS = 0 –1.0

VGS = ±10 V, VDS = 0

= –1.0 mA, VDS = –10 V – 0.45 –1.0 –1.5 V

ID = – 0.5 A, VGS = –4.0 V 300 420

ID = – 0.5 A, VGS = –2.5 V 420 560

ID = – 0.5 A, VDS = –10 V 1.0 2.0 S

80 pF

VDS = –10 V, VGS = 0, f = 1 MHz

12 pF

12 pF

12 ns

VDD = –15 V, VGS = –4.0 V, ID = – 0.5 A

6 ns

17 ns

10 ns

µA

±10 µA

mW

SBD

Parameter Symbol Conditions Min Typ Max Unit

Forward voltage V

Reverse current I

Note) Measuring methods are based on JAPANESE INDUSTRIAL STANDARD JIS C 7031 measuring methods for diodes.

2 SJF00111AED

IF = 500 mA 0.42 V

F

IF = 700 mA 0.45 V

VR = 6 V 90

R

VR = 15 V 250

µA

µA

Page 3

This product complies with the RoHS Directive (EU 2002/95/EC).

0

40

80

160120

0

400

200

600

MTM86628_ PD-T

a

Total power dissipation P

D

(mW)

Ambient temperature Ta (°C)

0 − 0.2 − 0.4 −1.0− 0.6 − 0.8

0

− 0.02

− 0.04

− 0.06

− 0.08

− 0.10

MTM86628_ ID-V

DS

Drain current I

D

(A)

Drain-source voltage VDS (V)

−1.4 V

−1.2 V

VGS = −1.6 V

0

−2 −10−8−6−4

0.1

0.2

0.3

0.4

0.5

MTM86628_ R

DS(on)-VGS

Drain-source ON resistance R

DS(on)

(Ω)

Gate-source voltage VGS (V)

ID = − 0.5 A

− 0.1 −1.0

0

0.1

0.2

0.3

0.4

0.5

MTM86628_ R

DS(on)-ID

Drain-source ON resistance R

DS(on)

(Ω)

Drain current ID (A)

VGS = 2.5 V

4.0 V

−50 −15 −20−10

0

20

40

60

120

100

80

MTM86628_ CX-V

DS

Drain-source voltage VDS (V)

Short-circuit input capacitance (Common source)

C

iss

,

Short-circuit output capacitance (Common source)

C

oss

,

Reverse transfer capacitance (Common source) C

rss

(pF)

C

iss

C

oss

C

rss

0 0.2 0.60.4

10

3

1

10

10

2

MTM86628_IF-V

F

Forward current I

F

(m

A

)

Forward voltage VF (V

)

Ta = 75°C

−25°C

25°C

0 9 1263 15

10

−1

1

10

10

3

10

2

10

4

MTM86628_IR-V

R

Reverse current I

R

(µ

A

)

Reverse voltage VR

(V)

Ta = 75°C

−25°C

25°C

0 2010 155

0

40

20

60

80

100

MTM86628_Ct-V

R

Terminal capacitance C

t

(pF)

Reverse voltage VR (V

)

MTM86628

Characteristics charts of FET

PD Ta ID VDS R

DS(on)

V

GS

R

ID CX V

DS(on)

DS

Characteristics charts of SBD

IF VF IR VR Ct V

R

SJF00111AED 4

Page 4

This product complies with the RoHS Directive (EU 2002/95/EC).

WSSMini6-F1 Unit: mm

+0.05

−0.02

1.60 ±0.05

1.00 ±0.05

(0.50) (0.50)

1.60 ±0.05

(0.10)

1.40 ±0.05

0.50 ±0.05

0.20

+0.05

−0.03

0.13

6 5 4

1 2 3

0 to 0.02

5°

5°

(0.15)

MTM86628

4 SJF00111AED

Page 5

Request for your special attention and precautions in using the technical information and

semiconductors described in this book

(1)If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and

regulations of the exporting country, especially, those with regard to security export control, must be observed.

(2)The technical information described in this book is intended only to show the main characteristics and application circuit examples

of the products. No license is granted in and to any intellectual property right or other right owned by Panasonic Corporation or any

other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any

other company which may arise as a result of the use of technical information described in this book.

(3)The products described in this book are intended to be used for standard applications or general electronic equipment (such as office

equipment, communications equipment, measuring instruments and household appliances).

Consult our sales staff in advance for information on the following applications:

– Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support

systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

– Any applications other than the standard applications intended.

(4)The products and product specifications described in this book are subject to change without notice for modification and/or im-

provement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product

Standards in advance to make sure that the latest specifications satisfy your requirements.

(5)When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions

(operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute

maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any

defect which may arise later in your equipment.

Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure

mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire

or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

(6)Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS,

thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. When using products for which

damp-proof packing is required, satisfy the conditions, such as shelf life and the elapsed time since first opening the packages.

(7)This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of our company.

20080805

Loading...

Loading...