Panasonic MN61113S, MN61113 Datasheet

EEPROMs

MN61113, MN61113S

2K-Bit EEPROMs

Overview

The MN61113 and MN61113S are 2048-bit, bit sequential EEPROMs with built-in address counters. They sequentially increment the address with the clock input to

produce serial output.

They include built-in charge pump circuit and timer for

automatically erasing, writing, and modifying data using

only a single 3 volt power supply.

To reduce write times, they include a block write function for writing up to 32 bits at a time. This function makes

it possible to rewrite the contents of all 2048 bits within

1 second (typ.).

Features

2048 words × 1 bit organization

Built-in reset function

Tristate output

Low power consumption

• 3 volt read: 1.5 mW (max.)

• 3 volt program: 6 mW (max.)

• 3 volt standby: 60 µW (max.)

Single 3 volt power supply (charge pump circuit

built in)

Self timer for use in automatically erasing and

writing data

Built-in data polling function

Write cycles: 105 times

Data storage interval: 10 years

Pull-up resistor on CE pin.

Pull-down resistors on PGM, CLK, and RST pins

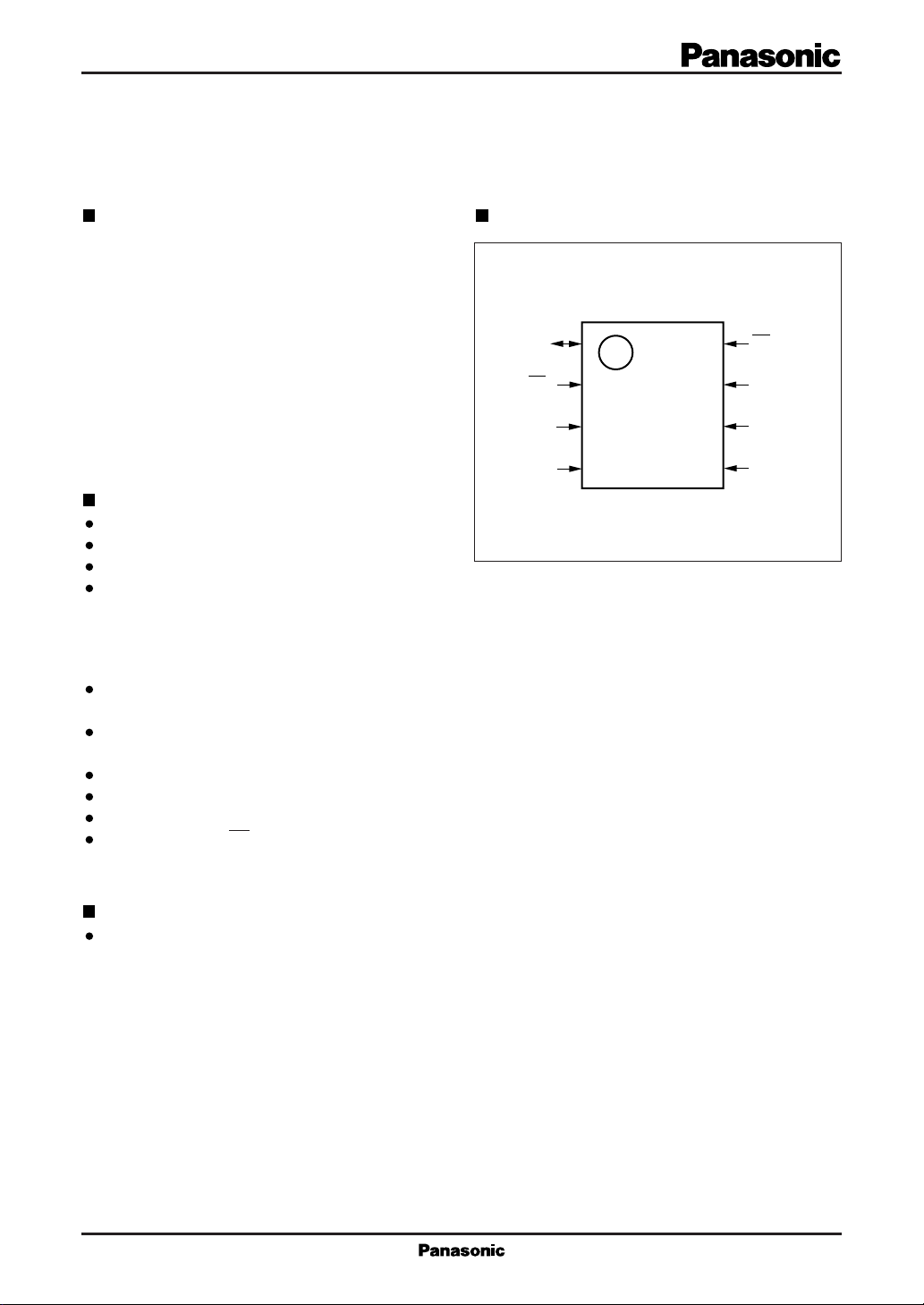

Pin Assignment

MN61113 DIP008-P-0300A

MN61113S SOP008-P-0225

CC

1

2

3

4

(TOP VIEW)

DATA

CE

V

GND

8

OE

7

RST

6

CLK

5

PGM

Applications

Personal wireless equipment, cordless telephones,

storage for recognition and adjustment data for

terminals, etc.

1

MN61113, MN61113S EEPROMs

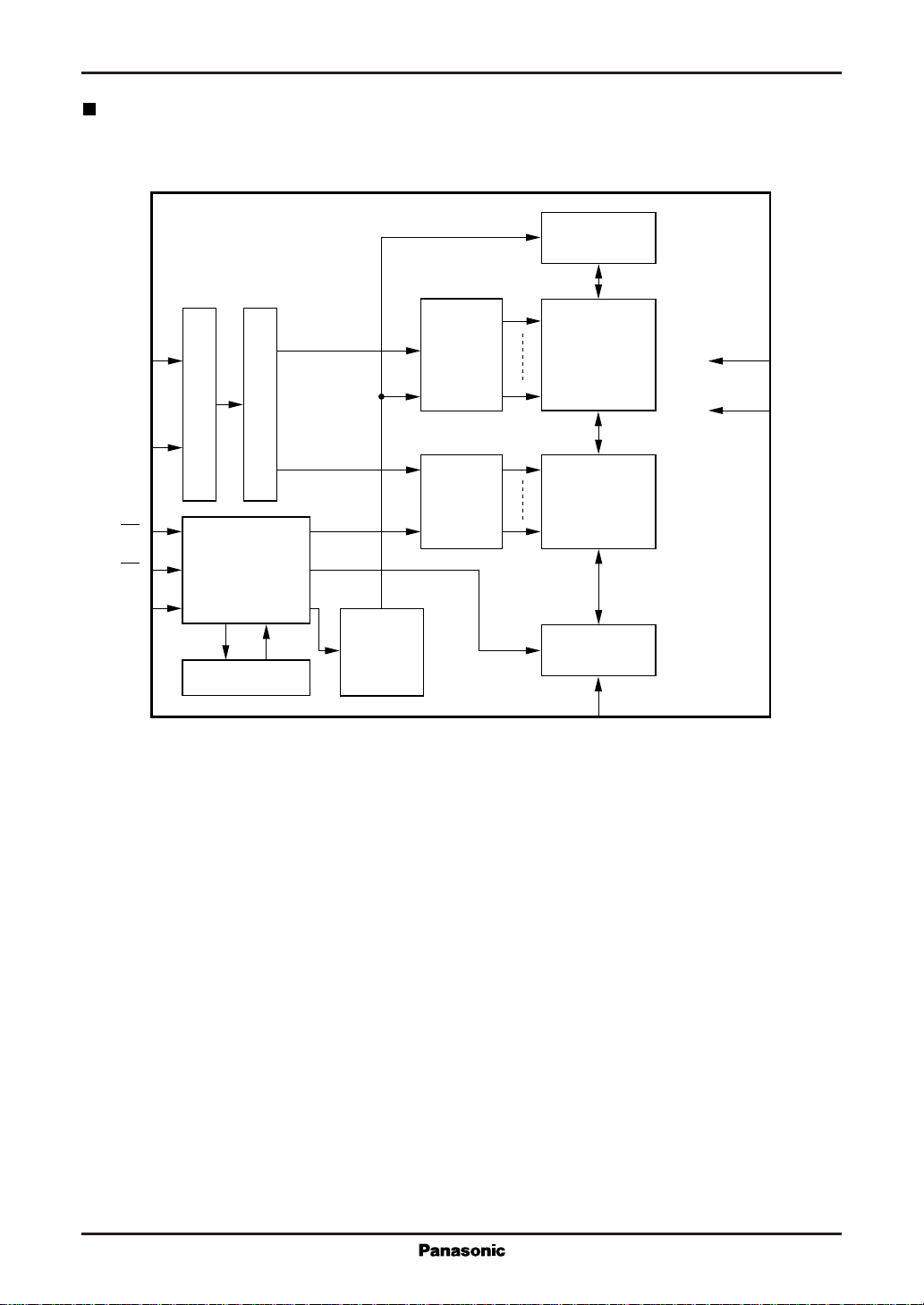

Block Diagram

Data latch pump

CLK

RST

6

7

Clock generator

8-bit counter

Row decoder

64 × 16

cell matrix

3

V

CC

4

GND

CE

OE

PGM

2

8

5

Control logic

Timer

VPP generator

Column

decoder

Column gate

Data I/O buffer

1

DATA

2

Loading...

Loading...