Panasonic MN3885S Datasheet

CCD Delay Line Series

MN3885S

NTSC-Compatible CCD Video Signal Delay Element

Overview

The MN3885S is a CCD signal delay element for video

signal processing applications.

It contains such components as a shift register clock

driver, charge I/O blocks, two CCD delay elements, a

clamp bias circuit, resampling output amplifiers, and

booster circuits.

The MN3885S samples the input using the supplied

clock signal with a frequency 7.15909 MHz of twice the

NTSC color signal subcarrier frequency, and after adding in the attached filter delay, produces independent delays of 1 H (the horizontal scan period) each for the two

lines.

Features

Single 5.0 V power supply

Single chip combining luminance signal delay line and

delay line for color signal converted to the low frequency.

Low EMI levels from clock during driving

Applications

VCRs, Video cameras

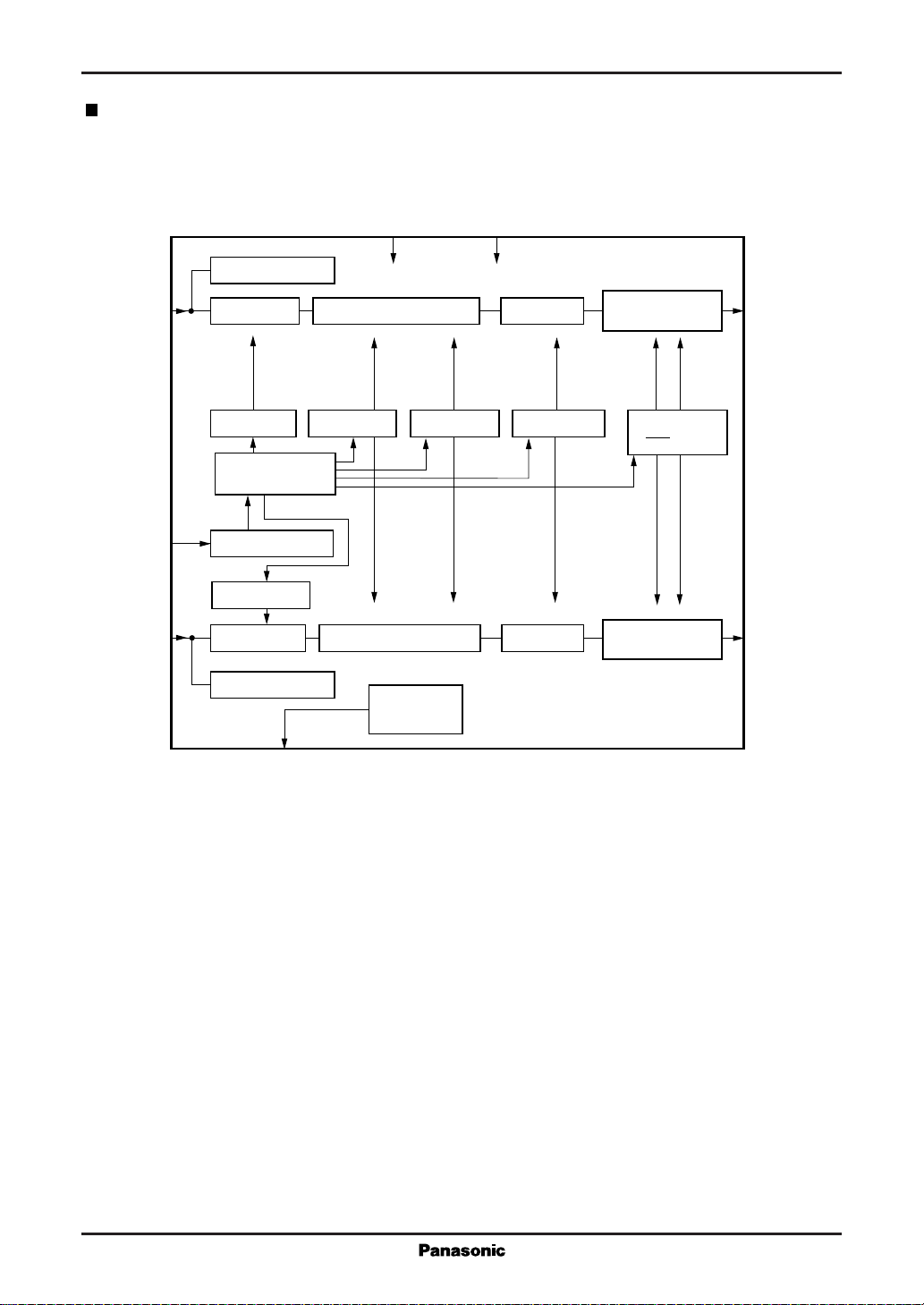

Structure and Operation

The MN3885S consists of the operational blocks shown

in the block diagram. The shift register has the structure

shown in the supplementary diagram.

Shift register clock driver

This block generates two transfer clock signals, ø1 and

ø2, synchronized with the 7.15909 MHz input clock signal.

It also generates the sampling clock signals øS and øS',

resampling clock signal øSH, and reset clock signal øR

based on the timing control.

Charge Input blocks

These blocks alter the analog input signals from the

VINC and VINY pins on their way to the shift registers.

One adds the bias voltage specified with the bias circuit

to the analog signal from the VINC pin. The other applies an "L" level clamp voltage from the clamp circuit

to the analog signal from the VINY pin.

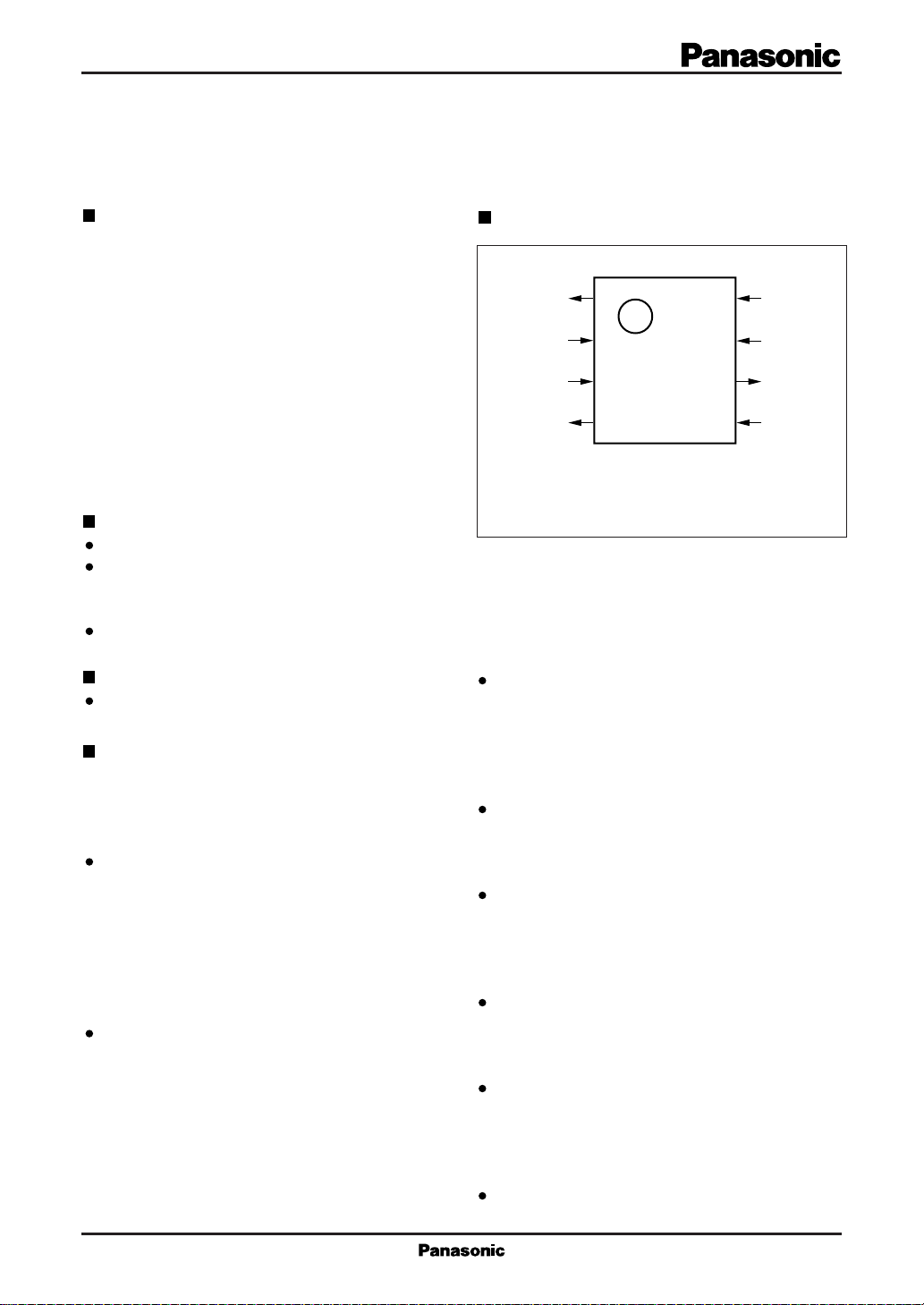

Pin Assignment

VOC

V

V

VOY

Analog shift registers

These blocks sample the shift register input signals with

the sampling clock, and convert the results to charges,

and use transfer clocks ø1 and ø2 to transfer the results to

the following block.

Charge detection blocks

These convert the signal charges from the final stage

of the analog shift registers into voltage signals.

Resampling output amplifiers

In the output stage of this blocks, the voltage signal is

executed Sample-and-Hold by resampling, and is outputted at signal output pin of VOC (1-pin) and V OY (4-pin).

Bias circuit

This circuit applies a bias voltage to the analog signal

from VINC (pin 8) to optimize it for the shift register.

Clamp circuit

This circuit applies an "L" level clamp to the analog

signal from VINY (pin 5) to optimize it for the shift register.

1

2

DD

3

SS

4

SOP008-P-0225A

( TOP VIEW )

8

VINC

7

XI

6

V

BB

5

VINY

Booster circuits

These generate reset drain voltages.

1

MN3885S CCD Delay Line Series

Block Diagram

VINC

XI

VINY

8

Charge input

block

øS driver

Timing adjustment

7

Waveform amplifier

adjustment block

øS' driver

5

Charge input

block

Clamp circuit

Bias circuit

6

3

CCD 454 stages

ø1 driver

CCD 453.5 stages

Substrate bias

generator

V

SS

ø2 driver

DD

V

2

Charge

detection block

øR driver

Charge

detection block

Resampling

output amplifier

øSH driver

øSH driver

Resampling

output amplifier

1

VOC

4

VOY

BB

V

2

Loading...

Loading...