For Communications Equipment

MN195902

Digital Signal Processor for Image CODEC

Overview

The MN195902 is a high-speed, programmable digital

signal processor based on a vector pipeline architecture

for image processing applications. It incorporates many

features that make it ideal for highly efficient coding and

decoding of still and moving pictures in applications

involving the transmission, storage, and retrieval of

images.

Features

Flexible support for complex processing by simply

rewriting the contents of its internal program memory

Built-in dedicated hardware effective for image

CODEC, including

• Discrete cosine transform (DCT) converter

• Two-dimensional address generator

Architecture that links internal memory, a generalpurpose arithmetic unit, dedicated arithmetic unit, and

other components with a pipeline to better support

vector calculations, multiply-and-accumulate, and

other key image processing operations

ITU-T H.261 coding for the QCIF size (176 × 144)

with a decoding rate of 15 frames per second or higher

Applications

Image-based communications:

Moving picture videophones, video

conferencing systems, cable television

systems, image LANs, remote monitoring

systems, etc.

Image storage and retrieval:

Electronic still cameras, optical disc files,

image databases, etc.

Multimedia computers

MN195902 For Communications Equipment

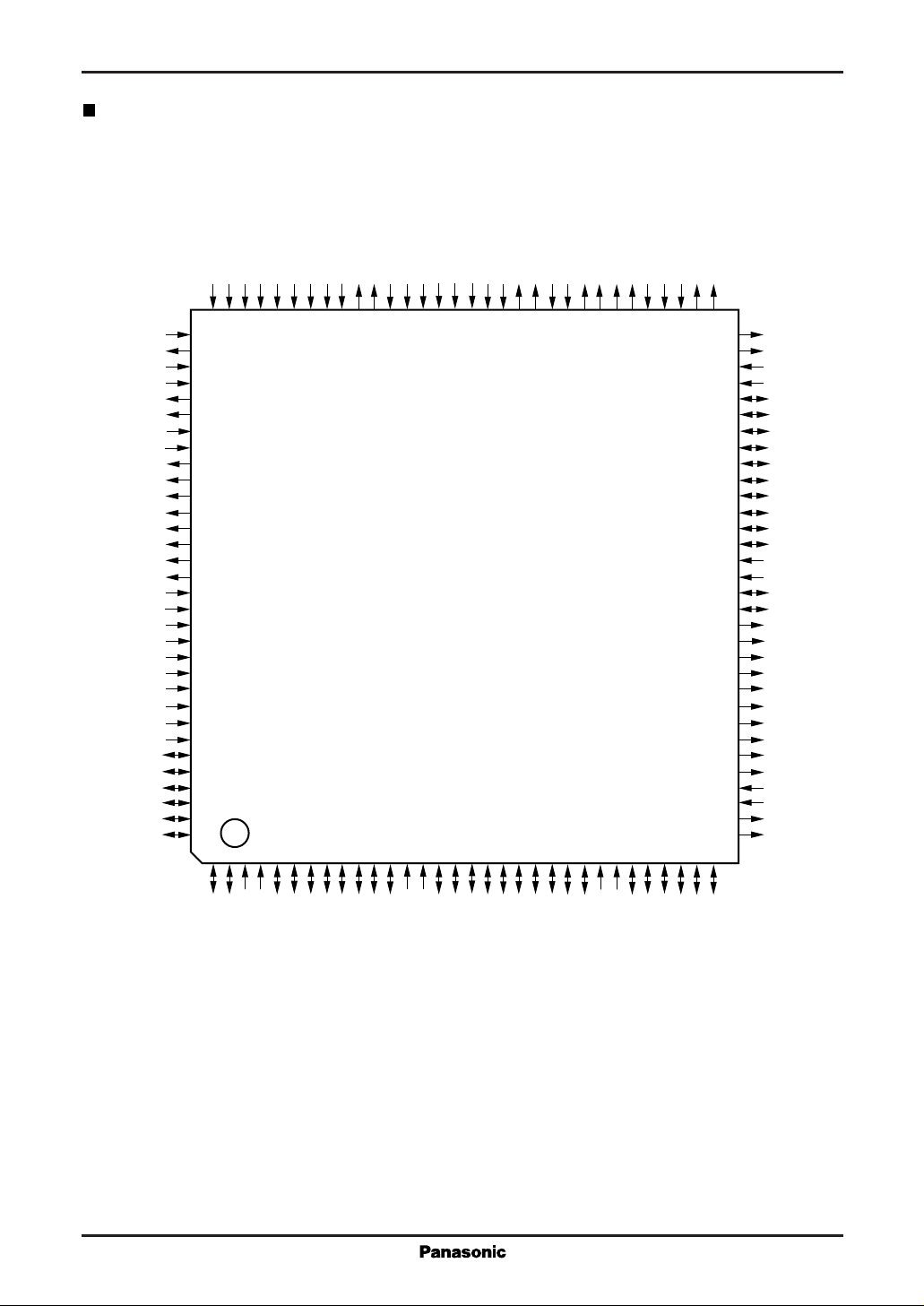

Pin Assignment

XSIEMP

SIRCLK

S1

XSOBSY

SOWCLK

S0

V

DD5

V

SS5

P0[7]

P0[6]

P0[5]

P0[4]

P0[3]

P0[2]

P0[1]

P0[0]

P0[7]

P0[6]

P0[5]

P0[4]

P0[3]

P0[2]

P0[1]

P0[0]

V

DD4

V

SS4

D2[15]

D2[14]

D2[13]

D2[12]

D2[11]

D2[10]

TEST1

DRMODE0

DRMODE1

SS6VDD6

V

XWCS

XSRE

ST1

ST2

XHLD/RUN

XRST

SPCLK

TEST0

96959493929190898887868584838281807978777675747372717069686766

97

XCS

XSWE

SS7

DD7

DRMODE2

V

SCLK

V

X801

X802

XRESEN1

XRESEN2

XOE1

XOE2

XWE1

XWE2

TEST2

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

12345678910111213141516171819202122232425262728293031

DDH

TEST3

V

XCAS1

XCAS2

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

XRAS1

XRAS2

V

SS8

V

DD8

A1[0]

A1[1]

A1[2]

A1[3]

A1[4]

A1[5]

A1[6]

A1[7]

A1[8]

A1[9]

V

SS9

V

DD9

A1[10]

A1[11]

A2[0]

A2[1]

A2[2]

A2[3]

A2[4]

A2[5]

A2[6]

A2[7]

A2[8]

A2[9]

V

SS10

V

DD10

A2[10]

A2[11]

D2[9]

D2[8]

V

DD3

SS3

V

D2[7]

D2[6]

D2[5]

D2[4]

D2[3]

D2[2]

SS2

DD2

V

V

D2[1]

D2[0]

D1[15]

LQFP128-P-1818

D1[14]

D1[13]

D1[12]

D1[11]

D1[9]

D1[10]

D1[8]

D1[7]

DD1

V

D1[6]

SS1

V

D1[5]

D1[4]

D1[3]

D1[2]

D1[1]

D1[0]

For Communications Equipment MN195902

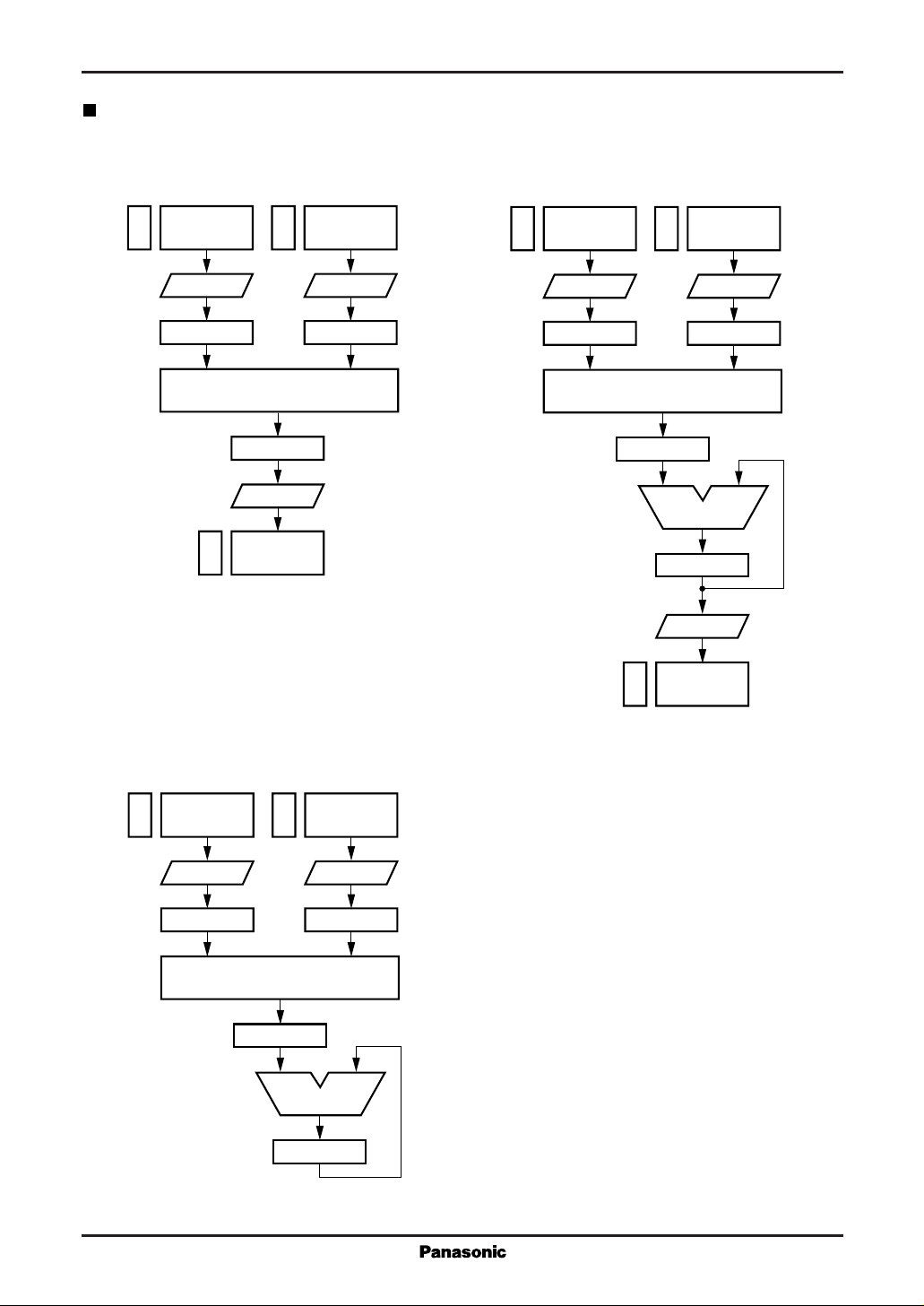

Vector Pipeline Processing Examples

SAG

P instruction

Internal

memory

SFT

REG

Pipeline arithmetic unit

REG

SFT

Internal

memory

SAG

SAG

Internal

memory

SFT

REG

SAG

QP instruction

Internal

memory

SFT

REG

Pipeline arithmetic unit

REG

SAG

SAG

ADD

REG

SFT

Internal

memory

Internal

memory

SFT

REG

SAG

Q instruction

Internal

memory

SFT

REG

Pipeline arithmetic unit

REG

SAG

Internal

memory

SFT

REG

ADD

REG

Loading...

Loading...