Page 1

SPARC/CPU−56T

Reference Guide

P/N 224548 Revision AA

November 2004

Page 2

Copyright

The information in this publication is subject to change without notice. Force Computers, GmbH reserves the right to make

changes without notice to this, or any of its products, to improve reliability, performance, or design.

Force Computers, GmbH shall not be liable for technical or editorial errors or omissions contained herein, nor for indirect,

special, incidental, or consequential damages resulting from the furnishing, performance, or use of this material. This

information is provided "as is" and Force Computers, GmbH expressly disclaims any and all warranties, express, implied,

statutory, or otherwise, including without limitation, any express, statutory, or implied warranty of merchantability, fitness for a

particular purpose, or non−infringement.

This publication contains information protected by copyright. This publication shall not be reproduced, transmitted, or stored

in a retrieval system, nor its contents used for any purpose, without the prior written consent of Force Computers, GmbH.

Force Computers, GmbH assumes no responsibility for the use of any circuitry other than circuitry that is part of a product of

Force Computers, GmbH. Force Computers, GmbH does not convey to the purchaser of the product described herein any

license under the patent rights of Force Computers, GmbH nor the rights of others.

CopyrightE 2004 by Force Computers, GmbH. All rights reserved.

The Force logo is a trademark of Force Computers, GmbH.a

IEEER is a registered trademark of the Institute for Electrical and Electronics Engineers, Inc.a

PICMGR, CompactPCIR, and the CompactPCI logo are registered trademarks and the PICMG logo is a trademark of the PCI

Industrial Computer Manufacturer’s Group.

AdvancedTCA and ATCA are trademarks of the PCI Computer Manufacturer’s Group.

MS−DOSR, Windows95R, Windows98R, Windows2000R, Windows NTR, Windows Server 2003R and Windows XPR are

registered trademarks and the logos are a trademark of the Microsoft Corporation.

IntelR and PentiumR are registered trademarks and the Intel logo is a trademark of the Intel Corporation.

SPARCR is a registerd trademark, the SPARC logo is a trademark and Ultra SPARCR is a registered trademark of SPARC

International, Inc.

PowerPCR is a registered trademark and the PowerPC logo is a trademark of International Business Machines Corporation.

AltiVecR is a registered trademark and the AltiVec logo is a trademark of Motorola, Inc.

TM

Solaris

Linux Kernel is a free system kernel developed under the GNU General Public License.

GoAheadR is a registered trademark of GoAhead Software, Inc. and SelfReliant

GoAhead Software, Inc.

LynxOSR and BlueCatR are registered trademarks of LynuxWorks, Inc.

TornadoR, VxWorksR, WindR, WindNavigatorR, Wind River SystemsR, Wind River SystemsR and design, WindViewR,

WinRouterR and XmathR are registered trademarks or service marks of Wind River Systems. Inc.

Envoy

SonyR is a registered trademark of Sony Corporation, Japan.

Ethernet

Service Availability

PowerQUICC

Other product names mentioned herein may be trademarks and/or registered trademarks of their respective companies.

a is a trademark of SUN Microsystems, Inc.

TM

, the Tornado logo, Wind RiverTM, and Zinc

TM

a is a trademark of Xerox Corporation.

TM

is a trademark of the Service Availability Forum.

TM

is a trademark of Motorola, Inc.

a

a

a

TM

a and Self AvailabilityTMa are trademarks of

TM

a are trademarks or service marks of Wind River Systems, Inc.

a

a

2 SPARC/CPU−56T

Page 3

World Wide Web: www.fci.com

24−hour access to on−line manuals, driver updates, and application

notes is provided via SMART, our SolutionsPLUS customer support

program that provides current technical and services information.

Headquarters

The Americas Europe Asia

Force Computers Inc.

4211 Starboard Drive

Fremont CA 94538

Tel.: +1 (510) 624−5300

Fax: +1 (510) 624−5301

Email: support@fci.com

224548 420 000 AA

SPARC/CPU−56T 3

Force Computers GmbH

Lilienthalstr. 15

D−85579 Neubiberg/München

Tel.: +49 (89) 608 14−0

Fax: +49 (89) 609 77 93

Email: support−de@fci.com

Force Computers Japan K.K.

Shibadaimon MF Bldg. 4F

Shiba Daimon 2−1−16

Minato−ku, Tokyo 105−0012

Tel.: +81 (03) 3437 3948

Fax: +81 (03) 3437 3968

Email: support−de@fci.com

Page 4

4 SPARC/CPU−56T

Page 5

Contents

Using this Guide

Other Sources of Information

Safety Notes

Sicherheitshinweise

1 Introduction

Features 28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Standard Compliances 30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ordering Information 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Product Nomenclature 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Order Numbers 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 Installation

Action Plan 35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Requirements 36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Environmental Requirements 36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Requirements 37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Hardware Accessories 38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

IOBPs for CPU and I/O Board 38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PMC Modules 39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Installation Procedure 41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Memory Modules 44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Hard Disk 45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SCSI−U160 Cable 45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SPARC/CPU−56T 5

Page 6

RS−422 Cable 45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PS/2 Splitter Cable 45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Switch Settings 46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Board Installation 48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Backplane Configuration 48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Installing the CPU Board 49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Removing the CPU Board 49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Powering Up 50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PLCC PROM and Flash Memory Device 50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Installing Solaris 51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Solaris Driver Package 52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

FRCgei 53. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

FRCvme 53. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

FRCflash 54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

FRCctrl 54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

FRCplatmod 55. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 Controls, Indicators, and Connectors

Front Panel 57. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

LEDs 58. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Key 59. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Connectors 59. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Serial I/O 60. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Keyboard/Mouse 60. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ethernet 61. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SCSI 61. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

On−Board Connectors 63. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PMC 63. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Memory Module 64. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

IDE 65. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

VME 66. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CPU Board 66. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I/O Board 68. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6 SPARC/CPU−56T

Page 7

4 Devices’ Features and Data Paths

Block Diagram 73. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UltraSPARC IIi+ Processor 75. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Controller 76. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PCI Bus A 77. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ethernet Controller 77. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SCSI Controller 77. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SENTINEL64 PCI−to−PCI Bridge 77. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PCI−to−VME Bridge 77. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PCI Bus B 79. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ethernet Controller 79. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Southbridge 79. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PCIO−2 Controller 79. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

EBus Interface 79. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Media Independent Interface 80. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

USB Interfaces 80. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

EBus 81. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

FPGA 81. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Watchdog 81. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer 82. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Temperature Sensor Control 82. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Local I2C Interface 82. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ethernet Interface 1/3 Switching 83. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

LED and Switch Control 83. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Reset Control 83. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PLCC PROM and Flash Memory Device 84. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Real−Time Clock and NVRAM 84. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Serial Controller 84. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PCI Bus C 86. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5 OpenBoot Firmware

Introduction 88. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CORE 88. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SPARC/CPU−56T 7

Page 8

CORE Workflow 89. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CORE Commands 90. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

POST 90. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

OpenBoot 90. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Optional Boot Parameters 91. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Boot Devices 91. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

OBDIAG 94. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Executing OBDIAG 94. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Terminating OBDIAG 95. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

OBDIAG Commands 95. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

VxWorks Support 96. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

NVRAM Boot Parameters 97. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Diagnostics 98. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SCSI Bus 98. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

All SCSI Buses 98. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Single Device 99. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Group of Devices 99. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Clock 99. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Network 100. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

IDE Devices 100. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Displaying System Information 101. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ethernet Address and Host ID 101. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

ID PROM 101. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Resetting the System 103. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Activating OpenBoot Help 104. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6 Maps and Registers

Interrupt Map 108. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Physical Memory Map 110. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UltraSPARC−IIi+ Physical Address Memory Map 110. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Memory Address Map 110. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8 SPARC/CPU−56T

Page 9

UltraSPARC−IIi+ Internal CSR Space 111. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PCI Bus Address Map 111. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PCIO−2 Address Map 112. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

System Configuration Registers 114. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Overview of System Configuration Registers 114. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Miscellaneous Control Register 115. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

User LED Control Registers 117. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

LED Control Register 1 117. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

LED Control Register 2 118. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

LED Control Register 3 118. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

LED Control Register 4 119. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

External Failure Status Register 120. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Watchdog Timer Registers 121. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Watchdog Timer Control Register 121. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Watchdog Timer Trigger Register 122. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Watchdog Timer Status Register 123. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer Registers 123. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer Control Register 123. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer Clear Control Register 124. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer Status Register 124. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer Initial Control Registers 125. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer Counter Status Register 126. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Registers 127. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Enable Control Register 127. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Pending Status Register 128. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Reset Register 129. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Board Status Registers 130. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Switch 1 and 2 Status Register 130. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Switch 3 and 4 Status Register 131. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Board Configuration Status Register 1 132. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Board Configuration Status Register 2 133. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Hardware Revision Register 133. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I2C Registers 134. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

AppendixA Troubleshooting

AppendixB Battery Exchange

Index

SPARC/CPU−56T 9

Page 10

Product Error Report

10 SPARC/CPU−56T

Page 11

Tables

Introduction

Tablei1aaaaaaaStandard Compliances 30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei2aaaaaaaProduct Nomenclature 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei3aaaaaaaBoard Ordering Information 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei4aaaaaaaBoard Accessories Ordering Information 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Installation

Tablei5aaaaaaaEnvironmental Requirements 36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei6aaaaaaaPower Requirements 37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei7aaaaaaaSwitch Settings 46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei8aaaaaaaSolaris Patches 52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei9aaaaaaaDevices and Their Appropriate Drivers 52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei10aaaaaaFlash Segmentation and Write Protection 54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Controls, Indicators, and Connectors

Tablei11aaaaaaDescription of Front Panel LEDs 58. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Devices’ Features and Data Paths

Tablei12aaaaaaReset Sources 83. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

OpenBoot Firmware

Tablei13aaaaaaBoot Parameters 91. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei14aaaaaaOpenBoot Aliases for SCSI Devices 91. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei15aaaaaaOpenBoot Aliases for Miscellaneous Devices 93. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei16aaaaaaOBDIAG Commands 95. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei17aaaaaaOpenBoot Configuration Parameters 97. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei18aaaaaaDiagnostic Routines 98. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei19aaaaaaCommands to Display System Information 102. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Maps and Registers

Tablei20aaaaaaUltraSPARC−IIi+ Main Address Map 110. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei21aaaaaaMain Memory Address Map 110. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei22aaaaaaUltraSPARC−IIi+ Internal CSR Space 111. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei23aaaaaaPCI Bus Address Map 112. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei24aaaaaaPCIO−2 Address Map 112. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei25aaaaaaCPU Board System Configuration Register Address Map 114. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei26aaaaaaMiscellaneous Control Register 116. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei27aaaaaaLED Control Register 1 117. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei28aaaaaaLED Control Register 2 118. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SPARC/CPU−56T 11

Page 12

Tablei29aaaaaaLED Control Register 3 119. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei30aaaaaaLED Control Register 4 120. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei31aaaaaaExternal Failure Register 120. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei32aaaaaaWatchdog Timer Control Register 122. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei33aaaaaaWatchdog Timer Trigger Register 122. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei34aaaaaaWatchdog Timer Status Register 123. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei35aaaaaaTimer Control Register 124. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei36aaaaaaTimer Clear Control Register 124. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei37aaaaaaTimer Status Register 125. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei38aaaaaaTimer Initial Control Registers 126. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei39aaaaaaTimer Counter Status Register 127. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei40aaaaaaInterrupt Enable Control Register 128. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei41aaaaaaInterrupt Pending Status Register 128. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei42aaaaaaReset Status Register 129. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei43aaaaaaSwitch 1 and 2 StatusRegister 130. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei44aaaaaaSwitch 3 and 4 Status Register 131. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei45aaaaaaBoard Configuration Status Register 1 132. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei46aaaaaaBoard Configuration Status Register 2 133. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei47aaaaaaHardware Revision Register 134. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei48aaaaaaI2C 1 Register 134. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tablei49aaaaaaI2C 2 Register 135. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12 SPARC/CPU−56T

Page 13

Figures

Introduction

Figurei1aaaaaaaFunction Blocks 29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Installation

Figurei2aaaaaaaLocation of PMC Voltage Keys 40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei3aaaaaaaLocation of Switches on Board’s Top Side 46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Controls, Indicators, and Connectors

Figurei4aaaaaaaCPU Board’s Front Panel 57. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei5aaaaaaaSerial A Connector Pinout 60. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei6aaaaaaaSerial B Connector Pinout 60. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei7aaaaaaaSUN−Type Keyboard/Mouse Connector Pinout 60. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei8aaaaaaaPS/2 Keyboard Connector Pinout 60. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei9aaaaaaaPS/2 Mouse Connector Pinout 61. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei10aaaaaaEthernet 1 Connector Pinout 61. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei11aaaaaaEthernet 2 Connector Pinout 61. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei12aaaaaaSCSI 1/2 Connector Pinouts 62. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei13aaaaaaLocation of PMC Connectors 63. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei14aaaaaaPMC I/O Connector Pn24 Pinout 64. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei15aaaaaaLocation of Memory Module Connectors 65. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei16aaaaaaIDE Connector Pinout 66. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei17aaaaaaLocation of VME Connectors 66. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei18aaaaaaCPU Board P2 VMEbus Connector Pinout Rows Z − B67. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei19aaaaaaCPU Board P2 VMEbus Connector Pinout Rows C + D 68. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei20aaaaaaI/O Board P2 VMEbus Connector Pinout Rows Z – B 69. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei21aaaaaaI/O Board P2 VMEbus Connector Pinout Rows C + D 70. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Devices’ Features and Data Paths

Figurei22aaaaaaCPU Board Block Diagram 73. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei23aaaaaaI/O Board Block Diagram 74. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

OpenBoot Firmware

Figurei24aaaaaaOpenBoot CORE Overview 88. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei25aaaaaa48−bit (6−byte) Ethernet Address 101. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figurei26aaaaaa32−bit (4−byte) Host ID 101. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SPARC/CPU−56T 13

Page 14

Using this Guide

No danger encountered. Pay attention to important

This Reference Guide is intended for users qualified in electronics or electrical

engineering. Users must have a working understanding of Peripheral Component

Interconnect (PCI), VMEbus, and telecommunications.

Conventions

Notation Description

57 All numbers are decimal numbers except when used with the

notations described below.

00000000

or 0x00000000

0000

or 0b0000

x Generic use of a letter

n Generic use of numbers

0.75 Decimal number

Bold Used to emphasize a word

Courier Used for on−screen output

Courier+Bold Used to characterize user input

Italics For references, table, and figure descriptions

File > Exit Notation for selecting a submenu

<text> Notation for variables and keys

[text] Notation for buttons and optional parameters

... Repeated item (example: A1, A2, A3, ..., A12)

.

.

.

16

2

Typical notation for hexadecimal numbers (digits 0 through F),

e.g. used for addresses and offsets

Same for binary numbers (digits are 0 and 1)

Omission of information from example/command that is not

necessary at the time being

.. Ranges, e.g.: 0..4 means one of the integers 0, 1, 2, 3, and 4

| Logical OR

14 SPARC/CPU−56T

(used in register description tables)

No danger encountered. Pay attention to important

information

Page 15

Notation Description

Possibly dangerous situation: slight injuries to people or

Dangerous situation: injuries to people or severe damage to

p

p

Possibly dangerous situation: slight injuries to people or

damage to objects possible

Dangerous situation: injuries to people or severe damage to

objects possible

Start of a procedure

End of a procedure

Abbreviations

Abbreviation Description

B

BGA

BIB Board Information Block

BMC Base Board Management Controller

C

CAS

CSR Control Status Register

D

DMA

DRAM Dynamic Random Access Memory

E

ECC

EEPROM Electrically Erasable Programmable Read−Only Memory

EPROM Erasable Programmable Read Only Memory

ESD

B

Ball Grid Array

C

Column Address Select

D

Direct Memory Access

E

Error−Correction Code

Electrostatic Sensitive Device

SPARC/CPU−56T 15

Page 16

Abbreviation Description

F

F

FAE

FIFO First In First Out

FPGA Field−Programmable Gate Array

I

IBMU

ICMB Intelligent Chassis Management Bus

ICT In−Circuit Test

IDE Integrated Drive Electronics

IEC International Electric Code

IOBP Input Output Back Panel

IOM I/O Memory Management Unit

IPMB Intelligent Platform Management Bus

IPMI Intelligent Platform Management Interface

ISO International Organization for Standardization

J

JTAG

L

LCA

LDO Local Data Output

LED Light Emitting Diode

LVD Low Voltage Differential

LVTTL Low Voltage Transistor Transistor Logic

M

Field Application Engineers

I

Intelligent Board Management Unit

J

Joint Test Access Group

L

Load Controller Assembly

M

MAC

MCU Memory Control Unit

MII Media Independent Interface

N

NEBS

NMI Nonmaskable Interrupt

NVRAM Nonvolatile Random Access Memory

O

OBDIAG

P

PBM

PCB Printed Circuit Board

PCI

16 SPARC/CPU−56T

Media Access Control Layer

N

Network Equipment Building Standards

O

OpenBoot Diagnostics

P

PCI Bus Module

Peripheral Component Interconnect

Page 17

Abbreviation Description

PCIO Peripheral Component Interconnect Input/Output

PHY Physical Layer

PIE PCI Interrupt Engine

PLCC Plastic Leadless Chip Carrier

PLL Phase−Locked Loop

PMC PCI Mezzanine Card

POST Power−On Self−Test

PROM Programmable Read Only Memory

R

R

RIC

ROM Read Only Memory

RTB Rear Transition Board

RTC Real−Time Clock

RTOS Real Time Operating System

S

SDRAM

SELV Safety Extra Low Voltages

SPD Serial Presence Detect

SRAM Static Random Access Memory

STP Shielded Twisted Pair

T

TPE

U

UART

UIC UPA Interrupt Connector

USB Universal Serial Bus

UTP Unshielded Twisted Pair

V

VME

Reset/Interrupt/Clock Controller

S

Synchronous DRAM

T

Twisted Pair Ethernet

U

Universal Asynchronous Receiver−Transmitter

V

Versa Module Eurocard

Revision History

Order No. Rev. Date Description

220306 AA May 2003 Preliminary

Manual

220306 AB September 2003 Final release

version

SPARC/CPU−56T 17

Page 18

Order No. DescriptionDateRev.

223146 AA April 2004 Corrected number

of SUN patch for

audio support.

Now it reads

109896−17; added

note to abort/reset

key description;

corrected feature

list of FRctrl

Solaris driver

224548 AA November 2004 Corrected typical

and maximum

power

consumption

values for 5V.a

18 SPARC/CPU−56T

Page 19

Other Sources of Information

For further information refer to:

Company www. Document

ALI Corporation ali.com.tw ALI M1535D+ Southbridge documentation

Force Computers forcecomputers.com SPARC/IOBP−CPU−56 Installation Guide

aa SPARC/IOBP−IO−56 Installation Guide

SPARC/MEM−550 Installation Guidea

ACC/CABLE/SCSI−U160 Installation Guide

ACC/CABLE/RS422 Installation Guide

IEEE Standards

Department

Intel intel.com Intel 82540 Ethernet controller specifications

aa aa Intel LXT971 PHY device specifications

LSI Logic lsilogic.com 53C1010 SCSI controller specifications

Maxim maxim−ic.com MAX1617 temperature sensor specifications

STMicroelectronicsst.com M48T35AV RTC/NVRAM specifications

National

Semiconductor

PCI Special

Interest Group

PICMGPCI

Special Interest

Group

SUN sun.com UltraSPARCIIi+ Processor specifications

aa aa SUN SME2300 PCIO−2 controller

Tundra tundra.com Universe II documentation

ieee.com IEEE P1386 Standard Mechanics for a Common

Mezzanine Card Family: CMC

national.com PC87307/PC97307 Plug and Play Compatible

Super I/O, Preliminary Specification, March

1998

pcisig.com PCI Local Bus Specification Rev2.1

picmg.org

pcisig.com

PCI Local Bus Specification Rev2.2

documentation

VITA vita.com VME64 Standard ANSI/VITA 1−1994

aa aa VME64 Extensions Draft Standard, Draft 1.8, Jun

13, 1997

Xilinx

SPARC/CPU−56T 19

xilinx.com Spartan XC520XL FPGA specifications

Page 20

Safety Notes

The text in this chapter is a translation of the Sicherheitshinweise" chapter

This section provides safety precautions to follow when installing, operating, and

maintaining the board.

We intend to provide all necessary information to install and handle the board in this

Installation Guide. However, as the product is complex and its usage manifold, we do not

guarantee that the given information is complete. If you need additional information, ask

your Force Computers representative.

The board has been designed to meet the standard industrial safety requirements. It

must not be used except in its specific area of office telecommunication industry and

industrial control.

Only personnel trained by Force Computers or persons qualified in electronics or

electrical engineering are authorized to install, remove or maintain the board. The

information given in this manual is meant to complete the knowledge of a specialist

and must not be taken as replacement for qualified personnel.

EMC

The board has been tested in a Standard Force Computers system and found to comply

with the limits for a Class A digital device in this system, pursuant to part 15 of the

FCC Rules respectively EN 55022 Class A. These limits are designed to provide

reasonable protection against harmful interference when the system is operated in a

commercial environment.

The board generates and uses radio frequency energy and, if not installed properly and

used in accordance with this Installation Guide, may cause harmful interference to

radio communications. Operating the system in a residential area is likely to cause

harmful interference, in which case the user will be required to correct the interference

at his own expense.

To ensure proper EMC shielding, always operate the board with the blind panel or

with PMC module installed. If boards are integrated into open systems, always cover

empty slots.

Switch Settings

Switches marked as ’reserved’ might carry production−related functions and can cause

the board to malfunction if their setting is changed. Therefore, only change settings of

switches not marked as ’reserved’.

20 SPARC/CPU−56T

Page 21

Setting/resetting the switches during operation causes board damage. Therefore, check

and change switch settings before you install the board.

Installation

Electrostatic discharge and incorrect board installation and removal can damage

circuits or shorten their life. Therefore:

S Touching the board or electronic components in a non−ESD protected environment

causes component and board damage. Before touching boards or electronic

components, make sure that you are working in an ESD−safe environment.

S When plugging the board in or removing it, do not press or pull on the front panel

but use the handles.

S Before installing or removing an additional device or module, read the respective

documentation.

S Make sure that the board is connected to the VME backplane via all assembled

connectors and that power is available on all power pins.

Power Up

If an unformatted floppy disk resides in a floppy drive connected to the VME board

during power up, the VME board does not boot and the OpenBoot prompt does not

appear. Therefore, never boot the VME board with an unformatted floppy disk

residing in a floppy drive connected to the VME board.

a

Operation

While operating the board ensure that the environmental and power requirements are

met:

S To ensure that the operating conditions are met, forced air cooling is required

within the chassis environment.

S High humdity and condensation on the surface cause short circuits. Only operate

the board above 0°C. Make sure the board is completely dry and there is no

moisture on any surface before applying power.

Replacement/Expansion

Only replace or expand components or system parts with those recommended by Force

Computers. Otherwise, you are fully responsible for the impact on EMC or any

possible malfunction of the product.

SPARC/CPU−56T 21

Page 22

Check the total power consumption of all components installed (see the technical

specification of the respective components). Ensure that any individual output current

of any source stays within its acceptable limits (see the technical specification of the

respective source).

RJ−45 Connector

The RJ−45 connector on the front panel must only be used for twisted−pair Ethernet

(TPE) connections. Connecting a telephone to such a connector may destroy your

telephone as well as your board. Therefore:

S Clearly mark TPE connectors near your working area as network connectors

S Only connect TPE bushing of the system to safety extra low voltage (SELV) circuits.

S Make sure that the length of the electric cable connected to a TPE bushing does not

exceed 100 meter.

If you have further questions, ask your system administrator.

Battery

If a lithium battery on the board has to be exchanged (see Appendix Battery Exchange),

observe the following safety notes:

S Wrong battery exchange may result in a hazardous explosion and board damage.

Therefore, always use the same type of lithium battery as is installed and make sure

the battery is installed as described.

S Exchanging the battery after seven years of actual battery use have elapsed results

in data loss. Therefore, exchange the battery before seven years of actual battery use

have elapsed.

S Exchanging the battery always results in data loss of the devices which use the

battery as power backup. Therefore, back up affected data before exchanging the

battery.

Environment

Always dispose of used batteries and/or old boards according to your country’s

legislation, if possible in an environmentally acceptable way.

22 SPARC/CPU−56T

Page 23

Sicherheitshinweise

Dieser Abschnitt enthält Sicherheitshinweise, die bei Einbau, Betrieb und Wartung des

Boards zu beachten sind.

Wir sind darauf bedacht, alle notwendigen Informationen, die für die Installation und den

Betrieb erforderlich sind, in diesem Handbuch bereit zu stellen. Da es sich jedoch bei dem

Board um ein komplexes Produkt mit vielfältigen Einsatzmöglichkeiten handelt, können

wir die Vollständigkeit der im Handbuch enthaltenen Informationen nicht garantieren.

Falls Sie weitere Informationen benötigen sollten, wenden Sie sich bitte an die für Sie

zuständige Geschäftsstelle von Force Computers.

Das Board erfüllt die für die Industrie geforderten Sicherheitsvorschriften und darf

ausschliesslich für Anwendungen in der Telekommunikationsindustrie und im

Zusammenhang mit Industriesteuerungen verwendet werden.

Einbau, Wartung und Betrieb dürfen nur von durch Force Computers ausgebildetem

oder im Bereich Elektronik oder Elektrotechnik qualifiziertem Personal durchgeführt

werden. Die in diesem Handbuch enthaltenen Informationen dienen ausschliesslich

dazu, das Wissen von Fachpersonal zu ergänzen, können es aber in keinem Fall

ersetzen.

EMV

Das Board wurde in einem Force Computers Standardsystem getestet. Es erfüllt die für

digitale Geräte der Klasse A gültigen Grenzwerte in einem solchen System gemäß den

FCC−Richtlinien Abschnitt 15 bzw. EN 55022 Klasse A. Diese Grenzwerte sollen einen

angemessenen Schutz vor Störstrahlung beim Betrieb des Boards in Gewerbe− sowie

Industriegebieten gewährleisten.

Das Board arbeitet im Hochfrequenzbereich und erzeugt Störstrahlung. Bei

unsachgemäßem Einbau und anderem als in diesem Handbuch beschriebenen Betrieb

können Störungen im Hochfrequenzbereich auftreten.

Warnung! Dies ist eine Einrichtung der Klasse A. Diese Einrichtung kann im

Wohnbereich Funkstörungen verursachen. In diesem Fall kann vom Betreiber verlangt

werden, angemessene Maßnahmen durchzuführen.

Wenn Sie das Board ohne PMC Modul verwenden, schirmen Sie freie Steckplätze mit

einer Blende ab, um einen ausreichenden EMV Schutz zu gewährleisten. Wenn Sie

Boards in Systeme einbauen, schirmen Sie freie Steckplätze mit einer Blende ab.

Schaltereinstellungen

Das Ändern der mit ’reserved’ gekennzeichneten Schalter kann zu Störungen im

Betrieb des Boards führen. Ändern Sie die Schaltereinstellungen der mit ’reserved’

SPARC/CPU−56T 23

Page 24

gekennzeichneten Schalter nicht, da diese Schalter mit produktionsrelevanten

Funktionen belegt sein können, die im normalen Betrieb Störungen auslösen könnten.

Das Ändern der Schaltereinstellungen während des laufendes Betriebs kann das Board

beschädigen. Prüfen und ändern Sie die Schaltereinstellungen, bevor Sie das Board

installieren.

Installation

Elektrostatische Entladung und unsachgemäßer Ein− und Ausbau des Boards kann

Schaltkreise beschädigen oder ihre Lebensdauer verkürzen. Beachten Sie deshalb die

folgenden Punkte:

S Berühren Sie das Board oder elektrische Komponenten in einem nicht

ESD−geschützten Bereich, kann dies zu einer Beschädigung des Boards führen.

Bevor Sie Boards oder elektronische Komponenten berühren, vergewissern Sie

sich, dass Sie in einem ESD−geschützten Bereich arbeiten.

S Drücken Sie beim Ein− oder Ausbau des Boards nicht auf die Frontplatte, sondern

benutzen Sie die Griffe.

S Lesen Sie vor dem Ein− oder Ausbau von zusätzlichen Geräten oder Modulen das

dazugehörige Benutzerhandbuch.

Booten

Betrieb

S Vergewissern Sie sich, dass das Board über alle Stecker an die VME Backplane

angeschlossen ist und alle Spannungskontakte mit Strom versorgt werden.

Befindet sich während des Bootens eine unformatierte Diskette in einem mit dem

VME Board verbundenen Diskettenlaufwerk, bootet das VME Board nicht, und die

OpenBoot−Eingabeaufforderung erscheint nicht. Booten Sie deshalb niemals das VME

Board, wenn sich eine unformatierte Diskette in einem mit dem VME Board

verbundenen Diskettenlaufwerk befindet.

Achten Sie darauf, dass die Umgebungs− und die Leistungsanforderungen während

des Betriebs eingehalten werden:

S Um zu gewährleisten, dass die Anforderungen während des Betriebs eingehalten

werden, ist eine Luftkühlung notwendig

S Betreiben Sie das Board nur innerhalb der angegebenen Grenzwerte für die relative

Luftfeuchtigkeit und Temperatur, da durch hohe Luftfeuchtigkeit Kurzschlüsse

24 SPARC/CPU−56T

Page 25

entstehen können. Stellen Sie vor dem Einschalten des Stroms sicher, dass sich auf

dem Board kein Kondensat befindet und betreiben Sie das Board nicht unter 0°C.

Wenn Sie das Board in Gebieten mit starker elektromagnetischer Strahlung betreiben,

stellen Sie sicher, dass das Board mit dem System verschraubt ist und das System

durch ein Gehäuse abgeschirmt wird.

Stellen Sie sicher, dass Anschlüsse und Kabel des Boards während des Betriebs nicht

versehentlich berührt werden können.

Austausch/Erweiterung

Verwenden Sie bei Austausch oder Erweiterung nur von Force Computers empfohlene

Komponenten und Systemteile. Andernfalls sind Sie für mögliche Auswirkungen auf

EMV oder Fehlfunktionen des Produktes voll verantwortlich.

Überprüfen Sie die gesamte aufgenomme Leistung aller eingebauten Komponenten

(siehe die technischen Daten der entsprechenden Komponente). Stellen Sie sicher, dass

die Stromaufnahme jedes Verbrauchers innerhalb der zulässigen Grenzwerte liegt

(siehe die technischen Daten des entsprechenden Verbrauchers).

RJ−45 Stecker

Batterie

Der RJ−45 Stecker auf der Frontblende darf nur für Twisted−Pair−Ethernet (TPE)

Verbindungen verwendet werden. Beachten Sie, dass ein versehentliches Anschließen

einer Telefonleitung an einen solchen TPE Stecker sowohl das Telefon als auch das

Board zerstören kann. Beachten Sie deshalb die folgenden Hinweise:

S Kennzeichnen Sie TPE−Anschlüsse in der Nähe Ihres Arbeitsplatzes deutlich als

Netzwerkanschlüsse.

S Schließen Sie an TPE−Buchsen ausschließlich SELV−Kreise

(Sicherheitskleinspannungsstromkreise) an.

S Die Länge des mit dem Board verbundenen Twisted−Pair Ethernet−Kabels darf 100

m nicht überschreiten.

Falls Sie Fragen haben, wenden Sie sich bitte an Ihren Systemadministrator.

Muss eine Lithium−Batterie auf dem Board ausgetauscht werden (siehe Appendix

Battery Exchange), beachten Sie die folgenden Sicherheitshinweise:

S Fehlerhafter Austausch von Lithium−Batterien kann zu lebensgefährlichen

Explosionen führen. Verwenden Sie deshalb nur den Batterietyp, der auch bereits

eingesetzt wurde und befolgen Sie die Installationsanleitung.

SPARC/CPU−56T 25

Page 26

S Verwenden Sie die Batterien länger als sieben Jahre, kann dies zu Datenverlusten

führen. Tauschen Sie deshalb die Batterie aus, bevor sieben Jahre reiner Betrieb

vorüber sind.

S Der Austausch der Batterie bringt immer einen Datenverlust bei den Komponenten

mit sich, die sich durch die Batterie die Stromversorgung sichern. Sichern Sie

deshalb vor dem Batterieaustausch Ihre Daten.

Umweltschutz

Entsorgen Sie alte Batterien und/oder Boards stets gemäß der in Ihrem Land gültigen

Gesetzgebung, wenn möglich immer umweltfreundlich.

26 SPARC/CPU−56T

Page 27

1

Introduction

Features 28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Standard Compliances 30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ordering Information 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Product Nomenclature 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Order Numbers 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SPARC/CPU−56T 27

Page 28

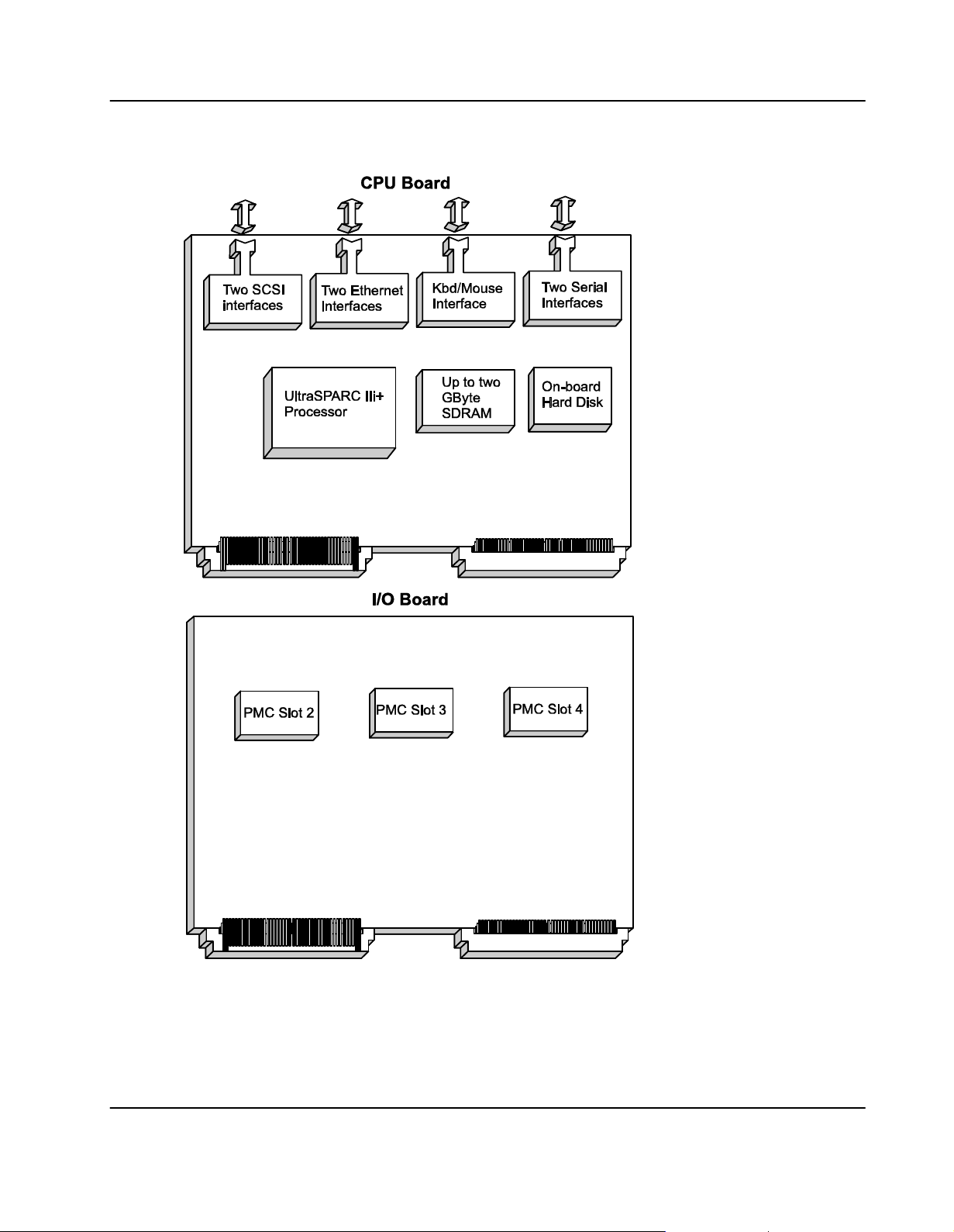

Introduction Features

Features

The SPARC/CPU56 is a high−performance VME single−board computer based on the 650

Mhz UltraSPARC IIi+ processor. It provides 512 MByte on−board SDRAM memory.

Important features are:

S Two Wide Ultra3 SCSI interfaces via front panel and one via I/O board′s IOBP

S Two 10/100/1000 BaseT Ethernet interfaces via front panel

S One 10/100 BaseT interface via front panel or CPU board′s IOBP

S Two serial RS−232 interfaces via front panel

S Two RS−232/RS−454 interfaces via CPU board′s IOBP

S Three USB interfaces via CPU board′s IOBP

S Optional on−board hard disk

S Keyboard/Mouse interface via front panel or CPU board′s IOBP

S Floppy disk and parallel interface via CPU board′s IOBP

S Three PMC slots on I/O board

S Solaris 8/9 and VxWorks support

a

28 SPARC/CPU−56T

Page 29

Features Introduction

Figure 1: Function Blocks

SPARC/CPU−56T 29

Page 30

Introduction Standard Compliances

Standard Compliances

The CPU board was designed to comply with the standards listed below.

Table 1: Standard Compliances

Standarda

IEC 68−2−1/2/3/13/14 Climatic environmental requirements.

IEC 68−2−6/27/32 Mechanical environmental requirements

EN 609 50/UL 1950 (predefined Force system);

UL 94V−0/1

EN 55022,a

EN 55024,

FCC Part 15 Class A

ANSI/IPC_A−610 Rev. B Class 2

ANSI/IPC−R−700B

ANSI−J−001...003

ISO 8601

Description

Legal safety requirements

EMC requirements on system level

Manufacturing requirements

Y2K compliance

30 SPARC/CPU−56T

Page 31

Ordering Information Introduction

Ordering Information

When ordering board variants, hard− and software upgrades use the order numbers

given below.

Product Nomenclature

In the following table you find the key for the product name extensions used for board

variants.

Table 2: Product Nomenclature

SPARC/CPU−56T/xxx−ccc−Lyyy−zz

xxx SDRAM capacity in MByte

ccc CPU speed in MHz

Lyyy L2−cache in KByte

a

zz

Order Numbers

The table below is an excerpt from the board’s ordering information. Ask your local Force

Computers representative for the current ordering information.

Table 3: Board Ordering Information

Order No.

111328 512−650−L512−16 512 MByte SDRAM, 650 MHz CPU

The table below is an excerpt from the board’s accessories ordering information. Ask your

local Force Computers representative for the current ordering information.

Table 4: Board Accessories Ordering Information

Order No. Accessory Description

111330 SPARC/IOBP−CPU−56/3 Three−row variant of CPU board′s

111331 SPARC/IOBP−CPU−56/5 Five−row variant of CPU board′s

Flash memory size in MByte

SPARC/CPU−56T/... Description

frequency, 512 KByte L2 cache and 16

MByte flash memory

IOBP

IOBP

120455

SPARC/CPU−56T 31

SPARC/IOBP−IO−56/5 Five−row variant of I/O board′s

IOBP

Page 32

Introduction Ordering Information

Order No. DescriptionAccessory

120456 SPARC/IOBP−IO−56/3 Three−row variant of I/O board′s

IOBP

111332 ACC/CABLE/SCSI−U160 SCSI−3−to−SCSI−4 adapter cablea

120454 ACC/CABLE/RS422 RS232−to−RS422 serial adapter cablea

109045a SPARC/MEM−550/1024 Memory module with 1 GByte

memory

107257

ACC/CABLE/KBDMSE/540 Splitter cable for PS2/SUN

keyboard/mouse

32 SPARC/CPU−56T

Page 33

2

Installation

Action Plan 35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Requirements 36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Environmental Requirements 36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Requirements 37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Hardware Accessories 38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

IOBPs for CPU and I/O Board 38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PMC Modules 39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Installation Procedure 41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Memory Modules 44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Hard Disk 45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SCSI−U160 Cable 45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RS−422 Cable 45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PS/2 Splitter Cable 45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Switch Settings 46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Board Installation 48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Backplane Configuration 48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Installing the CPU Board 49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Removing the CPU Board 49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Powering Up 50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PLCC PROM and Flash Memory Device 50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Installing Solaris 51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Solaris Driver Package 52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

FRCgei 53. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

FRCvme 53. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SPARC/CPU−56T 33

Page 34

FRCflash 54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

FRCctrl 54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

FRCplatmod 55. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

34 SPARC/CPU−56T

Page 35

Action Plan Installation

Action Plan

In order to install the board, the following steps are necessary and will be described in

further detail in the sections of this chapter.

SPARC/CPU−56T 35

Page 36

Installation Requirements

Requirements

In order to meet the environmental requirements, the CPU board has to be tested in the

system in which it is to be installed.

Before you power up the board, calculate the power needed according to your

combination of board upgrades and accessories.

Environmental Requirements

The environmental conditions must be tested and proven in the used system

configuration. The conditions refer to the surrounding of the board within the user

environment.

Note:aOperating temperatures refer to the temperature of the air circulating around the

board and not to the actual component temperature.

a

S Board damage

Operating the board in a chassis without forced air cooling may lead to board

damage.

When operating the board, make sure that forced air cooling is available.

S Board damage

High humidity and condensation on the board surface causes short circuits.

Do not operate the board outside the specified environmental limits. Make sure the

board is completely dry and there is no moisture on any surface before applying

power. Do not operate the board below 0°C.

Table 5: Environmental Requirements

Feature Operating Non−Operating

Temperature

Forced airflow 300 LFM (linear feet per minute) −

Temp. change

Rel. humidity

Altitude −300 m to + 3,000 m −300 m to + 13,000 m

Vibration aa aa

0°C to +50°C −40°C to +85°C

+/− 0.5°C/min +/− 1.0°C/min

5% to 95% non−condensating at +40°C

5% to 95% non−condensating at

+40°C

10 to 15 Hz

15 to 150 Hz

36 SPARC/CPU−56T

2 mm amplitude

2 g

5 mm amplitude

5 g

Page 37

Requirements Installation

Feature Non−OperatingOperating

Shock 5g/11 ms halfsine 15g/11 ms halfsine

Free fall 100 mm / 3 axes 1,200 mm / all edges and corners

(packed state)

Power Requirements

The board power requirements depend on the installed hardware accessories. In the

following table you will find typical examples of power requirements without any

accessories installed. If you want to install accessories on the board, the load of the

respective accessory has to be added to that of the board. For information on the

accessories’ power requirements, refer to the documentation delivered together with the

respective accessory or consult your local Force Computers representative for further

details.

The power supply has to meet the requirements given in the tables below.

Table 6: Power Requirements

Requirement

Minimum Voltage 4.88V 11.64V

Typical Voltage 5V 12V

Maximum Voltage 5.25V 12.6V

Typical Current 6A 1.5A

Maximum Current 7A 1.63A

Typical Power Requirement 30W 18W

Maximum Power Requirement

5V 12V

35W 20W

Note:aThe CPU board only powers up if the 5V and 12V supply voltages are stable and

within their limits. This complies to the VMEbus specification. However, there are

systems which are not fully VMEbus−compliant. The power supplies of these systems

do not turn on the 12V supply if the 5V supply has not been loaded before. Use a

VMEbus board which loads the 5V in these systems to avoid a power−up deadlock

situation.

a

SPARC/CPU−56T 37

Page 38

Installation Hardware Accessories

Hardware Accessories

The following upgrades and accessories are available:

S IOBPs for CPU and I/O Board

S PMC modules

S Memory modules

S Hard Disk

S SCSI−U160 cable

S RS−422 serial cable

S PS2 splitter cable

IOBPs for CPU and I/O Board

As separate price list items two IOBPs are available for the SPARC/CPU−56T. One is

called SPARC/IOBP−IO−56 and is connected to the I/O board. It is available in two

variants which differ in the number of VME connector rows: the three−row variant

SPARC/IOBP−IO−56−3 and the five−row variant SPARC/IOBP−IO−56−5. Both IOBPs

provide the following interfaces:

S SCSI (on SPARC/IOBP−IO−56−3 only single−ended SCSI)

S Audio

S PMC user I/O

For details about this IOBP and its installation refer to the

Guide.

The second IOBP is called SPARC/IOBP−CPU−56 and is connected to the CPU board. It is

available in two variants which also differ in the number of VMEconnector rows: the

three−row variant SPARC/IOBP−CPU−56−3 and the five−row variant

SPARC/IOBP−CPU−56−5. The interfaces available via both IOBP variants are:

S IDE

S 10/100Base−TX

S Parallel

aSPARC/IOBP−IO−56 Installation

S Two USB

S Two serial (RS−232 and RS−422)

38 SPARC/CPU−56T

Page 39

Hardware Accessories Installation

Note:aOn the IOBP−CPU−56−3 the RS−232 signals are limited to RXD, TXD, RTS and

CTS.

a

On the IOBP−CPU−56−5 the additional signals DTR, DSR, DCD and RI are available.a

In addition to these interfaces, the five−row variant IOBP−CPU−56−5 provides:

S Keyboard/mouse interface (SUN or PS/2 style)

S Third USB interface

S Floppy interface

S 10/100/1000 Base−TX Ethernet

For details about this IOBP and its installation refer to the

Installation Guide.

Board Damage

Using the board together with IOBPs for which it is not designed, may destroy the

board.

a

Only use the board together with the IOBP−CPU−56 or IOBP−IO−56.

PMC Modules

The I/O board allows to install three PMC modules compliant to IEEE P1386.a

Note:aThe used PMC modules must be compliant with the safety regulations of the

country where the equipment is installed.

The corresponding PMC slots are PMC slots 2, 3 and 4. The following figure shows which

PMC connectors are assigned to each PMC slot.

aSPARC/IOBP−CPU−56

a

SPARC/CPU−56T 39

Page 40

Installation Hardware Accessories

PMC#4 PMC#3 PMC#2

PMC slot 2 supports a 64−bit data bus width with a maximum frequency of 33 MHz and

is attached to PCI bus B. PMC slots 3 and 4 support a 64−bit data bus width with a

maximum frequency of 66 MHz and are attached to PCI bus C.

a

If a 32−bit PMC module is mounted into PMC slots 3 and 4, the Sentinel64 PCI−to−PCI

bridge dynamically detects the 32−bit bus and changes its transfer size to 32−bit for this

PMC module. If a 64−bit PMC module is mounted into PMC slots 3 and 4, burst transfers

between all 64−bit PCI devices on PCI bus B and C will be 64−bit PCI transfers.

Note:aIf a 33−MHz PMC module is mounted into PMC slots 3 and 4, the whole PCI bus

C will run with 33 MHz only. This may result in performance degradation.

The signaling level of each PMC slot is determined via a voltage key which has to be

installed into one of two holes that belong to each PMC slot. One hole corresponds to a

signalling level of 5V, the other to a signaling level of 3.3V. Depending on the hole the

voltage key is installed into, the signaling level is set accordingly. This is illustrated in the

figure below.

Figure 2: Location of PMC Voltage Keys

a

5V

3.3V

By default, PMC slots 3 and 4 have a signaling level of 3.3V and PMC slot 2 has a

signaling level of 5V. A description of how to change the signalling level for a PMC slot is

given in the following installation procedure.

a

Note:aA 66−MHz PCI bus configuration requires that the signaling level and therefore

the VI/O voltage is 3.3 V.

40 SPARC/CPU−56T

Page 41

Hardware Accessories Installation

Installation Procedure

Note:a

S To ensure proper EMC shielding, either operate each PMC slot with a blind panel

or with a PMC module installed.

S If the SPARC/CPU−56T is upgraded with PMC modules, ensure that the blind

panels are stored in a safe place in order to be used again when removing the

respective PMC module.a

S Processor PMC modules are only supported in non−monarch mode.a

Removing I/O Board

Start

1. Remove the 14 screws from I/O board which fix it to CPU board

SPARC/CPU−56T 41

Page 42

Installation Hardware Accessories

2. Carefully remove I/O board from CPU board by unplugging it from PMC

connectors

Finish

Changing Signaling Level

Start

1. Remove screw which fixes the voltage key to IO board

Voltage Key

Screw

2. Remove voltage key

3. Place voltage key into hole which corresponds to desired signalling level

5V

3.3V

Note:aThe signaling levels of PMC slots 3 and 4 must be equal. Otherwise they are

automatically set to 3.3V.

42 SPARC/CPU−56T

a

Page 43

Hardware Accessories Installation

4. Fix voltage key to I/O board by fastening screw

Voltage Key

Screw

Finish

Installing the PMC Module

Start

1. Plug PMC module into desired PMC connectors of I/O board

PMC#4 PMC#3 PMC#2

PMC Module Damage

If the power consumption of the PMC module exceeds 7.5W, the board and the PMC

module are damaged.

Make sure that the total power consumption at +/−12V, 5V and 3.3V level does not

exceed 7.5W.

2. Make sure standoffs of PMC module cover mounting holes of I/O board