Page 1

NCV78825

f

T

High Efficiency 3 A

Synchronous Buck Dual

LED Driver with Integrated

High Side Switch and

Current Sensing for

www.onsemi.com

Automotive Front Lighting

Description

The NCV78825 is a single−chip and high efficient Synchronous

Buck Dual LED Driver designed for automotive front lighting

applications like high beam, low beam, DRL (daytime running light),

turn indicator, fog light, static cornering, etc. The NCV78825 is in

particular designed for high current LEDs and provides a complete

solution to drive 2 LED strings of up−to 60 V. It includes 2

independent current regulators for the LED strings and required

diagnostic features for automotive front lighting with a minimum of

external components – the chip doesn’t need any external sense

resistor for the buck current regulation. The available output current

and voltages can be customized per individual LED string. When more

than 2 LED channels are required on 1 module, then 2, 3 or more

devices NCV78825 can be combined; also with NCV787x3 devices –

the predecessor of the NCV78825. Thanks to the SPI

programmability, one single hardware configuration can support

various application platforms.

Features

A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

G = Pb−Free Package

• Single Chip

• Buck Topology

• 2 LED Strings up−to 60 V

• High Current Capability up to 3 A DC per Output

See detailed ordering and shipping information on page 2 o

this data sheet.

ORDERING INFORMATION

• Integrated High Side Switch

• Low Side Pre−driver for External NMOS Device

• High Overall Efficiency

• Minimum of External Components

• Integrated High Accuracy Current Sensing

• Integrated Switched Mode Buck Current Regulator

• Average Current Regulation Through the LEDs

• High Operating Frequencies to Reduce Inductor Sizes

• Low EMC Emission for LED Switching and Dimming

ypical Applications

• High Beam

• Low Beam

• DRL

• Position or Park Light

• Turn Indicator

• Fog

• Static Cornering

• SPI Interface for Dynamic Control of System Parameters

• Fail Safe Operating (FSO) Mode, Stand−Alone Mode

• Master−Slave Synchronization Mode of the Buck Channels

• NCV Prefix for Automotive and Other Applications Requiring

Unique Site and Control Change Requirements; AEC−Q100

Qualified and PPAP Capable

• This is a Pb−Free Device

SSOP36 EP

CASE 940AB

MARKING DIAGRAM

NV78825−0

AWLYYWWG

© Semiconductor Components Industries, LLC, 2017

February, 2018 − Rev. 1

1 Publication Order Number:

NCV78825/D

Page 2

NCV78825

ORDERING INFORMATION

Table 1. AVAILABLE PART NUMBERS

Device Marking Package* Shipping

NCV78825DQ0R2G NV78825−0 SSOP36 EP

1500 / Tape & Reel

(PbFree)

*For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting

Techniques Reference Manual, SOLDERRM/D.

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging

Specification Brochure, BRD8011/D.

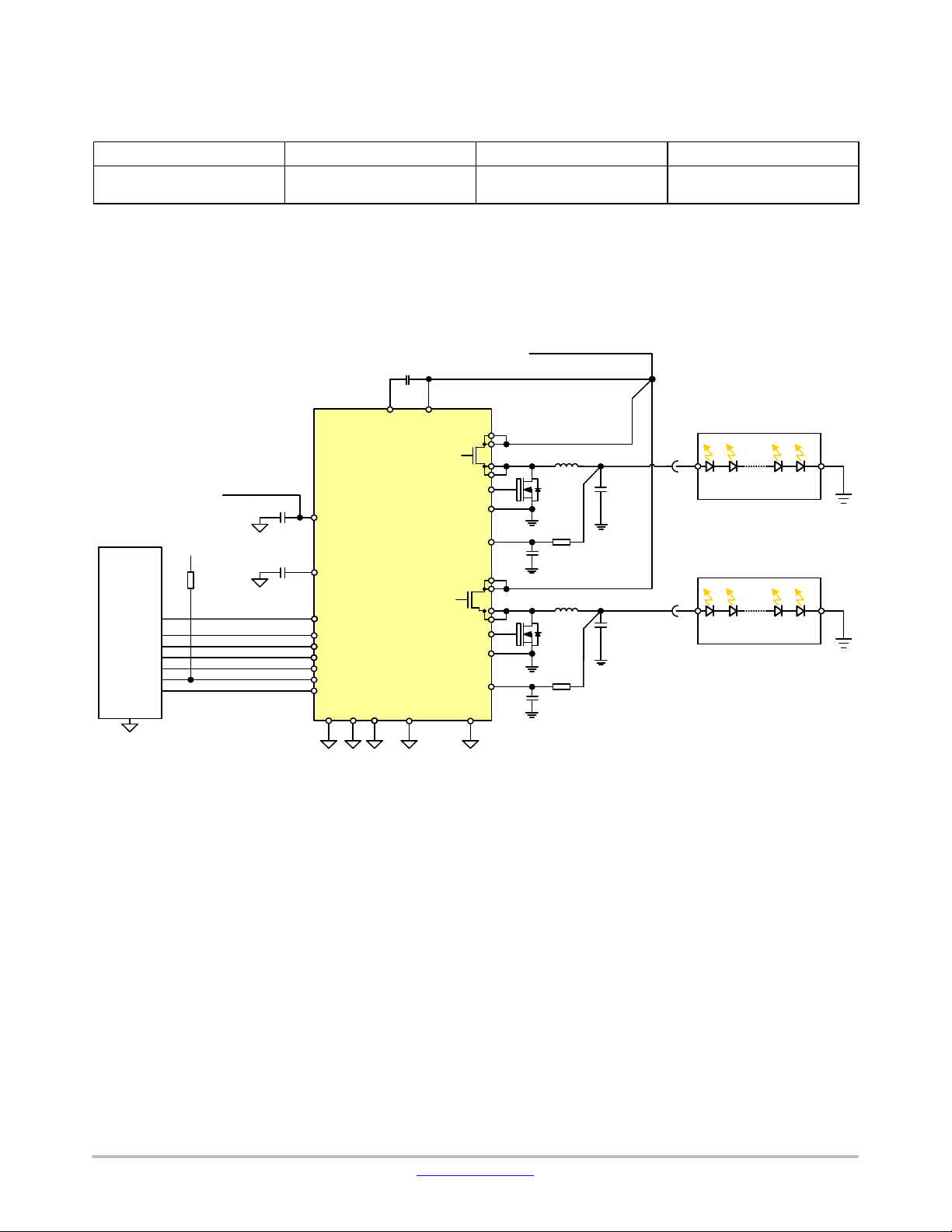

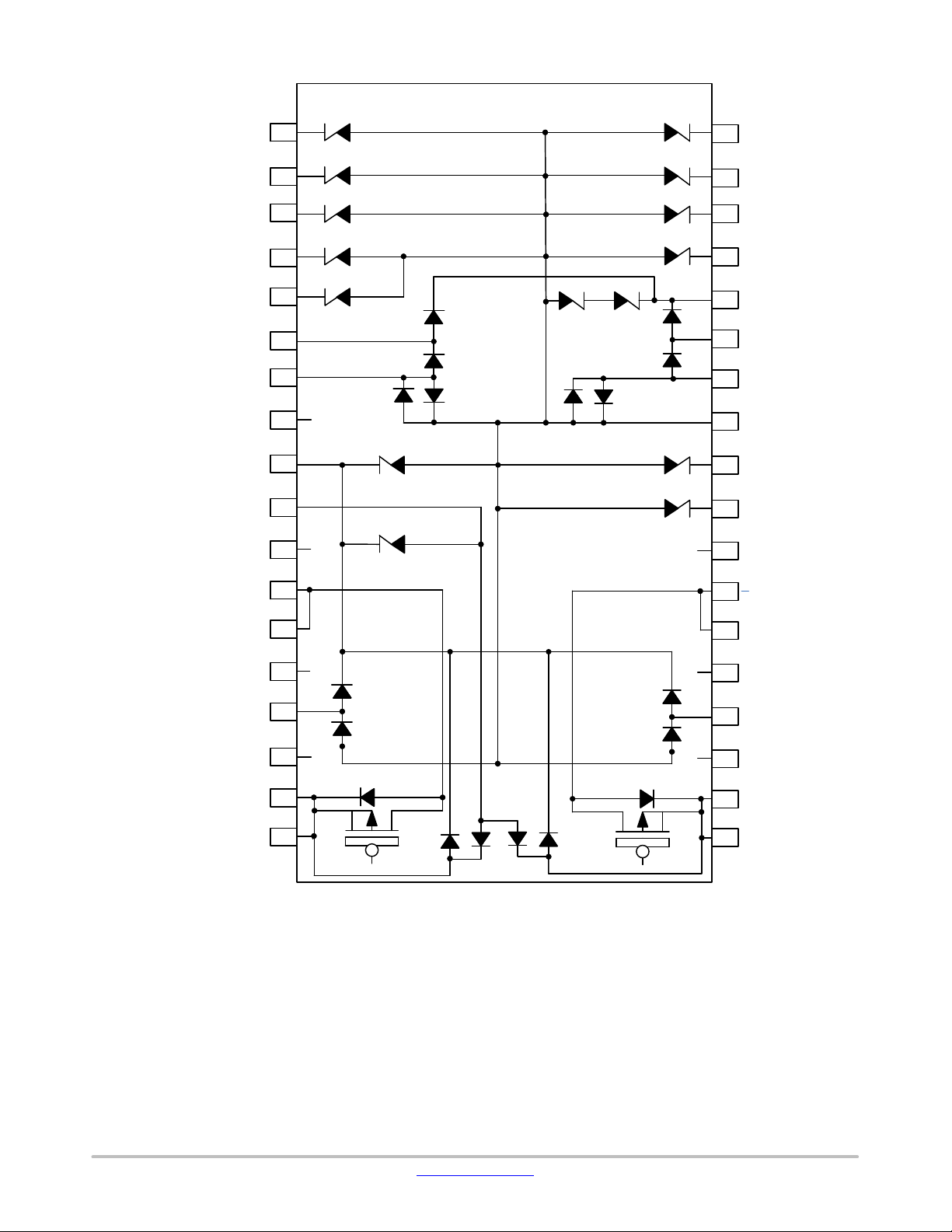

TYPICAL APPLICATION SCHEMATIC

VBOOST

C_M3V

†

μC

VIO of MCU

R_SDO

VDRIVE

C_DRV

C_DD

VINBCK1

VBOOST

LBCKSW1

VDRIVE

VDD_C

RSTB

LEDCTRL1

LEDCTRL2

SCLK

SDI

SDO

CSB

TEST

NCV78825

TEST1

TEST2

VBOOSTM3V

GND

LSFET1

GNDS1

VLED1

VINBCK2

LBCKSW2

LSFET2

GNDS2

VLED2

EXPOSED

PAD

R_LED_1

R_LED_2

Figure 1. Typical Application Schematic

L_BCK_1

T_LS 1

C_LED_1

L_BCK_2

T_LS 2

C_LED_2

LED−string 1

C_BCK_1

LED−string 2

C_BCK_2

www.onsemi.com

2

Page 3

NCV78825

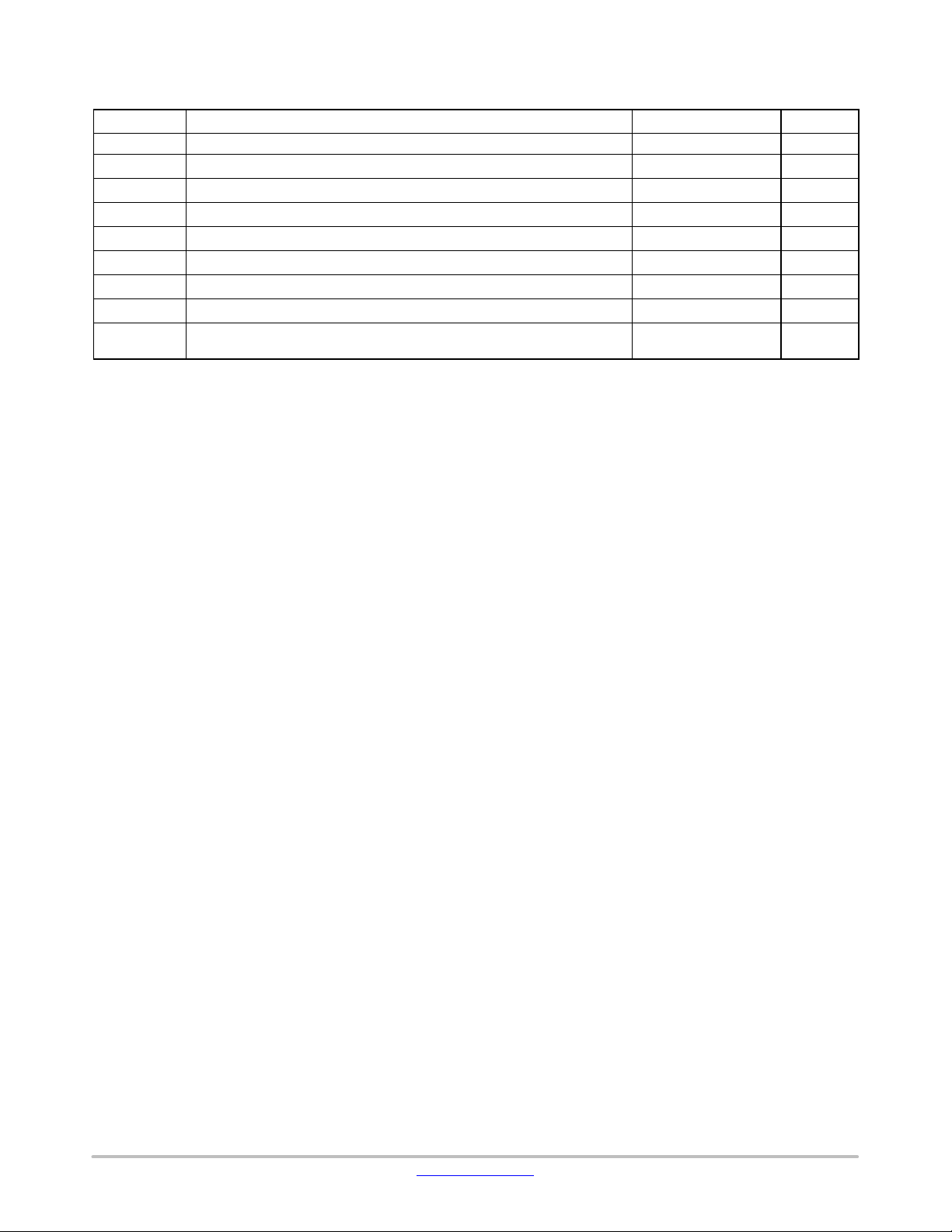

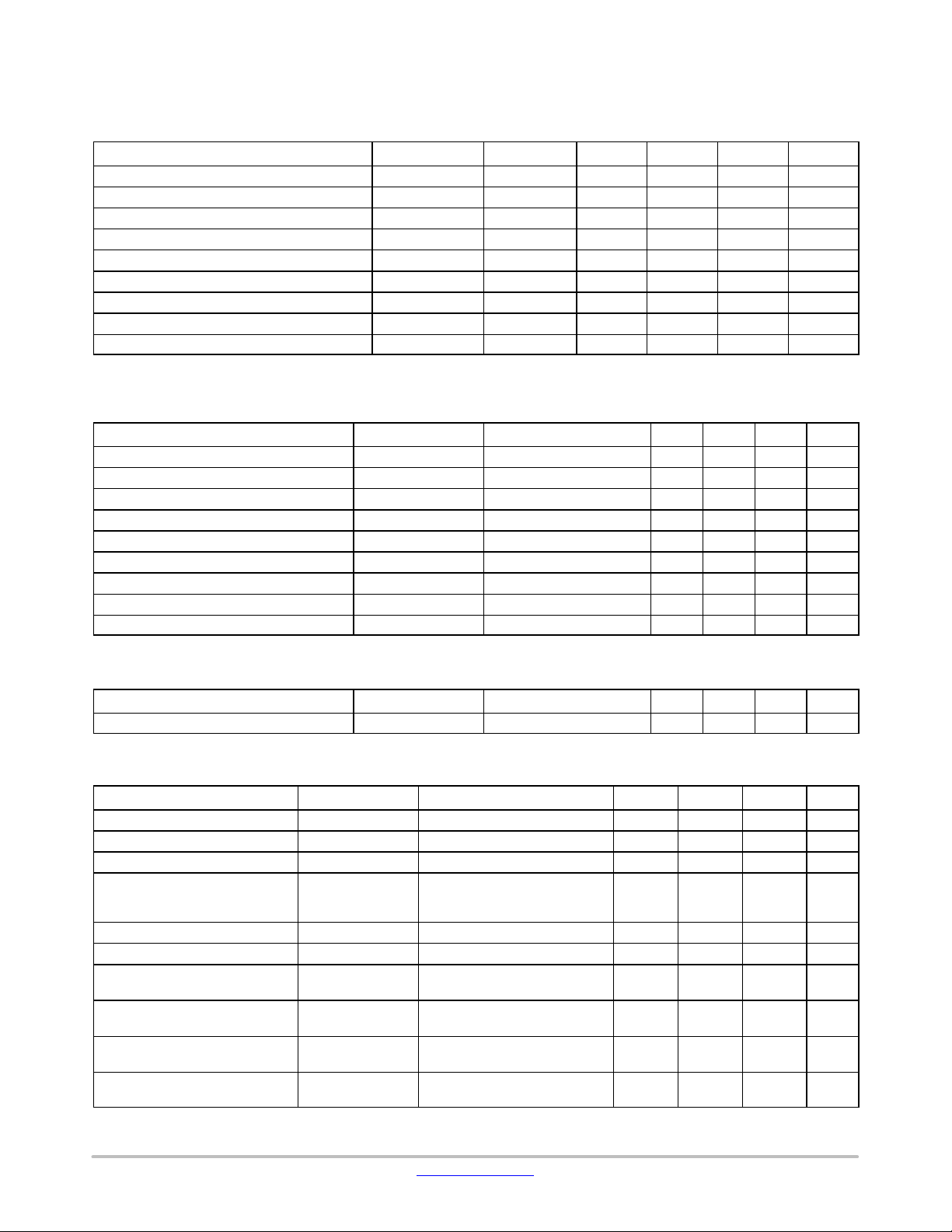

Table 2. EXTERNAL COMPONENTS

Component

L_BCK_x Buck regulator coil (see BUCK REGULATOR chapter for details) 47 (22) μH

C_BCK_x

C_M3V

C_DD

C_DRV

C_LED_x

R_LED_x

R_SDO

T_LSx

1. Pin TEST has to be connected to ground. TEST1 and TEST2 pins can be connected to ground or left floating.

2. C_LED_x is optional. If used, time constant of the C_LED_x and R_LED_x filter has to be lower than minimal LEDCTRLx PWM time for proper

VLED measurement.

3. R_LED_x is necessary to ensure Absolute maximum ratings of IVLEDx current (see Table 4).

4. GNDSx pins have to be star connections to the corresponding S of the external LS FET.

Buck regulator output capacitor (see BUCK REGULATOR chapter for details) 220 nF

Capacitor for M3V regulator 470 (see Table 8) nF

VDD decoupling capacitor 470 (see Table 7) nF

V

decoupling capacitor 470 nF

DRIVE

Optional VLEDx pin filter capacitor (Note 2) 1 nF

VLEDx pin serial resistor (Notes 2 and 3) 1 kΩ

SPI pull−up resistor 1 kΩ

Buck regulator low side switch (LS FET) NVTFS5C680NL,

Function Typ. Value Unit

NVMFS5C673NL

www.onsemi.com

3

Page 4

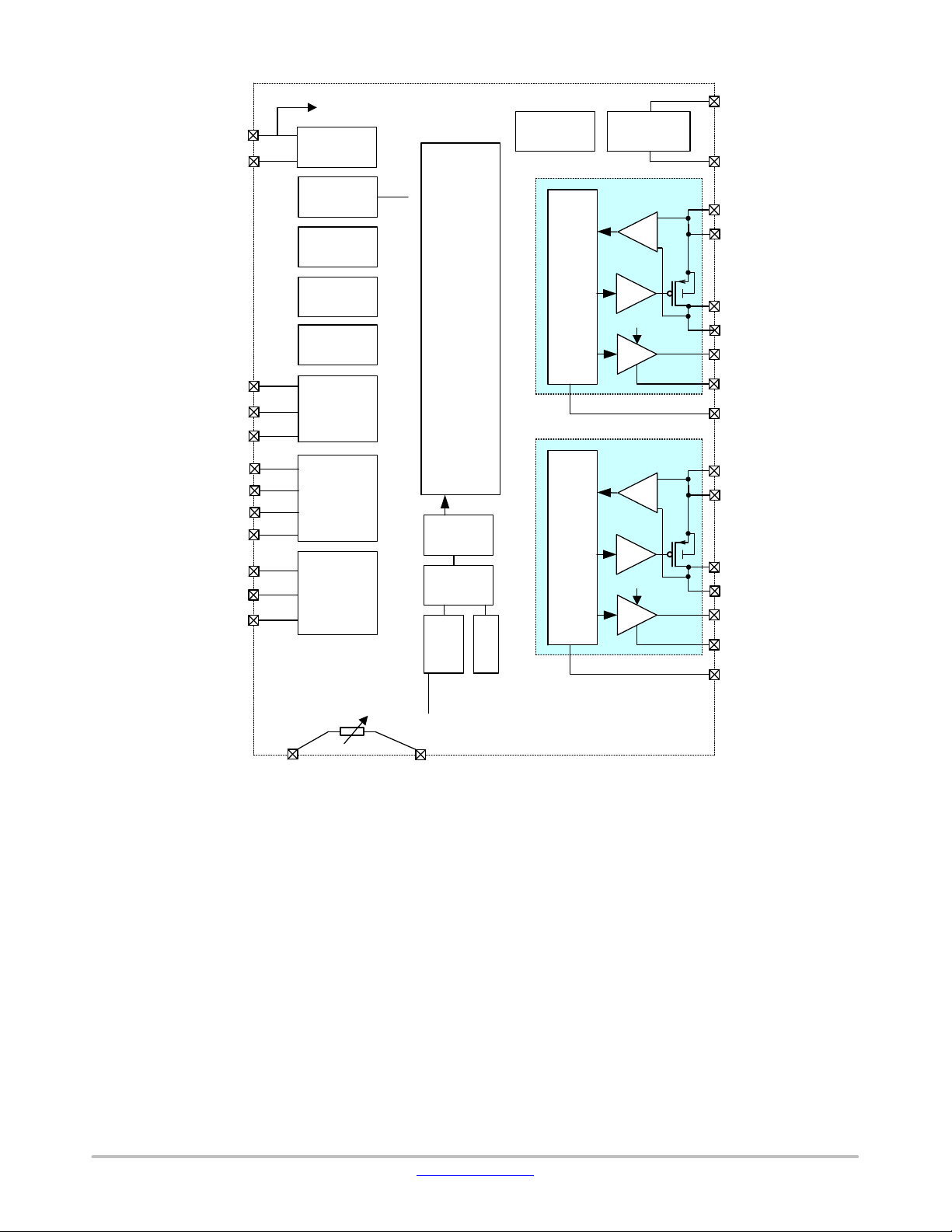

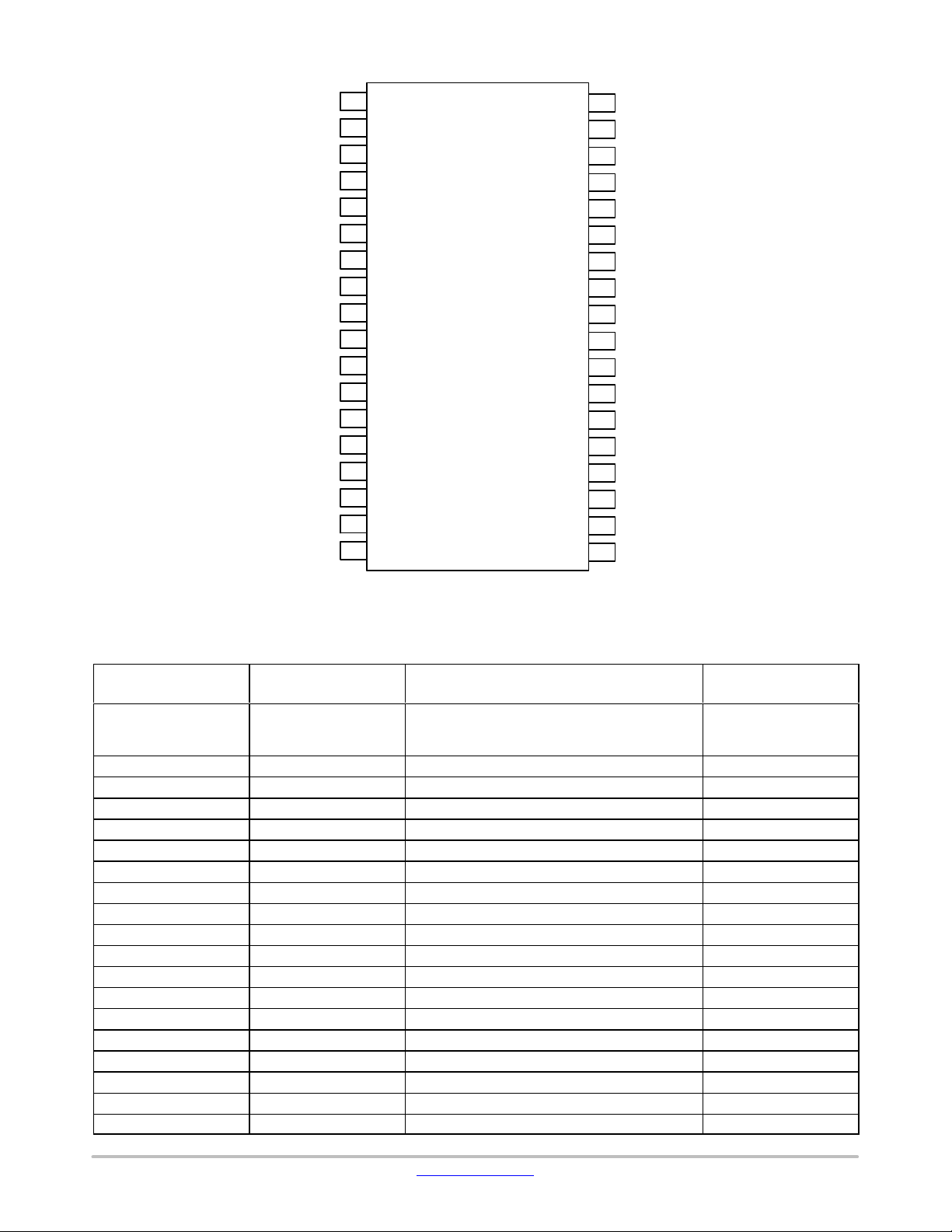

NCV78825

VDRIVE

(4.5 V – 10 V)

VDD_C

LEDCTRL1

LEDCTRL2

RSTB

SDI

SCLK

CSB

SDO

TEST

TEST1

TEST2

VGATE

LDO

Bandgap

POR

Bias

OSC

5 V input

5 V input/

OD output

LV IOs

2−Channel Buck

Vref

Digital control

ADC

MUX

Dividers

Temp

OTP

CTRL

CTRL

VBOOSTM3V

regulator

Current

sense CMP

Predriver

VGATE

Current

sense CMP

Predriver

VGATE

VBOOST

VBOOSTM3V

VINBCK11

VINBCK12

LBCKSW11

LBCKSW12

LSFET1

GNDS1

VLED1

VINBCK21

VINBCK22

LBCKSW21

LBCKSW22

LSFET2

GNDS2

VLED2

EXPOSED PAD

VDD,

VLEDx

VBOOST,

GND

Figure 2. Block Diagram

www.onsemi.com

4

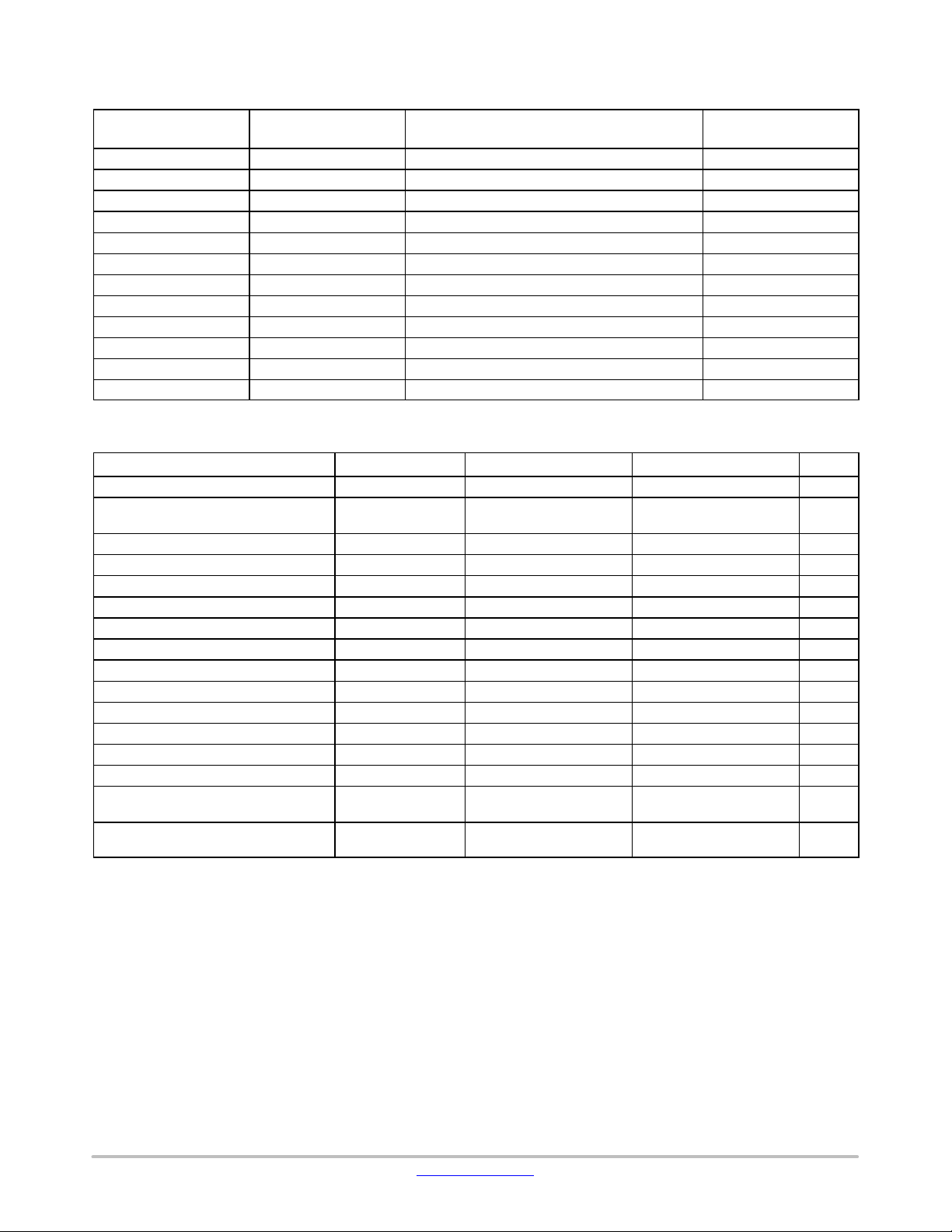

Page 5

NCV78825

RSTB

SDO

SCLK

SDI

CSB

LSFET1

GNDS1

NC

VBOOST

VBOOSTM3V

NC

10

11

1

2

3

4

5

6

7

8

9

36

35

34

33

32

31

30

29

28

27

26

LEDCTRL1

LEDCTRL2

TEST

TEST1

VDRIVE

LSFET2

GNDS2

GND

TEST2

VDD_C

NC

LBCKSW11

LBCKSW12

NC

VLED1

NC

VINBCK11

VINBCK12

12

13

14

15

16

SELF PROT PDMOS

17

18

Figure 3. ESD Schematic

SELF PROT PDMOS

25

24

23

22

21

20

19

LBCKSW21

LBCKSW22

NC

VLED2

NC

VINBCK21

VINBCK22

www.onsemi.com

5

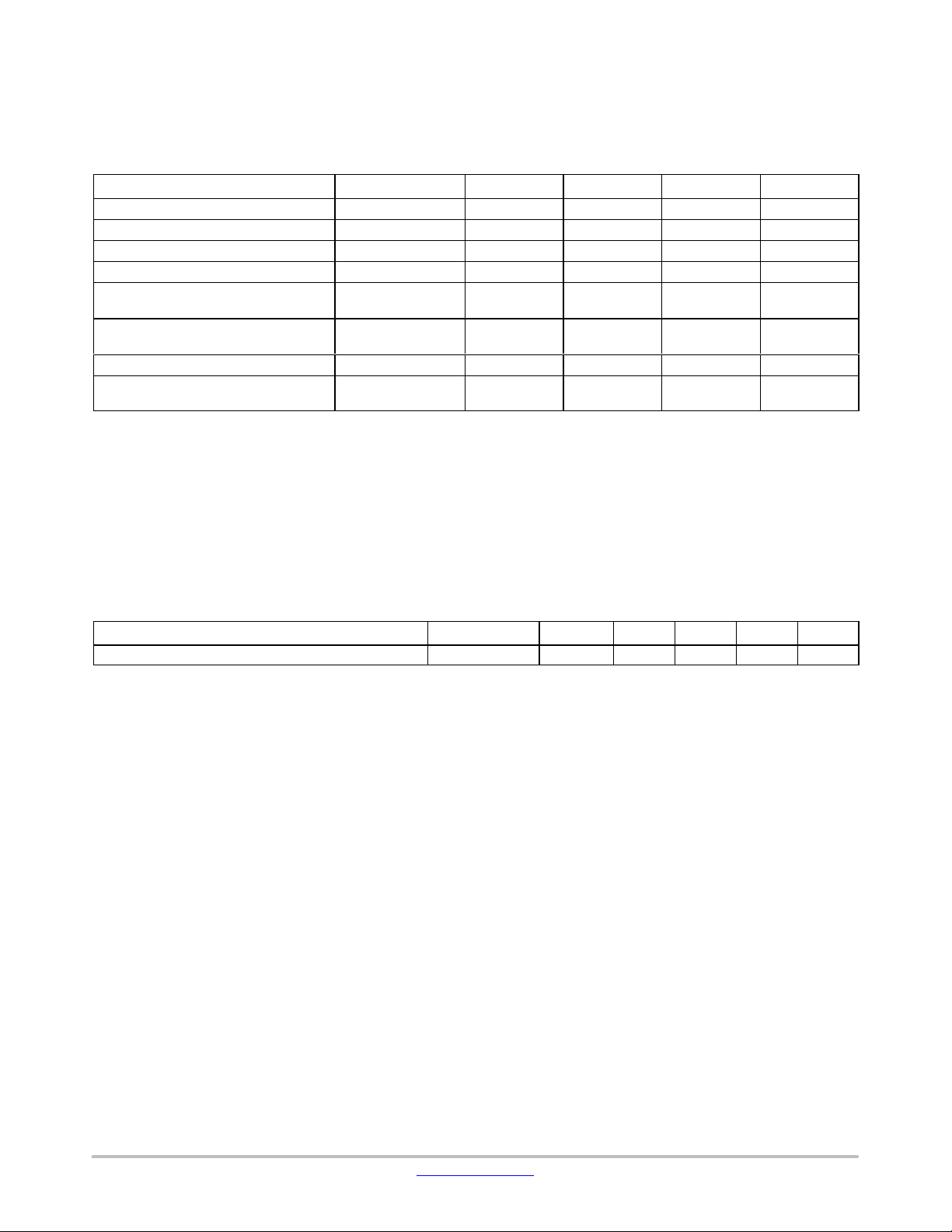

Page 6

RSTB

1

SDO

2

3

SCLK

4

SDI

5

CSB

LSFET1

6

GNDS1

7

NC

8

9

VBOOST

10

VBOOSTM3V

NC

11

12

LBCKSW11

13

LBCKSW12

14

NC

15

VLED1

16

NC

17

VINBCK11

18

VINBCK12

NCV78825

LEDCTRL1

LEDCTRL2

TEST

TEST1

VDRIVE

LSFET2

GNDS2

GND

TEST2

VDD_C

NC

LBCKSW21

LBCKSW22

NC

VLED2

NC

VINBCK21

VINBCK22

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

Figure 4. Pin Connections − SSOP36−EP (Top View)

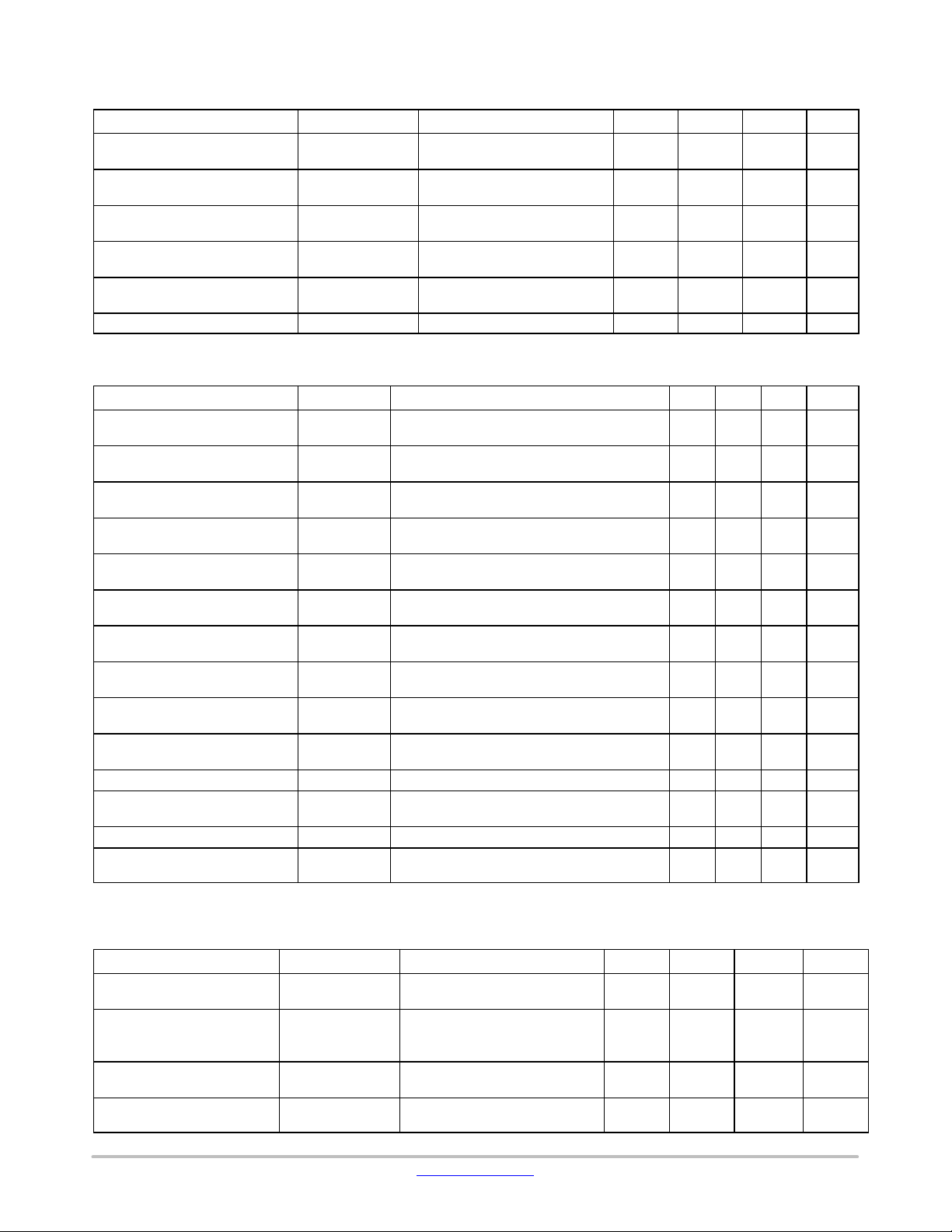

Table 3. PIN DESCRIPTION

Pin No.

SSOP36−EP

VBOOST Supply

Voltage

1

2 SDO SPI data output MV open−drain

3 SCLK SPI clock MV in

4 SDI SPI data input MV in

5 CSB SPI chip select (chip select bar) MV in

6 LSFET1 Buck 1 driver output for ext. low side switch MV out

7 GNDS1 Buck 1 ground sense for ext. low side switch MV out

8, 11, 14, 16, 21, 23, 26 GND/NC GND/NC connection in application NC

9 VBOOST Booster input voltage pin HV supply

10 VBOOSTM3V VBOOSTM3V regulator output pin HV out (supply)

12 LBCKSW11 Buck 1 switch output HV out

13 LBCKSW12 Buck 1 switch output HV out

15 VLED1 LED String 1 Forward Voltage Sense Input HV in

17 VINBCK11 Buck 1 high voltage supply HV supply

18 VINBCK12 Buck 1 high voltage supply HV supply

19 VINBCK22 Buck 2 high voltage supply HV supply

20 VINBCK21 Buck 2 high voltage supply HV supply

22 VLED2 LED String 2 Forward Voltage Sense Input HV in

24 LBCKSW22 Buck 2 switch output HV out

Pin Name Description I/O Type

RSTB External reset signal MV in

www.onsemi.com

6

Page 7

NCV78825

Table 3. PIN DESCRIPTION (continued)

Pin No.

SSOP36−EP

25 LBCKSW21 Buck 2 switch output HV out

27 VDD_C 3.3 V logic supply LV supply

28 TEST2 Internal function. To be tied to GND or left open LV in/out

29 GND Ground Ground

30 GNDS2 Buck 2 ground sense for ext. low side switch MV out

31 LSFET2 Buck 2 driver output for ext. low side switch MV out

32 VDRIVE Pre−driver supply MV supply

33 TEST1 Internal function. To be tied to GND or left open LV in/out

34 TEST Internal function. To be tied to GND LV in

35 LEDCTRL2 LED string 2 enable MV in

36 LEDCTRL1 LED string 1 enable MV in

EP EXPOSED PAD To be tied to GND

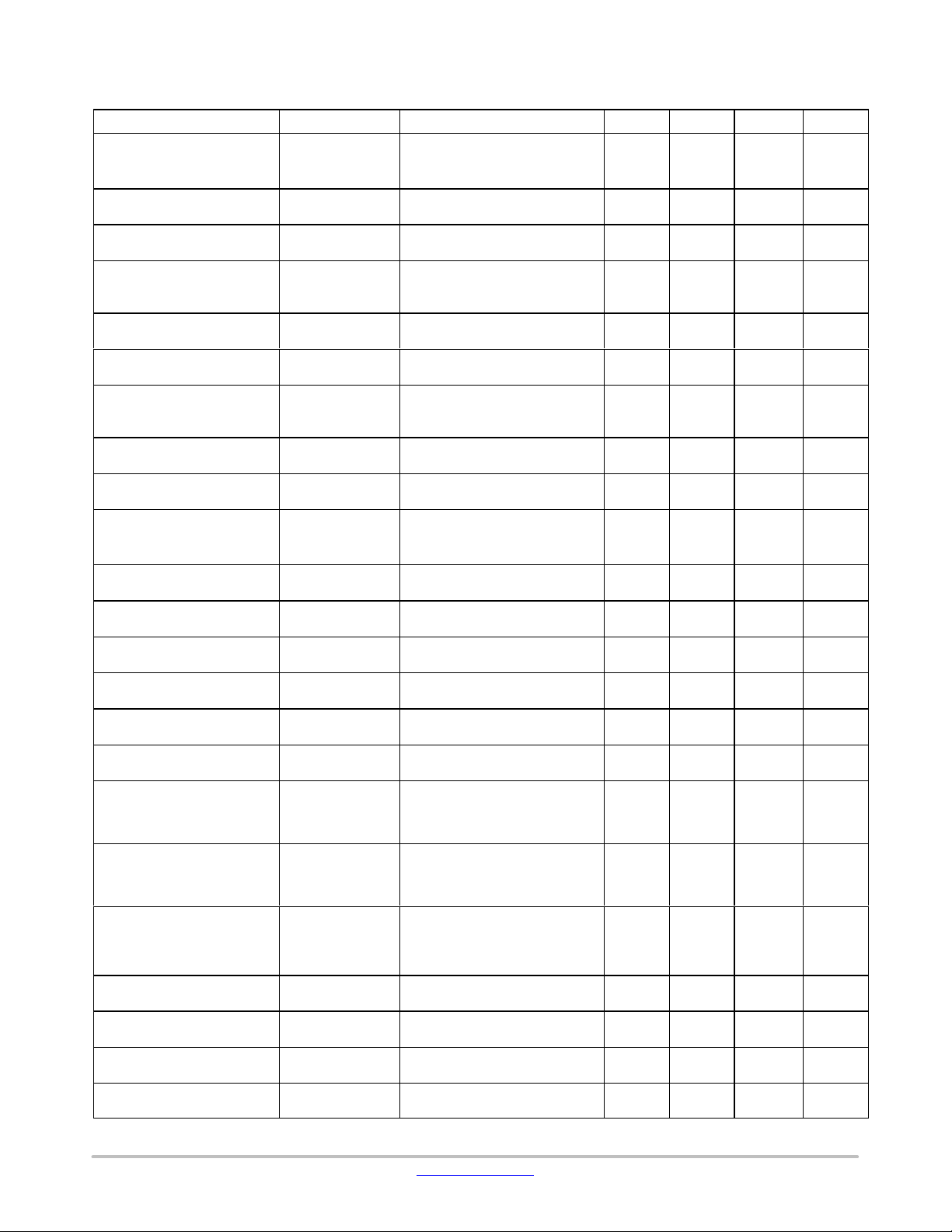

Table 4. ABSOLUTE MAXIMUM RATINGS

Characteristic

VBOOST Supply Voltage V

VINBCKx Supply Voltage (Note 1) VINBCKx Max of

VBOOSTM3V Supply Voltage (Note 2) VBOOSTM3V Max of V

VDRIVE Supply Voltage VDRIVE −0.3 12 V

LSFETx Voltage (Note 3) LSFETx −0.3 Min of VDRIVE + 0.3, 12 V

VLED Sense Voltage VLEDx −0.3 Min of V

Logic Supply Voltage (Note 4) V

Medium Voltage IO Pins IOMV −0.3 7.0 V

Test Pins (Note 5) TESTx −0.3 Min of V

Buck Switch Low Side (Note 1) LBCKSWx −2 VINBCKx + 0.3 V

VLED Sink/source Current IVLEDx −30 30 mA

Storage Temperature (Note 6) T

The Exposed Pad (Note 7) EXPAD GND − 0.3 GND + 0.3 V

The LS Pre−driver Sense GND Voltage GNDSx GND − 0.3 GND + 0.3 V

Electrostatic Discharge on Component

Level Human Body Model (Note 8)

Electrostatic Discharge on Component

Level Charge Device Model (Note 8)

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality

should not be assumed, damage may occur and reliability may be affected.

1. V(VINBCKx − LBCKSWx) < 70 V, the driver in off state.

2. The VBOOSTM3V regulator in off state.

3. The LSFETx driver in HiZ state.

4. Absolute maximum rating for pins: VDD, TEST. Also valid for relative difference VBOOST − VBOOSTM3V.

5. Absolute maximum rating for pins: TEST1, TEST2.

6. For limited time up to 100 hours. Otherwise the max storage temperature is 85°C.

7. The exposed pad must be hard wired to GND pin in the application to ensure both electrical and thermal connection.

8. This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per AECQ100002 (EIA−JESD22A114−B)

ESD Charge Device Model tested per EIA−JESD22C101

Latchup Current Maximum Rating: 100 mA per JEDEC standard: JESD78

Symbol Min Max Unit

BOOST

DD

STRG

V

ESD_HBM

V

ESD_CDM

VBOOSTM3V − 0.3, −0.3

−0.3 68 V

Min of V

BOOST

− 3.6, −0.3 Min of V

BOOST

BOOST

BOOST

−0.3 3.6 V

DD

−50 150 °C

−2 +2 kV

−500 +500 V

I/O TypeDescriptionPin Name

+ 0.3, 68 V

+ 0.3, 68 V

+ 0.3, 68 V

+ 0.3, 3.6 V

www.onsemi.com

7

Page 8

NCV78825

Operating ranges define the limits for functional

operation and parametric characteristics of the device. A

mission profile (Note 1) is a substantial part of the operation

conditions; hence the Customer must contact

ON Semiconductor in order to mutually agree in writing on

the allowed missions profile(s) in the application.

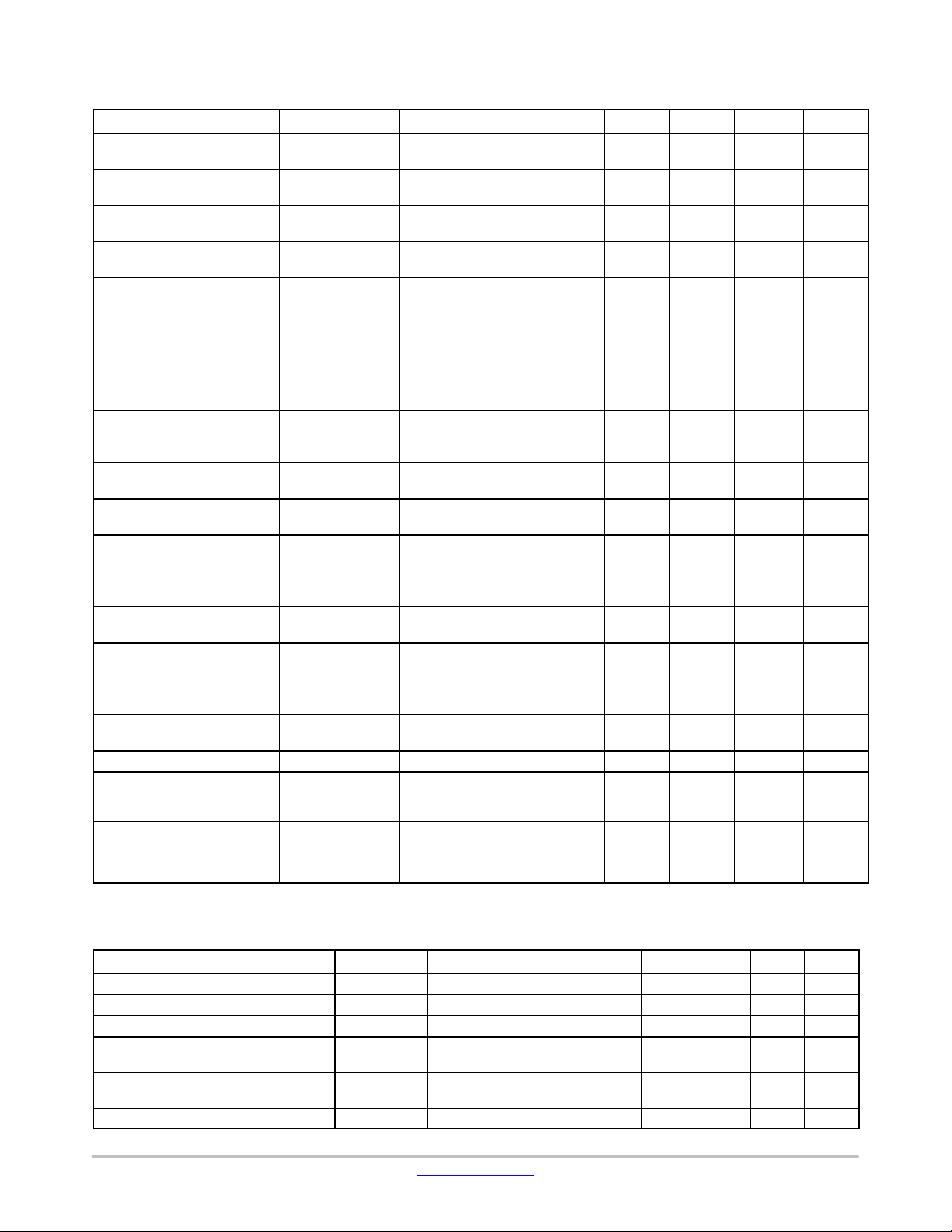

Table 5. RECOMMENDED OPERATING RANGES

Characteristic

Boost Supply Voltage V

VINBCKx Supply Voltage (Note 2) VINBCKx V

VDRIVE Voltage Supply VDRIVE 4.5 10 V

Buck Switch Peak Output Current I_LBCKSW 3.8 A

Functional Operating Junction

Temperature Range (Note 3)

Parametric Operating Junction

Temperature Range (Note 4)

The Exposed Pad Connection (Note 5) EXPOSED_PAD GND − 0.1 GND GND + 0.1 V

The LS Pre−driver Sense GND Voltage

(Note 6)

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond

the Recommended Operating Ranges limits may affect device reliability.

1. A mission profile describes the application specific conditions such as, but not limited to, the cumulative operating conditions over life time,

the system power dissipation, the system’s environmental conditions, the thermal design of the customer’s system, the modes, in which the

device is operated by the customer, etc. No more than 100 cumulated hours in life time above T

2. Hard connection of VINBCKx to VBOOST on PCB.

3. The circuit functionality is not guaranteed outside the functional operating junction temperature range. Also please note that the device is

verified on bench for operation up to 170°C but that the production test guarantees 155°C only.

4. The parametric characteristics of the circuit are not guaranteed outside the Parametric operating junction temperature range.

5. The exposed pad must be hard wired to GND pin in an application to ensure both electrical and thermal connection.

6. The hard connection of the GNDSx pins on the PCB, mainly to the S of the LS NMOS device

corresponding S of the LS NMOS max +/− 0.2 mV.

Symbol Min Typ Max Unit

BOOST

T

JF

T

JP

GNDSx GND − 0.1 GND GND + 0.1 mV

6 67 V

− 0.1 V

BOOST

−40 155 °C

−40 150 °C

BOOST

V

.

tw

+ 0.1 V

BOOST

the voltage difference between the pin and

Table 6. THERMAL RESISTANCE

Characteristic

Thermal Resistance Junction to Exposed Pad (Note 1) SSOP36−EP Rthjp − 3.5 − °C/W

1. Includes also typical solder thickness under the Exposed Pad (EP).

Package Symbol Min Typ Max Unit

www.onsemi.com

8

Page 9

NCV78825

ELECTRICAL CHARACTERISTICS

Table 7. VDD: 3.3 V LOW VOLTAGE ANALOG AND DIGITAL SUPPLY

Characteristic Symbol Conditions Min Typ Max Unit

The Regulator Output Voltage VDD 3.05 3.45 3.6 V

VDD External Decoupling Cap C_DD 0.3 0.47 2.2 μF

The VDRIVE Current Consumption (Note 2) I_VDRIVE 8 15 mA

Output Current Limitation VDD_ILIM 15 160 mA

POR Toggle Level on VDD Rising POR

POR Toggle Level on VDD Falling POR

POR Hysteresis POR

OTP UV Toggle Level on VBOOST OTP_UV 13 15 V

OTP UV Toggle Level Hysteresis OTP_UV_HYST 0.01 0.2 0.75 V

1. All Min and Max parameters are guaranteed over full junction temperature (TJP) range (−40 °C; 150 °C), unless otherwise specified.

2. Only internal consumption, Excluding LS NMOS gate charge current.

3V_H

3V_L

3V_HYST

Table 8. VBOOSTM3V: HIGH SIDE AUXILIARY SUPPLY

Characteristic

VBOOSTM3V Regulator Output Voltage V

DC Output Current Capability (Note 1) M3V_IOUT 7.5 42 mA

Output Current Limitation M3V_ILIM 300 mA

VBOOSTM3V External Decoupling Cap C_M3V Referenced to VBOOST 0.1 0.47 2.2

VBOOSTM3V Ext. Decoupling Cap. ESR C_M3V_ESR Referenced to VBOOST 200

VBSTM3V POR Level, Falling Edge M3V_PORL Referenced to VBOOST −2.7 −1.8 V

VBSTM3V POR Level, Rising Edge M3V_PORH Referenced to VBOOST −2.4 −1.8 V

VBSTM3V POR Level Hysteresis M3V_PORHYST 0.05 V

VBOOST POR Level M3V_VBSTPOR VBOOST goes down 3.5 5.5 V

1. VBOOST = 68 V, f

= 2 MHz, maximum total gate charge for both activated BUCK channels Qgate = 20 nC

BUCK

Symbol Conditions Min Typ Max Unit

BSTM3V

Referenced to VBOOST −3.6 −3.3 −3.0 V

2.7 3.05 V

2.45 2.8 V

0.01 0.2 0.75 V

mF

mW

Table 9. OSC10M: SYSTEM OSCILLATOR CLOCK

Characteristic Symbol Conditions Min Typ Max Unit

System Oscillator Frequency FOSC10M 8 10 12 MHz

Table 10. ADC FOR MEASURING VBOOST, VDD, VLED1, VLED2, TEMP

Characteristic

ADC Resolution ADC_RES 8 Bits

Integral Nonlinearity (INL) ADC_INL Best fitting straight line method −1.5 1.5 LSB

Differential Nonlinearity (DNL) ADC_DNL Best fitting straight line method −2 2 LSB

Full Path Gain Error for

Measurements of VLEDx,

VBOOST

Offset at Output of ADC ADC_OFFS −2 2 LSB

Time for 1 SAR Conversion ADC_CONV Full conversion of 8 bits 6.67 8 10

ADC Full Scale for VDD

Measurement

ADC Full Scale for VLEDx

Measurement

ADC Full Scale for VLEDx

Measurement

ADC Full Scale for VLEDx

Measurement

Symbol Conditions Min Typ Max Unit

ADC_GE −3.25 3.25 %

ADCFS_VDD 3.87 4 4.13 V

ADCFS_VLED00 The VLED range code is “00” 67.725 70 72.275 V

ADCFS_VLED01 The VLED range code is “01” 48.375 50 51.625 V

ADCFS_VLED10 The VLED range code is “10” 38.700 40 41.300 V

ms

www.onsemi.com

9

Page 10

NCV78825

Table 10. ADC FOR MEASURING VBOOST, VDD, VLED1, VLED2, TEMP (continued)

Characteristic UnitMaxTypMinConditionsSymbol

ADC Full Scale for VLEDx

Measurement

ADC Full Scale for VBOOST

Measurement

TSD Threshold Level ADC_TSD ADC measurement of junction

Temperature measurement

accuracy at hot

Temperature measurement

accuracy at cold

VLED Input Impedance VLED_RES 280 790

Table 11. BUCK REGULATOR – SWITCH

Characteristic Symbol Conditions Min Typ Max Unit

On Resistance, Range 1 RON1 At room−temperature, I(VINBCKx) = 0.18 A,

On Resistance at Hot, Range 1 RON1_H At Tj = 160 °C, I(VINBCKx) = 0.18 A,

On Resistance, Range 2 RON2 At room−temperature, I(VINBCKx) = 0.375 A,

On Resistance at Hot, Range 2 RON2_H At Tj = 160 °C, I(VINBCKx) = 0.375 A,

On Resistance, Range 3 RON3 At room−temperature, I(VINBCKx) = 0.75 A,

On Resistance at Hot, Range 3 RON3_H At Tj = 160 °C, I(VINBCKx) = 0.75 A,

On Resistance, Range 4 RON4 At room−temperature, I(VINBCKx) = 1.5 A,

On Resistance at Hot, Range 4 RON4_H At Tj = 160 °C, I(VINBCKx) = 1.5 A,

On Resistance, Range 5 RON5 At room−temperature, I(VINBCKx) = 3 A,

On Resistance at Hot, Range 5 RON5_H At Tj = 160 °C, I(VINBCKx) = 3 A,

Switching Slope – ON Phase TRISE Normal mode (DRV_SLOW_EN = “0”) 3 V/ns

Switching Slope – OFF Phase

(Note 22)

Switching Slope – ON Phase TRISE_SL Slow mode (DRV_SLOW_EN = “1”) 1.5 V/ns

Switching Slope – OFF Phase

(Note 22)

1. Falling switching slope depends on used current (range, current sense threshold level) and LBCKSWx node capacitance.

ADCFS_VLED11 The VLED range code is “11” 29.025 30 30.975 V

ADCFS_VBST 67.725 70 72.275 V

163 169 175 °C

temperature

ADC_TEMP_H T = 155°C −7 7 °C

ADC_TEMP_C T = −40°C −15 15 °C

7.36

V(BOOST − VINBCKx) 0.2 V

6.3 10.2

V(BOOST − VINBCKx) 0.2 V

3.68

V(BOOST − VINBCKx) 0.2 V

3.2 5.12

V(BOOST − VINBCKx) 0.2 V

1.84

V(BOOST − VINBCKx) 0.2 V

1.7 2.56

V(BOOST − VINBCKx) 0.2 V

0.92

V(BOOST − VINBCKx) 0.2 V

0.9 1.28

V(BOOST − VINBCKx) 0.2 V

0.46

V(BOOST − VINBCKx) 0.2 V

0.5 0.64

V(BOOST − VINBCKx) 0.2 V

TFALL Normal mode (DRV_SLOW_EN = “0”) 3 V/ns

TFALL_SL Slow mode (DRV_SLOW_EN = “1”) 1.5 V/ns

kW

W

W

W

W

W

W

W

W

W

W

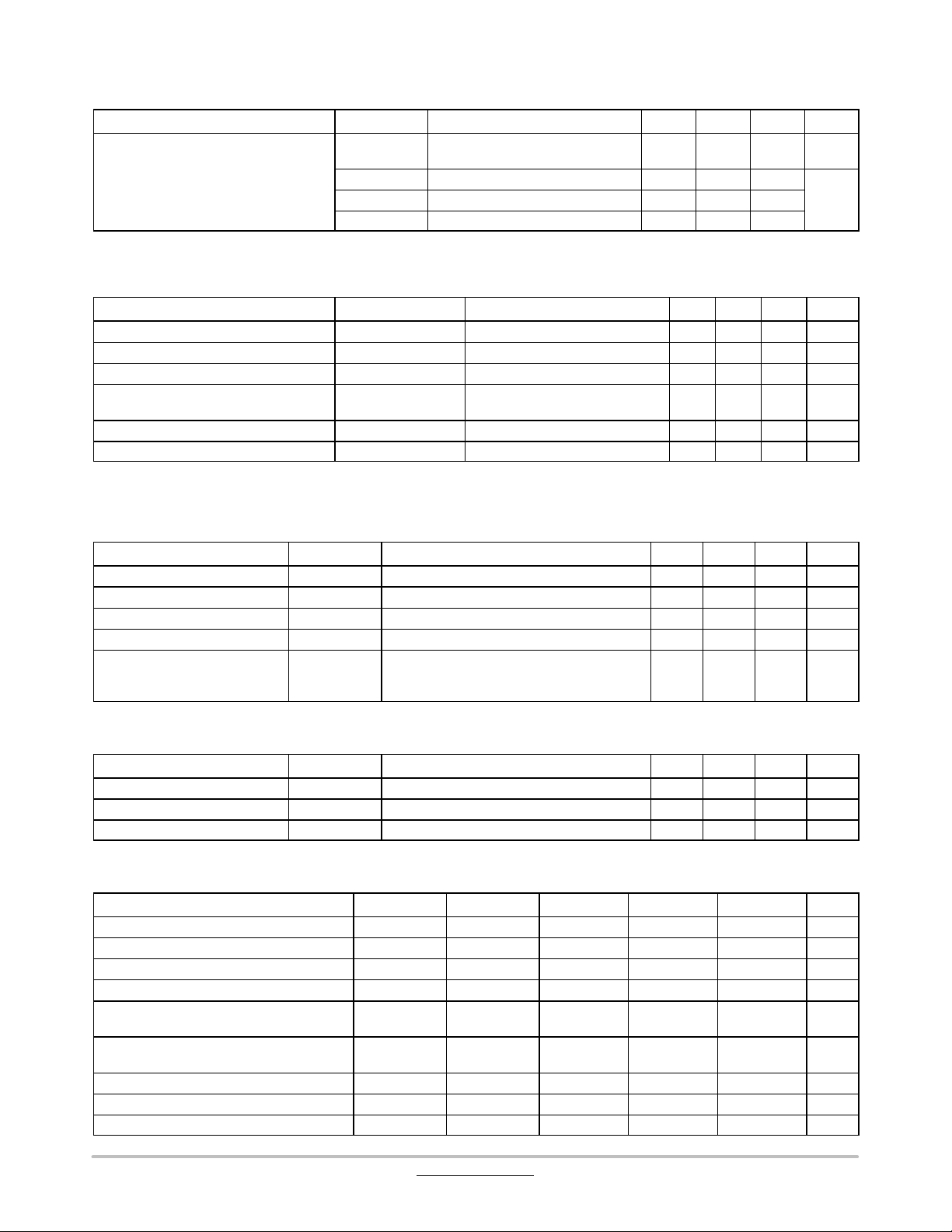

Table 12. BUCK REGULATOR – CURRENT REGULATION

Characteristic Symbol Conditions Min Typ Max Unit

Current Sense Threshold

Level, Range 1, Min Value

Current Sense Threshold

Level, Range 1, Spec. Value

Current Sense Threshold

Level, Range 1, Max Value

Current Sense Threshold

Level, Range 2, Min Value

ITHR1_000 [BUCKx_VTHR = 000000000]

end of the BUCK ON−phase

ITHR1_219 [BUCKx_VTHR = 011011011]

end of the BUCK ON−phase

Min. value for specified precision

ITHR1_511 [BUCKx_VTHR = 111111111]

end of the BUCK ON−phase

ITHR2_000 [BUCKx_VTHR = 000000000]

end of the BUCK ON−phase

23.40 29.30 35.20 mA

117.19 mA

234.38 mA

46.90 58.59 70.30 mA

www.onsemi.com

10

Page 11

NCV78825

Table 12. BUCK REGULATOR – CURRENT REGULATION (continued)

Characteristic UnitMaxTypMinConditionsSymbol

Current Sense Threshold

Level, Range 2, Spec. Value

Current Sense Threshold

Level, Range 2, Max Value

Current Sense Threshold

Level, Range 3, Min Value

Current Sense Threshold

Level, Range 3, Spec. Value

Current Sense Threshold

Level, Range 3, Max Value

Current Sense Threshold

Level, Range 4, Min Value

Current Sense Threshold

Level, Range 4, Spec. Value

Current Sense Threshold

Level, Range 4, Max Value

Current Sense Threshold

Level, Range 5, Min Value

Current Sense Threshold

Level, Range 5, Spec. Value

Current Sense Threshold

Level, Range 5, Max Value

Current Sense Threshold

Increase per Code, Range 1

Current Sense Threshold

Increase per Code, Range 2

Current Sense Threshold

Increase per Code, Range 3

Current Sense Threshold

Increase per Code, Range 4

Current Sense Threshold

Increase per Code, Range 5

Current Threshold Accuracy

Only with Trimming Constant

for Range 5 (Note 23)

Current Threshold Accuracy

without Temperature

Compensation (Note 23)

Current Threshold Accuracy

(Note 23)

Offset of Peak Current

Comparator

Over−current Detection

Level, Range1

Over−current Detection

Level, Range2

Over−current Detection

Level, Range3

ITHR2_219

ITHR2_511 [BUCKx_VTHR = 111111111]

ITHR3_000 [BUCKx_VTHR = 000000000]

ITHR3_219 [BUCKx_VTHR = 011011011]

ITHR3_511 [BUCKx_VTHR = 111111111]

ITHR4_000 [BUCKx_VTHR = 000000000]

ITHR4_219 [BUCKx_VTHR = 011011011]

ITHR4_511 [BUCKx_VTHR = 111111111]

ITHR5_000 [BUCKx_VTHR = 000000000]

ITHR5_219

ITHR5_511 [BUCKx_VTHR = 111111111]

dITHR1

dITHR2

dITHR3

dITHR4

dITHR5

ITHR_ERR_DD Specified for BUCKx_VTHR

ITHR_ERR_D Specified for BUCKx_VTHR

ITHR_ERR

CMP_OFFSET BUCKx_OFF_CMP_DIS = 1 −10 +10 mV

OCDR1 305 mA

OCDR2 609 mA

OCDR3 1219 mA

[BUCKx_VTHR = 011011011]

end of the BUCK ON−phase.

Min. value for specified precision

end of the BUCK ON−phase

end of the BUCK ON−phase

end of the BUCK ON−phase

Min. value for specified precision

end of the BUCK ON−phase

end of the BUCK ON−phase

end of the BUCK ON−phase

Min. value for specified precision

end of the BUCK ON−phase

end of the BUCK ON−phase

[BUCKx_VTHR = 011011011]

end of the BUCK ON−phase

Min. value for specified precision

end of the BUCK ON−phase

9 bit, linear increase 0.40 mA

9 bit, linear increase 0.80 mA

9 bit, linear increase 1.61 mA

9 bit, linear increase 3.21 mA

9 bit, linear increase 6.42 mA

011011011, without the delta of

the trimming code and without

temp. compensation

011011011, with the delta of the

trimming code and without temp.

compensation

Specified for BUCKx_VTHR

011011011, the delta of the

trimming code and temp.

compensation

234.38 mA

468.75 mA

93.80 117.19 140.60 mA

468.75 mA

937.5 mA

187.50 234.38 281.30 mA

937.5 mA

1875 mA

375.00 468.75 562.50 mA

1875 mA

3750 mA

−9 +9 %

−7 +7 %

−4 +4 %

www.onsemi.com

11

Page 12

NCV78825

Table 12. BUCK REGULATOR – CURRENT REGULATION (continued)

Characteristic UnitMaxTypMinConditionsSymbol

Over−current Detection

Level, Range4

Over−current Detection

Level, Range5

Time Constant for Longest

Off Time

Time Constant for Shortest

Off Time

TOFF Time Relative Error

with Temperature

Compensation

TOFF Time Relative Error TOFF_ERR TC = Toff × VCOIL @ VLED > 2

TOFF Time Absolute Error TOFF_ERR_ABS TC = Toff × VCOIL @ VLED > 2

Time Constant Decrease per

Code

Detection Level of VLED to

be too Low

Zero−cross−detection

Threshold Level

Zero−cross−detection Filter

Time

HS Overvoltage Detection

Threshold Level

HS Overvoltage Detection

Filter Time

HS Gate Voltage Detection

Threshold Level

HS Gate Voltage Detection

Filter Time

OpenLEDx Detection Time TON_OPEN 40 50 60

Buck Minimum TON Time TON_MIN For

Delay from BUCKx ISENS

Comparator Input Voltage

Balance to BUCKx Switch

Going OFF

1. Measured as comparator DC threshold value, without comparator delay and switch falling slope.

OCDR4 2437 mA

OCDR5 4875 mA

TC_00 [BUCKx_TOFF = 00000] 50

TC_31 [BUCKx_TOFF = 11111] 5

TOFF_ERRW TC = Toff × VCOIL @ VLED > 2

Toff > 350 ns, Toff temperature

dependency relative to Thot =

155°C, see Figure 8

dTC

VLED_LMT 1.62 1.8 1.98 V

TC_ZCD −2.8 −1.2 −0.2 mV

TC_ZCD_FT 20 80 ns

OVD_THR LBCKSWx−VINBCKx, rising

OVD_FT 100 ns

HSVT_THR 0.6 V

HSVT_FT 45 ns

ISENSCMP_DEL ISENS cmp. over−drive ramp >

5 bits, exponential decrease 7.16 %

VINBCKx – LBCKSWx < 2.4 V,

no failure at LBCKSWx pin

for Slope = 1.25 A/μs, @125°C

V,

V,

Toff > 350 ns

V,

Toff 350 ns

edge

1 mV/10 ns,

−10 +10 %

−15 +15 %

−35 +35 ns

100 200 mV

50 250 ns

45 ns

ms × V

ms × V

ms

Table 13. BUCK REGULATOR – LS SWITCH PRE−DRIVER

Characteristic

Top Switch Ron Ront 40

Bottom Switch Ron Ronb 8

The Pull Down Resistor LS_PUD 10

LS FET Gate Voltage Threshold Level LS_VT Comparator level for non−overlap

LS FET Gate Voltage Comparator

Propagation Delay

The Maximum Reverse Polarity Current LS_IREV LSx_IREV_NOCTRL = 1 300 mA

Symbol Conditions Min Typ Max Unit

0.4 V

control when LS−>off, HS−>on

LS_DEL 10 ns

www.onsemi.com

12

W

W

kW

Page 13

NCV78825

Table 13. BUCK REGULATOR – LS SWITCH PRE−DRIVER (continued)

Characteristic UnitMaxTypMinConditionsSymbol

The non−overlap Time LS−off to HS−on

1. The time from detection of the LS switch in off state (pre−driver voltage at LS_VT threshold), to start of switching HS on.

Table 14. 5 V TOLERANT DIGITAL INPUTS (SCLK, CSB, SDI, LEDCTRL1, LEDCTRL2, RSTB)

Characteristic

High−level Input Voltage VINHI 2 V

Low−level Input Voltage VINLO 0.8 V

Pull Resistance (Note 1) Rpull 40 160

LED PWM Propagation Delay (Note 2) BUCKx_SW_DEL Activation time of the BUCKx

Sampling Resolution LEDCTRL_SR 100 125 ns

RSTB Debouncer Time RSTB_DEB 100 200 ns

1. Pull down resistor (Rpd) for RSTB, LEDCTRLx, SDI and SCLK, pull up resistor (Rpu) for CSB to VDD.

2. Jitter is present due to the internal resynchronization.

LS_DT Adaptive: LSx_NO_MD[1:0] = 00

30 ns

(Note 1)

LS_FNO1 Adaptive: LSx_NO_MD[1:0] = 01 1 6.5

LS_FNO2 Fixed: LSx_NO_MD[1:0] = 10 2.5

LS_FNO3 Fixed: LSx_NO_MD[1:0] = 11 5

Symbol Conditions Min Typ Max Unit

4.4 5.5 6.95

switch from the LEDCTRLx pin

% of

Toff

kW

ms

Table 15. 5 V TOLERANT OPEN−DRAIN DIGITAL OUTPUT (SDO)

Characteristic

Low−voltage Output Voltage VOUTLO Iout = −10 mA (current flows into the pin) 0.4 V

Equivalent Output Resistance RDSON Lowside switch 10 40

SDO Pin Leakage Current SDO_ILEAK 2

SDO Pin Capacitance SDO_C 10 pF

CLK to SDO Propagation

Delay

Symbol Conditions Min Typ Max Unit

SDO_DL Low−side switch activation/deactivation time;

60 ns

@1 kΩ to 5 V, 100 pF to GND, for falling

edge V(SDO) goes below 0.5 V

Table 16. 3V DIGITAL INPUTS (TEST, TEST1, TEST2)

Characteristic

High−level Input Voltage VIN3HI 2.3 V

Low−level Input Voltage VIN3LO 0.8 V

Pull Resistance Rpd3 Pull−down resistance 60

Symbol Conditions Min Typ Max Unit

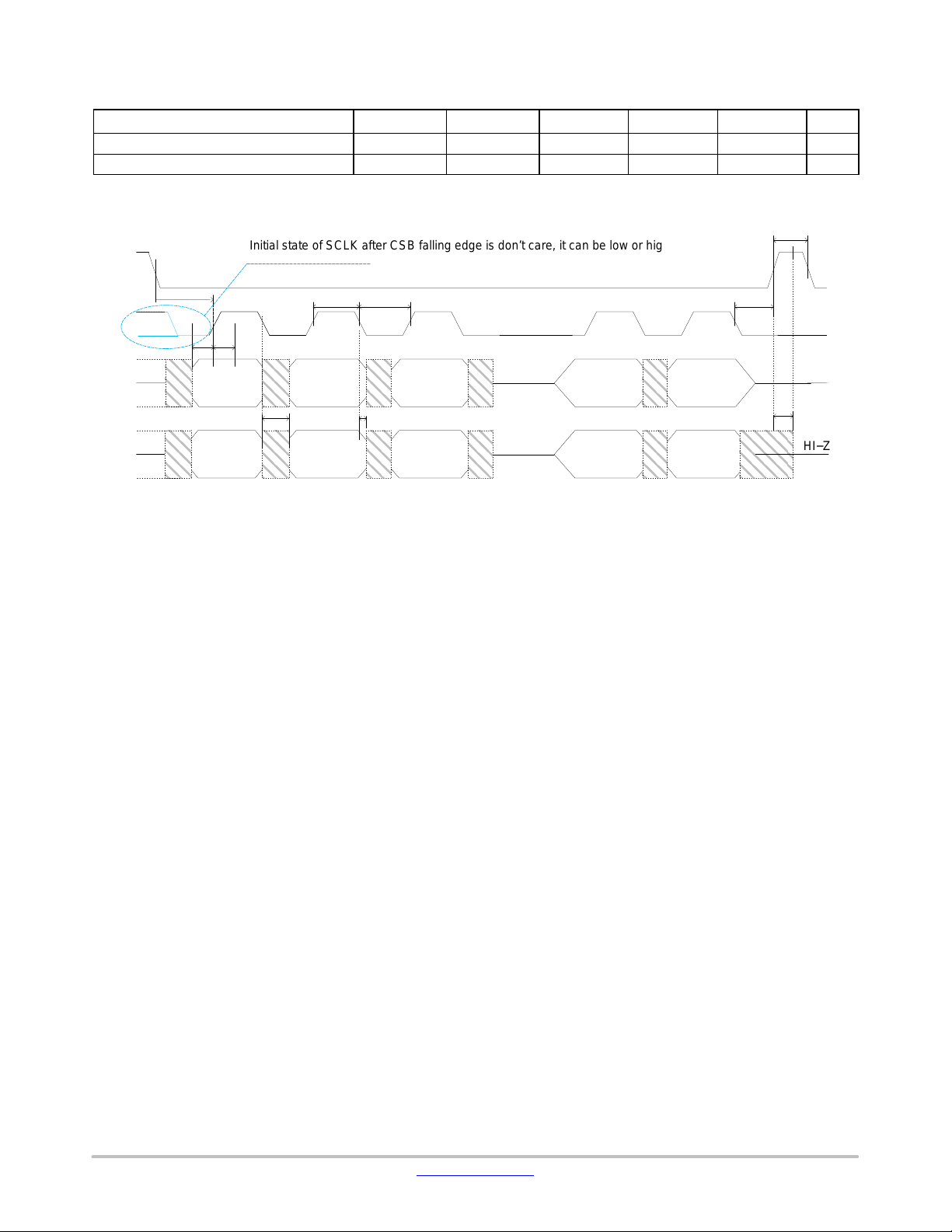

Table 17. SPI INTERFACE

Characteristic

CSB Setup Time t

CSB Hold Time t

SCLK Low Time t

SCLK High Time t

Data−in (DIN) Setup Time, Valid Data

before Rising Edge of CLK

Data−in (DIN) Hold Time, Hold Data after

Rising Edge of CLK

Output (DOUT) Disable Time (Note1) t

Output (DOUT) Valid (Note 1)

Output (DOUT) Valid (Note 2)

Symbol Conditions Min Typ Max Unit

CSS

CSH

WL

WH

t

DIS

t

V1→0

t

V0→1

SU

t

H

0.5 μs

0.25 μs

0.5 μs

0.5 μs

0.25 μs

0.275 μs

0.08 0.32 μs

0.32 μs

0.32 + t(RC) μs

W

mA

kW

www.onsemi.com

13

Page 14

Table 17. SPI INTERFACE (continued)

t

Characteristic UnitMaxTypMinConditionsSymbol

Output (DOUT) Hold Time t

CSB High Time t

1. SDO low–side switch activation time

2. Time depends on the SDO load and pull–up resistor

HO

CS

NCV78825

0.01 μs

1 μs

V

IH

CSB

V

IL

V

IH

SCLK

V

IL

V

IH

DIN

V

IL

V

IH

DOUT

HI−Z

V

IL

Initial state of SCLK after CSB falling edge is don’t care, it can be low or high

t

CSS

SU

tHt

DIN15

t

V

t

WH

DIN14

t

WL

DIN13

t

HO

CSB

DIN1

DOUT15 DOUT14 DOUT13 DOUT1 DOUT0

Figure 5. SPI Communication Timing

DIN0

t

CSH

t

CS

DIS

HI−Z

www.onsemi.com

14

Page 15

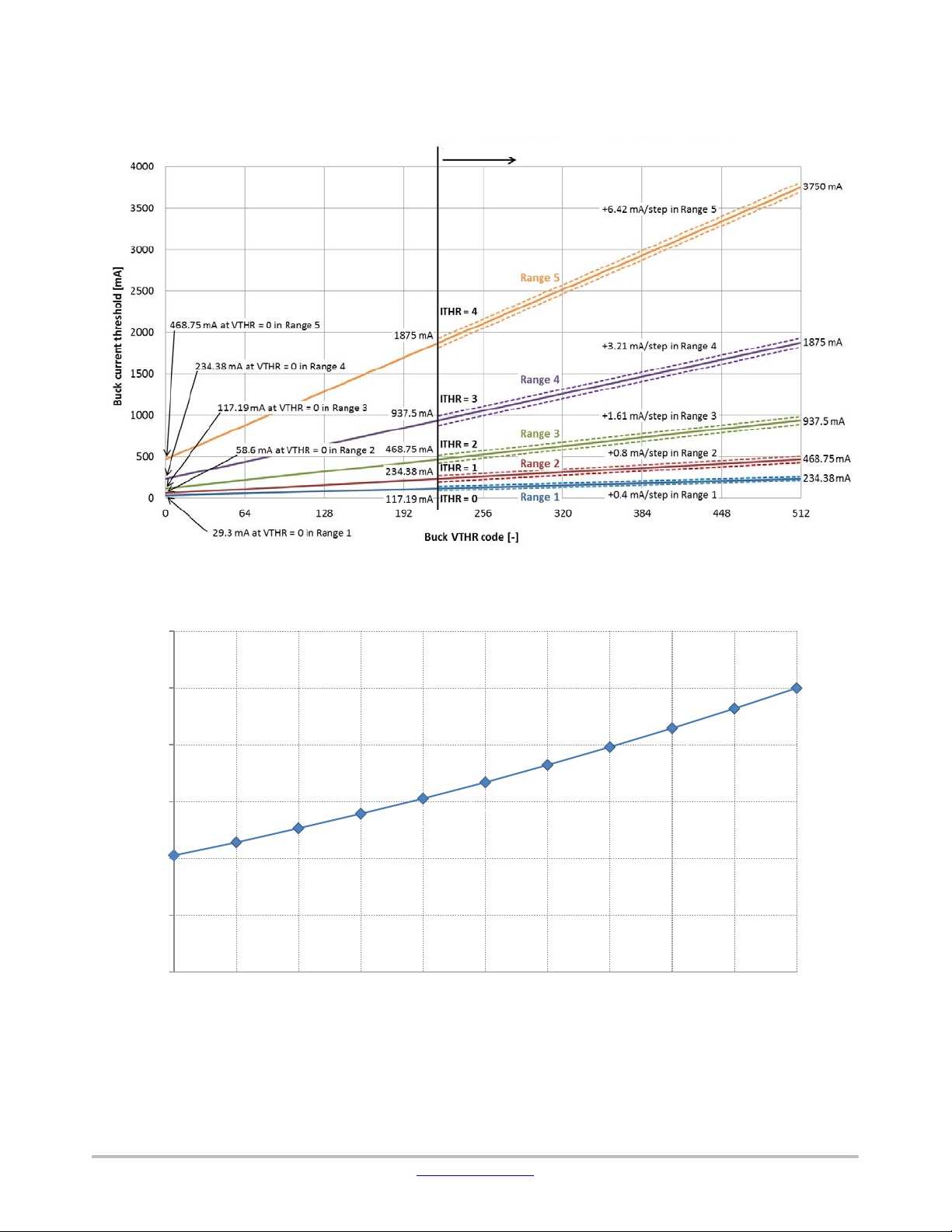

TYPICAL CHARACTERISTICS

NCV78825

Accuracy (±4% / ±7% / ±9%) guaranteed from VTHR code 219 [dec]

219

Figure 6. Buck Peak Current vs. Ranges and VTHR Code

120

[%]

100

80

79,2

72,9

60

40

41,0

20

Buck Switch Rdson relative to value at 1605C

0

−40 −20 0 20 40 60 80 100 120 140 160

45,6

50,6

55,7

61,1

66,8

Temperature [5C]

85,9

100,0

92,7

Figure 7. Typical Temperature Behavior of Buck HS Switch Rdson Relative to the V alue at 160ºC

www.onsemi.com

15

Page 16

NCV78825

6

5

4

TOFF_err = −0.025 x Tj + 3.875

3

2

dependecy [%]

1

0

TOFF time relative error temperature

−45 −20 5 30 55 80 105 130 155

Temperature [5C]

Figure 8. TOFF Time Relative Error Temperature Dependency Relative to Thot at 155°C

75,0

70,0

65,0

60,0

55,0

50,0

45,0

Comparator delay [ns]

40,0

35,0

30,0

25,0

0,1 1 10

Slope [A/ms] for Range 5 (Note *)

Figure 9. Typical Comparator Delay vs Slope

1. Range 5: Comp. delay [ns] = (0.04 × Temp [ °C] + 40) × Slope [A/us, range 5] ^ (−0.17)

Notes:

2. Range 4: Comp. delay [ns] = (0.04 × Temp [ °C] + 40) × Slope × 2 [A/us, range 5] ^ (−0.17)

3. Range 3: Comp. delay [ns] = (0.04 × Temp [ °C] + 40) × Slope × 4 [A/us, range 5] ^ (−0.17)

4. Range 2: Comp. delay [ns] = (0.04 × Temp [ °C] + 40) × Slope × 8 [A/us, range 5] ^ (−0.17)

5. Range 1: Comp. delay [ns] = (0.04 × Temp [ °C] + 40) × Slope × 16 [A/us, range 5] ^ (−0.17)

*in lower ranges, the same current slope (A/μs) translates into a higher voltage slope (V/μs) at the input of the comparator,

because of the higher Rdson. Resulting equations for all ranges:

−40degC

25degC

85degC

125degC

150degC

www.onsemi.com

16

Page 17

NCV78825

DETAILED OPERATING DESCRIPTION

Supply Concept in General

Two voltages have to be brought to the NCV78825 chip

– low voltage VDRIVE supply and high voltage VBOOST

for providing energy to the buck regulators. More detailed

description follows.

VDRIVE Supply

The VDRIVE supply voltage represents power for the

complete LS pre−driver block as well as for VDD supply.

The selection of external LS FET is driven by available

voltage for VDRIVE supply. There is not implemented any

voltage monitor on VDRIVE supply.

VBOOSTM3V Supply

The VBOOSTM3V is the high side auxiliary supply for

driving the gates of the buck regulator’s integrated

high−side P−MOSFET switches. This supply receives

energy directly from the VBOOST pin, which has to be

connected by low impedance track to input pins of both buck

channels VINBCKx.

The dedicated Power−On−Reset circuit (POR) of

high−side P−MOSFET switches monitors correct voltage

level of both this auxiliary supply and VBOOST voltage in

order to guarantee correct control of integrated switches.

VDD Supply

The VDD supply is the low voltage digital and analog

supply for the chip and derives energy from VDRIVE supply

voltage. NCV78825 contains internal VDD regulator.

The Power−On−Reset circuit (POR) monitors the VDD

voltage and RSTB pin to control the out−of−reset and reset

entering state. At power−up, the chip will exit from reset

state when VDD > POR3V_H and RSTB pin is in “log. 1”.

No SPI communication is possible in reset state.

VBOOST Supply

The VBOOST supply voltage is the main high voltage

supply for the chip. The voltage is supposed to be provided

by booster chip such as NCV78702/3 or NCV78763 in the

application. VINBCKx pins have to be connected by low

impedance track to this supply to ensure proper buck

performance.

The VBOOST voltage is monitored by under−voltage

comparator to check sufficient zapping voltage at VBOOST

pin during OTP programming operation.

Module Startup

A limited transient activation of the buck switch inside the

NCV78825 device can be measured at module startup, when

supply voltages VBOOST and VDRIVE rise for the first

time and voltage regulators VDD and M3V pass POR

thresholds.

In rare application cases a limited energy transfer to the

buck circuit, may build a voltage on the output capacitor

which reaching the LED voltage threshold, resulting in a

weak light output pulse. The pulse duration can be

suppressed by using slower VBOOST slope, smaller M3V

capacitor, bigger output capacitor value and VDRIVE

supply connection before VBOOST supply.

Internal Clock Generation – OSC10M

An internal RC clock named OSC10M is used to run all

the digital functions in the chip. The clock is trimmed in the

factory prior to delivery. Its accuracy is guaranteed under

full operating conditions and is independent from external

component selection (refer to Table 9 for details). All

timings depend on OSC10M accuracy.

www.onsemi.com

17

Page 18

NCV78825

BUCK REGULATOR

General

The NCV78825 contains two high−current integrated

buck current regulators, which are the sources for the LED

strings. The bucks are powered from the external booster

regulator.

Buck Current Regulation Principle

Each buck controls the individual inductor peak current

(I

BUCKpeak

(ΔI

BUCKpkpk

current through the LED string, independently from the

string voltage. The buck average current is in fact described

by the formula:

This is graphically exemplified by Figure 10.

) and incorporates a constant ripple

) control circuit to ensure also stable average

DI

BUCK

I

BUCK

AVG

I

BUCK

peak

pkpk

2

(eq. 1)

The parameter I

BUCKpeak

is programmable through the

device by means of the internal registers for range selection

BUCKx_ISENS_THR[2:0] and current threshold code

BUCKx_VTHR[8:0]. The range setting will be applied only

after the setting of the current threshold in order to allow

smooth changes of peak current.

The formula that defines the total ripple current over the

buck inductor is also hereby reported:

(V

V

I

BUCK

pkpk

T

OFF

In the formula above, T

time, V

is the LED voltage feedback sensed at the

LED

LED

L

BUCK

OFF

NCV78825 VLEDx pin and L

value. The parameter T

OFF

× V

)

DIODE

T

represents the buck switch off

is the buck inductance

BUCK

is programmable by SPI

COIL

V

COIL

BUCK

(eq. 2)

off

L

(BUCKx_TOFF[4:0] register), with values related to Table

12. In order to achieve a constant ripple current value, the

device varies the T

V

sensed at the device pin, according to the selected

COIL

factor T

OFF

× V

COIL

time inversely proportional to the

OFF

.

As a consequence to the constant ripple control and

variable off time, the buck switching frequency depends on

the boost voltage and LED voltage in the following way:

Figure 10. Buck Regulator Controlled

Average Current

f

BUCK

(V

BOOST

V

V

BOOST

LED

)

T

If the offset cancelation of the peak current comparator is

not disabled by BUCKx_OFF_CMP_DIS bit, the inductor

Toff = constant

Toff = constant

Figure 11. Peak Current Comparator Offset Cancelation

The LED average current in time (DC) is equal to the buck

time average current. Therefore, to achieve a given LED

current target, it is sufficient to know the buck peak current

and the buck current ripple. A rule of thumb is to count a

minimum of 50% ripple reduction by means of the capacitor

C

and this is normally obtained with a low cost ceramic

BUCK

component ranging from 100 nF to 470 nF (such values are

1

OFF

(V

BOOST

V

V

BOOST

LED

V

)

COIL

T

V

off

COIL

peak current will vary from cycle−to−cycle as depicted on

Figure 11.

Toff = constant

Typical LED current

2x Peak current comparator offset

Fixed peak level

typically used at connector sides anyway, so this is included

in a standard BOM). The use of C

is a cost effective

BUCK

way to improve EMC performances without the need to

increase the value of L

, which would be certainly a far

BUCK

more expensive solution. The following figure reports a

typical example waveform:

(eq. 3)

www.onsemi.com

18

Page 19

NCV78825

Figure 12. LED Current AC Components Filtered out by Output Impedance (Oscilloscope Snapshot)

SW Compensation of the Buck Current Accuracy

In order to ensure buck current accuracy as specified in

Table 12, set of constants trimmed during manufacturing

process is available. Microcontroller should use them in the

following way:

To reach ±9 % accuracy (±7 % for Range 5) over whole

temperature operating range:

• All ranges: BUCKx_ISENS_TRIM[6:0] =

BUCKx_ISENS_RNG[6:0]

• BUCKx_ISENS_RNG[6:0] is trimming constant for

the highest current range (Range 5) at hot temperature

• BUCKx_ISENS_RNG[6:0] constant is loaded into

BUCKx_ISENS_TRIM[6:0] register automatically

after the reset of the device

To reach ±7 % accuracy over whole temperature operating

range:

• BUCKx_ISENS_Dx[3:0] registers, meaning delta of

the trimming constant with respect to the higher current

range at hot temperature, have to be used. Trimming

constant for the particular range at hot temperature can

be then calculated as:

• Range 5:

BUCKx_R5_trim_hot = BUCKx_ISENS_RNG[6:0],

• Range 4:

BUCKx_R4_trim_hot = BUCKx_ISENS_RNG[6:0]

+ BUCKx_ISENS_D4[3:0],

• Range 3:

BUCKx_R3_trim_hot = BUCKx_ISENS_RNG[6:0]

+ BUCKx_ISENS_D4[3:0] +

BUCKx_ISENS_D3[3:0],

• Range 2:

BUCKx_R2_trim_hot = BUCKx_ISENS_RNG[6:0]

+ BUCKx_ISENS_D4[3:0] +

BUCKx_ISENS_D3[3:0] +

BUCKx_ISENS_D2[3:0],

• Range 1:

BUCKx_R1_trim_hot = BUCKx_ISENS_RNG[6:0]

+ BUCKx_ISENS_D4[3:0] +

BUCKx_ISENS_D3[3:0] +

BUCKx_ISENS_D2[3:0] +

BUCKx_ISENS_D1[3:0],

Where delta of the trimming constant

BUCKx_ISENS_Dx[3:0] is signed, coded as two’s

complement. Range of this constant is decadic <−8; 7>,

binary <1000; 0111>.

Calculated trimming constant of selected range (y) has to

be then written into trimming SPI register:

BUCKx_ISENS_TRIM[6:0] = BUCKx_Ry_trim_hot

To reach ±4 % accuracy over whole temperature operating

range:

• In addition to BUCKx_ISENS_Dx[3:0] registers, the

BUCK_ISENS_TCx[3:0] registers, meaning

temperature coefficient for the appropriate range, have

to be used. Trimming value for a certain temperature

can be then calculated as:

• Range 5:

BUCK1_R5_trim = BUCK1_R5_trim_hot

× (Tj – Thot) + kQ × (Tj – Thot)2,

+ k

L1

BUCK2_R5_trim = BUCK2_R5_trim_hot

× (Tj – Thot) + kQ × (Tj – Thot)

+ k

L3

2

• Range 4:

BUCK1_R4_trim = BUCK1_R4_trim_hot

× (Tj – Thot) + kQ × (Tj – Thot)2,

+ k

L1

BUCK2_R4_trim = BUCK2_R4_trim_hot

× (Tj – Thot) + kQ × (Tj – Thot)

+ k

L3

2

• Range 3:

BUCK1_R3_trim = BUCK1_R3_trim_hot

× (Tj – Thot) + kQ × (Tj – Thot)2,

+ k

L1

BUCK2_R3_trim = BUCK2_R3_trim_hot

× (Tj – Thot) + kQ × (Tj – Thot)

+ k

L3

2

• Range 2:

BUCK1_R2_trim = BUCK1_R2_trim_hot

× (Tj – Thot) + kQ × (Tj – Thot)2,

+ k

L0

BUCK2_R2_trim = BUCK2_R2_trim_hot

× (Tj – Thot) + kQ × (Tj – Thot)2,

+ k

L2

• Range 1:

BUCK1_R1_trim = BUCK1_R1_trim_hot

× (Tj – Thot) + kQ × (Tj – Thot)2,

+ k

L0

BUCK2_R1_trim = BUCK2_R1_trim_hot

× (Tj – Thot) + kQ × (Tj – Thot)

+ k

L2

Where buck temperature coefficient

BUCK_ISENS_TCx[3:0] is signed, coded as two’s

complement. Range of this constant is decadic <−8; 7>,

binary <1000; 0111>

2

www.onsemi.com

19

Page 20

NCV78825

• k

is linear coefficient for each current range

Lx

calculated:

k

= (BUCK_ISENS_TCx[3:0] –

Lx

k

(200°C)2)/(−200°C) [code/°C]

Q x

• k

is quadratic constant for all current ranges:

Q

k

= 1.2 × 10

Q

−4

[code/(°C)2]

• Tj is junction temperature in °C calculated from

VTEMP[7:0] SPI register value according to the

equation defined in chapter ADC: Device Temperature

ADC: V

TEMP

• Thot temperature is constant equal to 155°C

Calculated trimming constant of selected range (y) has to

be then written into trimming SPI register:

VBOOST

supply

C

M3V

VBOOSTM3V VBOOST

VBOOSTM3V

reg.

BUCKx_ISENS_TRIM[6:0] = BUCKx_Ry_trim

The BUCKx_ISENS_TRIM[6:0] SPI register allows

compensation of the peak current app. in range ±40 % from

actual value according to the following equation:

IBUCKx = (ITHRx_000 +

δITHRx × BUCKx_VTHR[8:0]) × (1 + 0.4 × (

(BUCKx_ISENS_TRIM[6:0] − 63)/63)),

Where ITHRx_000 is current for VTHR code 0 in ITHRx

range (see Table 12), δITHRx code step in range ITHRx

(see Table 12).

The complete buck circuit diagram follows:

VINBCKx

POWER STAGE

Driver

HSVt

cmp

Digital

Control

Zero Cross Detector

Isense/OC /

OVD

Constant Ripple

Control

Figure 13. Buck Regulator Circuit Diagram

The zero−cross−detection (ZCD) comparator is

implemented for the case when VLED is low (< 1.8 V typ.)

to ensure proper Toff time termination just at the moment

when the coil current decreases to zero (boundary

conduction mode).

LBCKSWx

ZCD

LSFETx

GNDSx

VLEDx

L

M

Dbulk

LED string

C

ZCD is also used in normal buck mode when LS switch is

functional for proper determination of LS switch activation

and also deactivation when LS switch should be disabled in

reverse buck current mode.

www.onsemi.com

20

Page 21

NCV78825

HSVt Comparator

The HSVt comparator senses the gate voltage of the HS

switch and is used together with ZCD comparator for proper

activation of the LS switch. The comparator indicates that

gate voltage of the HS switch is at its Vt voltage, so it is safe

to turn LS switch on without risk of cross−current from

VBOOST/VINBCKx to ground.

Over Current Protection

Being a current regulator, the NCV78825 buck is by

nature preventing overcurrent in all normal situations.

However, in order to protect the system from overcurrent

even in case of failures, protection mechanism is available.

This protection is based on internal sensing over the buck

switch: when the peak current rises above the limit (situated

above OCDRx level, see Table 12), an internal counter starts

to increment at each period, until the count written in

BUCK_OC_OCCMP_THR[1:0] + 1 is attained. The

counter is reset if the buck channel is disabled and also at

each dimming cycle. From the moment the count is reached

onwards, the buck is kept continuously off, until the SPI

error flag OCLEDx is read. After reading the flag, the buck

channel “x” is automatically re−enabled and will try to

regulate the current again.

Over Voltage Detector

The OVD comparator ensures switching ON the HS

switch in case, that LBCKSWx pin is externally overdriven

over the VINBCKx potential. This feature prevents possible

HS switch bulk current and associated power loss or even

latch−up.

LS pre−driver

The LS pre−driver drives external NMOS device that is

performing synchronous rectification. The main advantage

is more efficient buck performance by minimizing voltage

drop across the flyback diode. The pre−driver is supplied

from VDRIVE pin, so its output is either switched to

VDRIVE or to GNDSx based on the required state of the LS

switch.

Implemented pull−down resistor ensures off state of the

LS switch in case that there is no supply of the device.

The LS pre−driver also contains the output voltage

monitor, the comparator indicating that LS switch gate

voltage is below a certain threshold voltage. The switching

on of the LS driver (LS pre−driver output is switched to

VDRIVE) is in normal continuous buck mode determined

by ZCD or HSVt comparator, the faster event activates the

LS switch.

The different buck modes and corresponding LS switch

functionality is implemented as follows:

• Buck output current discontinuous mode,

(VLED>VLED_LMT, LSx_IREV_NOCTRL = 0) the

LS driver is switched off as soon as the voltage drop

across the LS switch rises above ZCD threshold and

stays off till end of the corresponding Toff period

• Buck output current discontinuous mode,

(VLED>VLED_LMT, LSx_IREV_NOCTRL = 1) the

LS driver stays on till end of the Toff period regardless

of the ZCD state. The maximum buck output reverse

current (LS_IREV) is not sensed by the chip. It is

responsibility of application to guarantee that the

current will never exceed the specified value

• VLED_LOW is active,

(VLED<VLED_LMT, LSx_VLEDLOW_ENA = 0) the

LS driver is deactivated immediately, the bulk diode of

the LS switch is working as a flyback diode

• VLED_LOW is active,

(VLED<VLED_LMT, LSx_VLEDLOW_ENA = 1) the

LS driver stays functional like in case of high VLED

voltage (VLED>VLED_LMT)

• LS driver is disabled (LSx_DRV_ENA = 0), the LS

pre−driver output is switched to GNDSx, the LS switch

is kept off

Non−overlap Control of HS and LS Switches

The Non−overlap time is controlled in such a way, that HS

switch is activated just at the moment when gate voltage of

the LS switch is below its threshold voltage still with some

safety non−overlap time (see Table 13 for details). The

different non−overlap times can be selected by LS

non−overlap mode selection SPI bits:

• Adaptive mode (LSx_NO_MD[1:0] = “00” or “01”),

the switching off of the LS driver and switching on of

the HS driver is controlled by the self−adaptation

circuitry. This circuitry ensures, that the HS switch is

switched on just at the moment when gate voltage of

the LS FET passes through a LS_VT threshold when

the LS FET is surely off.

During settling time, the LS FET can be switched off

earlier than in balanced state, but the LS FET on time is

corrected for the next buck period in such a way, that

the balanced state should be reached.

During settling time, the LS FET can be switched off

later than in balanced state, but the LS FET on time is

corrected for the next buck period in such a way, that

the balanced state should be reached. As a

consequence, the Toff time must be extended just for

this buck period to prevent the cross−current

• Fixed mode (LSx_NO_MD[1:0] = “10” or “11”), the

switching off of the LS driver and switching on of the

HS driver is controlled by constant time as fixed

percentage of Toff time regardless of the LS FET

parasitics and switch−off time. In case of improper

application setup, the fixed non−overlap time can be too

short for given Toff time. In such case Toff time is

automatically extended just to prevent cross−current

(LS switch is still on, but HS switch should be already

switched on)

www.onsemi.com

21

Page 22

LBCKSW

I

COIL

HSVt_CMP

ZCD

HS_ON

LS_ON

NCV78825

T

OFF

LS_vt

Figure 14. Adaptive HS/LS Non-overlap Control

Paralleling the Bucks for Higher Current Capability

Different buck channels can be paralleled at the module

output (after the buck inductors) for higher current

capability on a unique channel, summing up together the

individual DC currents.

The Buck channels can be configured to a master−slave

synchronization mode by SPI bit BUCK_SYNC set to “1”.

Then, the Buck 1 performs as in the normal mode, the

Buck 2 “ON” phase starts when Buck1 “ON” phase finishes

(Buck 1 peak current reached) and also Buck 2 “OFF” phase

is synchronized with this signal from the master (Buck 2

Toff generator is not used). Only adaptive non−overlap

control for Buck 2 is allowed (LS2_NO_MD[1:0] = “00” or

“01”). If fixed non−overlap is set (LS2_NO_MD[1:0] =

“10” or “11”) then LS2_NO_MD[1:0] = “01” is set in the

device automatically. The duty cycle has to be less than 50%

for proper synchronous operation. This mode of operation is

suitable for further improvement of EMC performance, but

for the cost of worse Buck 2 average current accuracy.

Dimming

The NCV78825 supports both analog and digital

dimming (or so called PWM dimming). Analog dimming is

performed by controlling the LED amplitude current during

operation. This can be done by means of changing the peak

current level and/or the T

OFF

× V

constants by SPI

COIL

commands (see Buck Regulator section).

In this section, only the PWM dimming is described as this

is the preferred method to maintain the desired LED color

temperature for a given current rating. In PWM dimming,

the LED current waveform frequency is constant and the

duty cycle is set according to the required light intensity. In

Wait for LS_vt – Toff extended

order to avoid the beats effect, the dimming frequency

should be set at “high enough” values, typically above

300 Hz.

PWM dimming is controlled externally by means of

LEDCTRLx inputs.

External Dimming

The two independent control inputs LEDCTRLx handle

the dimming signals for the related channel “x”. In external

dimming, the buck activation is transparently linked to the

logic status of the LEDCTRLx pins. The only difference is

the controlled phase shift of typical 5.5 μs (see

BUCKx_SW_DEL parameter in Table 14) that allows

synchronized measurements of the VLEDx pins via the

ADC (see dedicated section for more details). As the phase

shift is applied both to rising edges and falling edges, with

a very limited jitter, the PWM duty cycle is not affected.

Apart from the phase shift and the system clock OSC10M,

there is no limitation to the PWM duty cycle values or

resolutions at the bucks, which is a copy of the reference

provided at the inputs.

ZOOM: buck inductor switching current

DIM_DUT = DIM_TON / DIM_T = DIM_T

DIM_T

ON

DIM_T

Figure 15. Buck Current Digital or PWM Dimming

ON

x F

www.onsemi.com

22

Page 23

NCV78825

ADC

General

The built−in analog to digital converter (ADC) is an 8−bit

capacitor based successive approximation register (SAR).

This embedded peripheral can be used to provide the

following measurements to the external Micro Controller

Unit (MCU):

• VBOOST voltage: sampled at the VBOOST pin

• VDD voltage: sampled at the VDD pin

• VLED1ON, VLED2ON voltages

• VLED1 and VLED2 voltages

• VTEMP measurement (chip temperature)

The internal NCV78825 ADC state machine samples all

the above channels automatically, taking care for setting the

analog MUX and storing the converted values in memory.

The external MCU can readout all ADC measured values via

the SPI interface, in order to take application specific

decisions. Please note that none of the MCU SPI commands

interfere with the internal ADC state machine sample and

conversion operations: the MCU will always get the last

available data at the moment of the register read.

VDDsample & convert

V

sample & convert

BOOST

Update LED_SEL_DUR count;

When counter ripples, trigger

VLEDx interrupt for once

V

sample & convert

TEMP

V

sample & convert

BOOST

points marked with a rhombus, with a minimum cadence

corresponding to the number of the elapsed ADC sequences

(forced interrupt). In formulas:

T

VLEDx_INT_forced

LED_SEL_DUR[8 : 0] T

ADC_SEQ

(eq. 4)

In general, prior to the forced interrupt status, the

VLEDxON ADC interrupts are generated when a falling

edge on the control line for the buck channel “x” is detected

by the device. In case of external dimming, this interrupt

start signal corresponds to the LEDCTRLx falling edge

together with a controlled phase delay (Table 14). The

purpose of the phase delay is to allow completion the

ongoing ADC conversion before starting the one linked to

the VLEDx interrupt: if at the moment of the conversion

LEDCTRLx pin is logic high, then the updated registers are

VLEDxON[7:0] and VLEDx[7:0]; otherwise, if

LEDCTRLx pin is logic low, the only register refreshed is

VLEDx[7:0]. This mechanism is handled automatically by

the NCV78825 logic without need of intervention from the

user, thus drastically reducing the MCU cycles and

embedded firmware and CPU cycles overhead that would be

otherwise required.

To avoid loss of data linked to the ADC main sequence,

one LED channel is served at a time also when interrupt

requests from both channels are received in a row and a full

sequence is required to go through to enable a new interrupt

VLEDx. In addition, possible conflicts are solved by using

a defined priority (channel pre−selection). Out of reset, the

default selection is given to channel “1”. Then an internal

flag keeps priority tracking, toggling at each time between

channels pre−selection. Therefore, up to two dimming

periods will b e required to obtain a full measurement update

of the two channels. This is not considered however a

limitation, as typical periods for dimming signals are in the

order of 1 ms period, thus allowing very fast failure

detection.

A flow chart referring to the ADC interrupts is also

displayed (see Figure 17).

Figure 16. ADC Sample and Conversion

Main Sequence

Referring to the figure above, the typical rate for a full

SAR plus digital conversion per channel is 8 μs (T able 10).

For instance, each new VBOOST ADC converted sample

occurs at 16 μs typical rate, whereas for both the VBB and

VTEMP channel the sampling rate is typically 32 μs, that is

to say a complete cycle of the depicted sequence. This time

is referred to as TADC_SEQ.

If the SPI setting LED_SEL_DUR[8:0] is not zero, then

interrupts for the VLEDx measurements are allowed at the

www.onsemi.com

23

Page 24

NCV78825

LEDx sample & convert

Toggle channel “x” selection

NO

Interrupts Enabled

NO

Proceed to next step in the

Figure 17. ADC VLEDx Interrupt Sequence

YES

V

second channel do not serve

immediately and complete

VLEDx

Synchronization

signal?

YES

In case of interrupt on

the ADC sequence first

ADC sequence

All NCV78825 ADC registers data integrity is protected

by ODD parity on the bit 8 (that is to say the 9th bit if

counting from the least significant bit named “0”). Please

refer to the SPI map section for further details.

Logic Supply Voltage ADC: V

DD

The logic supply voltage is sampled at VDD pin. The

(8−bit) conversion ratio is 4/255 (V/dec) = 0.0157 (V/dec)

typical. The converted value can be found in the SPI register

VDD[7:0], protected with ODD parity bit.

Boost Voltage ADC: V

BOOST

This measure refers to the boost voltage at the VBOOST

pin, with an 8 bit conversion ratio of 70/255 (V/dec) = 0.274

(V/dec) typical, inside the SPI register VBOOST[7:0]. The

value is protected by ODD parity bit. This measurement can

be used by the MCU for diagnostics and booster control loop

monitoring.

Device Temperature ADC: V

TEMP

By means of the VTEMP measurement, the MCU can

monitor the device junction temperature (T

) over time. The

J

conversion formula is:

TJ (VTEMP[7 : 0] 50.5)0.805

(eq. 5)

VTEMP[7:0] is the value read out directly from the

related 8bit−SPI register (please refer to the SPI map). The

value is also used internally by the device for the thermal

warning and thermal shutdown functions. More details on

these two can be found in the dedicated sections in this

document. The value is protected by ODD parity bit.

LED String Voltages ADC: V

LEDx

, V

LEDxON

The voltage at the pins VLEDx (1, 2) is measured. There

are 4 ranges available, that can be selected by means of

ADC_VLEDx_RNG_SEL[1:0] register, to obtain higher

resolution for LED voltage measurement.

Conversion ratios in dependency on selected range are:

0x0: 70/255 (V/dec) = 0.274 (V/dec)

0x1: 50/255 (V/dec) = 0.196 (V/dec)

0x2: 40/255 (V/dec) = 0.157 (V/dec)

0x3: 30/255 (V/dec) = 0.118 (V/dec)

This information, found in registers VLEDxON[7:0] and

VLEDx[7:0], can be used by the MCU to infer about the

LED string status, for example, individual shorted LEDs. As

for the other ADC registers, the values are protected by

ODD parity.

Please note that in the case of constant LEDCTRLx inputs

and no dimming (in other words dimming duty cycle equals

to 0% or 100%) the VLEDx interrupt is forced with a rate

equal to, given in the ADC general section. This feature can

be exploited by MCU embedded algorithm diagnostics to

read the LED channels voltage even when in OFF state,

before module outputs activation (module startup

pre−check).

www.onsemi.com

24

Page 25

NCV78825

DIAGNOSTICS

The NCV78825 features a wide range of embedded

diagnostic features. Their description follows. Please also

refer to the previous SPI section for more details.

w Thermal Warning:

This mechanism detects a user−programmable junction

temperature which is in principle close, but lower, to

the chip maximum allowed, thus providing the

information that some action (power de−rating) is

required to prevent overheating that would cause

Thermal Shutdown. A typical power de−rating

technique consists in reducing the output dimming duty

cycle in function of the temperature: the higher the

temperature above the thermal warning, the lower the

duty cycle. The thermal warning flag (TW) is given in

status register 0x16 and is latched. When VTEMP[7:0]

raises to or above THERMAL_WARNING_THR[7:0]

threshold, the TW flag is set. At power up the default

thermal warning threshold is typically 159°C (SPI code

179)

w Thermal Shutdown:

This safety mechanism intends to protect the device

from damage caused by overheating, by disabling the

both buck channels. The diagnostic is displayed per

means of the TSD bit in status register 0x16 (latched).

Once occurred, the thermal shutdown condition is

exited when the temperature drops below the thermal

warning level, thus providing hysteresis for thermal

shutdown recovery process. Outputs are re−enabled

automatically if BUCKx_TSD_AUT_RCRV_EN = 1,

respectively can be re−enabled by rising edge on

BUCKx_EN if BUCKx_TSD_AUT_RCRV_EN = 0.

The application thermal design should be made as such

to avoid the thermal shutdown in the worst case

conditions. The thermal shutdown level is not user

programmable and is factory trimmed (see ADC_TSD

in Table 10)

w SPI Error:

In case of SPI communication errors the SPIERR bit in

status register 0x16 is set. The bit is latched. For more

details, please refer to section “SPI protocol: framing

and parity error”

w Open LEDx String:

Individual open LED diagnostic flags indicate whether

the “x” string is detected open. The detection is based

on a counter overflow of typical 50 μs when the related

channel is activated. Both OPENLED1 and

OPENLED2 flags (latched) are contained in status

register 0x15. Please note that the open detection does

not disable the buck channel(s)

w Short LEDx String:

A short circuit detection is available independently for

each LED channel per means of the flag SHORTLEDx

(latched, status register 0x15). The detection is based

on the voltage measured at the VLEDx pins via a

dedicated internal comparator: when the voltage drops

below the VLED_LMT threshold (1.8 V typ. , see

Table 11) the related flag is set. Note that the detection

is active when buck channel is enabled and inactive

during the 1

of low VLEDx voltage the Toff time is terminated

immediately when the inductor current reaches zero.

This improves the dimming behavior via external short

switches (pixel control)

st

switching period after enabling. In case

w Overcurrent on Channel x:

This diagnostics protects the LEDx and the buck

channel x electronics from overcurrent. As the

overcurrent is detected, the OCLEDx flag (latched,

status register 0x15) is raised and the related buck

channel is disabled. More details about the detection

mechanisms and parameters are given in section “Buck

Overcurrent Protection”

w Buckx Status:

Register BUCKx_STATUS shows the actual status of

Buckx output. When BUCKx_STATUS is 1, the

corresponding output regulates current to the LED

w LEDCTRLx Pin Status:

SPI registers LED1VAL resp. LED2VAL indicate the

actual logic level of the debounced LEDCTRLx pins.

These signals follow the output of 200 ns digital

debouncers implemented on LEDCTRLx pins

w Buckx Running at Minimum TON Time:

Register BUCKx_MIN_TON (latched) indicates that

minimal TON time is detected on the corresponding

channel. It is clear by read flag. This information can be

used for detection of transition period during which the

BUCKx output current decreases due to the change of

BUCKx_VTHR code or BUCKx_ISENS_THR range

w Buckx TON Time Duration:

SPI register BUCKx_TON_DUR[7:0] reflects the last

measured Buckx TON time (1LSB = 200 ns) on the

corresponding channel. When Buckx runs with TON

time < typ. 200 ns, the BUCKx_TON_DUR[7:0] SPI

register returns value 0x00. When Buckx is stopped, the

BUCKx_TON_DUR[7:0] register keeps the last

measured TON time

w HW Reset:

The out of reset condition is reported through the HWR

bit (latched). This bit is set only at each Power On

Reset (POR) and indicates the device is ready to

operate

Each diagnostic latched flag is cleared by read.

A short summary table of the main diagnostic bits related

to the LED outputs follows.

www.onsemi.com

25

Page 26

NCV78825

Table 18. LED OUTPUTS DIAGNOSTIC SUMMARY

Diagnose

Flag Description

TW Thermal Warning SPI register programmable Not Disabled

TSD Thermal Shutdown Factory trimmed Disabled (automatically re−enabled

SPIERR SPI error See SPI section Not Disabled Yes

OPENLEDx LED string open circuit Buck on time > TON_OPEN Not Disabled Yes

SHORTLEDx LED string short circuit VLEDx < VLED_LMT Not Disabled Yes

OCLEDx LED string overcurrent Ibuckx > OCDR{1..5} Disabled Yes

Transition priority:

(0) − highest

(1)

(2)

(3) − lowest

Detection level LED Output Latched

(if no TSD, otherwise disabled)

when temp falls below TW and

BUCKx_TSD_AUT_RCVR_EN = 1)

Mode = RESET (0)

OFF

LED is off

TSD = 1 (1)

Yes

Yes

OCLEDx = 1 or

BUCKx_EN = 0 (2)

BUCKx_TSD_AUT_RCVR_EN = 1 or

rising edge on BUCKx_EN detected) (3)

BUCKx_TSD_AUT_RCVR_EN = 1 or

rising edge on BUCKx_EN detected) and

(OCLEDx = 1 or BUCKx_EN = 0) (2)

OCLEDx = 0 and

BUCKx_EN = 1 (2)

NORMAL mode: LED is on if LEDCTRLx = 1

FSO/STANDALONE mode: LED is on

RECOVERY

LED is off

VTEMP < THERMAL EARNING_THR (1)

DIMMING

TSD = 1 (1)

TSD = 1 (1)

TSD

LED is off

Figure 18. LED Dimming State Diagram

www.onsemi.com

26

Page 27

FUNCTIONAL MODE DESCRIPTION

Transition condition (priority level):

action executed when transition is performed

(0) − highest

(1)

(2)

(3) − lowest

NCV78825

POR (0)

RESET

SPI disabled

Dimming disabled

HWR := 1

RSTB = 0 and

(FSO_MD = 000 or

001 or 110 or 111) (1)

RSTB = 1 (1)

150μs timeout expired (3)

SPI pre−load from OTPs when

FSO_MD = 001 or 100 or 101

RSTB = 0 and

(FSO_MD = 010 or

011 or 100 or 101) and

OTP_CUST_LOCK = 1 (2)

SPI pre−load from OTPs

FSO := 1

INIT

SPI disabled

Dimming disabled

OTP refresh ongoing

150μs timeout expired

(

FSO_MD = 110 or111) and

OTP_CUST_LOCK = 1 (2)

SPI pre−load from OTPs

NORMAL

SPI enabled

Dimming: LEDCTRLx

(FSO_MD = 000 or 001) (1)

RSTB = 0 (1)

FSO := 1

FSO_MD = 000 or 001 (2)

RSTB = 1 or

RSTB = 0 (1)

STANDALONE

SPI disabled when

FSO_MD = 110

Dimming: BUCKx_EN

FSO

SPI disabled when

FSO_MD = 010 or 100

Dimming: BUCKx_EN

Figure 19. Functional Modes State Diagram

Reset

Asynchronous reset is caused either by POR (POR always

causes asynchronous reset − transition to reset state) or by

falling edge on RSTB pin (in normal/stand−alone mode,

when FSO_MD[2:0] = 000 or 001 or 110 or 111).

www.onsemi.com

Init and Normal mode

Normal mode is entered through Init state after internal

delay of 150 μs. In Init state, OTP refresh is performed. If

OTP bits for FSO_MD[2:0] register and OTP Lock Bit are

programmed, transition to FSO/SA mode is possible.

27

Page 28

NCV78825

e

RSTB in normal or stand−alone mode

FSO/Stand−Alone Mode

FSO (Fail−Safe Operation)/Stand−Alone modes can be

used for two main purposes:

• Default power−up operation of the chip (Stand−Alone

functionality without external microcontroller or

preloading of the registers with default content for

default operation before microcontroller starts sending

SPI commands for chip settings)

• Fail−Safe functionality (chip functionality definition in

fail−safe mode when the external microcontroller

functionality is not guaranteed)

FSO/stand−alone function is controlled according to

Table 19. Entrance into FSO/Stand−alone mode is possible

only after customer OTP zapping when OTP Lock Bit is set.

After FSO mode activation, the FSO bit in status register

is set. FSO register is cleared by read register.

When FSO/Stand−Alone mode is activated, content of the

following SPI registers is preloaded from OTP memory:

BUCK1_VTHR[8:1]

BUCK1_ISENS_THR[1:0]

BUCK2_VTHR[8:1]

BUCK2_ISENS_THR[1:0]

BUCK1_TOFF[4:0]

BUCK2_TOFF[4:0]

BUCK1_EN

BUCK2_EN

FSO_MD[2:0]

BUCK1_TSD_AUT_RCVR_EN

BUCK2_TSD_AUT_RCVR_EN

BUCK_OC_OCCMP_THR[1:0]

BUCKx_ISENS_TRIM[6:0] register is preloaded from

corresponding BUCKx_ISENS_RNG[6:0] register.

In FSO (entered via falling edge on RSTB pin) and

Stand−Alone modes, BUCK1_EN & BUCK2_EN are

controlled from SPI register map (SPI registers are updated

from OTP’s after entrance into these modes).

BUCK1_EN and BUCK2_EN are supposed to be set ‘1’

for the BUCKx operation in the FSO/stand−alone mode.

When control registers are pre−loaded from OTP’s after

POR and FSO mode is not entered (valid for FSO_MD[2:0]

= 100 or 101), BUCK1_EN and BUCK2_EN are kept

inactive (‘0’) until the first valid SPI operation is finished

(even in FSO mode) to avoid potential activation of buck

regulators immediately after POR (to prevent undefined

state of LEDCTRLx pins in case MCU leaves POR later than

NCV78825).

In FSO and Stand−Alone modes, the logic level at

LEDCTRLx pins is ignored and external PWM dimming

with LEDCTRLx pins is not available. The outputs can be

dimmed only by means of BUCKx_EN register.

Prior to entrance into FSO mode, low level on RSTB pin

always generates reset of digital. Falling edge on RSTB pin

may generate either entrance into FSO mode or reset in

dependency on FSO_MD[2:0] register value.

Once FSO mode is entered via falling edge on RSTB pin,

reset function of RSTB pin is blocked until FSO mode is

exited. FSO mode can be exited by the rising edge on RSTB

pin or by writing FSO_MD[2:0] = 000 or 001 (possible only

in FSO modes, where SPI control register update is allowed:

FSO_MD[2:0] = 011 or 101).

In stand−alone mode (FSO_MD[2:0] = 110 or 1 1 1), RSTB

has always reset functionality.

During entrance into FSO mode, value of FSO_MD[2:0]

SPI register (preloaded from OTP at power up only) is

latched into internal register and all FSO related functions

are then controlled according to it. The purpose is to avoid

the reset of the device when FSO mode is active and

FSO_MD[2:0] is changed to value corresponding to

stand−alone mode, where RSTB pin has reset functionality.

The internal register is cleared after POR or when FSO mode

is exited.

POR

(internal)

RSTB

POR

(internal)

RSTB

Normal mode (SPI possible)

Power−up

Possible OTP pre−load Possible OTP pre−load

RSTB in FSO mode

Normal mode (SPI possible)

Power−up

OTP pre−load OTP pre−load

Figure 20. RSTB Pin Functionality in Normal, Stand−alone and FSO Modes

www.onsemi.com

Normal mode (no SPI)

FSO mode

(SPI possible/no SPI)

28

Normal mode

Reset mod

FSO modeNormal mode

OTP pre−load

Page 29

NCV78825

Table 19. FSO MODES

FSO_MD[2:0]

000b = 0 FSO mode disabled, registers are loaded with safe value = 0x00h after POR, default

− After the reset, control registers are loaded with 0x00h value

− Entrance into FSO mode is not possible unless dedicated SPI write command to change FSO_MD[2:0] value is

sent

− RSTB pin has reset functionality

− LEDCTRLx pins are functional (buck enable/disable, external PWM dimming available)

001b = 1 FSO mode disabled, registers are loaded with data from OTP memory after POR

− After the reset, control registers are loaded with data stored in OTP memory (device’s OTP memory has to be

programmed, OTP Lock Bit has to be set). It reduces number of SPI transfers needed to configure the device

after the reset

− Entrance into FSO mode is not possible unless dedicated SPI write command to change FSO_MD[2:0] value is

sent

− RSTB pin has reset functionality

− LEDCTRLx pins are functional (buck enable/disable, external PWM dimming available)

010b = 2 FSO entered after falling edge on RSTB pin, registers are loaded with safe value = 0x00h except FSO_MD[2:0]

value after POR

− After FSO mode activation, control registers are loaded with data stored in OTP memory

− SPI register update (SPI write/read operation) in FSO mode is disabled (SPI write operation is blocked;

Diagnostig flags clearing of SPI registers is blocked; in case of invalid SPI frame, SPIERR flag is set)

− RSTB pin serves to enter/exit FSO mode

− LEDCTRLx pins are not functional (buck enable/disable only by means of BUCKx_EN SPI/OTP bits, external

PWM dimming not available)

011b = 3 FSO entered after falling edge on RSTB pin, registers are loaded with safe value = 0x00h except FSO_MD[2:0]

value after POR

− After FSO mode activation, control registers are loaded with data stored in OTP memory

− SPI register update (SPI write/read operation) in FSO mode is enabled

− FSO mode can be exited by writing FSO_MD[2:0] = 000 or 001

− RSTB pins serves to enter/exit FSO mode

− LEDCTRLx pins are not functional (buck enable/disable only by means of BUCKx_EN SPI/OTP bits, external

PWM dimming not available)

100b = 4 FSO entered after falling edge on RSTB pin, registers are loaded with data from OTP memory after POR

− After FSO mode activation, control registers are loaded with data stored in OTP memory