Page 1

NCV47721

LDO Regulator - Adjustable

Current Limit,

Diagnostic Features

3.3 V to 20 V

The NCV47721 LDO regulator with 200 mA output current is

designed for use in harsh automotive environments. The device has a

high peak input voltage tolerance and reverse input voltage, reverse

bias, overcurrent and overtemperature protections. The integrated

current sense feature (adjustable by resistor connected to CSO pin)

provides diagnosis and system protection functionality. The CSO pin

output current creates voltage drop across CSO resistor which is

proportional to output current. Extended diagnostic features in OFF

state are also available and controlled by dedicated input and output

pins.

Features

• Adjustable Output: 3.3 V to 20 V ±3% Output Voltage

• Output Current: up to 200 mA

• Enable Input (3.3 V Logic Compatible)

• Adjustable Current Limit: up to 300 mA

• Protection Features:

♦ Current Limitation

♦ Thermal Shutdown

♦ Reverse Input Voltage and Reverse Bias Voltage

• Diagnostic Features:

♦ Short To Battery (STB) and Open Load (OL) in OFF State

♦ Internal Components for OFF State Diagnostics

♦ Open Collector Flag Output

• AEC−Q100 Grade 1 Qualified and PPAP Capable

• These Devices are Pb−Free, Halogen Free/BFR Free and are RoHS

Compliant

www.onsemi.com

MARKING

DIAGRAM

14

14

1

(Note: Microdot may be in either location)

TSSOP−14

Exposed Pad

CASE 948AW

47721 = Specific Device Code

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

G = Pb−Free Package

NCV4

7721

ALYWG

G

1

ORDERING INFORMATION

See detailed ordering and shipping information in the package

dimensions section on page 14 of this data sheet.

Typical Applications

• Audio and Infotainment System

• Active Safety System

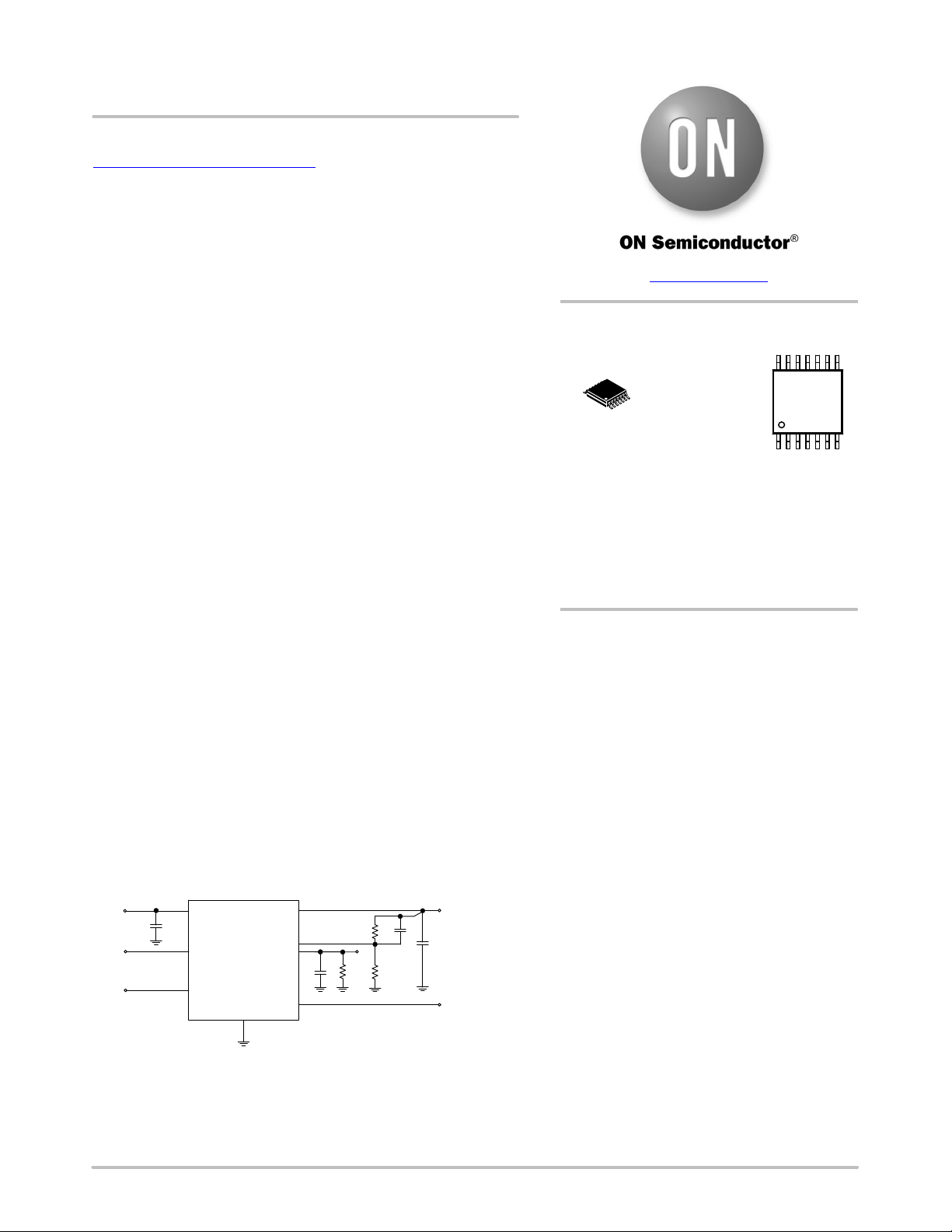

GND

ADJ

CSO

V

out

EF

V

C

in

1 µF

Diagnostic Enable Input

in

EN

NCV47721

DE

Cb*

- is optional for stability with ceramic output capacitor

Figure 1. Application Schematic

© Semiconductor Components Industries, LLC, 2015

September, 2019 − Rev. 1

C

CSO

1 µF

R1Cb*

To A /D

R

R

CSO

Error Flag Output (Open Collector)

10 mF

2

C

out

1 Publication Order Number:

NCV47721/D

Page 2

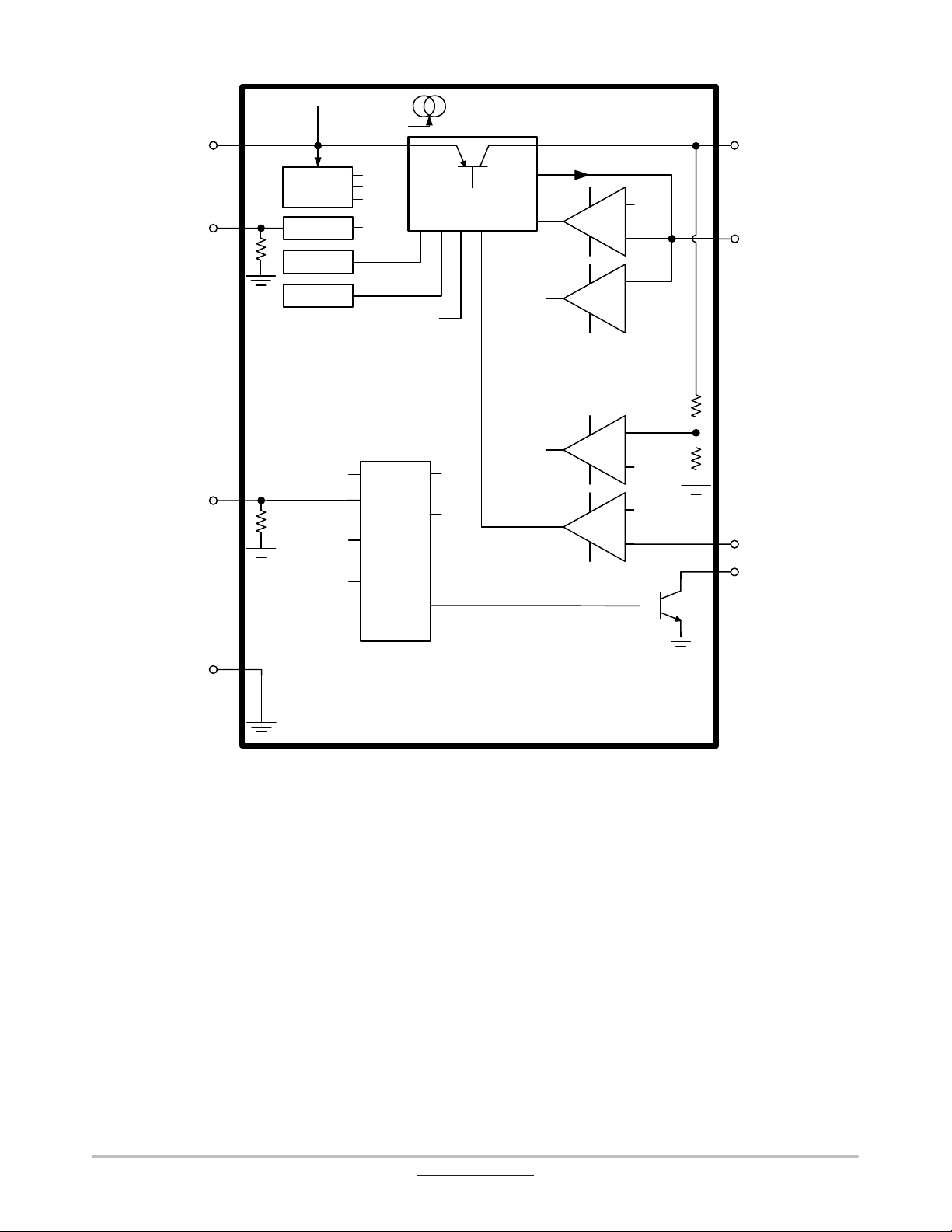

EN

DE

NCV47721

I

10 mA

PU

IPU_ON

V

in

V

EN

REF1

V

REF2

V

REF_OFF

EN

PD_ON

DIAGNOSTIC

CONTROL

LOGIC

PASS DEVICE

AND

CURRENT MIRROR

STB_OL_OFF

IPU_ON

PD_ON

R

PD_EN

780k

VOLTAGE

REFERENCE

ENABLE

SATURATION

PROTECTION

THERMAL

SHUTDOWN

R

PD_DE

780k

STB_OL_OFF

OC_ON

OC_ON

I

CSO

= I

out

/ 100

EA

V

REF2

+

2.55 V

−

+

0.95x

−

V

REF2

R

PD1

500k

+

−

+

V

REF_OFF

1.05 V

V

REF1

1.265 V

R

100k

PD2

−

V

out

CSO

ADJ

EF

GND

Figure 2. Simplified Block Diagram

www.onsemi.com

2

Page 3

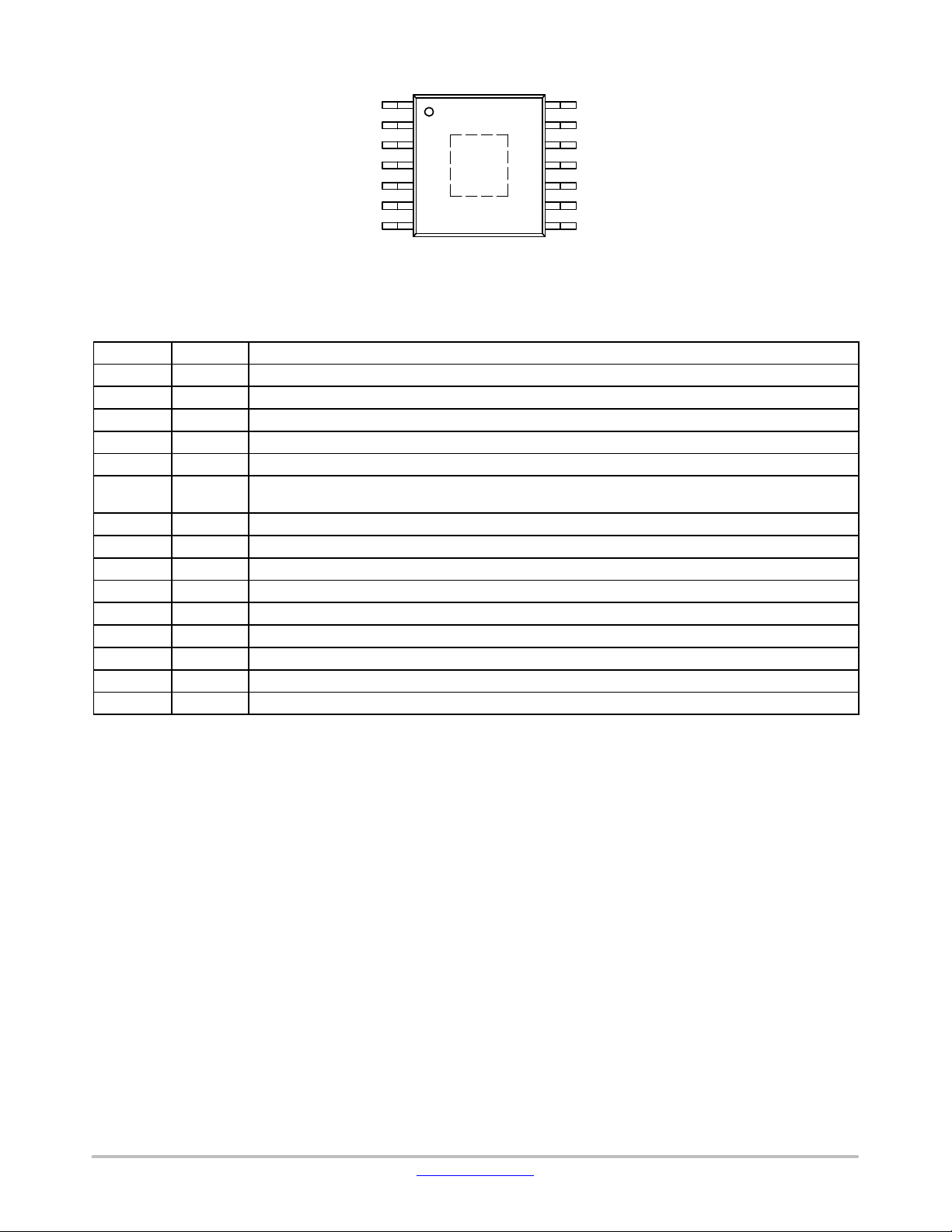

NCV47721

411

NC

NC

NC

GND

EN

CSO

V

in

EPAD

TSSOP−14 EPAD

Figure 3. Pin Connections (Top Views)

Table 1. PIN FUNCTION DESCRIPTION

Pin No. Pin Name Description

1 NC Not Connected, not internally bonded.

2 NC Not Connected, not internally bonded.

3 NC Not Connected, not internally bonded.

4 GND Power Supply Ground.

5 EN Enable Input; low level disables regulator. (Used also for OFF state diagnostics control.

6 CSO Current Sense Output, Current Limit setting and Output Current value information. See Application Section

7 V

8 V

9 ADJ Adjustable Voltage Setting Input. See Application Section for more details.

10 DE Diagnostic Enable Input.

11 EF Error Flag (Open Collector) Output. Active Low.

12 NC Not Connected, not internally bonded.

13 NC Not Connected, not internally bonded.

14 NC Not Connected, not internally bonded.

EPAD EPAD Exposed Pad is connected to Ground. Connect to GND plane on PCB.

in

out

for more details.

Power Supply Input.

Regulated Output Voltage.

NC

NC

NC

EF

DE

ADJ

V

out

www.onsemi.com

3

Page 4

NCV47721

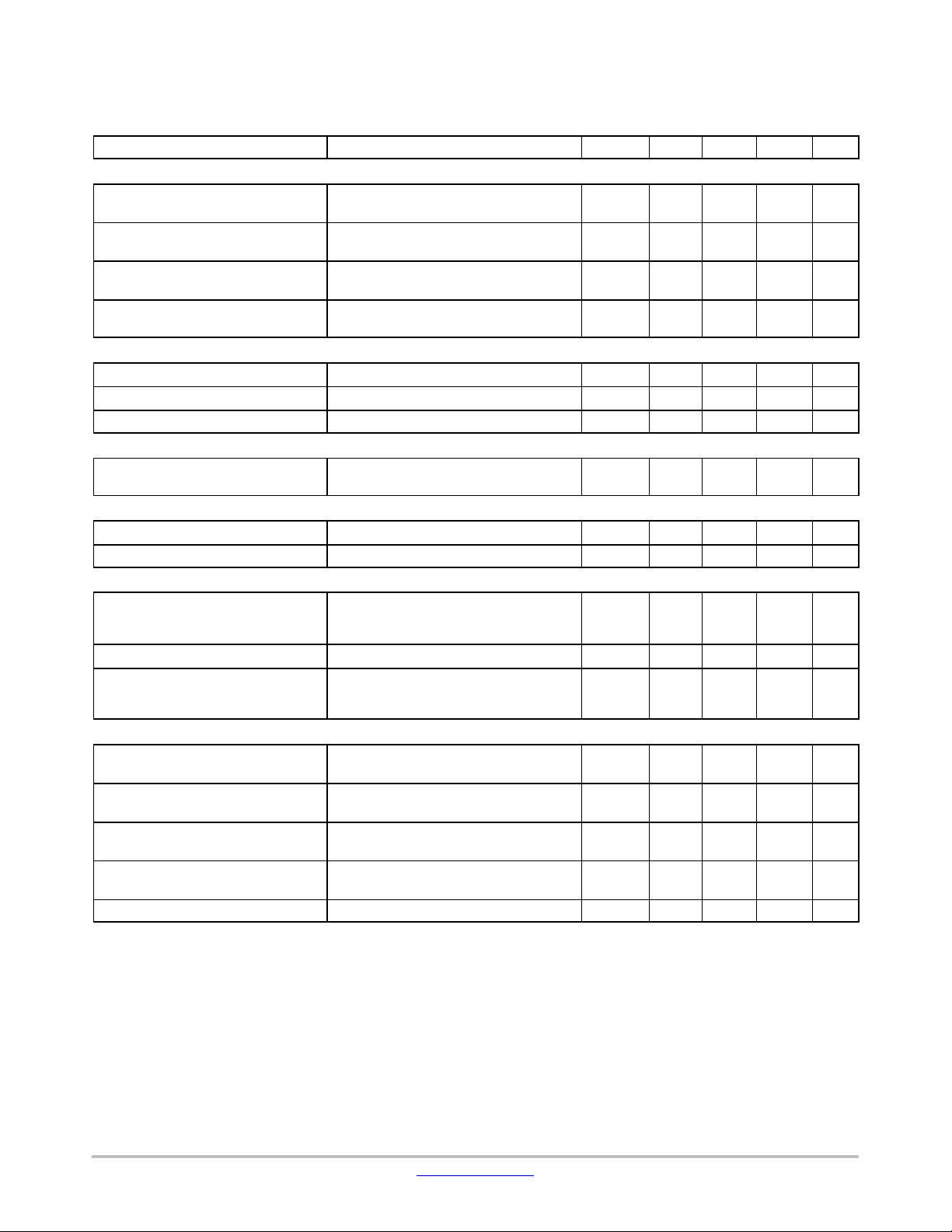

Table 2. MAXIMUM RATINGS

Rating Symbol Min Max Unit

Input Voltage DC V

Input Voltage (Note 1)

Load Dump − Suppressed

Enable Input Voltage V

ADJ Input Voltage V

CSO Voltage V

DE, EF Voltages VDE, V

Output Voltage V

Junction Temperature T

Storage Temperature T

U

ADJ

CSO

STG

in

s*

EN

EF

out

J

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality

should not be assumed, damage may occur and reliability may be affected.

1. Load Dump Test B (with centralized load dump suppression) according to ISO16750−2 standard. Guaranteed by design. Not tested in

production. Passed Class A according to ISO16750−1.

Table 3. ESD CAPABILITY (Note 2)

Rating

ESD Capability, Human Body Model ESD

2. This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per AEC−Q100−002 (JS−001−2010)

Field Induced Charge Device Model ESD characterization is not performed on plastic molded packages with body sizes < 50 mm

to the inability of a small package body to acquire and retain enough charge to meet the minimum CDM discharge current waveform

characteristic defined in JEDEC JS−002−2014.

Symbol Min Max Unit

HBM

Table 4. LEAD SOLDERING TEMPERATURE AND MSL (Note 3)

Rating

Moisture Sensitivity Level MSL 1 −

3. For more information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D

Symbol Min Max Unit

THERMAL CHARACTERISTICS (Note 4)

Rating

Thermal Characteristics (single layer PCB)

Thermal Resistance, Junction−to−Air (Note 5)

Thermal Reference, Junction−to−Lead (Note 5)

Thermal Characteristics (4 layers PCB)

Thermal Resistance, Junction−to−Air (Note 5)

Thermal Reference, Junction−to−Lead (Note 5)

4. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

5. Values based on copper area of 645 mm

2

(or 1 in2) of 1 oz copper thickness and FR4 PCB substrate. Single layer − according to JEDEC51.3,

4 layers − according to JEDEC51.7

Symbol Value Unit

R

θJA

R

ψJL

R

θJA

R

ψJL

Table 5. RECOMMENDED OPERATING RANGES

Rating Symbol Min Max Unit

Input Voltage (Note 6) V

Nominal Output Voltages V

Output Current Limit (Note 7) I

Junction Temperature T

Current Sense Output (CSO) Capacitor C

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond

the Recommended Operating Ranges limits may affect device reliability.

6. Minimum V

7. Corresponding R

= 4.4 V or (V

in

CSO

+ 0.5 V), whichever is higher.

out

is in range from 25.5 kW down to 850 W.

in

out_nom

LIM

J

CSO

−42 45 V

− 60

−42 45 V

−0.3 10 V

−0.3 7 V

−0.3 7 V

−1 40 V

−40 150 °C

−55 150 °C

−2 2 kV

°C/W

62.6

23.7

°C/W

44.1

16.8

4.4 40 V

3.3 20 V

10 300 mA

−40 150 °C

1 4.7

mF

V

2

due

www.onsemi.com

4

Page 5

NCV47721

Table 6. ELECTRICAL CHARACTERISTICS V

Max values are valid for temperature range −40°C v T

statistical correlation. Typical values are referenced to T

Parameter

= 13.5 V, VEN = 3.3 V, R

in

v +150°C unless noted otherwise and are guaranteed by test, design or

J

= 25°C (Note 8)

J

CSO

= 0 W, C

= 1 mF, Cin = 1 mF, C

CSO

= 10 mF, Min and

out

Test Conditions Symbol Min Typ Max Unit

REGULATOR OUTPUTS

Output Voltage (Accuracy %) (Note 9)

Vin = V

I

= 5 mA to 200 mA

out

Line Regulation (Note 9) Vin = V

I

= 5 mA

out

Load Regulation Vin = (V

I

= 5 mA to 200 mA

out

Dropout Voltage (Note 10) V

out_nom

V

DO

in_min

in_min

out_nom

= 5 V, I

= Vin − V

to 40 V

to (V

out_nom

+ 8.5 V)

out

out

+ 20 V)

= 200 mA

V

Reg

Reg

V

out

DO

line

load

−3 − +3

%

%

− 0.1 1.0

%

− 0.4 1.4

− 250 500 mV

DISABLE AND QUIESCENT CURRENTS

Disable Current

Quiescent Current, Iq = Iin − I

Quiescent Current, Iq = Iin – I

out

out

VEN = 0 V I

I

= 500 mA, Vin = (V

out

I

= 200 mA, Vin = (V

out

+ 8.5 V) I

out_nom

+ 8.5 V) I

out_nom

DIS

q

q

− 0.002 10

mA

− 0.35 1 mA

− 7.5 15 mA

CURRENT LIMIT PROTECTION

Current Limit

Vin = (V

=

V

0.9 x V

out

out_nom

+ 8.5 V),

out_nom

I

LIM

300 − − mA

PSRR & NOISE

Power Supply Ripple Rejection (Note 11)

f = 100 Hz, 0.5 V

p−p

Output Noise Voltage (Note 11) f = 10 Hz to 100 kHz, C

= 10 nF V

b

PSRR − 80 − dB

n

− 168 −

mV

rms

ENABLE

Enable Input Threshold Voltage

Logic Low (OFF)

Logic High (ON)

v

V

0.1 V

out

w

V

out

0.9 x V

out_nom(Vout_nom

= 5 V)

V

Enable Input Current VEN = 3.3 V I

Turn On Time from Enable ON to 90 % of V

I

= 100 mA, C

out

= 82 kW, R2 = 27 kW

R

1

= 10 nF,

b

out_nom

th(EN)

EN

t

on

0.99

−

1.8

1.9

2 8 20

− 1.6 −

−

2.31

V

mA

ms

OUTPUT CURRENT SENSE

CSO Voltage Level at Current Limit

CSO Transient Voltage Level

Output Current to CSO Current Ratio

(Notes 11 & 12)

Output Current to CSO Current Ratio

(Note 12)

CSO Current at no Load Current

= 0.9 x V

out

(V

C

I

out

V

(V

V

(V

V

= 5 V) R

out_nom

= 4.7 mF, R

CSO

pulse from 10 mA to 300 mA, tr = 1 ms

= 2 V, I

CSO

= 5 V)

out_nom

= 2 V, I

CSO

= 5 V)

out_nom

= 0 V, I

CSO

,

out_nom

out

out

out

= 1 kW

CSO

= 1 kW

CSO

= 1 mA to 10 mA

= 10 mA to 300 mA

= 0 mA, (V

out_nom

= 5 V)

V

CSO_I

V

CSO

I

out/ICSO

I

out/ICSO

I

CSO_off

2.448

lim

(−4%)

− − 3.3

−

(−5%)

−

(−5%)

− − 10

2.55 2.652

(+4%)

98 −

(+5%)

100 −

(+5%)

V

V

−

−

mA

V

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

performance may not be indicated by the Electrical Characteristics if operated under different conditions.

8. Performance guaranteed over the indicated operating temperature range by design and/or characterization tested at T

cycle pulse techniques are used during testing to maintain the junction temperature as close to ambient as possible.

9. Minimum input voltage V

10.Measured when the output voltage V

11.Values based on design and/or characterization.

is 4.4 V or (V

in_min

has dropped by 2% of V

out

+ 1 V) whichever is higher.

out_nom

from the nominal valued obtained at Vin = V

out_nom

[ TJ. Low duty

A

+ 8.5 V.

out

12.Not guaranteed in dropout.

www.onsemi.com

5

Page 6

NCV47721

Table 6. ELECTRICAL CHARACTERISTICS V

Max values are valid for temperature range −40°C v T

statistical correlation. Typical values are referenced to T

= 13.5 V, VEN = 3.3 V, R

in

v +150°C unless noted otherwise and are guaranteed by test, design or

J

= 25°C (Note 8)

J

CSO

= 0 W, C

= 1 mF, Cin = 1 mF, C

CSO

= 10 mF, Min and

out

Parameter UnitMaxTypMinSymbolTest Conditions

DIAGNOSTICS

Overcurrent Voltage Level Threshold

Short To Battery (STB) Voltage

Threshold in OFF state

Open Load (OL) Current Threshold

V

Vin = 4.4 V to 18 V, I

out_nom

= 5 V, R

= 1 kW

CSO

= 0 mA V

out

Vin = 4.4 V to 18 V I

in OFF state

Diagnostics Enable Threshold Voltage

Logic Low (OFF)

Logic High (ON)

Error Flag Low Voltage IEF = −1 mA V

V

OC

STB

OL

V

th(DE)

EF_Low

92 95 98 % of

V

CSO_

2 3 4 V

5 10 25 mA

0.99

−

1.8

1.9

−

2.31

− 0.04 0.4 V

Ilim

V

THERMAL SHUTDOWN

Thermal Shutdown Temperature

(Note 11)

= 5 mA, V

out

= 5 V T

out_nom

SD

150 175 195 °C

I

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

performance may not be indicated by the Electrical Characteristics if operated under different conditions.

8. Performance guaranteed over the indicated operating temperature range by design and/or characterization tested at T

cycle pulse techniques are used during testing to maintain the junction temperature as close to ambient as possible.

9. Minimum input voltage V

10.Measured when the output voltage V

11.Values based on design and/or characterization.

is 4.4 V or (V

in_min

has dropped by 2% of V

out

+ 1 V) whichever is higher.

out_nom

from the nominal valued obtained at Vin = V

out_nom

[ TJ. Low duty

A

+ 8.5 V.

out

12.Not guaranteed in dropout.

www.onsemi.com

6

Page 7

NCV47721

TYPICAL CHARACTERISTICS

1.30

1.29

1.28

1.27

1.26

1.25

, REFERENCE VOLTAGE (V)

1.24

REF1

V

1.23

1.4

1.2

1.0

0.8

0.6

0.4

, REFERENCE VOLTAGE (V)

0.2

REF1

V

0

0.5

Vin = 13.5 V

= 5 mA

I

out

0.4

0.3

0.2

TJ = 25°C

= 1 mA

0.1

, QUIESCENT CURRENT (mA)

q

I

I

out

V

out_nom

= 5 V

0

40 120 160

1401008060200−20−40

TJ, JUNCTION TEMPERATURE (°C) Vin, INPUT VOLTAGE (V)

Figure 4. Reference Voltage vs. Temperature Figure 5. Quiescent Current vs. Input Voltage

0

TJ = 25°C

= 5 mA

I

out

−0.5

TJ = 25°C

R

= 3.3 kW

out

V

out_nom

= 3.3 V

−1.0

−1.5

−2.0

, INPUT CURRENT (mA)

in

I

−2.5

−3.0

543210

−25 −5

Vin, INPUT VOLTAGE (V) Vin, INPUT VOLTAGE (V)

Figure 6. Output Voltage vs. Input Voltage Figure 7. Input Current vs. Input Voltage

(Reverse Input Voltage)

50403020100

0−10−15−20−30−35−40−45

450

400

350

300

250

200

150

100

, DROPOUT VOLTAGE (mV)

DO

V

50

0

V

out_nom

= 5 V

TJ = 150°C

TJ = 25°C

1.15

1.10

1.05

1.00

0.95

TJ = 25°C

TJ = −40°C

TJ = 150°C

0.90

TJ = −40°C

0.85

0.80

0.75

0.70

, OUTPUT CURRENT LIMIT (A)

V

I

LIM

0.65

= 0.9 x V

out

out_nom

0.60

0.300.250.20 0.350.150.100.050

I

, OUTPUT CURRENT (A) Vin, INPUT VOLTAGE (V)

out

35 40

Figure 8. Dropout Voltage vs. Output Current Figure 9. Output Current Limit vs. Input

Voltage

www.onsemi.com

7

45302520151050

Page 8

NCV47721

TYPICAL CHARACTERISTICS

350

300

250

200

150

100

, OUTPUT CURRENT LIMIT (mA)

50

LIM

I

0

61014 202226

R

Figure 10. Output Current Limit vs. R

1.0

TJ = 25°C

0.9

= V

V

in

out_nom

+ 8.5 V

0.8

0.7

0.6

0.5

0.4

0.3

0.2

, QUIESCENT CURRENT (mA)

q

I

0.1

0

I

, OUTPUT CURRENT (mA) I

out

Figure 12. Current Consumption vs. Output

Current

CSO

(kW)

V

= 3.3 V to 20 V

out

CSO

17.515.012.510.07.55.02.50

3.0

V

= 3.3 V to 20 V

out

= −40°C to 150°C

T

2.5

J

I

= 10 mA to 300 mA

LIM

2.0

1.5

, CSO VOLTAGE (V)

1.0

CSO

V

0.5

0

LIM

1008060504020100

)

241816128420

30 70 90 110

I

, OUTPUT CURRENT (% of I

out

Figure 11. CSO Voltage vs. Output Current

(% of Output Current Limit)

14

TJ = 25°C

12

= V

V

in

out_nom

+ 8.5 V

10

8

6

4

, QUIESCENT CURRENT (mA)

2

q

I

0

20.0

, OUTPUT CURRENT (mA)

out

28024020016012080400

Figure 13. Current Consumption vs. Output

Current

OUTPUT CURRENT TO

CSO

/I

out

I

112

110

108

106

TJ = 25°C

= V

V

in

out_nom

+ 8.5 V

104

102

100

98

96

94

CSO CURRENT RATIO (−)

92

90

88

I

, OUTPUT CURRENT (mA) I

out

Figure 14. Output Current to CSO Current

Ratio vs. Output Current

100

95

90

85

80

75

70

OUTPUT CURRENT TO

65

CSO

60

CSO CURRENT RATIO (−)

/I

out

I

55

50

1K100101

www.onsemi.com

8

TJ = 25°C

= 4.5 V

V

in

, OUTPUT CURRENT (mA)

OUT

V

out_nom

= 5 V

Figure 15. Output Current to CSO Current

Ratio in Dropout vs. Output Current

1K100101

Page 9

NCV47721

TYPICAL CHARACTERISTICS

ESR (W)

100

Unstable Region Area

Above Curves

10

1

TJ = 25°C

0.1

= V

V

in

C

= 10 mF − 100 mF

out

C

= none

b

out_nom

+ 8.5 V

Stable Region Area

Under Curves

0.01

I

, OUTPUT CURRENT (mA) FREQUENCY (Hz)

OUT

Figure 16. Output Capacitor Stability Region

vs. Output Current

120

110

100

90

80

70

60

PSRR (dB)

50

TA = 25°C

40

30

20

= 13.5 V DC + 0.5 VPP AC

V

in

V

out_nom

3500

)

3000

1/2

V

V

out_nom

V

out_nom

out_nom

= 20 V

= 5 V

= 3.3 V

2500

2000

1500

1000

, NOISE DENSITY (nV/Hz

n

500

V

0

200150100500

I

= 5 mA

out

I

= 200 mA

out

= 5 V

FREQUENCY (Hz)

Figure 18. PSRR vs. Frequency

f = 10 Hz − 100 kHz

V

= 168.2 mV

n

Figure 17. Noise vs. Frequency

100K10K1K10010

TJ = 25°C

= 12 V

V

in

C

= 10 nF

b

I

= 5 mA

out

100K10K1K10010

www.onsemi.com

9

Page 10

NCV47721

DEFINITIONS

General

All measurements are performed using short pulse low

duty cycle techniques to maintain junction temperature as

close as possible to ambient temperature.

Output Voltage

The output voltage parameter is defined for specific

temperature, input voltage and output current values or

specified over Line, Load and Temperature ranges.

Line Regulation

The change in output voltage for a change in input voltage

measured for specific output current over operating ambient

temperature range.

Load Regulation

The change in output voltage for a change in output

current measured for specific input voltage over operating

ambient temperature range.

Dropout Voltage

The input to output differential at which the regulator

output no longer maintains regulation against further

reductions in input voltage. It is measured when the output

drops 2% of V

below its nominal value. The junction

out_nom

temperature, load current, and minimum input supply

requirements affect the dropout level.

Quiescent and Disable Currents

Quiescent Current (Iq) is the difference between the input

current (measured through the LDO input pin) and the

output load current. If Enable pin is set to LOW the regulator

reduces its internal bias and shuts off the output, this term is

called the disable current (I

DIS

).

Current Limit

Current Limit is value of output current by which output

voltage drops below 90% of its nominal value.

PSRR

Power Supply Rejection Ratio is defined as ratio of output

voltage and input voltage ripple. It is measured in decibels

(dB).

Line Transient Response

Typical output voltage overshoot and undershoot

response when the input voltage is excited with a given

slope.

Load Transient Response

Typical output voltage overshoot and undershoot

response when the output current is excited with a given

slope between low-load and high-load conditions.

Thermal Protection

Internal thermal shutdown circuitry is provided to protect

the integrated circuit in the event that the maximum junction

temperature is exceeded. When activated at typically 175°C,

the regulator turns off. This feature is provided to prevent

failures from accidental overheating.

Maximum Package Power Dissipation

The power dissipation level is maximum allowed power

dissipation for particular package or power dissipation at

which the junction temperature reaches its maximum

operating value, whichever is lower.

www.onsemi.com

10

Page 11

NCV47721

APPLICATIONS INFORMATION

Circuit Description

The NCV47721 is an integrated low dropout regulator

that provides a regulated voltage at 200 mA to output. It is

enabled with an input to the enable pin. The regulator

voltage is provided by a PNP pass transistor controlled by an

error amplifier with a bandgap reference, which gives it the

lowest possible dropout voltage. The output current

capability of the LDO is 200 mA and the base drive

quiescent current is controlled to prevent oversaturation

when the input voltage is low or when the output is

overloaded. The integrated current sense feature provides

diagnosis and system protection functionality. The current

limit of the device is adjustable by resistor connected to CSO

pin. Voltage on CSO pin is proportional to output current.

The regulator is protected by both current limit and thermal

shutdown. Thermal shutdown occurs above 150°C to

protect the IC during overloads and extreme ambient

temperatures.

Regulator

The error amplifier compares the reference voltage to a

sample of the output voltage (V

) and drives the base of a

out

PNP series pass transistor via a buffer. The reference is a

bandgap design to give it a temperature stable output.

Saturation control of the PNP is a function of the load current

and input voltage. Oversaturation of the output power

device is prevented, and quiescent current in the ground pin

is minimized.

Regulator Stability Considerations

The input capacitor (Cin) is necessary to stabilize the input

impedance to avoid voltage line influences. The output

capacitor (C

) helps determine three main characteristics

out

of a linear regulator: startup delay, load transient response

and loop stability. The capacitor value and type should be

based on cost, availability, size and temperature constraints.

The aluminum electrolytic capacitor is the least expensive

solution, but, if the circuit operates at low temperatures

(−25°C to −40°C), both the value and ESR of the capacitor

will vary considerably. The capacitor manufacturer’s data

sheet usually provides this information. The value for the

output capacitor C

, shown in Figure 1 should work for

out

most applications; see also Figure 16 for output stability at

various load and Output Capacitor ESR conditions. Stable

region of ESR in Figure 16 shows ESR values at which the

LDO output voltage does not have any permanent

oscillations at any dynamic changes of output load current.

Marginal ESR is the value at which the output voltage

waving is fully damped during four periods after the load

change and no oscillation is further observable.

ESR characteristics were measured with ceramic

capacitors and additional series resistors to emulate ESR.

Low duty cycle pulse load current technique has been used

to maintain junction temperature close to ambient

temperature.

Calculating Bypass Capacitor

If improved stability (reducing output voltage ringing

during transients) is demanded, connect the bypass

capacitor C

between Adjustable Input pin and V

b

out

pin

according to Applications circuit at Figure 1. Parallel

combination of bypass capacitor C

resistor R

contributes in the device transfer function as an

1

with the feedback

b

additional zero and affects the device loop stability,

therefore its value must be optimized. Attention to the

Output Capacitor value and its ESR must be paid. See also

Stability in High Speed Linear LDO Regulators Application

Note, AND8037/D for more information. Optimal value of

bypass capacitor is given by following expression

Cn+

2 p f

1

z

R

(F)

1

(eq. 1)

where

R

the upper feedback resistor

1

f

the frequency of the zero added into the device

z

transfer function by R

and Cb external

1

components.

Set the R

Choose the f

resistor according to output voltage requirement.

1

with regard on the output capacitance C

z

out

refer to the table below.

C

(mF)

out

fZ range (kHz) max 24 max 37 N/A* N/A*

NOTE: * For C

out

needed for stability improvement. C

useful for noise reduction. See electrical characteristic

table.

10 22 47 100

= 47 mF and higher, Cb capacitors are not

capacitors are

b

Ceramic capacitors and their part numbers listed below

have been used as low ESR output capacitors C

from the

out

table above to define the frequency ranges of additional zero

required for stability:

GRM31CR71C106KAC7 (10 mF, 16 V, X7R, 1206)

GRM32ER71C226KE18 (22 mF, 16 V, X7R, 1210)

GRM32ER61C476ME15 (47 mF, 16 V, X5R, 1210)

GRM32ER60J107ME20 (100 mF, 6.3 V, X5R, 1210)

Enable Input

The enable pin is used to turn the regulator on or off. By

holding the pin down to a voltage less than 0.99 V, the output

of the regulator will be turned off. When the voltage on the

enable pin is greater than 2.31 V, the output of the regulator

will be enabled to power its output to the regulated output

voltage. The enable pin may be connected directly to the

input pin to give constant enable to the output regulator.

Setting the Output Voltage

The output voltage range can be set between 3.3 V and

20 V. This is accomplished with an external resistor divider

feeding back the voltage to the IC back to the error amplifier

by the voltage adjust pin ADJ. The internal reference voltage

,

www.onsemi.com

11

Page 12

NCV47721

is set to a temperature stable reference (V

) of 1.265 V.

REF1

The output voltage is calculated from the following formula.

Ignoring the bias current into the ADJ pin:

R

V

out_nom

+ V

REF1

ǒ

1 )

1

Ǔ

R

2

(eq. 2)

Use R2 < 50 kW to avoid significant voltage output errors

due to ADJ bias current.

Designers should consider the tolerance of R

and R

1

during the design phase.

Setting the Output Current Limit

The output current limit can be set up to 300 mA by

external resistor R

1 mF in parallel with R

(see Figure 1). Capacitor C

CSO

is required for stability of current

CSO

CSO

of

limit control circuitry (see Figure 1).

R

2.55

CSO

2.55

I

100

LIM

1

Ǔ

(eq. 3)

(eq. 4)

(eq. 5)

V

CSO

I

R

+ I

LIM

CSO

+

out

+

ǒ

100

1

R

CSO

100

1

where

R

− current limit setting resistor

CSO

voltage at CSO pin proportional to I

V

CSO

I

− current limit value

LIM

I

− output current actual value

out

out

CSO pin provides information about output current actual

value. The CSO voltage is proportional to output current

according to Equation 3.

Once output current reaches its limit value (I

external resistor R

2.55 V. Calculations of I

than voltage at CSO pin is typically

CSO

LIM

or R

values can be done

CSO

LIM

) set by

using Equation 4 and Equation 5, respectively. Minimum

and maximum value of Output Current Limit can be

calculated according to Equations 6 and 7.

V

I

LIM_min

I

LIM_max

+ RATIO

+ RATIO

min

max

CSO_min

R

CSO_max

V

CSO_max

R

CSO_min

(eq. 6)

(eq. 7)

where

RATIO

− minimum value of Output Current to

min

CSO Current Ratio from electrical

characteristics table and particular output

current range

RATIO

− maximum value of Output Current to

max

CSO Current Ratio from electrical

characteristics table and particular output

current range

V

minimum value of CSO Voltage Level at

CSO_min

Current Limit from electrical characteristics

table

2

V

maximum value of CSO Voltage Level at

CSO_max

Current Limit from electrical characteristics

table

R

− minimum value of R

CSO_min

with respect its

CSO

accuracy

R

− maximum value of R

CSO_max

with respect its

CSO

accuracy

Designers should consider the tolerance of R

the design phase.

Diagnostic in OFF State

The NCV47721 contains also circuitry for OFF state

diagnostics for Short to Battery (STB) and Open Load (OL).

There are internal current source and Pull Down resistors

which provide additional cost savings for overall application

by excluding external components and their assembly cost

and saving PCB space and safe control IOs of a

Microcontroller Unit (MCU).

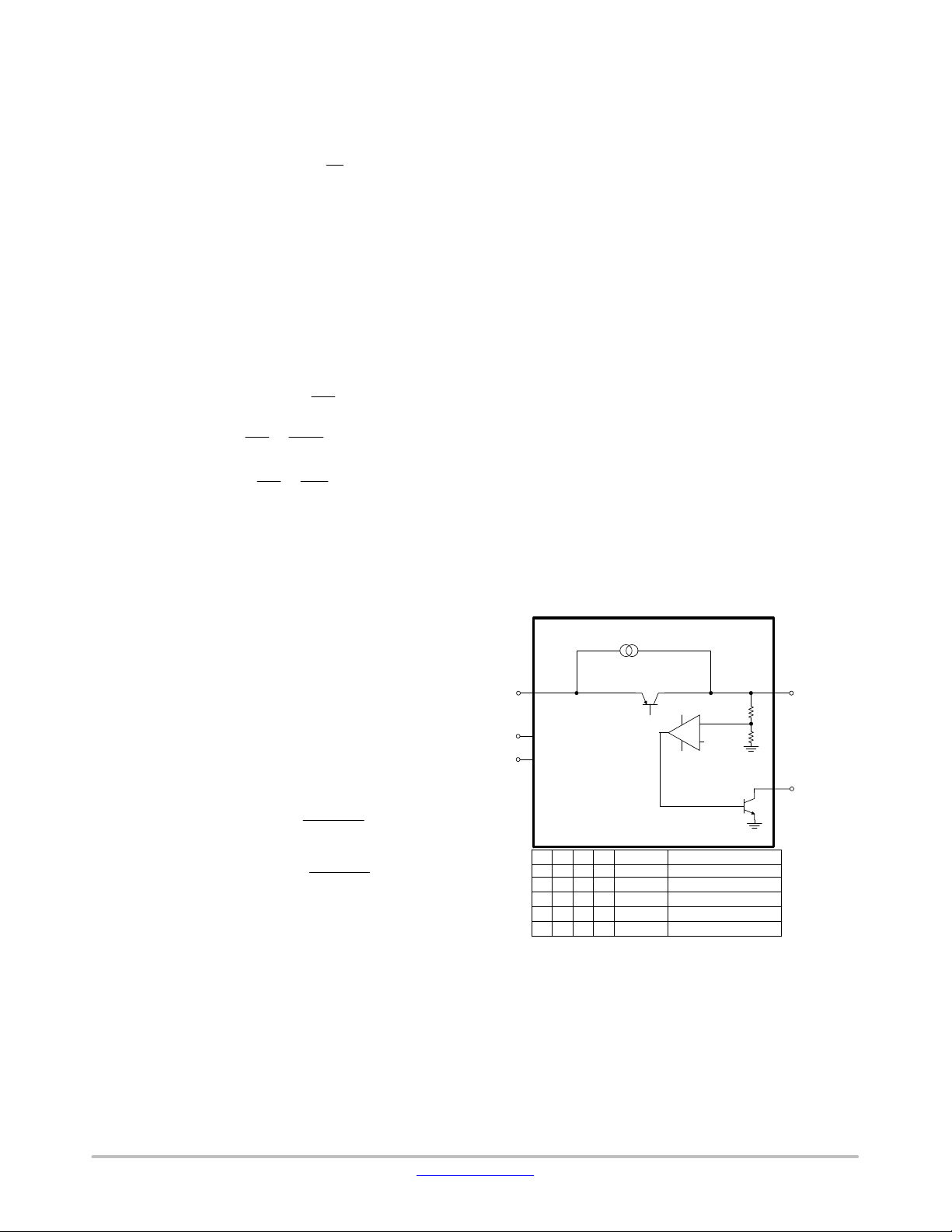

Simplified functional schematic and truth table is shown

in Figure 19 and related flowchart in Figure 20.

Current source enabled via EN and DE pins

I

PU

PASS DEVICE is OFF in Diagnostics

state (DE = H).

Mode in OFF state

out

> V

out

out_OFF

< V

out

out_OFF

> V

out

out_OFF

< V

out

out_OFF

+

V

−

REF_OFF

Diagnostic Status/Action

Short to Battery (STB)

Check for Open Load (OL)

Open Load (OL)

No Failure (V

close to 0 V)

out

R

R

V

in

Comparator active only in Diagnostic

EN

DE

EN – Enable (Logic Input)

DE – Diagnostics Enable (Logic Input)

EF – Error Flag Output (Open Collector Output)

EN DE IPUEF V

L L OFF HZ Unknown None (Diagnostics OFF)

L H OFF L V

L H OFF HZ V

HHONLV

H H ON HZ V

Figure 19. Simplified Functional Diagram of OFF

State Diagnostics (STB and OL)

CSO

V

out

PD1

PD2

EF

Digital Diagnostics:

to MCU’s digital input

with pull−up resistor

to MCU’s DIO supply rail

during

www.onsemi.com

12

Page 13

NCV47721

Start

For diagnostics in OFF state the input DE pin has to be put

logic high. Logic level on EN pin determines which failure

(STB or OL) is diagnosed. For detailed information see

Diag. OFF. Set

EN = L & DE = L

Diag. ON. Set

EN = L & DE = H

Diagnostic Truth Table 7.

Diagnostic in ON State

Diagnostic in ON State provides information about

Overcurrent or Short to Ground failures, during which the

EF output is in logic low state. For detailed information see

HZ

SPU ON. Set

EN = H & DE = H

HZ

No Failure Open Load Short to Battery

EF = ?

EF = ?

L

L

Figure 20. Flowchart for Diagnostics in OFF State

Table 7. DIAGNOSTIC FEATURES TRUTH TABLE

Operational Status EN DE Output Voltage (V

Disabled L L Low (~0 V) Low (~0 V) HZ

Short to Battery L H High (V

Open Load (OFF) H H High (V

Normal (OFF) H H Low (~0 V) Low (~0 V) HZ (Note 14)

Open Load (ON) H L V

Normal (ON) H L V

Over Current H L ≤ 90% of V

Short to Ground H L Low (~0 V) High (~2.55 V) L

13.Internal current source disabled (between V

14.Internal current source enabled (between V

and Vin)

out

and Vin)

out

~ Vin) Low (~0 V) L (Note 13)

out

~ Vin) Low (~0 V) L (Note 14)

out

out_nom

out_nom

out_nom

Diagnostic Features Truth Table 7.

) Diagnostic Output (CSO) Error Flag (EF)

out

Low (~0 V) HZ

Proportional to I

High (~2.55 V) L

(±5%) HZ

out

www.onsemi.com

13

Page 14

NCV47721

Thermal Considerations

As power in the device increases, it might become

necessary to provide some thermal relief. The maximum

power dissipation supported by the device is dependent

upon board design and layout. Mounting pad configuration

on the PCB, the board material, and the ambient temperature

affect the rate of junction temperature rise for the part. When

the device has good thermal conductivity through the PCB,

the junction temperature will be relatively low with high

power applications. The maximum dissipation the device

can handle is given by:

ƪ

T

P

D(MAX)

+

J(MAX)

R

Since TJ is not recommended to exceed 150°C, then the

device soldered on 645 mm

2

, 1 oz copper area, FR4 can

dissipate up to 2 W when the ambient temperature (T

25°C. See Figure 21 for R

versus PCB area. The power

JA

q

dissipated by the device can be calculated from the

following equations:

PD[ V

ǒ

in

Iq@I

out

Ǔ

) I

out

or

V

in(MAX)

P

[

D(MAX)

)ǒV

I

out

* T

qJA

ǒ

Vin* V

out

) I

ƫ

A

out

I

out

q

(eq. 8)

) is

A

Ǔ

(eq. 9)

Ǔ

(eq. 10)

120

110

100

90

80

70

60

50

40

, THERMAL RESISTANCE (°C/W)

JA

30

q

R

20

1 oz, Single Layer

2 oz, Single Layer

1 oz, 4 Layer

2 oz, 4 Layer

600 7005004003002001000

COPPER HEAT SPREADER AREA (mm2)

Figure 21. Thermal Resistance vs. PCB Copper Area

Hints

Vin and GND printed circuit board traces should be as

wide as possible. When the impedance of these traces is

high, there is a chance to pick up noise or cause the regulator

to malfunction. Place external components, especially the

output capacitor, as close as possible to the device and make

traces as short as possible.

ORDERING INFORMATION

Device Output Voltage Marking Package Shipping

NCV47721PAAJR2G Adjustable Line1: NCV4

Line2: 7721

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging

Specifications Brochure, BRD8011/D

TSSOP−14 Exposed Pad

(Pb−Free)

2500 / Tape & Reel

†

www.onsemi.com

14

Page 15

MECHANICAL CASE OUTLINE

PACKAGE DIMENSIONS

14

TSSOP−14 EP

CASE 948AW

1

SCALE 1:1

NOTE 6

B

14 8

c1

NOTE 5

E1

E

c

PIN 1

REFERENCE

NOTE 6

0.05 C

0.10 C

14X

A

e

1

TOP VIEW

NOTE 4

14X

NOTE 3

7

D

0.20 C

2X 14 TIPS

A2

A

BA

B

b

0.10

C

B A

SEATING

SS

C

PLANE

c

B

SIDE VIEW

D2

H

E2

A1

NOTE 7

DETAIL A

BOTTOM VIEW

RECOMMENDED

SOLDERING FOOTPRINT*

3.40

3.06

1

0.65

PITCH

DIMENSIONS: MILLIMETERS

*For additional information on our Pb−Free strategy and soldering

details, please download the ON Semiconductor Soldering and

Mounting Techniques Reference Manual, SOLDERRM/D.

14X

1.15

6.70

14X

0.42

ISSUE C

b

b1

SECTION B−B

NOTE 8

DETAIL A

END VIEW

L

L2

NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME

Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION b DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE PROTRUSION SHALL BE

0.07 mm MAX. AT MAXIMUM MATERIAL CONDITION.

DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OF THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD IS 0.07.

4. DIMENSION D DOES NOT INCLUDE MOLD FLASH,

PROTRUSIONS OR GATE BURRS. MOLD FLASH,

PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED

0.15 mm PER SIDE. DIMENSION D IS DETERMINED AT

DATUM H.

5. DIMENSION E1 DOES NOT INCLUDE INTERLEAD

FLASH OR PROTRUSIONS. INTERLEAD FLASH OR

PROTRUSIONS SHALL NOT EXCEED 0.25 mm PER

SIDE. DIMENSION E1 IS DETERMINED AT DATUM H.

6. DATUMS A AND B ARE DETERMINED AT DATUM H.

7. A1 IS DEFINED AS THE VERTICAL DISTANCE FROM

C

M

GAUGE

PLANE

THE SEATING PLANE TO THE LOWEST POINT ON THE

PACKAGE BODY.

8. SECTION B−B TO BE DETERMINED AT 0.10 TO 0.25 mm

FROM THE LEAD TIP.

MILLIMETERS

DIM MIN MAX

A −−−− 1.20

A1 0.05 0.15

A2 0.80 1.05

b 0.19 0.30

b1 0.19 0.25

c 0.09 0.20

c1 0.09 0.16

D 4.90 5.10

D2 3.09 3.62

E 6.40 BSC

E1 4.30 4.50

E2 2.69 3.22

0.65 BSCe

L 0.45 0.75

L2 0.25 BSC

M 0 8

__

GENERIC

MARKING DIAGRAM*

14

XXXX

XXXX

ALYWG

G

1

XXXX = Specific Device Code

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

G = Pb−Free Package

(Note: Microdot may be in either location)

*This information is generic. Please refer to

device data sheet for actual part marking.

Pb−Free indicator, “G” or microdot “ G”,

may or may not be present.

DATE 09 OCT 2012

DOCUMENT NUMBER:

DESCRIPTION:

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.

ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding

the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically

disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the

rights of others.

© Semiconductor Components Industries, LLC, 2019

98AON66474E

TSSOP−14 EP, 5.0X4.4

Electronic versions are uncontrolled except when accessed directly from the Document Repository.

Printed versions are uncontrolled except when stamped “CONTROLLED COPY” in red.

PAGE 1 OF 1

www.onsemi.com

Page 16

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.

ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor’s product/patent

coverage may be accessed at www.onsemi.com/site/pdf/Patent−Marking.pdf

ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability

arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards,

regardless of any support or applications information provided by ON Semiconductor. “Typical” parameters which may be provided in ON Semiconductor data sheets and/or

specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer

application by customer’s technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not

designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification

in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized

application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and

expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such

claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This

literature is subject to all applicable copyright laws and is not for resale in any manner.

. ON Semiconductor reserves the right to make changes without further notice to any products herein.

PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

ON Semiconductor Website: www.onsemi.com

TECHNICAL SUPPORT

North American Technical Support:

Voice Mail: 1 800−282−9855 Toll Free USA/Canada

Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

◊

www.onsemi.com

1

Loading...

Loading...