Page 1

© Semiconductor Components Industries, LLC, 2012

May, 2012 − Rev. 2

1 Publication Order Number:

EVBUM2110/D

NCP2824FCT2GEVB

NCP2824FCT2 Evaluation

Board User's Manual

Overview

The NCP2824 is a Filterless Class D amplifier capable of

delivering up to 2.4 W to a 4 W load with a 5 V supply

voltage. With the same battery voltage, it can deliver 1.2 W

to an 8 W load with less than 1% THD+N. The Non-clipping

function adjusts automatically the output voltage in order to

control the distortion when an excessive input is applied to

the amplifier. This adjustment is done thanks to an

Automatic Gain Control circuitry (AGC) built-in the chip.

A simple Single wire interface allows to enable/disable the

non Clipping function and also to configure the maximum

distortion level in the output. A programmable power limit

function is also embedded in order to protect speakers from

damage caused by an excessive sound level.

The intent of the evaluation boards is to illustrate typical

operation of the NCP2824 device for laboratory

characterization. The NCP2824FCT2GEVB schematic is

depicted in Figure 2.

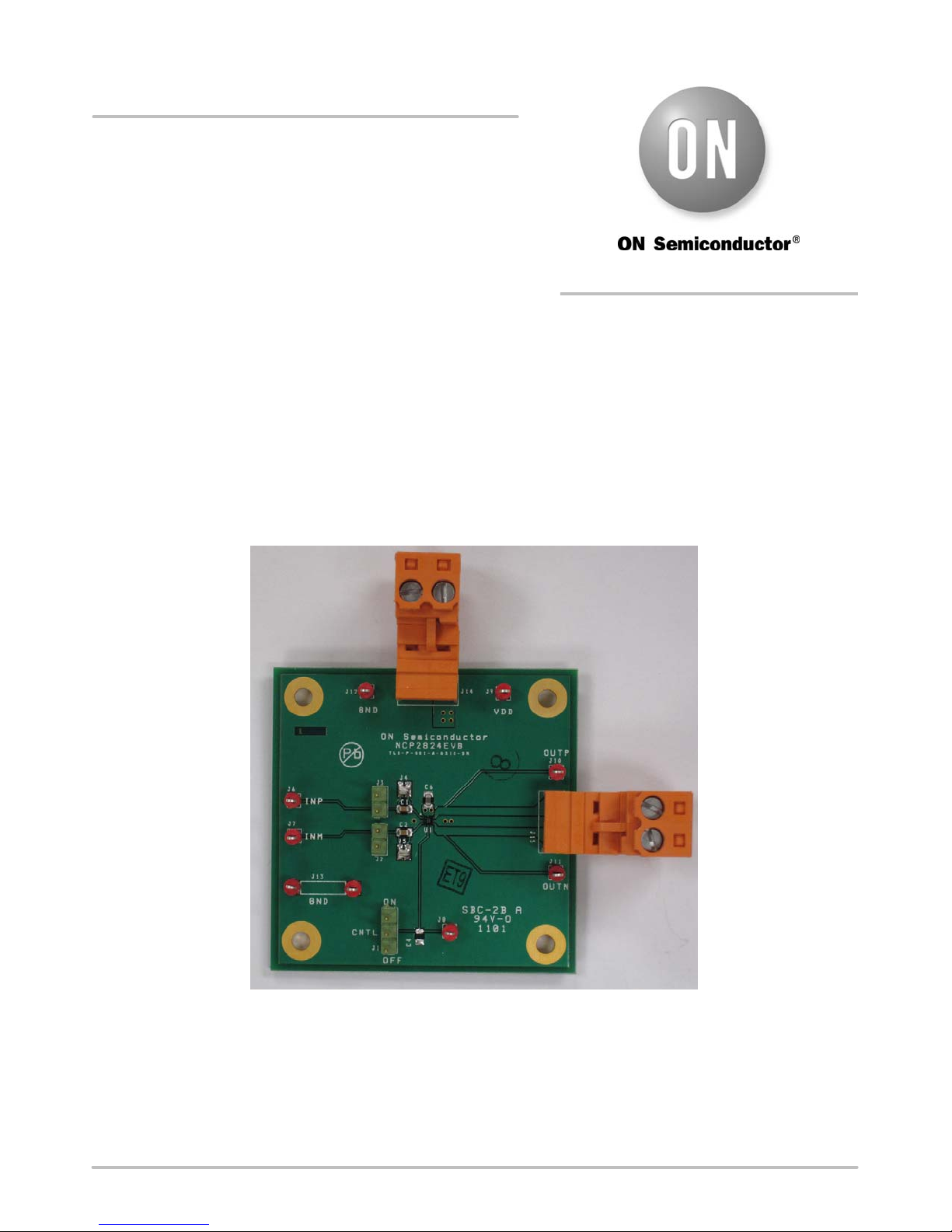

Figure 1. NCP2824FCT2GEVB Board Picture

http://onsemi.com

EVAL BOARD USER’S MANUAL

Page 2

NCP2824FCT2GEVB

http://onsemi.com

2

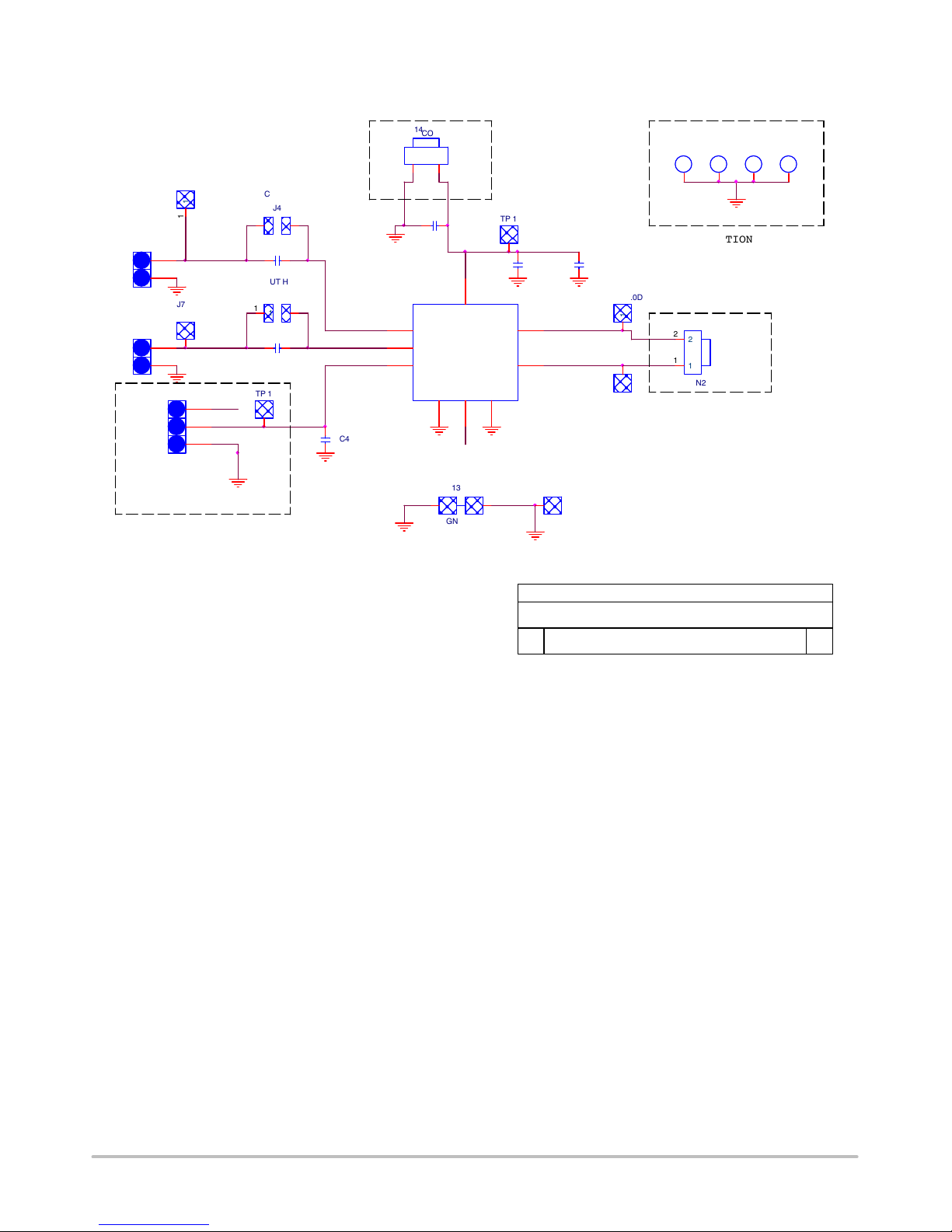

BOARD SCHEMATIC

Figure 2. NCP2824FCT2GEVB Evaluation Board Schematic

Title

Size Document Number Rev

Date: Sheet

of

NCP2824 EVB TLS−P−001−A−0310−DR

NCP2824 EVB

Custom

11

U1

NCP2824

INP

A1

VDD

A2

OUTP

A3

AGNDB1NCB2PGND

B3

INM

C1

CNTL

C2

OUTM

C3

C1

100n

C2

100n

C3

4.7μF

0

OUTN

OUTP

0 0

J1

Jumper3

1

1

2

2

3

3

0

Vdd

J2

Jumper2

1

1

2

2

J3

Jumper2

1

1

2

2

0

0

J4

CUT H

112

2

J5

CUT H

112

2

INPF

J6

TP 1.0D

1

1

J7

TP 1.0D

1

1

J8

TP 1.0D

1

1

CNTL

J9

TP 1.0D

1

1

Vdd

J10

TP 1.0D

1

1

J11

TP 1.0D

1

1

J13

GND

112

2

0

0

INMF

J14

CON2

112

2

0

J15

CON2

1

1

2

2

C4

NC

0

C5

100μF−NC

C6

4.7μF

0

J16

FIX 3.2 H

1

1

J17

FIX 3.2 H

1

1

J18

FIX 3.2 H

1

1

J19

FIX 3.2 H

1

1

0

J12

TP 1.0D

1

1

ENABLE− SINGLE WIRE

BOARD FIXATION HOLES

POWER SUPPLY

SPEAKER CONNECTION

Page 3

NCP2824FCT2GEVB

http://onsemi.com

3

OPERATION

The operating power supply of the NCP2824 is from 2.5

to 5.5 V. The absolute maximum input voltage is 7.0 V. A

power supply set to 3.6 V and current limit set to at least

1.5 A must be connected to J14 connector to powering the

NCP2824EVB/D. Also to compensate for parasitic

inductance of wires between the power supply and the

evaluation board it is highly recommended to connect a

470 mF electrolytic capacitor to bypass J14 terminal. Like

this the device can be evaluated under powering condition

very similar that battery power supplies.

Performances of EVB Solution

To be as close as possible with final handset application,

the design of this power conversion solution used small size

footprints where possible. Changing components may

positively or negatively impact the evaluation board

performance illustrated in Figure 3 to 8. For more

information please refer to the NCP2824 datasheet.

Single Wire Interface Operation

The single wire interface allows changing the default

configuration of the NCP2824.

After Wake up, the NCP2824 is configured with:

• AGC enable

• Non Clip + Power limit

• Gain = 18 dB

• THD max = 1%

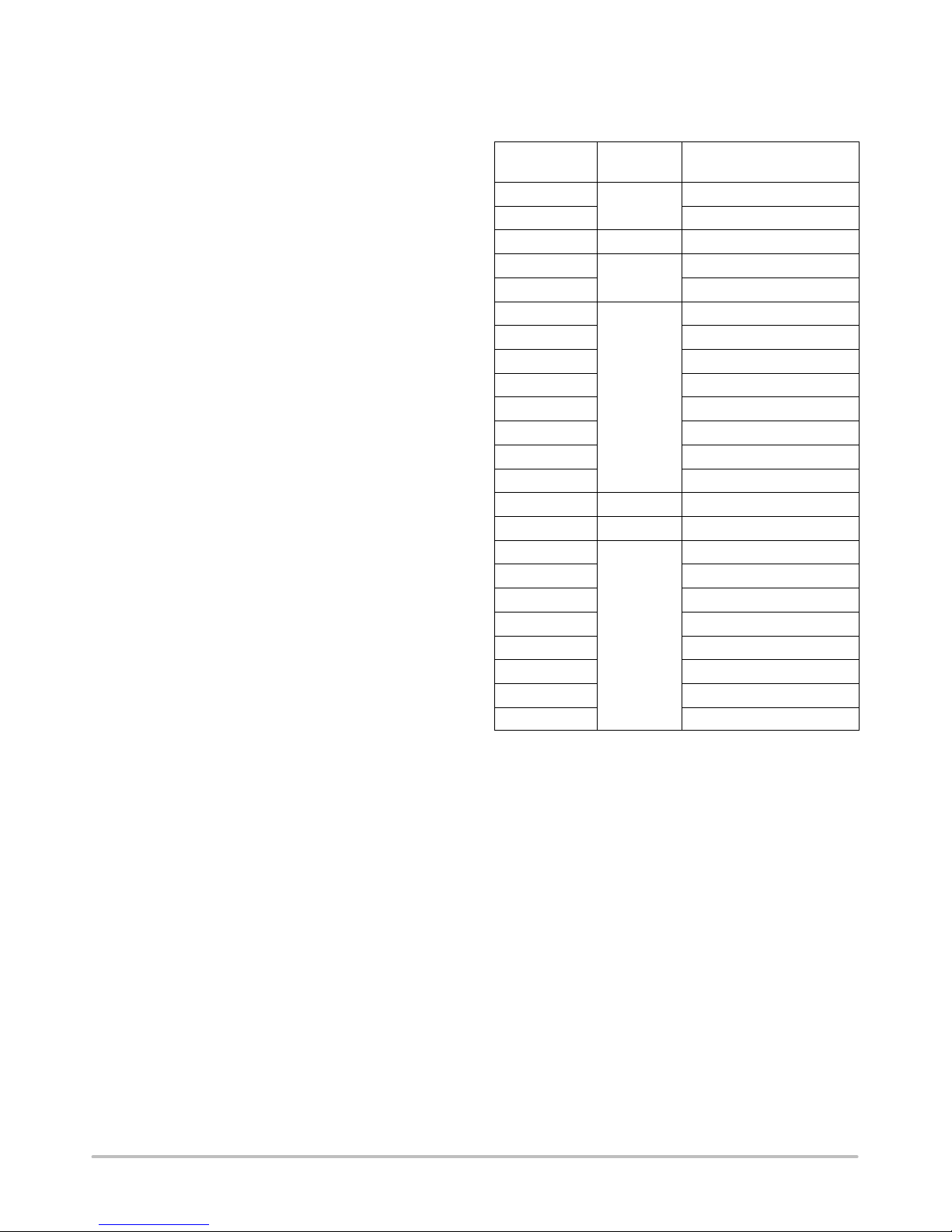

The following table described all the NCP2824

configurations.

Table 1. NCP2824 CONFIGURATION

Pulse

Counting

Register Description

01

AGC

AGC disable

02 AGC Enable

03 Reset Reset configuration

04

Gain

Control

Gain = 12 dB

05 Gain = 18 dB

06

THD

Control

1%

07 2%

08 4%

09 6%

10 8%

11 10%

12 15%

13 20%

14 NC+L Non Clip + Power limit

15 NC Non Clip only

16

Power

Limit

Control

0.45 V

Peak

17 0.9 V

Peak

18 1.35 V

Peak

19 1.8 V

Peak

20 2.25 V

Peak

21 2.7 V

Peak

22 3.15 V

Peak

23 3.6 V

Peak

Single Wire commands can easily be emulated using a

pulse generator configured in accordance with the Single

wire specification, for more information about timings

please refers to NCP2824 datasheet.

Page 4

NCP2824FCT2GEVB

http://onsemi.com

4

Table 2. BOARD CONNECTIONS

INPUT POWER

Symbol

Descriptions

J14−1 This is the positive connection for power supply. The leads (positive + ground) to the input supply should

be twisted and kept as short as possible.

J14−2 This is the return connection for the power supply (Ground signal)

J13 Ground clip

AUDIO

Symbol

Descriptions

J3 Positive Audio input

J2 Negative Audio input

J15−2 Positive Audio output

J15−1 Negative Audio output

SWITCHES SETUP

Symbol

Switch Descriptions

J1 Enable

J4 Short input capacitor on positive input

J5 Short input capacitor on negative input

J2 Connect the positive audio input to Gnd

J3 Connect the negative audio input to Gnd

TEST POINT

Symbol

Switch Descriptions

J12 This test point is directly connected to the GND

J9 This test point is directly connected to the Vdd pin

J6 This test point is connected to the positive audio input

J7 This test point is connected to the negative audio input

J10 This test point is connected to the positive audio output

J11 This test point is connected to the negative audio output

Page 5

NCP2824FCT2GEVB

http://onsemi.com

5

TYPICAL OPERATING CHARACTERISTICS

Figure 3. THD vs. P

OUT

, RI = 8 W, f = 1 kHz Figure 4. THD vs. P

OUT

, RI = 4 W, f = 1 kHz

THD+N vs Pout @ 25°C

0.01

0.1

1

10

100

10 100 1000 10000

Pout (mW)

THD (%)

Vdd=2.5V Vdd=2.7V Vdd=3V Vdd=3.6V Vdd=4.2V Vdd=5V Vdd=5.5V

THD+N vs Pout @ 255C

0.01

0.1

1

10

100

10 100 1000 10000

Pout (mW)

THD (%)

Vdd=2.5V Vdd=2.7V Vdd=3V Vdd=3.6V Vdd=4.2V Vdd=5V Vdd=5.5V

Figure 5. Efficiency vs. P

OUT

, RI = 8 W, f = 1 kHz Figure 6. THD vs. Frequency, RI = 8 W,

P

OUT

= 250 mW

Eff vs Pout @ Vdd=3.6V

0

10

20

30

40

50

60

70

80

90

100

0 200 400 600 800 1000

Pout (mW)

(%)

RL = 8 W

THD ve rsus Fre quency @ Vdd=3.6V

0.001

0.01

0.1

1

10

10 100 1000 10000 100000

Freq (Hz)

THD+N (%)

Pout=250mW Pout=500mW

Figure 7. Peak Output Voltage in Power Limit vs. Input

Voltage (rms) and Power Limit Settings, Av = 12 dB

Figure 8. PSRR vs. Frequency

Peak voltage vs. Vin for VDD=5V

Temp=25 5C

0.0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

4.0

0.0 0.2 0.4 0.6 0.8 1.0 1.2

Vin(V)

(V)

Vpeak Target=0.45V Vpeak Target=0.9V Vpeak Target=1.35V Vpeak Target=1.8V

Vpeak Target=2.25V Vpeak Target=2.7V Vpeak Target=3.15V Vpeak Target=3.6V

PSRR vs Frequency (Inputs grounded, Gain = 12 dB, Cin = 1 mF)

−80

−70

−60

−50

−40

−30

−20

−10

0

10 100 1000 10000 100000

Fr e q (Hz)

PSRR (dB)

Vdd=3V Vdd=3.6V Vdd=5V

Page 6

NCP2824FCT2GEVB

http://onsemi.com

6

PCB LAYOUT

As with all Class D amplifiers, care must be observed to

place the components on the PCB and layout the critical

nodes. The evaluation board is made of 4 PCB layers where

first internal layer is a GND. Figure 9, Figure 10 and

Figure 11 show the layout of the NCP2824FCT2GEVB

board.

For more specific layout guidelines please refer to the

NCP2824 datasheet.

Figure 9. Assembly Layer TOP

Figure 10. Top Layer Routing

Page 7

NCP2824FCT2GEVB

http://onsemi.com

7

Figure 11. Bottom Layer Routing

Table 3. BILL OF MATERIALS

Qty Ref Des. Description Size Manufacturer Part Number

1 U1 NCP2824 CSP−9

1.45 x 1.45

mm

ON Semiconductor NCP2824

2 C1, C2 Capacitor, Ceramic 100 nF 0603 KEMET C0603C104K5RAC

2 C3, C6

Capacitor, Ceramic 4.7 mF 6.3 V

0603 KEMET C0603C475K9PAC

2 J14, J15 Mal. SL5.08/2/90B plus Fem. BLZ

5.08/2

Weidmuller SL5.08/2/90 +

BLZ 5.08/2

3 J1 Header 3 pin, 100 mil spacing 0.100 x 2 Std Std

2 J2, J3 Header 2 pin, 100 mil spacing 0.100 x 2 Std Std

1 J6 GND Connection Std Std

9 J6, J7, J9, J10,

J11, J12, J13

Test Point Std Std

2 J4, J5 Soldering point must be connected

1 PCB PCB 2.0 in x 2.0 in x 1.0 mm, 4 Layers Any TLS−P−001−A−0310−RD

NOTE: C3 is not mounted

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice

to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability

arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All

operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights

nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications

intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should

Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,

and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death

associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal

Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

PUBLICATION ORDERING INFORMATION

N. American Technical Support: 800−282−9855 Toll Free

USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81−3−5817−1050

EVBUM2110/D

LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor

P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303−675−2175 or 800−344−3860 Toll Free USA/Canada

Fax: 303−675−2176 or 800−344−3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local

Sales Representative

Loading...

Loading...