Page 1

SERVICE MANUAL

SERVICE MANUAL

STEREO CASSETTE TAPE DECK

MODEL TA-RW255

TA-RW255

Ref. No. 3872

062005

ONKYO

North American model

Other models

EJECT

DECK-A

PLAY

HI-SPEED DUBBING

L

dB -20- -10 -6 -3 +30+6

R

DOLBY NR

REVERCE MODE

POWER

STANDBY

STANDBY/ON

STANDBY

STANDBY/ON

MAIN POWER

OFF

ON

STANDBY

DOLBY NR

OFF B C

DUBBING COUNTER

AUTO SPACE

HIGHNORMAL A/B RESET

EJECT

DECK-B

PAUSE

PLAY

REC

A

B

DUBB.STOP

REC LEVEL

MIN MAX

Black and Silver models

BMDD

BMPA, BMGT

120V AC, 60Hz

230-240V AC, 50Hz

BMPP, SMPP

SAFETY-RELATED COMPONENT

WARNING!!

COMPONENTS IDENTIFIED BY MARK ON THE

SCHEMATIC DIAGRAM AND IN THE PARTS LIST ARE

CRITICAL FOR RISK OF FIRE AND ELECTRIC SHOCK.

REPLACE THESE COMPONENTS WITH ONKYO

PARTS WHOSE PART NUMBERS APPEAR AS SHOWN

IN THIS MANUAL.

MAKE LEAKAGE-CURRENT OR RESISTANCE

MEASUREMENTS TO DETERMINE THAT EXPOSED

PARTS ARE ACCEPTABLY INSULATED FROM THE

SUPPLY CIRCUIT BEFORE RETURNING THE

APPLIANCE TO THE CUSTOMER.

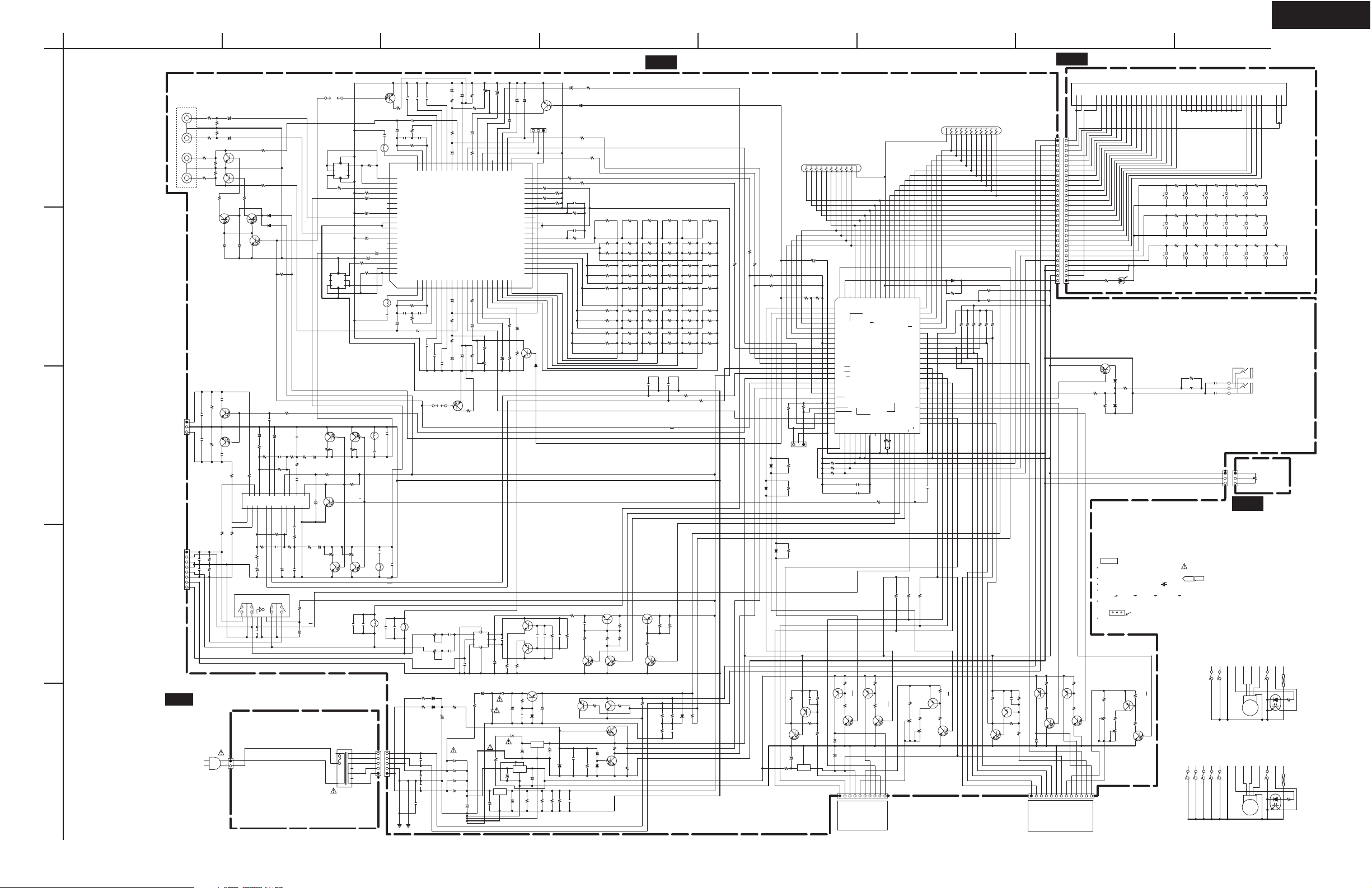

Page 2

SPECIFICATIONS

Format: Auto reverse double deck

Track format: 4-tracks, 2-channels

Recording system: AC bias

Erasing system: AC erase

Tape speed: 4.76 cm/sec. (1-7/8 i.p.s)

Wow and Futter: 0.13 % (WRMS)

Frequency response:

Metal position tape 30 Hz to 15 kHz ±3 dB

High position tape 30 Hz to 14 kHz ±3 dB

Normal position tape

Signal to noise ratio: 56 dB (metal position tape/ Type IV,

Input Jacks:

LINE IN: 2

Input sensitivity: 80 mV

Input impedance: 50 k ohm

Output Jacks:

LINE OUT: 2

Standard output level:

Output load impedance:

Motors: DC servo motor: 1+1

Heads:

PB Head: Special Hard Permalloy x 1

Rec/PB Head: Special Hard Permalloy x 1

Erase head: Ferrite x 1

Power supply rating: North American: AC 120 V, 60 Hz

Power consumption: 17 W

Standby power consumption:

Dimensions: (W x H x D):

Weight: 4.9 kg (10.8 lbs.)

Operation condition temperature/humidity:

30 Hz to 13 kHz ±3 dB

Dolby NR off)

55 dB (high position/ Type II, Dolby NR

off)

50 dB (normal position/ Type I, Dolby

NR off)

Noise reduction of 10 dB above 5 kHz

and 5 dB at 1 kHz possible with Dolby B.

Noise reduction of 20 dB at 5 kHz

possible with Dolby C.

500 mV

over 50 k ohm

European: AC 230 - 240 V, 50 Hz

North American: 7.0 W

European: 0.6 W

435 mm x 121 mm x 303 mm

(17-1/8" x 4-3/4" x 11-15/16")

5 C - 35 C/ 5% - 85% (no condensation)

TA-RW255

Specifications and external appearance are subject to change

without notice because of product improvements.

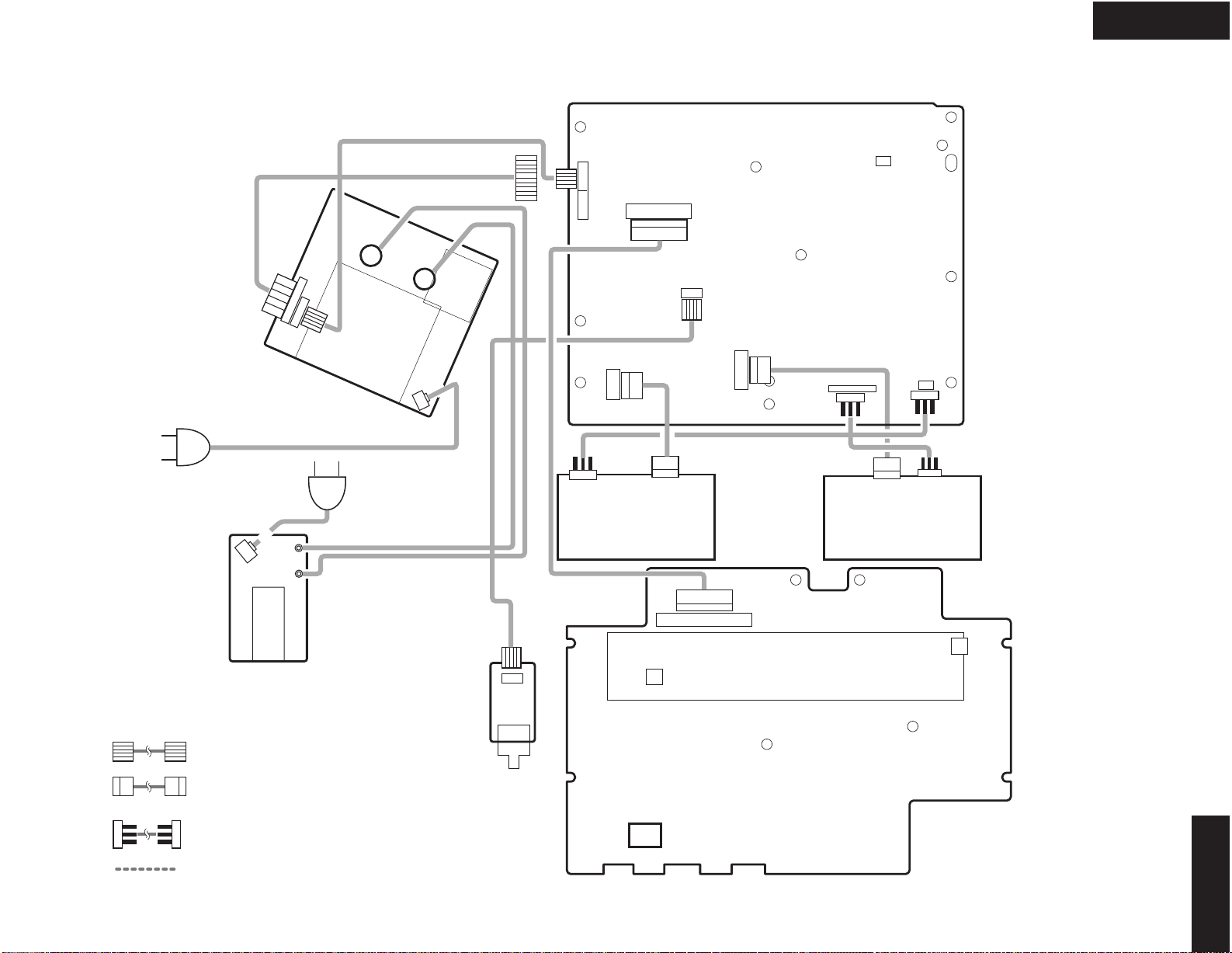

Page 3

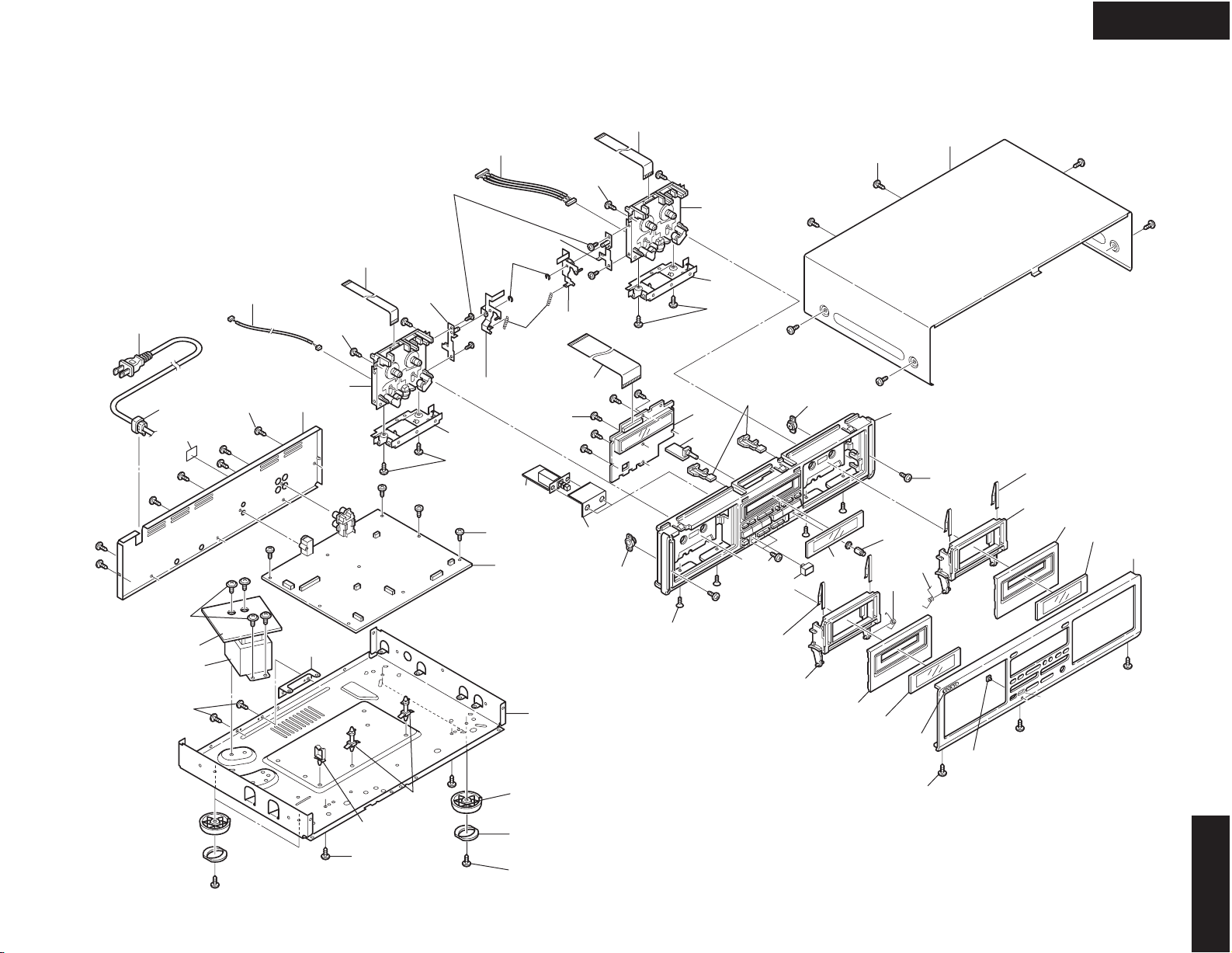

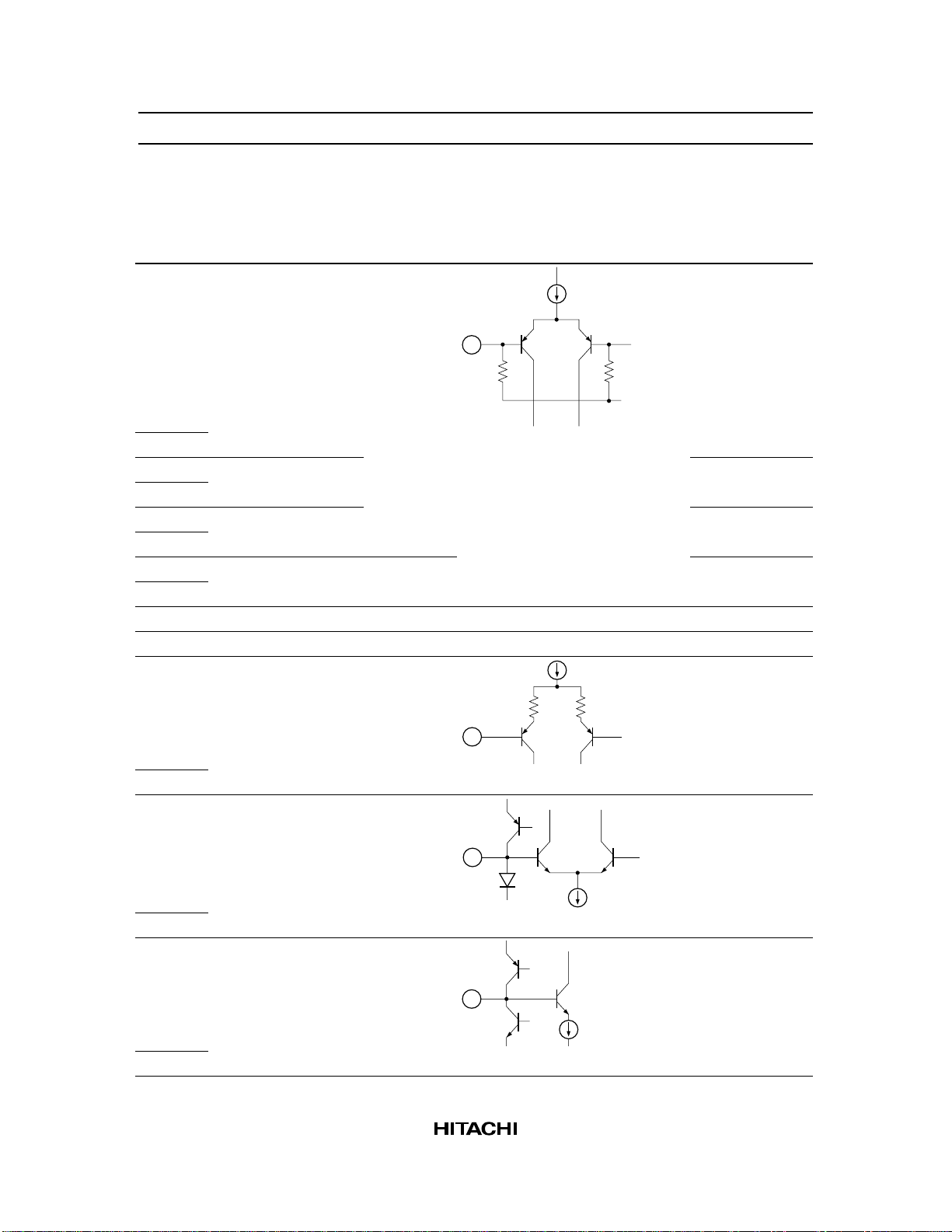

TA-RW255

EXPLODED VIEW

P101

P901A

A202

A026 A201

A208

x 7 pcs.

P801

A029

x 2 pcs.

Z001

Z009

x 4 pcs.

Z005

P102

Z008

x 2 pcs.

Z003

A010

A011

x 2 pcs.

Z006

Z007

x 2 pcs.

A029

x 5 pcs.

U05

A029

x 4 pcs.

U01

A029

x 2 pcs.

Z004

P701

A204

A007

P802

Z002

A010

A011

x 2 pcs.

U02

U04

A008

x 2 pcs.

A205

A203

A007

A006

A302

x 6 pcs.

A001

A021

A016

A015

A301

A004

x 2 pcs.

A014

x 2 pcs.

A013

A316

A317

A305

A028

x 4 pcs.

U03

T901

A029

x 2 pcs.

A020

E851

A206

x 2 pcs.

A019

x 2 pcs.

A017

A311

x 4 pcs.

A313

x 8 pcs.

A312

x 4 pcs.

A003

x 4 pcs.

A014

x 2 pcs.

A013

A315

A317

A308

A306

x 3 pcs.

A307

Except

<MDD>

TA-RW255

Page 4

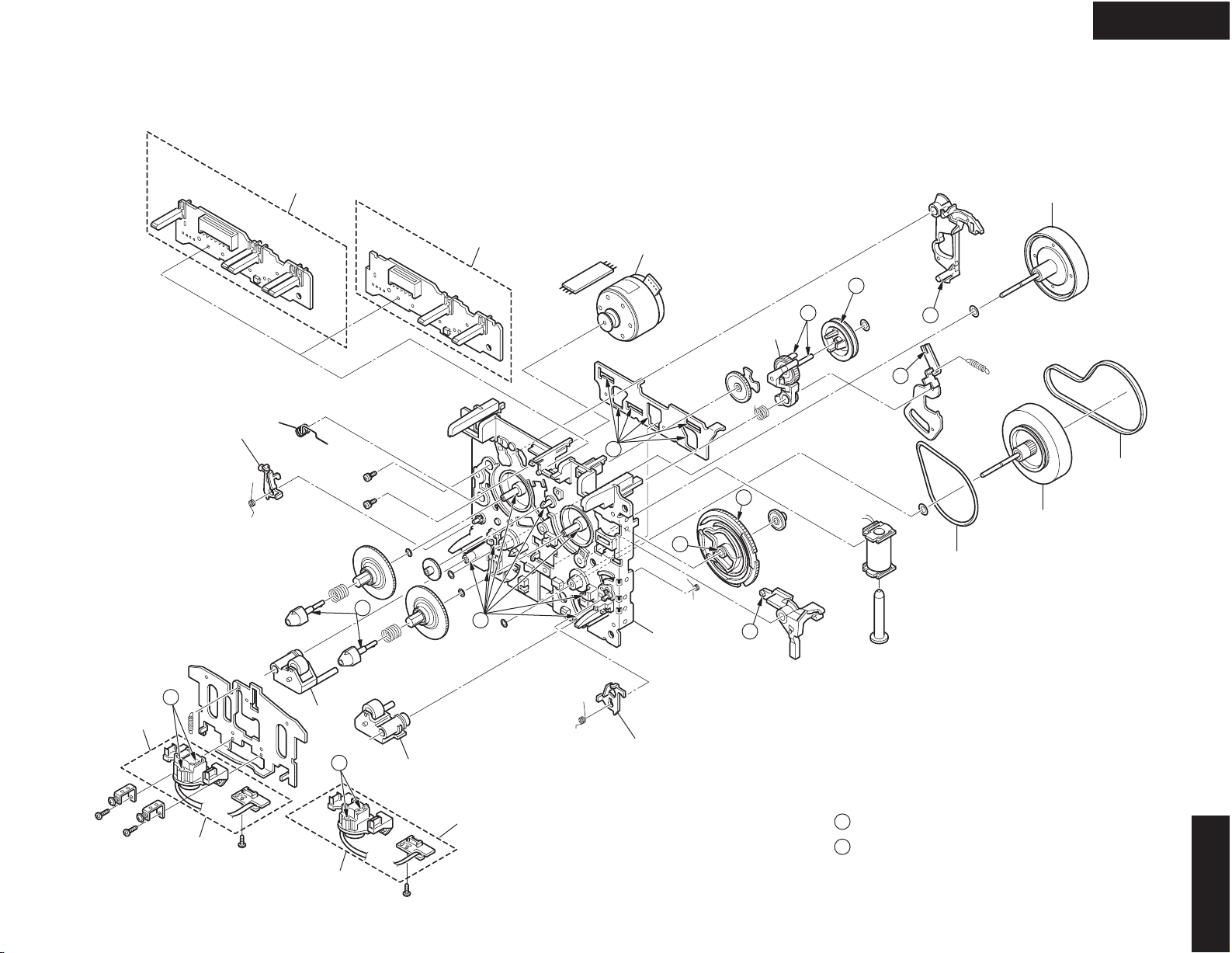

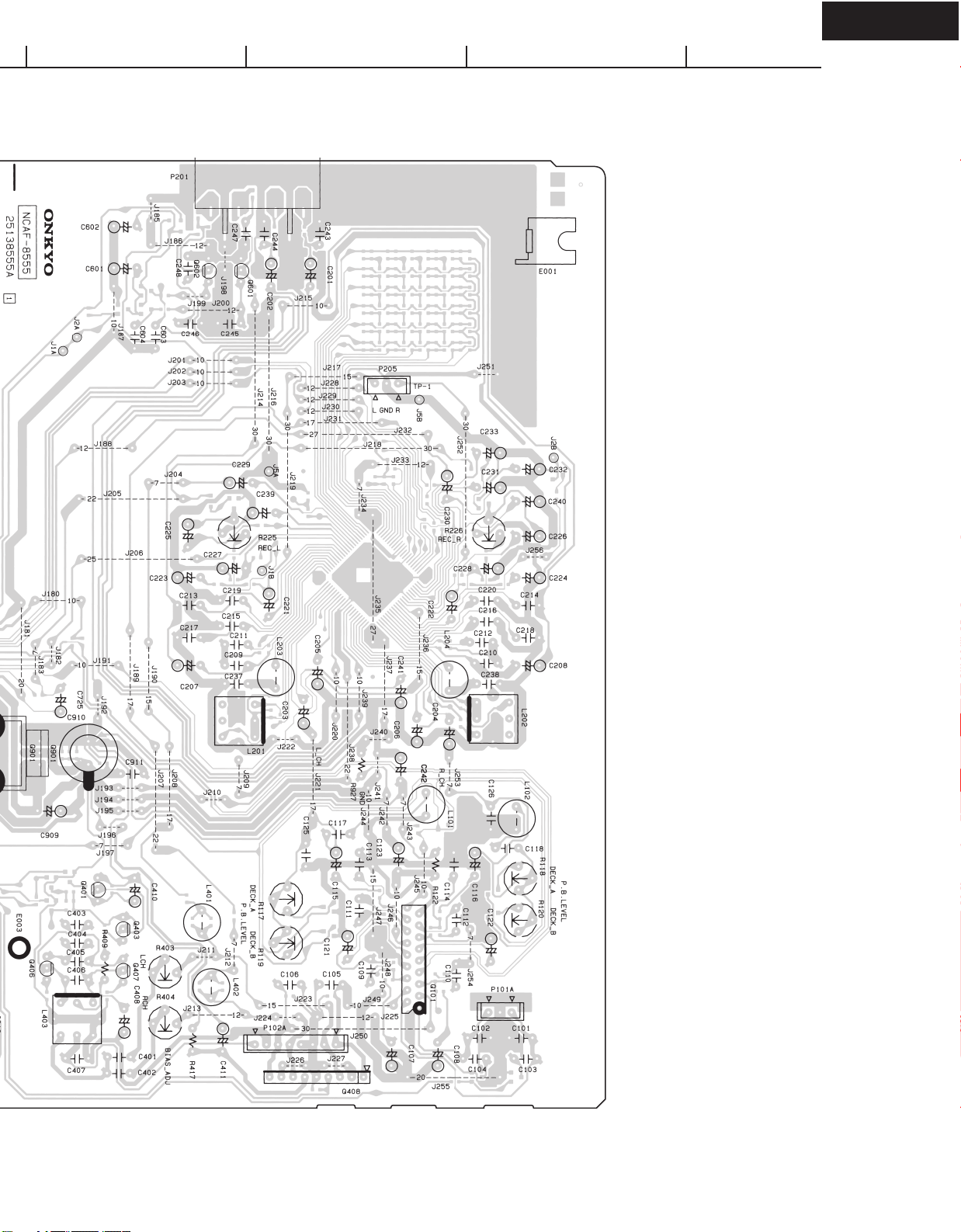

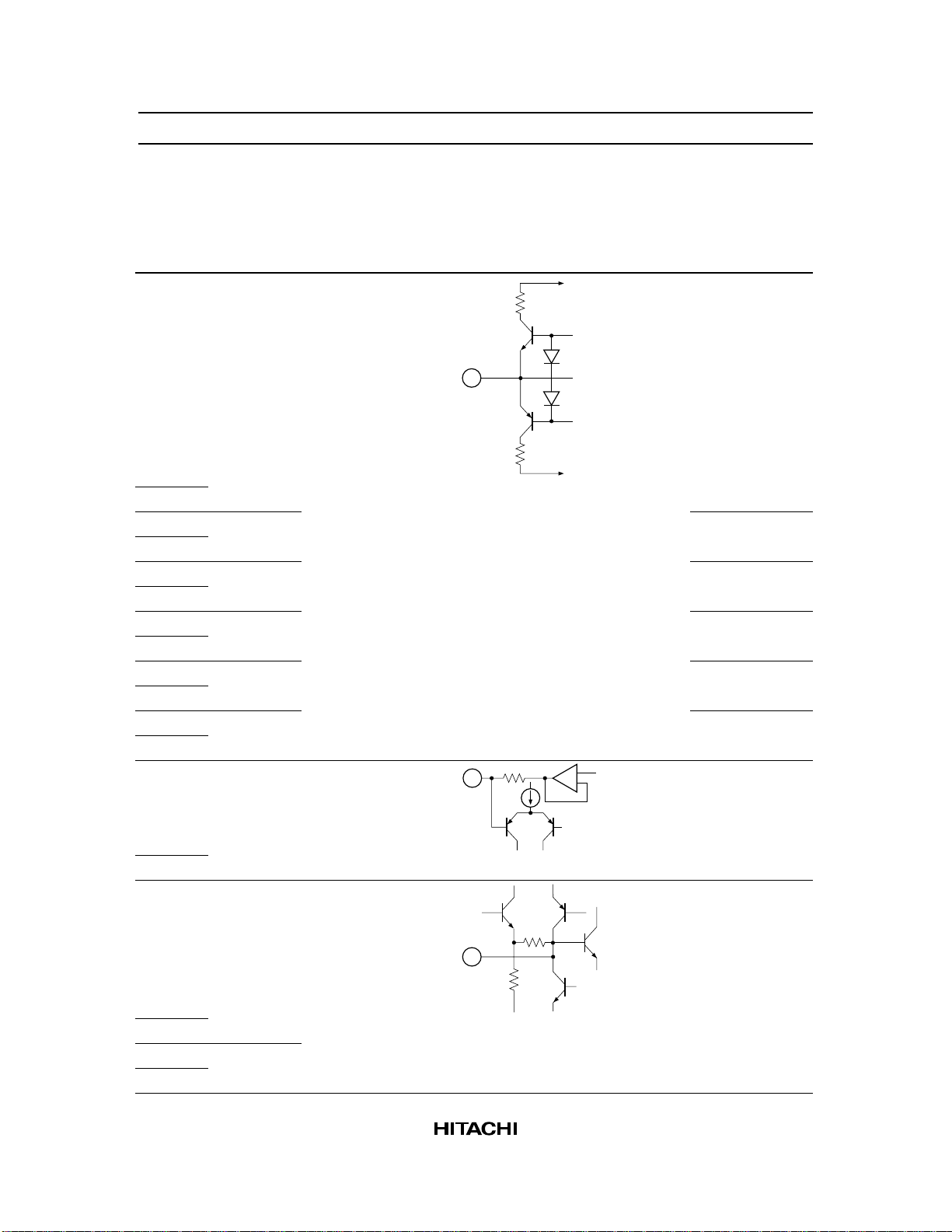

TA-RW255

EXPLODED VIEW

F567-750

F REC

CMAL2Z226B

Lever for prevent to lever.

(only Left side mecha.)

METAL

PACK

05a

Cr

R REC

CASSETTE MECHANISM

Z001 : CMAL2Z226B (PLAY Deck)

Z002 : CMAL2Z227B (REC/PLAY Deck)

F567-739

05b

PACK

Cr

04

A

A

30

A

A

06

A

A

A

25

29

42

F513-930

A

B

32

B

03a

03b

31

A

F513-931

02

CMAL2Z227B

Lever for prevent to eject

(Both mecha.)

A

: MOLYKOTE EM-60L : CORNING

A

: SCREW LOCK : BOND

B

TA-RW255

Page 5

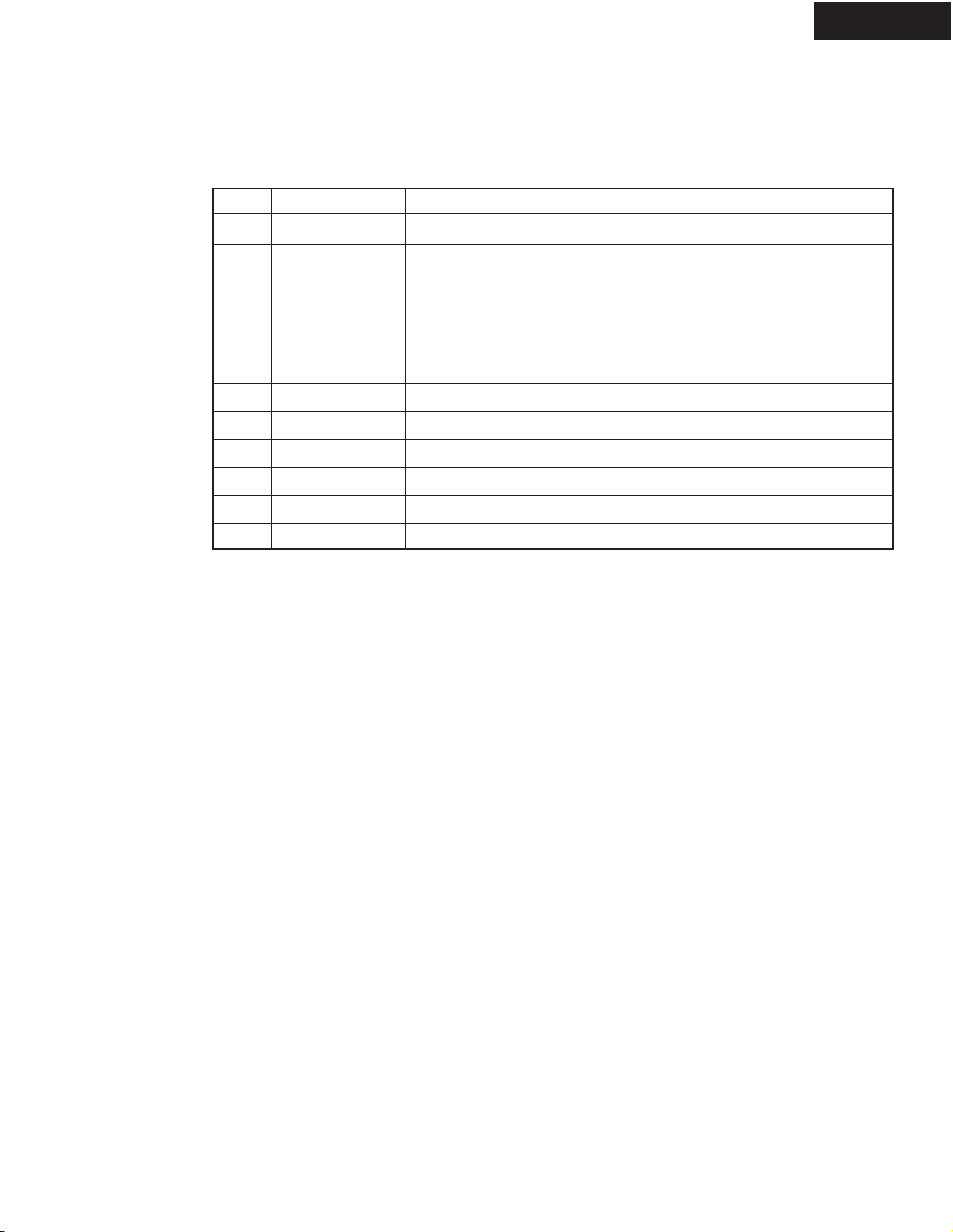

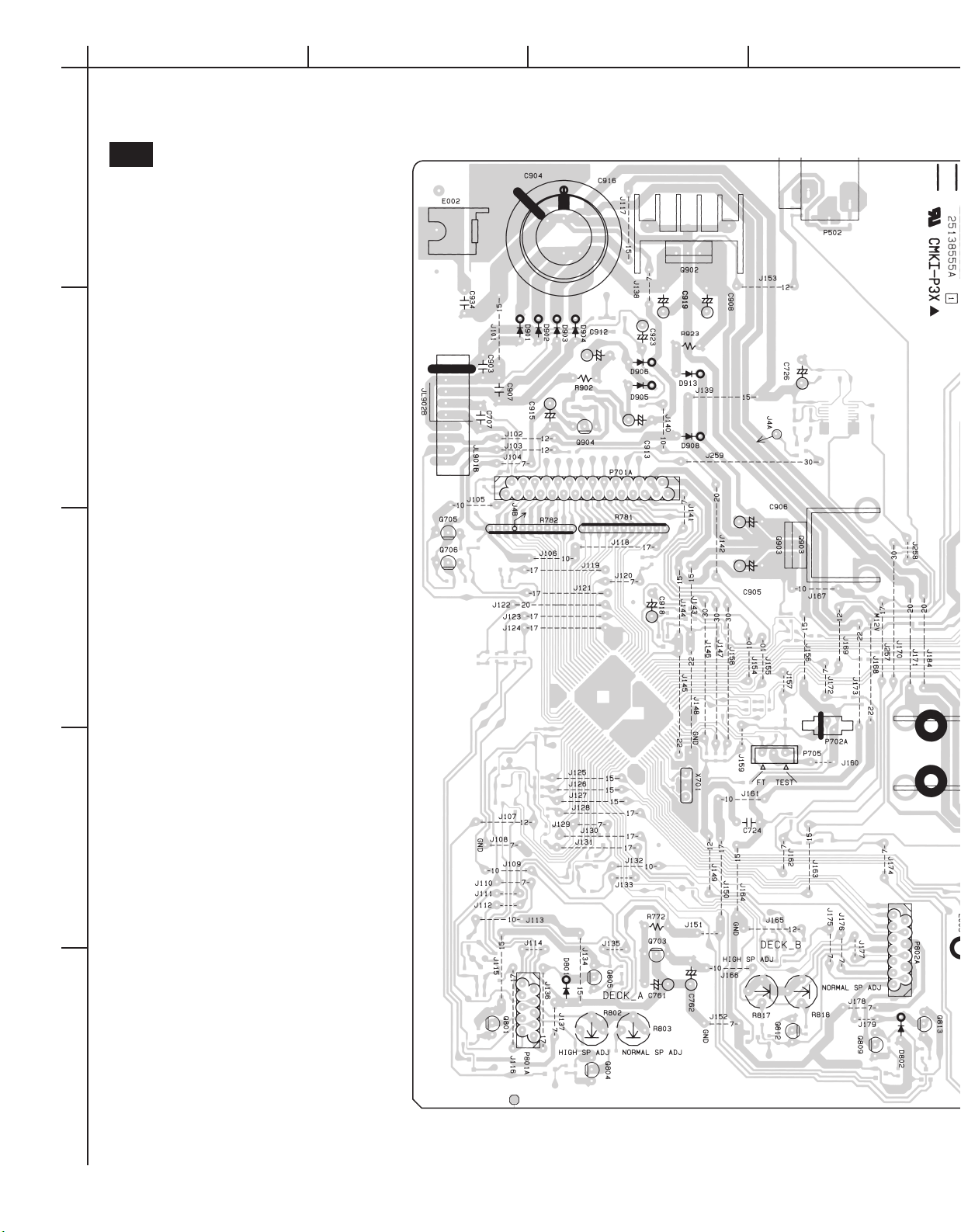

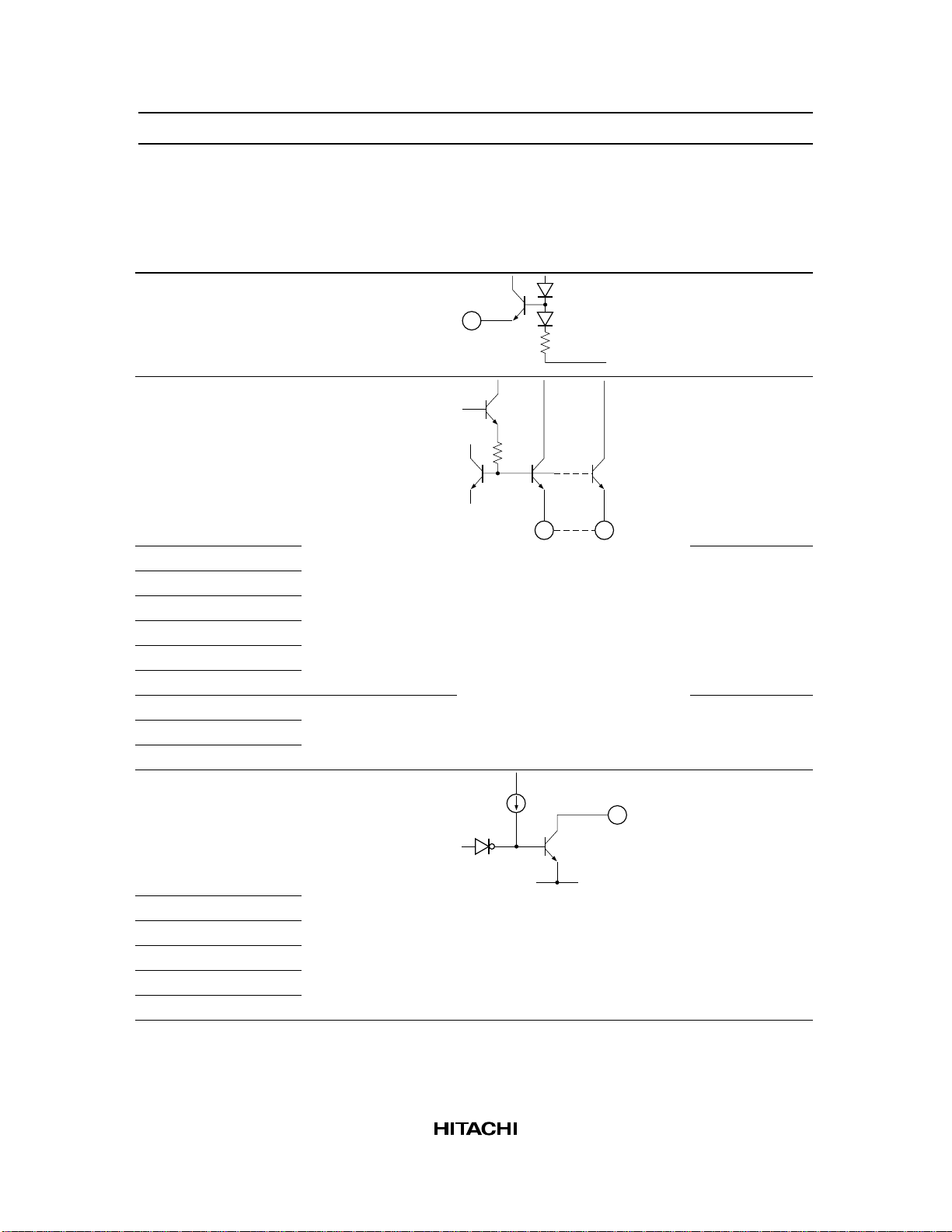

CASSETTE MECHA. PARTS LIST

TA-RW255

No.

03a

03b

04

05a

05b

06

25

29

30

31

32

42

PART No.

F513-931

F513-930

F525-382

F567-739

F567-750

F522-063

FF19N

FR26D-11

FR26B-21

F514-133

F514-134

FF19S

PART NAME

PLATE HEADD BLOCK

PLATE HEADD BLOCK

MOTOR MAIN BLOCK

PCB CONTROL BLOCK

PCB CONTROL BLOCK

CLUTCH ASSY BLOCK

MAIN BELT

ASSY F/W

ASSY F/W

ROLLER PINCH BLOCK R

ROLLER PINCH BLOCK L

F/R BELT

NOTE

226B

227B

226B

227B

F/W Material: ES-5

F/W Material: ES-5 x 2

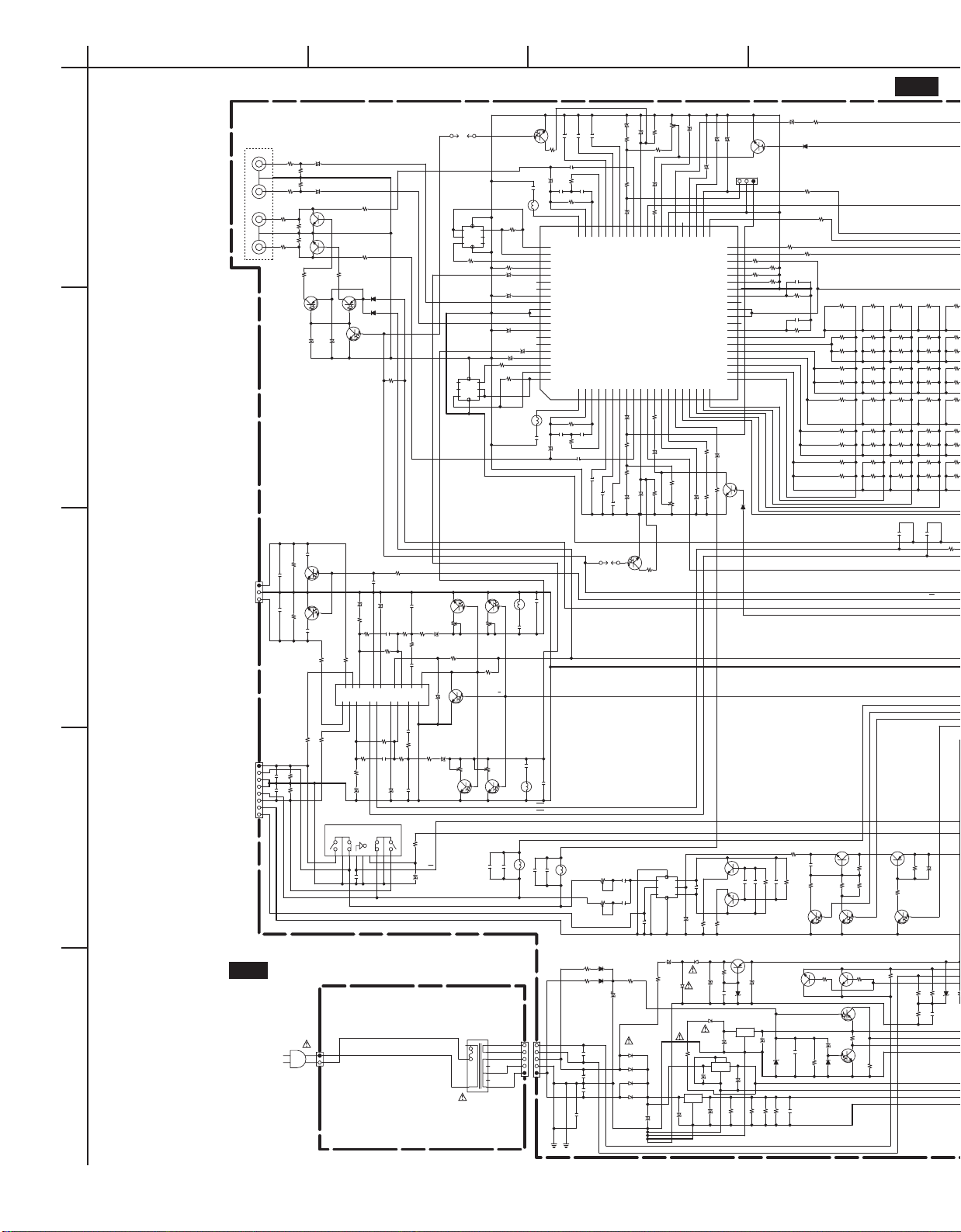

Page 6

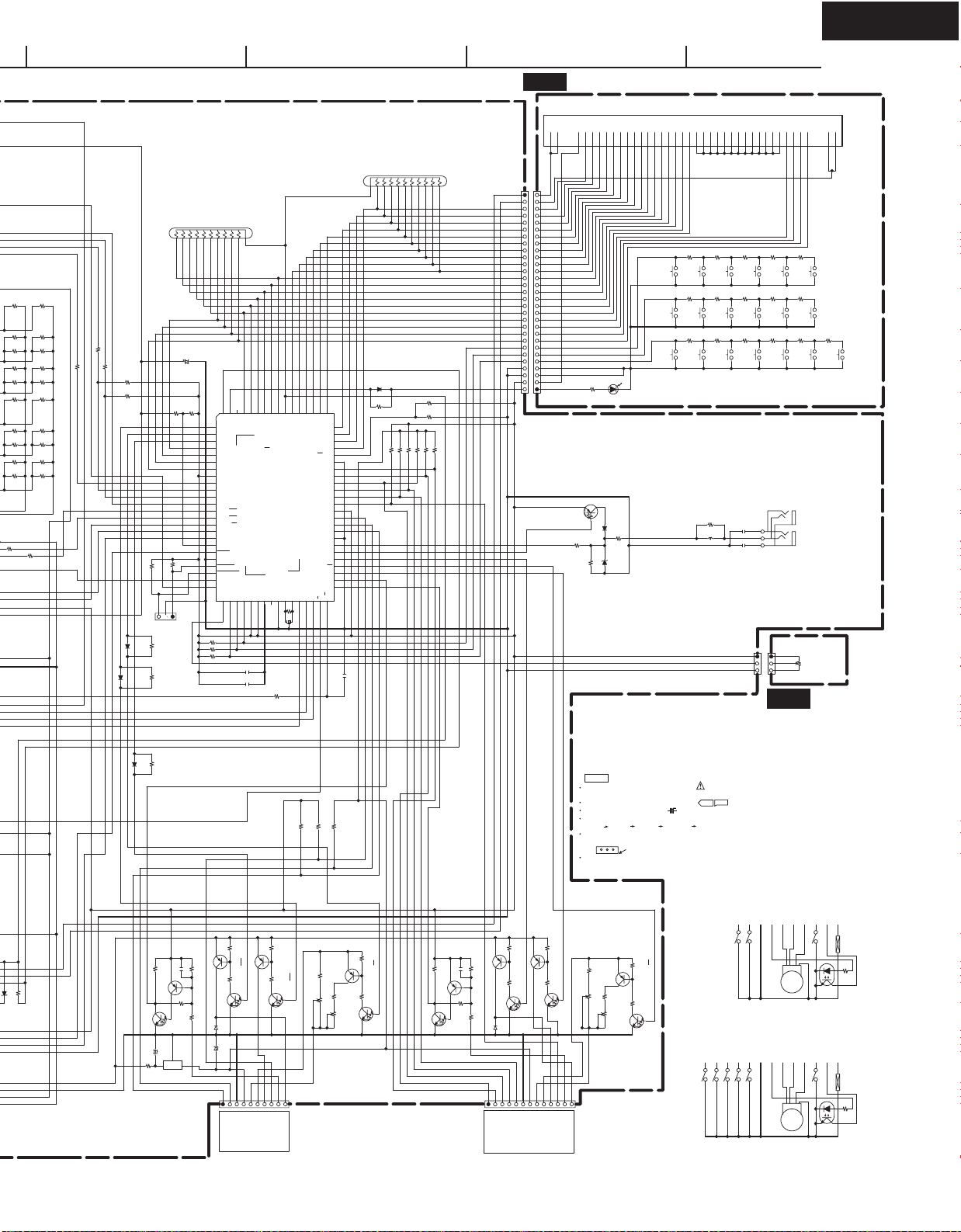

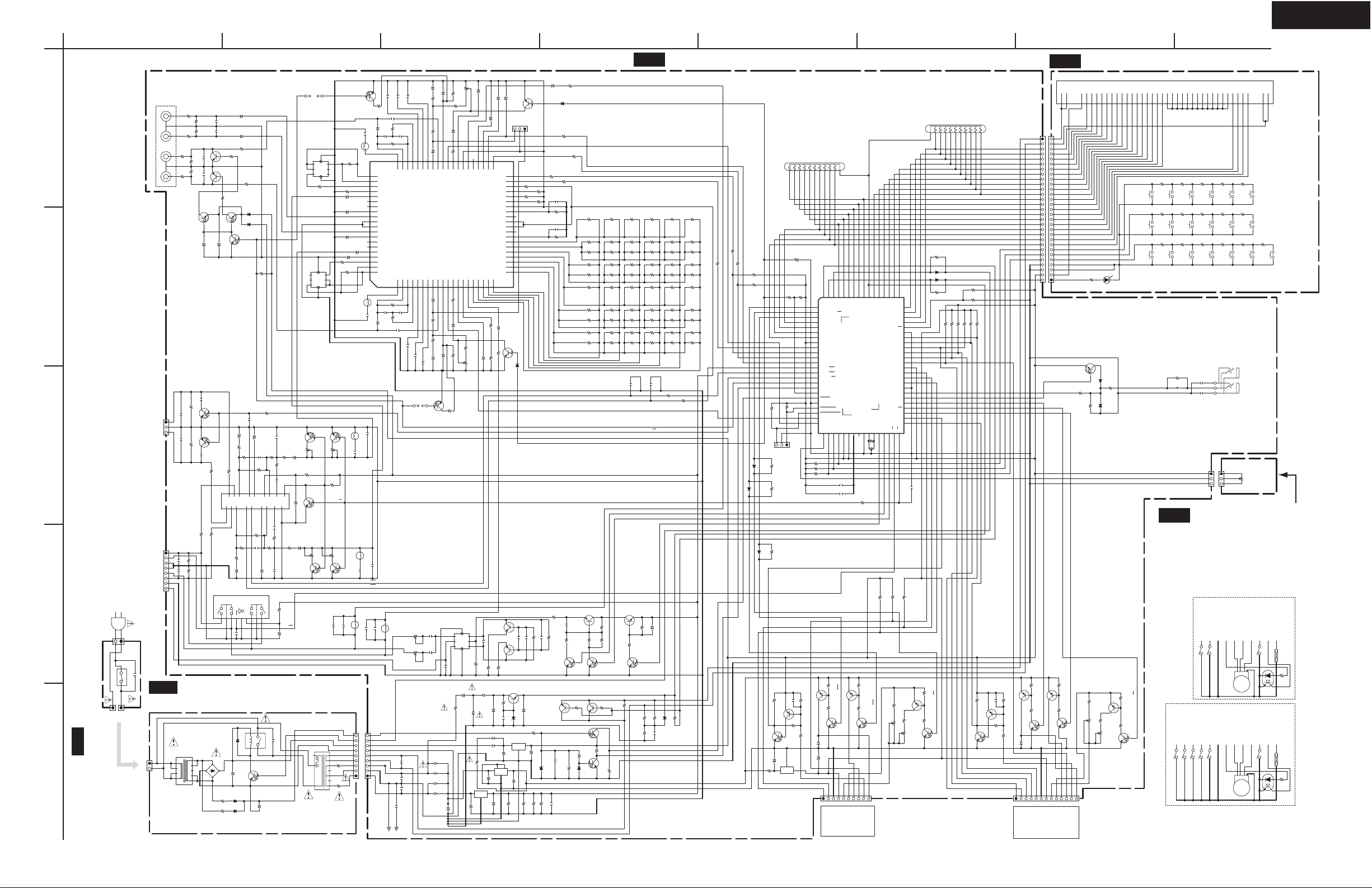

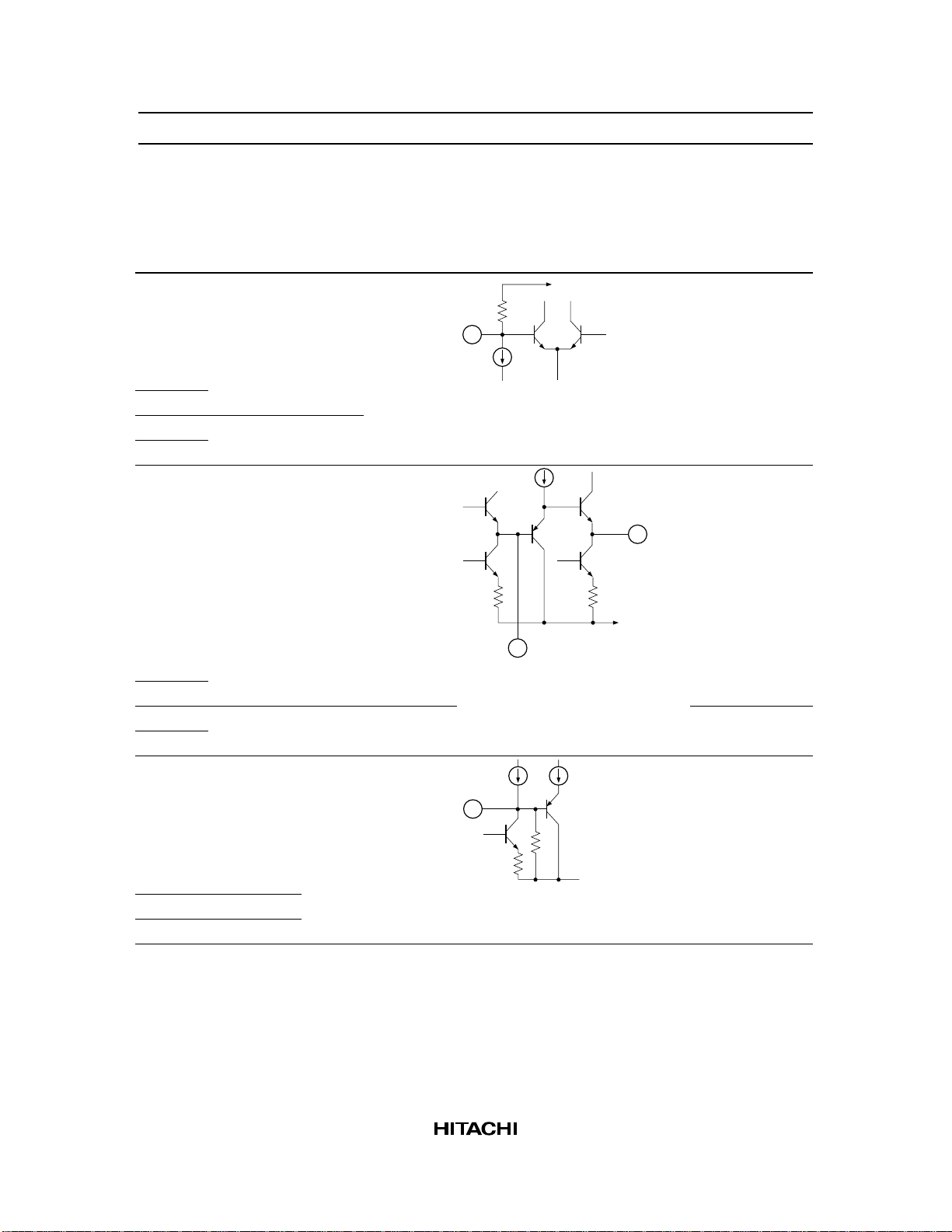

SCHEMATIC

DIAGRAM

<MDD> ONLY

A

1

2

3

4

5

BCDEFGH

BIAS_CTRL

BIAS_NORM

BIAS_H

DECK_B_70/120

DECK_A_70/120

LINE_MUTE

PB_X1/X2

LINE_MUTE

REC/PB

+5V

+12VM

+12VA

-17V

DECK_B/A

A:H/B:L

LCHRCH

A_PB_LCH B_PB_LCH

B_PB_RCH

A_PB_RCH

NAPS-8557

Alternative use C904 or C916.

R405

4.7

R406

4.7

Q407

2SC1959

C105

681

C106

681

R103

100K

R104

100K

C109

333

R109

100K

R111

3.3K

C113

681

R113

3.9K

C111

153

R115

10K

R108

3.9K

C110

333

R110

100K

C112

153

R112

3.3K

C114

681

R116

10K

C123

470/16

+

C126

101

R910

5.6K

R911

5.6K

D601

1SS352

D602

1SS352

R114

3.9K

R224

10K

R220

100K

R214

560

C216

222

C218

104

C220

104

C210

222

R212

22K

C214

104

R229

12K

R211

22K

C211

222

R213

560

C213

104

C219

104

C217

104

C215

222

C209

222

R227

12K

R260

180K

R261

68K

R262

1M

R263

100K

R264

100K

R265

120K

R266

220K

R267

220K

R268

120K

R269

NC

R270

220K

R271

47K

R272

1M

R273

47K

R274

NC

R275

150K

R276

120K

R277

NC

R278

330K

R279

330K

R280

220K

R281

33K

R282

330K

R283

47K

R284

150K

R285

33K

R286

100K

R287

1M

R288

82K

R289

NC

R290

82K

R291

33K

R292

330K

R293

33K

R295

82K

R296

120K

R297

NC

R298

180K

R299

NC

R294

220K

R300

82K

R301

47K

R302

47K

R303

33K

R304

NC

R305

100K

R306

150K

R307

NC

R308

220K

R309

NC

R727

470

C712

104

R751

R416

5.6K

R122

100(1/2W)

R121

4.7K

Q604

KRA107S

R107

3.9K

R408

39K

C404 472

Q406

2SC1959

R415

47K

R410

1K

R414

2.2K

R413

10K

R407

39K

C403 472

Q401

2SB1068

Q403

2SC1959

C206

1/50

+

C205

1/50

+

R231

18K

R241

3.3K

R242

3.3K

R243

6.8K

R244

6.8K

R215

4.7K

R217

3.3K

C223

1/50

+

R216

4.7K

R218

3.3K

C224

1/50

+

C228

2.2/50

+

C227

2.2/50

+

R417

100(1/2W)

Q603

KRA107S

R409

10(1/2W)

R411

820

C406

183

C241

1/50

+

C602

470/16

+

C601

1/50

+

C208

10/16

+

R201

22K

R202

22K

R203

68K

L203

NCH2137

2 1

R228

12K

C229

4.7/50

+

R222

10K

R221

10K

C230

4.7/50

+

R230

12K

C232

4.7/50

+

C231

4.7/50

+

D201

1SS352

D202

1SS352

Q203

RN1411

Q408 uPC1330HA

123

4

CNT

5

GND6VCC

789

L201

NMC6079

3

2

176

5

4

8

L202

NMC6079

6

5

4

8

3

2

1

7

C102

221

R101

100K

C101

221

R102

100K

C104

471

C103

471

C707

104

C918

2.2/50

+

R914

2.2K

R915

2.2K

R909

2.7K

C932

104

R725

22K

Q706

2SD655

R724

22K

Q705

2SD655

R728

0

C911

273

C212

222

C238

331

C237

331

C407

123/100V

C402

101

L403

NLO-2059

3

2

1

8

6

5

4

7

R404

100KB

123

R403

100KB

123

R119

50KB

2

13

R117

50KB

2

13

R118

50KB

2

31

R120

50KB

2

31

Q101 BA3416BL

13579

111315

17

1816141210

864

2

R237

56K

R238

47K

R240

100K

R239

100K

R245

10K

C236

104

C235

104

P205

321

C125

101

C401

101

C409

223

D703

UDZS5.6B

C405 223

R903

3.9K

C914

104

R912

2.2K

R913

2.2K

Q903

78M05

1

I

2

G

3

O

Q901

78M12

1

I

2

G

3

O

R923

10(1/2W)

D907

UDZS18C

D904 1N4003

2 1

D9031N4003

2 1

D902 1N4003

2 1

D9011N4003

2 1

D913

1N4003

2 1

C915

1/50

+

Q904

2SA933S

C910

2200/16

+

P102A

8

7

6

5

4

3

2

1

P101A

1

2

3

L401

4.7mH

NCH2133

2 1

C413

681

C415

680

C414

681

C416

680

Q902

7812

1

I

4

2

G

5

3

O

D911

1SS352

D905

1N4003

1 2

R924

680

R925

680

R926

680

D923

1SS352

D924

1SS352

C923

22/50

R902

1(1/2W)

C912

10/50

+

C913

47/50

+

D906

1N4003

21

Q906

KRA107S

R726

470

R723

22K

Q201

HA12169FB

61

VREF2

62

NRIN2

63

IAOUT2

64

BIAS

65

RPI2

66

VRI32

67

VRI22

68

CONT2

69

VRI12

70

GND22

71

GND11

72

VRI11

73

CONT1

74

VRI21

75

VRI31

76

RPI1

77

REF1

78

IAOUT1

79

NRIN1

80

VREF1

1

BIASTRAP12PBOUT13SS114SS215CCR16HLS17LLS18RECOUT19LMIN1

10

LMDET111LMOUT112EQIN113EQCONT114IREF15EQOUT116NN17NH18NM19HN20HH

21

HM

22

GP

23

GL

24

GH

25

F/Q

26

FQ

27

FM

28

BIASCONT1

29

DACOUT1

30

VCC

31

VCC

32

DACOUT2

33

BIASCONT2

34

GND

35

BIASADJN

36

BIASADJM

37

BIASADJH

38

INJ

39

CLK

40

DATA

41

STB

42

RESET

43

MPX

44

C/B

45

NRONOFF

46

EQOUT2

47

DGND

48

EQCONT2

49

EQIN2

50

LMOUT2

51

LMDET2

52

LMIN2

53

RECOUT2

54

LLS2

55

HLS2

56

CCR2

57

SS2258SS12

59

PBOUT2

60

BIASTRAP2

R236

47K

R235

3.3K

R105

33

R106

33

C108

470/6.3

+

R226

20KB

1

2

3

R123

560

R223

10K

R225

20KB

2

1 3

R219

100K

C128

223

Q204

RN1411

L204

NCH2137

1 2

C764

223

C763

223

R753

3.3K

R601

2.2K

R232

0

R233

0

R234

0

C127

104

C233

0.1/50

+

C919

100/25

+

R314

56

R313

56

R204

68K

J2A

1

J2B

1

J1A

1

J1B

1

E002 E001

C903

104

C907

104

C934

223

Q102

KRC107S

Q103

KRC107S

Q104

KRC107S

Q905

KRC107S

Q404

KRC107S

Q605

KRC107S

Q105

KRC107S

Q402

KRC107S

Q405

KRC107S

Q107

KRC107S

Q108

KRC107S

Q206

KRC107S

Q205

KRC107S

C107

470/6.3

+

C115

10/50

+

C116

10/50

+

C122

10/50

+

C121

22/50

+

C202

10/50

+

C201

10/50

+

C203

10/50

+

C204

10/50

+

C207

10/50

+

C221

100/25

+

C222

100/25

+

C226

10/50

+

C225

10/50

+

C239

10/50

+

C240

10/50

+

C408

10/50

+

C410

22/50

+

C411

220/25

+

C905

10/50

+

C906

100/25

+

C908

220/25

+

C909

10/50

+

P201

2

1

3

5

4

6

JL902A

5

4

3

2

1

JL902B

1

2

3

4

5

T901

NPT-1523D

6

5

2 15

14

NC

13

12

NC

11

10

9

D910

UDZS5.6B

L101

NCH2137

1 2

C117

331

L402

4.7mH

NCH2133

2 1

P901

2

1

P901A

C118

331

Q106

KRC107S

L102

NCH2137

2

1

R206

1K

R205

1K

R207

6.8K

R208

6.8K

Q602

2SD655

Q601

2SD655

R315

100

R316

100

R209

2.2K

R210

2.2K

R125

470

R126

470

R127

470

R128

470

C904

13000/25

+

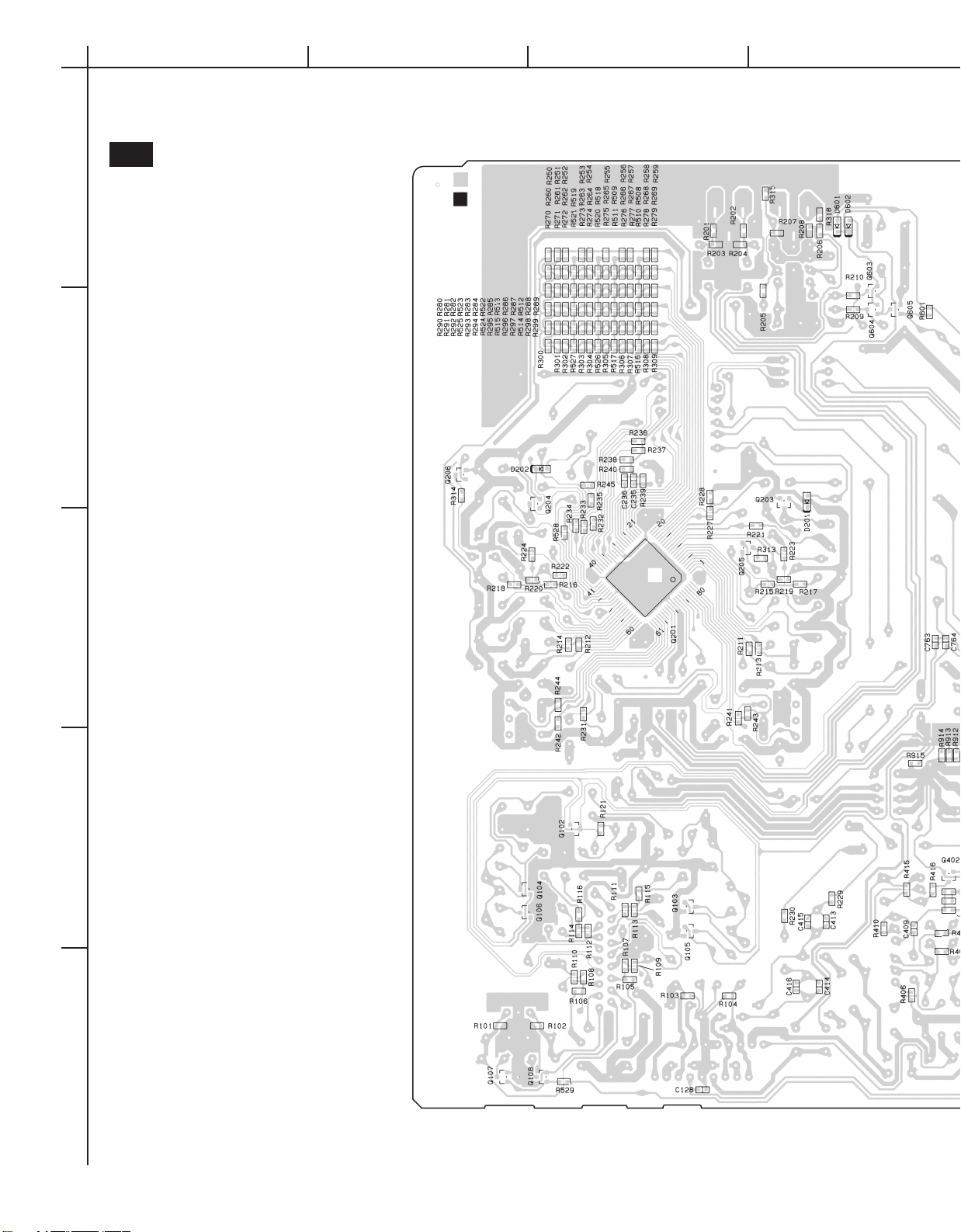

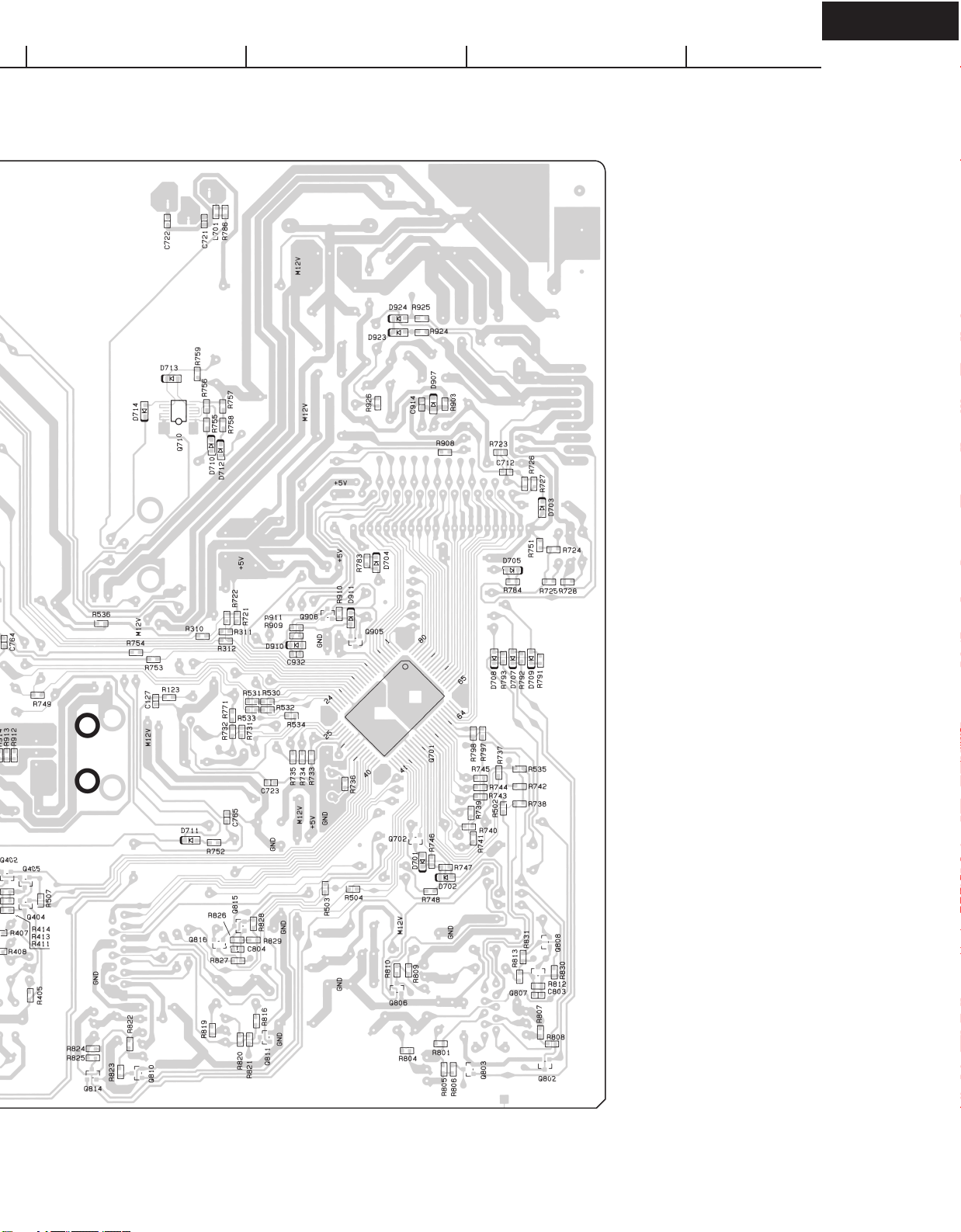

U01 MAIN PC BOARD NAAF-8555

U03

POWER SUPPLY PC BOARD

NC

NC

NC

NC

NC

NC

DECK A

DECK B

Page 7

TA-RW255

P-OFF

RESET

SOL_A_ON/OFF

CAP_A_X1/X2

CAP_A_ON/OFF

CAP_B_X1/X2

SOL_B

CAP_B

REC_MUTE

SIG_L

SIG_RCH

1G

4G

P15

P10P9P8P7P6P5P4P3P2

P1

1G2G3G

4G

P15

P14

P13

P12

P11

P10

P9

P8

P7

P6

P5

P4

P3

P2

P1

1G

2G

3G

4G

KEY0

KEY1

KEY2

HIGH SW

PACK SW

REC INH FWD

FM

FQ

F/Q

GH

GL

GP

N.NORMN.HIGHN.MTLH.NORMH.HIGHH.MTL

HIGH SPEED

NORM SPEED

NORM SPEED

HIGH SPEED

TEST_MODE

DECK A

REC INH REV

METAL SW

MOTOR +

MOTOR B

MOTOR A

ROT PH DIODE

MOTER -

FT

PACK SW

HIGH SW

MOTER -

ROT PH DIODE

MOTOR A

MOTOR B

MOTOR +

PLAY SW

ROT PH OUT A

SOLENOID

ROT PH OUT B

SOLENOID

PLAY SW

DECK B

NAAF-8555

F-PLAY R-PLAY DOLBY_NRREWFFSTOP

DECK_B

STOP B-FF B-REW B_F-PLAY B_R-PLAY REV_MODE

STBY

ON/OFF

REC_PAUSE

AUTO_SPACE

NORM_DUBB

HIGH_DUBB

COUNTER

RESET

COUNTER

A/B

DECK_A

NADIS-8556

NAETC-8558

INPUT VR

BA-+

MOTOR

DECK B

BA-+

MOTOR

SOL

SOL

DECK A

OTP ONLY

OTP ONLY

7

+5V SENSOR

6

MOTOR A5MOTOR B

8

MOTOR- COM

9

HIGH SW

10

PACK SW

11

REC INH FWD

12

REC INH REV

13

METAL SW

4

MOTOR+

3

PLAY SW

2

ROT PHT OUT

1

SOLENOID

7

+5V SENSOR

6

MOTOR A5MOTOR B

4

MOTOR+

3

PLAY SW

2

ROT PHT OUT

1

SOLENOID

8

MOTOR- COM

9

HIGH SW

10

PACK SW

R823

3.9K

R825

3.9K

R826

18K

C804

223

R250

100K

R251

56K

R252

NC

R253

56K

R254

NC

R255

56K

R256

82K

R257

NC

R258

100K

R259

NC

R260

180K

R261

68K

R262

1M

R263

100K

R264

100K

R265

120K

R266

220K

R267

220K

R268

120K

R269

NC

R751

100K

Q809 2SB1068

R822

47K

R824

47K

R829

1M

R817

2KB

2

3 1

R820

100K

Q812

2SA933S

R807

47K

R808

3.9K

R809

47K

Q805 2SB1068

R810

3.9K

R812

18K

C803

223

R831

1M

R772

180(1/2W)

R805

100K

R802

2KB

2

3 1

Q801

2SB1068

Q804

2SA933S

Q813

2SB1068

R733

2.7K

R734

2.7K

R735

2.7K

R742

4.7K

R738

4.7K

P5021

2

3

C722

104Z

C721

104Z

Q702

KRA107S

D701

1SS352

R748

470

R747

220K

R781100KX10

11

10

987654321

R783

0

R745

4.7K

D704

1SS352

R830

10K

Q815

2SA1037AK

R828

10K

Q807

2SA1037AK

R786

0

L701

BK1608LM182-T

D702

UDZS5.6B

D703

UDZS5.6B

R782 100KX10

123456789

10

11

R791

0

D708

1SS352

D707

1SS352

R792

0

R793

0

P705

1

2

3

D709

1SS352

D801

1N4003

2

1

D802

1N4003

2 1

R731

4.7K

R732

4.7K

R744

4.7K

R743

4.7K

R741

4.7K

R739

4.7K

R740

4.7K

R797

10K

R798

0

P701A

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

R746

47K

P801A

123456789

10

R737

4.7K

Q703

78L05

1I3

O

2

G

P702A

1

2

3

R813

47K

R827

47K

P802A

12345678910111213

R801

6.8K

R816

6.8K

R803

1KB

2

3 1

R818

1KB

2

3 1

R821

10K

R806

10K

R311

10K

R312

10K

R753

3.3K

R754

3.3K

R310

10K

Q701

MPD78042FGF

1

CAP_A

2

CAP_A_X2/X1

3

SOL_A

4

1G

5

2G

6

3G

7

4G

8

VDD

9

DOL_CLK

10

DOL_DATA

11

DOL_STB

12

DOL_RST

13

A_70/120

14

B_70/120

15

PB_X1/X2

16

LINE_MUTE

17

RESET

18

REC MUTE

19

P-OFF

20

AVSS

21

FT_MODE

22

TEST_MODE

23

SIG_LCH

24

SIG_RCH

25

VOL

26

KEY227KEY1

28

KEY029AVDD

30

AVREF

31

XT1/GND32XT2/NC

33

VSS34X135X2

36

BIAS_CONT37N.BIAS38H.BIAS39R/P

40

B/A

41

R.SEN_B

42

R.SEN_A

43

CAP_B

44

CAP_B_X1/X2

45

SOL_B

46

RI_OUT

47

RI_IN

48

IC(VPP)GND

49

A_PACK_SW

50

A_HIGH_SW

51

A_PLY_SW

52

VDD

53

B_PLY_SW

54

B_HIGH_SW

55

B_PACK_SW

56

B_F.REC_INH

57

B_MTL_SW

58

B_R.REC_INH

59

NC

60

SRCH_OFF/ON

61

P16

62

P15

63

P14

64

P13

65

P1266P1167P10

68P969P870P771

VDISP

72P673P574P475P376P277P178

RELAY

79

S_LED

80

FL

R771

2.2K

R721

4.7K

R722

4.7K

R749

1K

C725

22/50

R819

1K

R804

1K

Q811

KRC107S

Q806

KRC107S

Q808

KRC107S

Q803

KRC107S

Q802

KRC107S

Q810

KRC107S

Q814

KRC107S

Q816

KRC107S

C761

10/50

+

C762

10/50

+

X701

CSTLS5M00

R736

NC

R752

3.3K

C765

223

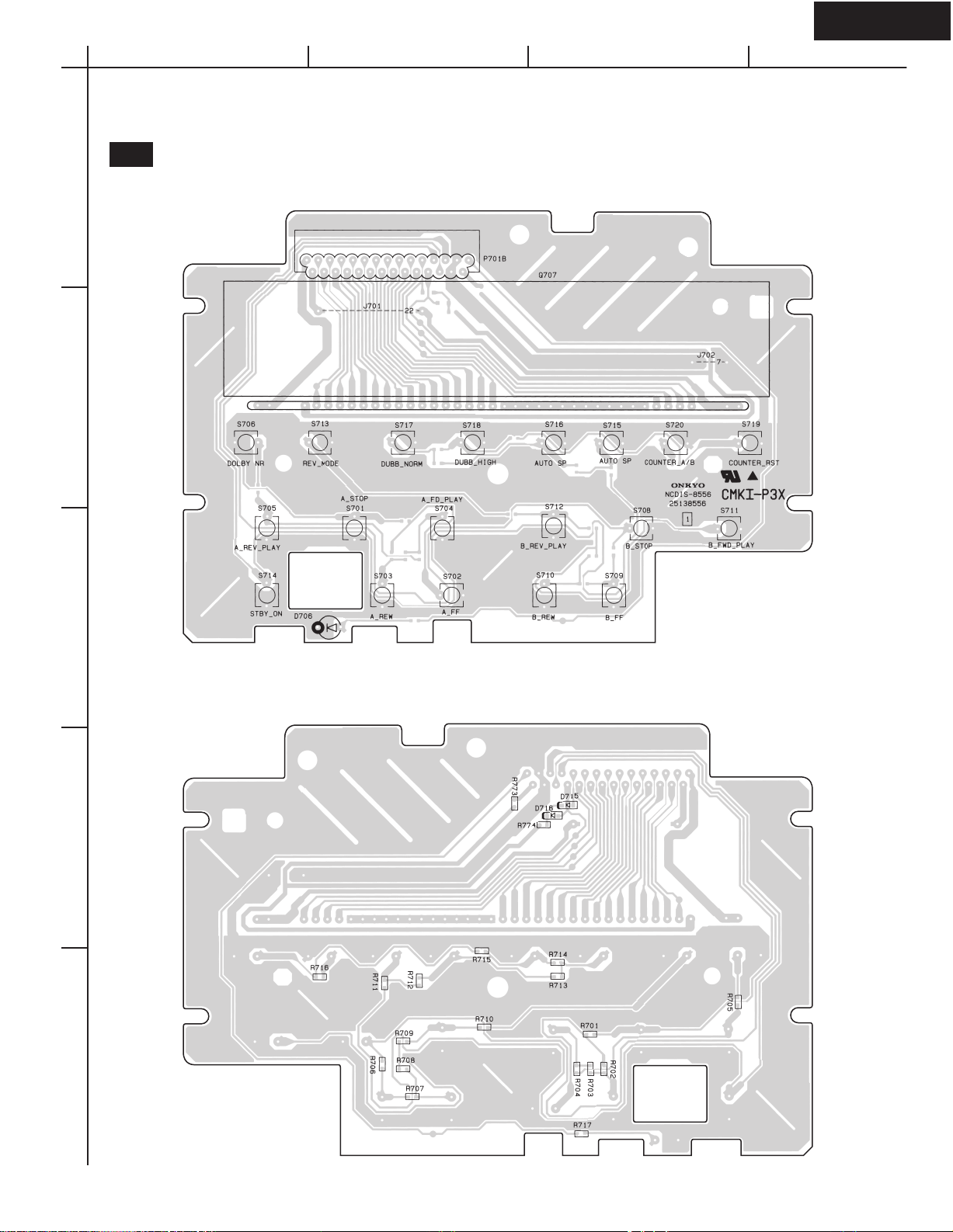

S704

S705

S708

S710

S711

S712

S713

S714

S715

S716

S717

S719

S718

R702

470

R703

820

R7041KR705

1.8K

R706

390

R707

470

R708

820

R7091KR710

1.8K

R711

390

R712

470

R713

820

R7141KR715

1.8K

S702S709

R701

390

S703

R716

3.9K

S720

S706

S701

R717

3.9K

D706

SLI-343URC-TE7

Q707 BJ246GK

1

F112F125P176P167P158P149P13

10

P1211P1112P1013P914P815P716P617P518P419P320P221P122NC23NC24NC25NC26NC27NC28NC29NC30NC31NC32NC33NC34NC351G362G373G384G41F2142F22

P701B

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

R761

20KB

2

1

3

P702B

3

2

1

C723

104

C724

223

THE COMPONENTS IDENTIFIED BY MARK ARE CRITICAL FOR SAFETY.

REPLACE ONLY WITH PART NUMBER SPECIFIED.

VOLTAGE (MEASURED WITH VOLTMETER) IS DC VOLTAGE. (NO INPUT SIGNAL)

ELECTROLYTIC CAPACITORS ARE IN uF/WV.

ALL CAPACITORS ARE IN pF/50WV UNLESS OTHERWISE NOTED.

EX) 030 3pF 330 33pF 331 330pF 333 0.033uF

ALL RESISTORS ARE IN OHMS 1/4WATTS UNLESS OTHERWISE NOTED.

THE THICK LINES ON PC BOARD ARE THE PRINTING SIDE OF THE PARTS.

EX) PRINTING SIDE

CIRCUIT IS SUBJECT TO CHANGE FOR IMPROVEMENT.

NOTE

( )

NAAF-8555

U02

DISPLAY CIRCUIT PC BOARD

NADIS-8556

U04

INPUT VOLUME

PC BOARD

NAETC-8558

Page 8

TA-RW255

SCHEMATIC

DIAGRAM

<MDD> ONLY

A

1

2

3

4

5

BCDEFGH

BIAS_CTRL

BIAS_NORM

BIAS_H

P-OFF

RESET

DECK_B_70/120

DECK_A_70/120

LINE_MUTE

PB_X1/X2

LINE_MUTE

SOL_A_ON/OFF

CAP_A_X1/X2

CAP_A_ON/OFF

REC/PB

CAP_B_X1/X2

SOL_B

CAP_B

+5V

+12VM

REC_MUTE

+12VA

-17V

SIG_L

SIG_RCH

DECK_B/A

1G

4G

P15

P10P9P8P7P6P5P4P3P2

P1

1G2G3G

4G

P15

P14

P13

P12

P11

P10

P9

P8

P7

P6

P5

P4

P3

P2

P1

1G

2G

3G

4G

KEY0

KEY1

KEY2

HIGH SW

PACK SW

REC INH FWD

FM

FQ

F/Q

GH

GL

GP

N.NORMN.HIGHN.MTLH.NORMH.HIGHH.MTL

A:H/B:L

HIGH SPEED

NORM SPEED

LCHRCH

A_PB_LCH B_PB_LCH

B_PB_RCH

A_PB_RCH

NORM SPEED

HIGH SPEED

TEST_MODE

DECK A

REC INH REV

METAL SW

MOTOR +

MOTOR B

MOTOR A

ROT PH DIODE

MOTER -

FT

PACK SW

HIGH SW

MOTER -

ROT PH DIODE

MOTOR A

MOTOR B

MOTOR +

PLAY SW

ROT PH OUT A

SOLENOID

ROT PH OUT B

SOLENOID

PLAY SW

DECK B

NAAF-8555

F-PLAY R-PLAY DOLBY_NRREWFFSTOP

DECK_B

STOP B-FF B-REW B_F-PLAY B_R-PLAY REV_MODE

STBY

ON/OFF

REC_PAUSE

AUTO_SPACE

NORM_DUBB

HIGH_DUBB

COUNTER

RESET

COUNTER

A/B

DECK_A

NADIS-8556

NAETC-8558

INPUT VR

NAPS-8557

BA-+

MOTOR

DECK B

BA-+

MOTOR

SOL

SOL

DECK A

Alternative use C904 or C916.

OTP ONLY

OTP ONLY

7

+5V SENSOR

6

MOTOR A5MOTOR B

8

MOTOR- COM

9

HIGH SW

10

PACK SW

11

REC INH FWD

12

REC INH REV

13

METAL SW

4

MOTOR+

3

PLAY SW

2

ROT PHT OUT

1

SOLENOID

7

+5V SENSOR

6

MOTOR A5MOTOR B

4

MOTOR+

3

PLAY SW

2

ROT PHT OUT

1

SOLENOID

8

MOTOR- COM

9

HIGH SW

10

PACK SW

R405

4.7

R406

4.7

Q407

2SC1959

C105

681

C106

681

R103

100K

R104

100K

C109

333

R109

100K

R111

3.3K

C113

681

R113

3.9K

C111

153

R115

10K

R108

3.9K

C110

333

R110

100K

C112

153

R112

3.3K

C114

681

R116

10K

C123

470/16

+

C126

101

R823

3.9K

R825

3.9K

R826

18K

C804

223

R910

5.6K

R911

5.6K

D601

1SS352

D602

1SS352

R114

3.9K

R224

10K

R220

100K

R214

560

C216

222

C218

104

C220

104

C210

222

R212

22K

C214

104

R229

12K

R211

22K

C211

222

R213

560

C213

104

C219

104

C217

104

C215

222

C209

222

R227

12K

R250

100K

R251

56K

R252

NC

R253

56K

R254

NC

R255

56K

R256

82K

R257

NC

R258

100K

R259

NC

R260

180K

R261

68K

R262

1M

R263

100K

R264

100K

R265

120K

R266

220K

R267

220K

R268

120K

R269

NC

R270

220K

R271

47K

R272

1M

R273

47K

R274

NC

R275

150K

R276

120K

R277

NC

R278

330K

R279

330K

R280

220K

R281

33K

R282

330K

R283

47K

R284

150K

R285

33K

R286

100K

R287

1M

R288

82K

R289

NC

R290

82K

R291

33K

R292

330K

R293

33K

R295

82K

R296

120K

R297

NC

R298

180K

R299

NC

R294

220K

R300

82K

R301

47K

R302

47K

R303

33K

R304

NC

R305

100K

R306

150K

R307

NC

R308

220K

R309

NC

R727

470

C712

104

R751

100K

R416

5.6K

Q809 2SB1068

R822

47K

R824

47K

R829

1M

R122

100(1/2W)

R121

4.7K

Q604

KRA107S

R817

2KB

2

3 1

R820

100K

Q812

2SA933S

R807

47K

R808

3.9K

R809

47K

Q805 2SB1068

R810

3.9K

R812

18K

C803

223

R107

3.9K

R408

39K

C404 472

Q406

2SC1959

R415

47K

R410

1K

R414

2.2K

R413

10K

R407

39K

C403 472

Q401

2SB1068

Q403

2SC1959

C206

1/50

+

C205

1/50

+

R231

18K

R241

3.3K

R242

3.3K

R243

6.8K

R244

6.8K

R215

4.7K

R217

3.3K

C223

1/50

+

R216

4.7K

R218

3.3K

C224

1/50

+

C228

2.2/50

+

C227

2.2/50

+

R417

100(1/2W)

Q603

KRA107S

R409

10(1/2W)

R411

820

C406

183

R831

1M

C241

1/50

+

C602

470/16

+

C601

1/50

+

C208

10/16

+

R201

22K

R202

22K

R203

68K

L203

NCH2137

2 1

R228

12K

C229

4.7/50

+

R222

10K

R221

10K

C230

4.7/50

+

R230

12K

C232

4.7/50

+

C231

4.7/50

+

D201

1SS352

D202

1SS352

Q203

RN1411

Q408 uPC1330HA

123

4

CNT

5

GND6VCC

789

L201

NMC6079

3

2

176

5

4

8

L202

NMC6079

6

5

4

8

3

2

1

7

C102

221

R101

100K

C101

221

R102

100K

C104

471

C103

471

C707

104

C918

2.2/50

+

R914

2.2K

R915

2.2K

R909

2.7K

C932

104

R725

22K

Q706

2SD655

R724

22K

Q705

2SD655

R728

0

C911

273

C212

222

C238

331

C237

331

C407

123/100V

C402

101

L403

NLO-2059

3

2

1

8

6

5

4

7

R404

100KB

123

R403

100KB

123

R119

50KB

2

13

R117

50KB

2

13

R118

50KB

2

31

R120

50KB

2

31

R772

180(1/2W)

Q101 BA3416BL

13579

111315

17

1816141210

864

2

R805

100K

R802

2KB

2

3 1

Q801

2SB1068

Q804

2SA933S

Q813

2SB1068

R733

2.7K

R734

2.7K

R735

2.7K

R742

4.7K

R738

4.7K

P5021

2

3

C722

104Z

C721

104Z

Q702

KRA107S

D701

1SS352

R748

470

R747

220K

R781100KX10

11

10

987654321

R783

0

R745

4.7K

D704

1SS352

R830

10K

Q815

2SA1037AK

R828

10K

Q807

2SA1037AK

R786

0

L701

BK1608LM182-T

R237

56K

R238

47K

R240

100K

R239

100K

R245

10K

C236

104

C235

104

P205

321

C125

101

C401

101

C409

223

D702

UDZS5.6B

D703

UDZS5.6B

R782 100KX10

123456789

10

11

R791

0

D708

1SS352

D707

1SS352

R792

0

R793

0

P705

1

2

3

D709

1SS352

D801

1N4003

2

1

D802

1N4003

2 1

C405 223

R903

3.9K

C914

104

R912

2.2K

R913

2.2K

Q903

78M05

1

I

2

G

3

O

Q901

78M12

1

I

2

G

3

O

R923

10(1/2W)

D907

UDZS18C

D904 1N4003

2 1

D9031N4003

2 1

D902 1N4003

2 1

D9011N4003

2 1

D913

1N4003

2 1

C915

1/50

+

Q904

2SA933S

C910

2200/16

+

R731

4.7K

R732

4.7K

R744

4.7K

R743

4.7K

R741

4.7K

R739

4.7K

R740

4.7K

R797

10K

R798

0

P701A

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

P102A

8

7

6

5

4

3

2

1

P101A

1

2

3

R746

47K

P801A

123456789

10

L401

4.7mH

NCH2133

2 1

C413

681

C415

680

C414

681

C416

680

Q902

7812

1

I

4

2

G

5

3

O

D911

1SS352

D905

1N4003

1 2

R924

680

R925

680

R926

680

D923

1SS352

D924

1SS352

C923

22/50

R737

4.7K

Q703

78L05

1I3

O

2

G

P702A

1

2

3

R902

1(1/2W)

C912

10/50

+

C913

47/50

+

D906

1N4003

21

Q906

KRA107S

R726

470

R723

22K

Q201

HA12169FB

61

VREF2

62

NRIN2

63

IAOUT2

64

BIAS

65

RPI2

66

VRI32

67

VRI22

68

CONT2

69

VRI12

70

GND22

71

GND11

72

VRI11

73

CONT1

74

VRI21

75

VRI31

76

RPI1

77

REF1

78

IAOUT1

79

NRIN1

80

VREF1

1

BIASTRAP12PBOUT13SS114SS215CCR16HLS17LLS18RECOUT19LMIN1

10

LMDET111LMOUT112EQIN113EQCONT114IREF15EQOUT116NN17NH18NM19HN20HH

21

HM

22

GP

23

GL

24

GH

25

F/Q

26

FQ

27

FM

28

BIASCONT1

29

DACOUT1

30

VCC

31

VCC

32

DACOUT2

33

BIASCONT2

34

GND

35

BIASADJN

36

BIASADJM

37

BIASADJH

38

INJ

39

CLK

40

DATA

41

STB

42

RESET

43

MPX

44

C/B

45

NRONOFF

46

EQOUT2

47

DGND

48

EQCONT2

49

EQIN2

50

LMOUT2

51

LMDET2

52

LMIN2

53

RECOUT2

54

LLS2

55

HLS2

56

CCR2

57

SS2258SS12

59

PBOUT2

60

BIASTRAP2

R236

47K

R235

3.3K

R813

47K

R827

47K

P802A

12345678910111213

R801

6.8K

R816

6.8K

R803

1KB

2

3 1

R818

1KB

2

3 1

R821

10K

R806

10K

R105

33

R106

33

C108

470/6.3

+

R226

20KB

1

2

3

R311

10K

R312

10K

R123

560

R223

10K

R225

20KB

2

1 3

R219

100K

C128

223

Q204

RN1411

L204

NCH2137

1 2

C764

223

C763

223

R753

3.3K

R754

3.3K

R601

2.2K

R232

0

R233

0

R234

0

C127

104

R310

10K

C233

0.1/50

+

C919

100/25

+

Q701

MPD78042FGF

1

CAP_A

2

CAP_A_X2/X1

3

SOL_A

4

1G

5

2G

6

3G

7

4G

8

VDD

9

DOL_CLK

10

DOL_DATA

11

DOL_STB

12

DOL_RST

13

A_70/120

14

B_70/120

15

PB_X1/X2

16

LINE_MUTE

17

RESET

18

REC MUTE

19

P-OFF

20

AVSS

21

FT_MODE

22

TEST_MODE

23

SIG_LCH

24

SIG_RCH

25

VOL

26

KEY227KEY1

28

KEY029AVDD

30

AVREF

31

XT1/GND32XT2/NC

33

VSS34X135X2

36

BIAS_CONT37N.BIAS38H.BIAS39R/P

40

B/A

41

R.SEN_B

42

R.SEN_A

43

CAP_B

44

CAP_B_X1/X2

45

SOL_B

46

RI_OUT

47

RI_IN

48

IC(VPP)GND

49

A_PACK_SW

50

A_HIGH_SW

51

A_PLY_SW

52

VDD

53

B_PLY_SW

54

B_HIGH_SW

55

B_PACK_SW

56

B_F.REC_INH

57

B_MTL_SW

58

B_R.REC_INH

59

NC

60

SRCH_OFF/ON

61

P16

62

P15

63

P14

64

P13

65

P1266P1167P10

68P969P870P771

VDISP

72P673P574P475P376P277P178

RELAY

79

S_LED

80

FL

R771

2.2K

R721

4.7K

R722

4.7K

R749

1K

C725

22/50

R314

56

R313

56

R204

68K

J2A

1

J2B

1

J1A

1

J1B

1

E002 E001

C903

104

C907

104

C934

223

R819

1K

R804

1K

Q102

KRC107S

Q103

KRC107S

Q104

KRC107S

Q905

KRC107S

Q404

KRC107S

Q605

KRC107S

Q811

KRC107S

Q806

KRC107S

Q808

KRC107S

Q105

KRC107S

Q402

KRC107S

Q405

KRC107S

Q107

KRC107S

Q108

KRC107S

Q803

KRC107S

Q802

KRC107S

Q810

KRC107S

Q814

KRC107S

Q816

KRC107S

Q206

KRC107S

Q205

KRC107S

C107

470/6.3

+

C115

10/50

+

C116

10/50

+

C122

10/50

+

C121

22/50

+

C202

10/50

+

C201

10/50

+

C203

10/50

+

C204

10/50

+

C207

10/50

+

C221

100/25

+

C222

100/25

+

C226

10/50

+

C225

10/50

+

C239

10/50

+

C240

10/50

+

C408

10/50

+

C410

22/50

+

C411

220/25

+

C761

10/50

+

C762

10/50

+

C905

10/50

+

C906

100/25

+

C908

220/25

+

C909

10/50

+

X701

CSTLS5M00

R736

NC

R752

3.3K

C765

223

P201

2

1

3

5

4

6

S704

S705

S708

S710

S711

S712

S713

S714

S715

S716

S717

S719

S718

R702

470

R703

820

R7041KR705

1.8K

R706

390

R707

470

R708

820

R7091KR710

1.8K

R711

390

R712

470

R713

820

R7141KR715

1.8K

S702S709

R701

390

S703

R716

3.9K

S720

S706

S701

R717

3.9K

D706

SLI-343URC-TE7

Q707 BJ246GK

1

F112F125P176P167P158P149P13

10

P1211P1112P1013P914P815P716P617P518P419P320P221P122NC23NC24NC25NC26NC27NC28NC29NC30NC31NC32NC33NC34NC351G362G373G384G41F2142F22

P701B

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

R761

20KB

2

1

3

P702B

3

2

1

JL902A

5

4

3

2

1

JL902B

1

2

3

4

5

T901

NPT-1523D

6

5

2 15

14

NC

13

12

NC

11

10

9

D910

UDZS5.6B

C723

104

C724

223

L101

NCH2137

1 2

C117

331

L402

4.7mH

NCH2133

2 1

P901

2

1

P901A

C118

331

Q106

KRC107S

L102

NCH2137

2

1

R206

1K

R205

1K

R207

6.8K

R208

6.8K

Q602

2SD655

Q601

2SD655

R315

100

R316

100

R209

2.2K

R210

2.2K

R125

470

R126

470

R127

470

R128

470

C904

13000/25

+

THE COMPONENTS IDENTIFIED BY MARK ARE CRITICAL FOR SAFETY.

REPLACE ONLY WITH PART NUMBER SPECIFIED.

VOLTAGE (MEASURED WITH VOLTMETER) IS DC VOLTAGE. (NO INPUT SIGNAL)

ELECTROLYTIC CAPACITORS ARE IN uF/WV.

ALL CAPACITORS ARE IN pF/50WV UNLESS OTHERWISE NOTED.

EX) 030 3pF 330 33pF 331 330pF 333 0.033uF

ALL RESISTORS ARE IN OHMS 1/4WATTS UNLESS OTHERWISE NOTED.

THE THICK LINES ON PC BOARD ARE THE PRINTING SIDE OF THE PARTS.

EX) PRINTING SIDE

CIRCUIT IS SUBJECT TO CHANGE FOR IMPROVEMENT.

NOTE

( )

NAAF-8555

U01 MAIN PC BOARD NAAF-8555

U02

DISPLAY CIRCUIT PC BOARD

NADIS-8556

U04

INPUT VOLUME

PC BOARD

NAETC-8558

U03

POWER SUPPLY PC BOARD

NC

NC

NC

NC

NC

NC

DECK A

DECK B

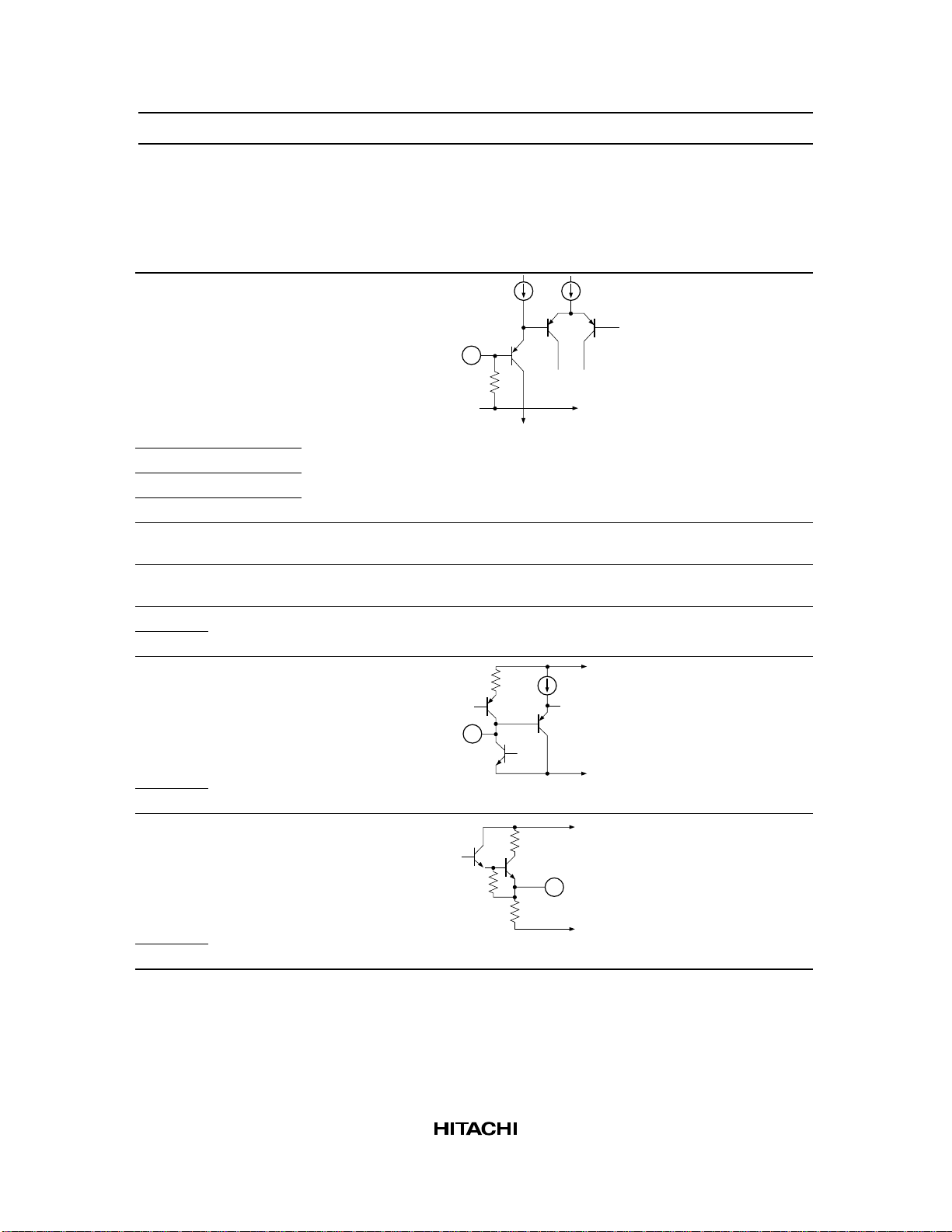

Page 9

BIAS_CTRL

BIAS_NORM

BIAS_H

P-OFF

RESET

DECK_B_70/120

DECK_A_70/120

LINE_MUTE

PB_X1/X2

LINE_MUTE

REC/PB

+5V

+12VM

+12VA

GND_T

-17V

SIG_L

DECK_B/A

N.NORMN.HIGHN.MTLH.NORMH.HIGHH.MTL

A:H/B:L

LCHRCH

A_PB_LCH B_PB_LCH

B_PB_RCHA_PB_RCH

PP,PA MODEL

PP,PA MODEL

NPT-1523P

NPT-1524P

R405

4.7

R406

4.7

Q407

2SC1959

C105

681

C106

681

R103

100K

R104

100K

C109

333

R109

100K

R111

3.3K

C113

681

R113

3.9K

C111

153

R115

10K

R108

3.9K

C110

333

R110

100K

C112

153

R112

3.3K

C114

681

R116

10K

C123

470/16

+

C118

331

R910

5.6K

R911

5.6K

D601

1SS352

D602

1SS352

R114

3.9K

R224

10K

R220

100K

R214

560

C216

222

C218

104

C220

104

C210

222

R212

22K

C214

104

R229

12K

R211

22K

C211

222

R213

560

C213

104

C219

104

C217

104

C215

222

C209

222

R227

12K

R250

100K

R251

56K

R252

NC

R253

56K

R254

NC

R255

56K

R256

82K

R257

NC

R258

100K

R259

NC

R260

180K

R261

68K

R262

1M

R263

100K

R264

100K

R265

120K

R266

220K

R267

220K

R268

120K

R269

NC

R270

220K

R271

47K

R272

1M

R273

47K

R274

NC

R275

150K

R276

120K

R277

NC

R278

330K

R279

330K

R280

220K

R281

33K

R282

330K

R283

47K

R284

150K

R285

33K

R286

100K

R287

1M

R288

82K

R289

NC

R290

82K

R291

33K

R292

330K

R293

33K

R295

82K

R296

120K

R297

NC

R298

180K

R299

NC

R294

220K

R300

82K

R301

47K

R302

47K

R303

33K

R304

NC

R305

100K

R306

150K

R307

NC

R308

220K

R309

NC

R727

470

C712

104

R751

100K

R416

5.6K

R122

100(1/2W)

R121

4.7K

Q604

KRA107S

R107

3.9K

R408

39K

C404 472

Q406

2SC1959

R415

47K

R410

1K

R414

2.2K

R413

10K

R407

39K

C403 472

Q401

2SB1068

Q403

2SC1959

C206

1/50

+

C205

1/50

+

R231

18K

R241

3.3K

R242

3.3K

R243

6.8K

R244

6.8K

R215

4.7K

R217

3.3K

C223

1/50

+

R216

4.7K

R218

3.3K

C224

1/50

+

C228

2.2/50

+

C227

2.2/50

+

R417

100(1/2W)

Q603

KRA107S

R409

10(1/2W)

R411

820

C406

183

C241

1/50

+

C602

470/16

+

C601

1/50

+

C208

10/16

+

L203

NCH2137

2 1

R228

12K

C229

4.7/50

+

R222

10K

R221

10K

C230

4.7/50

+

R230

12K

C232

4.7/50

+

C231

4.7/50

+

D201

1SS352

D202

1SS352

Q203

RN1411

Q408 uPC1330HA

123

4

CNT

5

GND

6

VCC

789

L201

NMC6079

3

2

176

5

4

8

L202

NMC6079

6

5

483

2

1

7

C102

221

R101

100K

C101

221

R102

100K

C104

471

C103

471

C707

104

C918

2.2/50

+

R914

2.2K

R915

2.2K

R908

470

R909

2.7K

C932

104

R725

22K

Q706

2SD655

R724

22K

Q705

2SD655

R728

0

C911

273

C212

222

C238

331

C237

331

C407

123/100V

C402

101

L403

NLO-2059

3

2

186

5

4

7

R404

100KB

123

R403

100KB

123

R119

50KB

2

13

R117

50KB

2

13

R118

50KB

2

31

R120

50KB

2

31

Q101 BA3416BL

13579

11

131517

1816141210

864

2

R237

56K

R238

47K

R240

100K

R239

100K

R245

10K

C236

104

C235

104

P205

321

C401

101

C409

223

D703

UDZS5.6B

C405 223

R903

3.9K

C914

104

R912

2.2K

R913

2.2K

Q903

78M05

1

I

2

G

3

O

Q901

78M12

1

I

2

G

3

O

R923

10(1/2W)

D907

UDZS18C

D908

1N4003

2 1

D904 1N4003

2 1

D9031N4003

2 1

D902 1N4003

2 1

D9011N4003

2 1

D913

1N40032 1

C915

1/50

+

Q904

2SA933S

C910

2200/16

+

P102A

8

7

6

5

4

3

2

1

P101A

1

2

3

L102

NCH2137

2 1

L401

4.7mH

NCH2133

2 1

C413

681

C415

680

C414

681

C416

680

L402

4.7mH

NCH2133

2 1

Q902

7812

1

I

4

2

G

5

3

O

D911

1SS352

D905

1N4003

1 2

R902

1(1/2W)

C912

10/50

+

C913

47/50

+

D906

1N4003

21

Q906

KRA107S

R726

470

R723

22K

Q201

HA12169FB

61

VREF2

62

NRIN2

63

IAOUT2

64

BIAS

65

RPI2

66

VRI32

67

VRI22

68

CONT2

69

VRI12

70

GND22

71

GND11

72

VRI11

73

CONT1

74

VRI21

75

VRI31

76

RPI1

77

REF1

78

IAOUT1

79

NRIN1

80

VREF1

1

BIASTRAP12PBOUT13SS114SS215CCR16HLS17LLS18RECOUT19LMIN1

10

LMDET111LMOUT112EQIN113EQCONT114IREF15EQOUT116NN17NH18NM19HN20HH

21

HM

22

GP

23

GL

24

GH

25

F/Q

26

FQ

27

FM

28

BIASCONT1

29

DACOUT1

30

VCC

31

VCC

32

DACOUT2

33

BIASCONT2

34

GND

35

BIASADJN

36

BIASADJM

37

BIASADJH

38

INJ

39

CLK

40

DATA

41

STB

42

RESET

43

MPX

44

C/B

45

NRONOFF

46

EQOUT2

47

DGND

48

EQCONT2

49

EQIN2

50

LMOUT2

51

LMDET2

52

LMIN2

53

RECOUT2

54

LLS2

55

HLS2

56

CCR2

57

SS2258SS12

59

PBOUT2

60

BIASTRAP2

R236

47K

R235

3.3K

R105

33

R106

33

C108

470/6.3

+

R226

20KB

1

2

3

R123

560

R223

10K

R225

20KB

2

1 3

R219

100K

C128

223

Q204

RN1411

L204

NCH2137

1 2

C764

223

C763

223

R753

3.3K

R754

3.3K

R601

2.2K

R232

0

R233

0

R234

0

C127

104

C233

0.1/50

+

C919

100/25

+

R314

56

R313

56

J2A

1

J2B

1

J1A

1

J1B

1

JL901B

1

2

3

4

5

6

7

8

9

E001

C903

104

C907

104

C934

223

Q102

KRC107S

Q103

KRC107S

Q104

KRC107S

Q106

KRC107S

Q905

KRC107S

Q404

KRC107S

Q605

KRC107S

Q105

KRC107S

Q402

KRC107S

Q405

KRC107S

Q107

KRC107S

Q108

KRC107S

Q206

KRC107S

Q205

KRC107S

C107

470/6.3

+

C115

10/50

+

C116

10/50

+

C122

10/50

+

C121

22/50

+

C203

10/50

+

C204

10/50

+

C207

10/50

+

C221

100/25

+

C222

100/25

+

C226

10/50

+

C225

10/50

+

C239

10/50

+

C240

10/50

+

C408

10/50

+

C410

22/50

+

C411

220/25

+

C905

10/50

+

C906

100/25

+

C908

220/25

+

C909

10/50

+

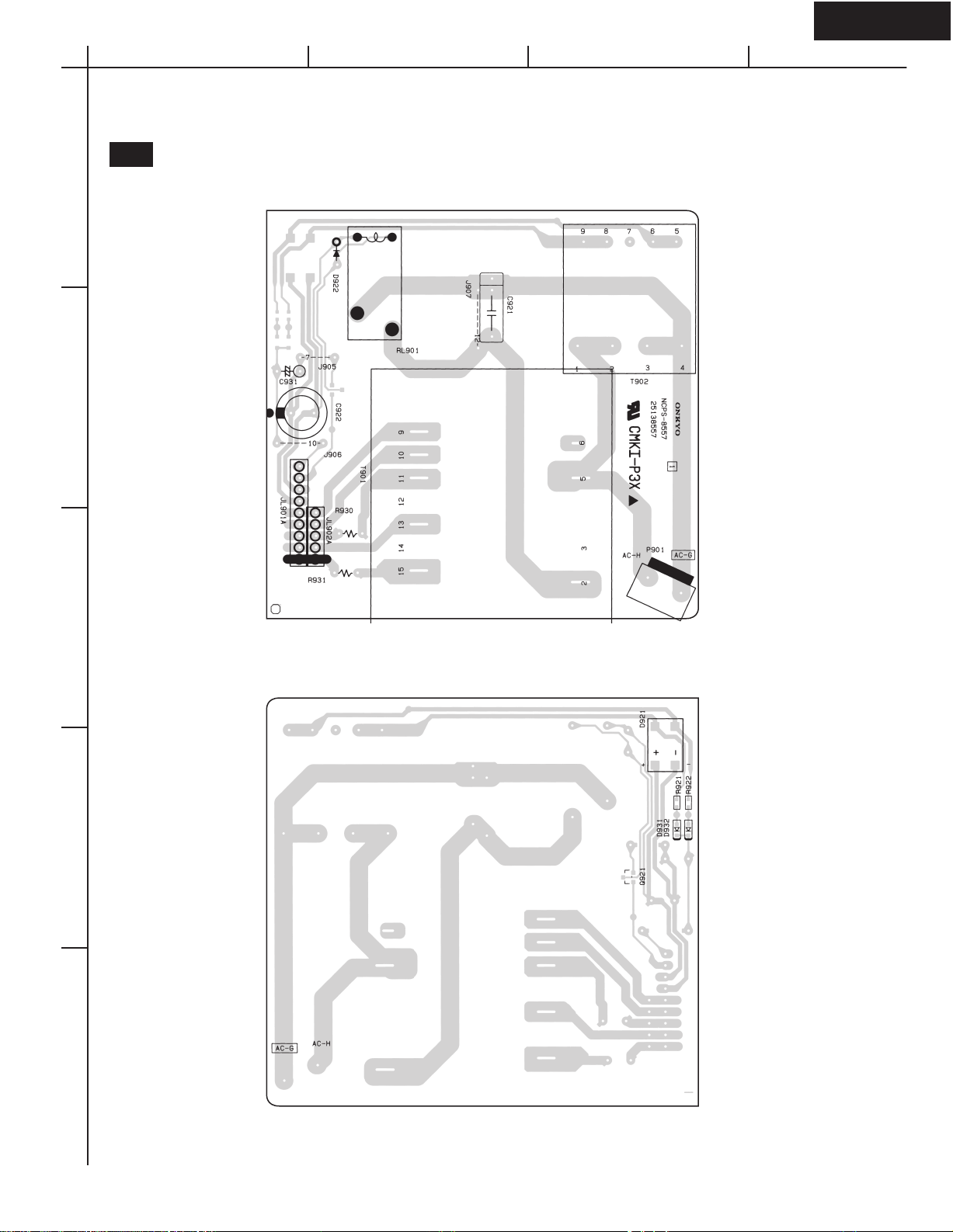

Q921

KRC107S

D922

1N4003

D931

1SS352

D932

1SS352

P901

2

1

RL901

3

1 4

2

D921

421

3

R921

470

R922

470

C922

470/16

+

T901

NPT-1523

6

5

2

15

14

NC

13

12

NC

11

10

9

T902

NPT-1524

4

3

2

1

9

8

NC

7

NC

6

5

C921

103M

JL901A

9

8

7

6

5

4

3

2

1

C931

22/50

+

J901B

1

S901

1 2

J901A

1

C933

103M

D910

UDZS5.6B

L101

NCH2137

1 2

C117

331

C125

221

C126

221

P902

2

1

P902A

R125

470

R126

470

R127

470

R128

470

R201

22K

R202

22K

R203

68K

R204

68K

P201

2

1

3

5

4

6

C202

10/50

+

C201

10/50

+

C243

181

R206

1K

R205

1K

R207

6.8K

R208

6.8K

R209

2.2K

R210

2.2K

Q602

2SD655

C244

181

Q601

2SD655

C247

332

C248

332

R315

100

R316

100

C904

13000/25

+

E002

R930

2.5A/125V

R931

2.5A/125V

EXCEPT

<MDD>

U01 MAIN PC BOARD NAAF-8555

NAPS-8557

U03

POWER SUPPLY

PC BOARD

U05

POWER SWITCH

PC BOARD NASW-8559

DECK B

DECK A

NC

NC

NC

NC

NC

NC

SCHEMATIC DIAGRAM

A

1

2

3

4

5

BCDEFGH

Page 10

P-OFF

RESET

SOL_A_ON/OFF

CAP_A_X1/X2

CAP_A_ON/OFF

CAP_B_X1/X2

SOL_B

CAP_B

REC_MUTE

SIG_L

SIG_RCH

1G

4G

P15

P10P9P8P7P6P5P4P3P2

P1

1G2G3G

4G

P15

P14

P13

P12

P11

P10

P9

P8

P7

P6

P5

P4

P3

P2

P1

1G

2G

3G

4G

KEY0

KEY1

KEY2

HIGH SW

PACK SW

REC INH FWD

FM

FQ

F/Q

GH

GL

GP

N.NORMN.HIGHN.MTLH.NORMH.HIGHH.MTL

HIGH SPEED

NORM SPEED

NORM SPEED

HIGH SPEED

TEST_MODE

DECK A

REC INH REV

METAL SW

MOTOR +

MOTOR B

MOTOR A

ROT PH DIODE

MOTER -

FT

PACK SW

HIGH SW

MOTER -

ROT PH DIODE

MOTOR A

MOTOR B

MOTOR +

PLAY SW

ROT PH OUT A

SOLENOID

ROT PH OUT B

SOLENOID

PLAY SW

DECK B

F-PLAY

R-PLAY

DOLBY_NR

REW

FF

STOP

DECK_B

STOP

B-FF

B-REW

B_F-PLAY

B_R-PLAY

REV_MODE

STBY

ON/OFF

REC_PAUSE

AUTO_SPACE

NORM_DUBB

HIGH_DUBB

COUNTER

RESET

COUNTER

A/B

DECK_A

NAETC-8558

INPUT VR

BA-+

MOTOR

DECK B

BA-+

MOTOR

SOL

SOL

DECK A

OTP ONLY

OTP ONLY1

NAAF-8555

7

+5V SENSOR

6

MOTOR A5MOTOR B

8

MOTOR- COM

9

HIGH SW

10

PACK SW

11

REC INH FWD

12

REC INH REV

13

METAL SW

4

MOTOR+

3

PLAY SW

2

ROT PHT OUT

1

SOLENOID

7

+5V SENSOR

6

MOTOR A5MOTOR B

4

MOTOR+

3

PLAY SW

2

ROT PHT OUT

1

SOLENOID

8

MOTOR- COM

9

HIGH SW

10

PACK SW

R823

3.9K

R825

3.9K

R826

18K

C804

223

R250

100K

R251

56K

R252

NC

R253

56K

R254

NC

R255

56K

R256

82K

R257

NC

R258

100K

R259

NC

100K

Q809 2SB1068

R822

47K

R824

47K

R829

1M

R817

2KB

2

3 1

R820

100K

Q812

2SA933S

R807

47K

R808

3.9K

R809

47K

Q805 2SB1068

R810

3.9K

R812

18K

C803

223

R831

1M

R772

180(1/2W)

R805

100K

R802

2KB

2

3 1

Q801

2SB1068

Q804

2SA933S

Q813 2SB1068

R733

2.7K

R734

2.7K

R735

2.7K

R742

4.7K

R738

4.7K

P5021

2

3

C722

104Z

C721

104Z

Q702

KRA107S

D701

1SS352

R748

470

R747

220K

R781100KX10

11

10

987654321

R783

0

R745

4.7K

D704

1SS352

D705

1SS352

R784

0

R830

10K

Q815

2SA1037AK

R828

10K

Q807

2SA1037AK

R786

0

L701

BK1608LM182-T

D702

UDZS5.6B

R782 100KX10

123456789

10

11

R791

0

D708

1SS352

D707

1SS352

R792

0

R793

0

P705

1

2

3

D709

1SS352

D801

1N4003

2 1

D802

1N4003

2 1

R731

4.7K

R732

4.7K

R744

4.7K

R743

4.7K

R741

4.7K

R739

4.7K

R740

4.7K

R797

10K

R798

0

P701A

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

R746

47K

P801A

123456789

10

R737

4.7K

Q703

78L05

1I3

O

2

G

P702A

1

2

3

R813

47K

R827

47K

P802A

12345678910111213

R803

1KB

2

3 1

R818

1KB

2

3 1

R821

10K

R806

10K

R311

10K

R312

10K

R754

3.3K

R310

10K

Q701

MPD78042FGF

1

CAP_A

2

CAP_A_X2/X1

3

SOL_A

4

1G

5

2G

6

3G

7

4G

8

VDD

9

DOL_CLK

10

DOL_DATA

11

DOL_STB

12

DOL_RST

13

A_70/120

14

B_70/120

15

PB_X1/X2

16

LINE_MUTE

17

RESET

18

REC MUTE

19

P-OFF

20

AVSS

21

FT_MODE

22

TEST_MODE

23

SIG_LCH

24

SIG_RCH

25

VOL26KEY227KEY128KEY029AVDD30AVREF31XT1/GND32XT2/NC33VSS34X135X236BIAS_CONT37N.BIAS38H.BIAS39R/P40B/A

41

R.SEN_B 41

42

R.SEN_A

43

CAP_B

44

CAP_B_X1/X2

45

SOL_B

46

RI_OUT

47

RI_IN

48

IC(VPP)GND

49

A_PACK_SW

50

A_HIGH_SW

51

A_PLY_SW

52

VDD

53

B_PLY_SW

54

B_HIGH_SW

55

B_PACK_SW

56

B_F.REC_INH

57

B_MTL_SW

58

B_R.REC_INH

59

NC

60

SRCH_OFF/ON

61

P16

62

P15

63

P14

64

P13

65

P1266P1167P10

68P969P870P771

VDISP

72P673P574P475P376P277P178

RELAY

79

S_LED

80

FL

R771

2.2K

R721

4.7K

R722

4.7K

R749

1K

C725

22/50

R819

1K

R804

1K

Q811

KRC107S

Q806

KRC107S

Q808

KRC107S

Q803

KRC107S

Q802

KRC107S

Q810

KRC107S

Q814

KRC107S

Q816

KRC107S

C761

10/50

+

C762

10/50

+

X701

CSTLS5M00

R736

NC

R752

3.3K

C765

223

S704

S705

S708

S710

S711

S712

S713

S714

S715

S716

S717

S719

S718

R702

470

R703

820

R704

1K

R705

1.8K

R706

390

R707

470

R708

820

R709

1K

R710

1.8K

R711

390

R712

470

R713

820

R714

1K

R715

1.8K

S702S709

R701

390

S703

R716

3.9K

S720

S706

S701

R717

3.9K

D706

SLI-343URC-TE7

Q707 BJ246GK

1

F112F125P176P167P158P149P13

10

P1211P1112P1013P914P815P716P617P518P419P320P221P122NC23NC24NC25NC26NC27NC28NC29NC30NC31NC32NC33NC34NC351G362G373G384G41F2142F22

P701B

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

R761

20KB

2

1

3

P702B

3

2

1

C723

104

C724

223

R816

5.6K

R801

5.6K

NC

NC

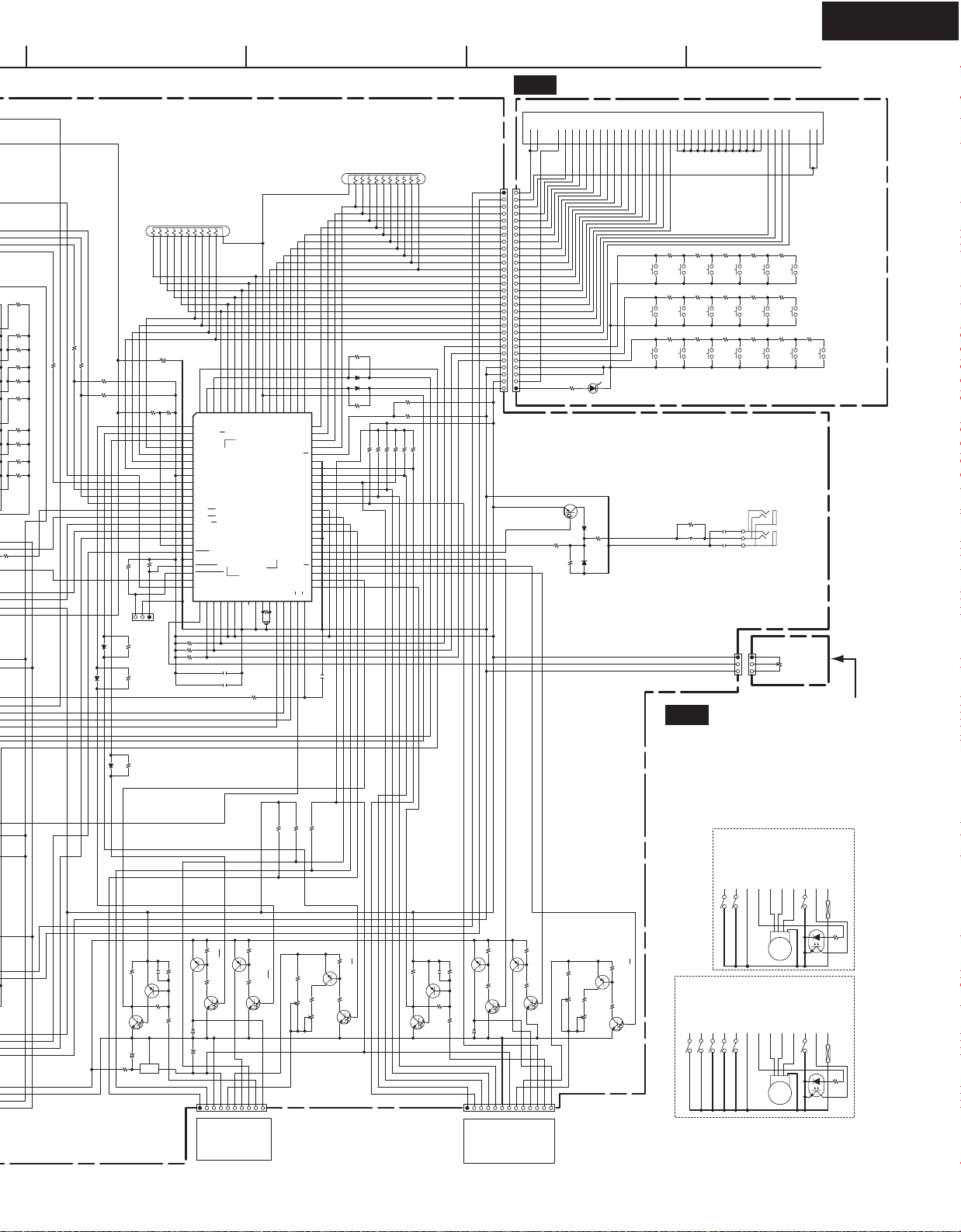

U02 DISPLAY CIRCUIT PC BOARD

NADIS-8556

U04

INPUT VOLUME

PC BOARD

NAETC-8558

TA-RW255

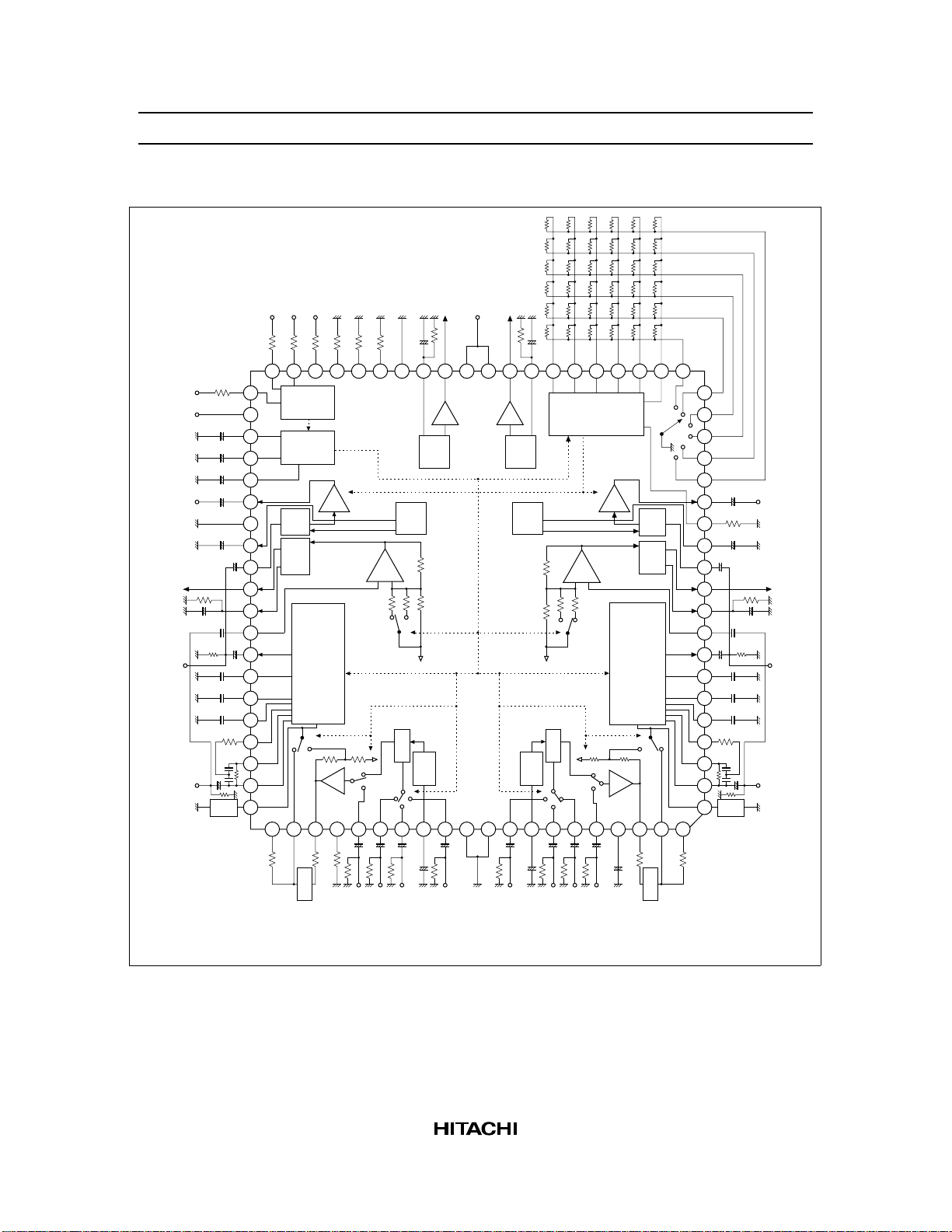

Page 11

BIAS_CTRL

BIAS_NORM

BIAS_H

P-OFF

RESET

DECK_B_70/120

DECK_A_70/120

LINE_MUTE

PB_X1/X2

LINE_MUTE

SOL_A_ON/OFF

CAP_A_X1/X2

CAP_A_ON/OFF

REC/PB

CAP_B_X1/X2

SOL_B

CAP_B

+5V

+12VM

REC_MUTE

+12VA

GND_T

-17V

SIG_L

SIG_RCH

DECK_B/A

1G

4G

P15

P10P9P8P7P6P5P4P3P2

P1

1G2G3G

4G

P15

P14

P13

P12

P11

P10

P9

P8

P7

P6

P5

P4

P3

P2

P1

1G

2G

3G

4G

KEY0

KEY1

KEY2

HIGH SW

PACK SW

REC INH FWD

FM

FQ

F/Q

GH

GL

GP

N.NORMN.HIGHN.MTLH.NORMH.HIGHH.MTL

A:H/B:L

HIGH SPEED

NORM SPEED

LCHRCH

A_PB_LCH B_PB_LCH

B_PB_RCHA_PB_RCH

NORM SPEED

HIGH SPEED

TEST_MODE

DECK A

REC INH REV

METAL SW

MOTOR +

MOTOR B

MOTOR A

ROT PH DIODE

MOTER -

FT

PACK SW

HIGH SW

MOTER -

ROT PH DIODE

MOTOR A

MOTOR B

MOTOR +

PLAY SW

ROT PH OUT A

SOLENOID

ROT PH OUT B

SOLENOID

PLAY SW

DECK B

F-PLAY

R-PLAY

DOLBY_NR

REW

FF

STOP

DECK_B

STOP

B-FF

B-REW

B_F-PLAY

B_R-PLAY

REV_MODE

STBY

ON/OFF

REC_PAUSE

AUTO_SPACE

NORM_DUBB

HIGH_DUBB

COUNTER

RESET

COUNTER

A/B

DECK_A

NAETC-8558

INPUT VR

BA-+

MOTOR

DECK B

BA-+

MOTOR

SOL

SOL

DECK A

OTP ONLY

OTP ONLY1

NAAF-8555

PP,PA MODEL

PP,PA MODEL

NPT-1523P

NPT-1524P

7

+5V SENSOR

6

MOTOR A5MOTOR B

8

MOTOR- COM

9

HIGH SW

10

PACK SW

11

REC INH FWD

12

REC INH REV

13

METAL SW

4

MOTOR+

3

PLAY SW

2

ROT PHT OUT

1

SOLENOID

7

+5V SENSOR

6

MOTOR A5MOTOR B

4

MOTOR+

3

PLAY SW

2

ROT PHT OUT

1

SOLENOID

8

MOTOR- COM

9

HIGH SW

10

PACK SW

R405

4.7

R406

4.7

Q407

2SC1959

C105

681

C106

681

R103

100K

R104

100K

C109

333

R109

100K

R111

3.3K

C113

681

R113

3.9K

C111

153

R115

10K

R108

3.9K

C110

333

R110

100K

C112

153

R112

3.3K

C114

681

R116

10K

C123

470/16

+

C118

331

R823

3.9K

R825

3.9K

R826

18K

C804

223

R910

5.6K

R911

5.6K

D601

1SS352

D602

1SS352

R114

3.9K

R224

10K

R220

100K

R214

560

C216

222

C218

104

C220

104

C210

222

R212

22K

C214

104

R229

12K

R211

22K

C211

222

R213

560

C213

104

C219

104

C217

104

C215

222

C209

222

R227

12K

R250

100K

R251

56K

R252

NC

R253

56K

R254

NC

R255

56K

R256

82K

R257

NC

R258

100K

R259

NC

R260

180K

R261

68K

R262

1M

R263

100K

R264

100K

R265

120K

R266

220K

R267

220K

R268

120K

R269

NC

R270

220K

R271

47K

R272

1M

R273

47K

R274

NC

R275

150K

R276

120K

R277

NC

R278

330K

R279

330K

R280

220K

R281

33K

R282

330K

R283

47K

R284

150K

R285

33K

R286

100K

R287

1M

R288

82K

R289

NC

R290

82K

R291

33K

R292

330K

R293

33K

R295

82K

R296

120K

R297

NC

R298

180K

R299

NC

R294

220K

R300

82K

R301

47K

R302

47K

R303

33K

R304

NC

R305

100K

R306

150K

R307

NC

R308

220K

R309

NC

R727

470

C712

104

R751

100K

R416

5.6K

Q809 2SB1068

R822

47K

R824

47K

R829

1M

R122

100(1/2W)

R121

4.7K

Q604

KRA107S

R817

2KB

2

3 1

R820

100K

Q812

2SA933S

R807

47K

R808

3.9K

R809

47K

Q805 2SB1068

R810

3.9K

R812

18K

C803

223

R107

3.9K

R408

39K

C404 472

Q406

2SC1959

R415

47K

R410

1K

R414

2.2K

R413

10K

R407

39K

C403 472

Q401

2SB1068

Q403

2SC1959

C206

1/50

+

C205

1/50

+

R231

18K

R241

3.3K

R242

3.3K

R243

6.8K

R244

6.8K

R215

4.7K

R217

3.3K

C223

1/50

+

R216

4.7K

R218

3.3K

C224

1/50

+

C228

2.2/50

+

C227

2.2/50

+

R417

100(1/2W)

Q603

KRA107S

R409

10(1/2W)

R411

820

C406

183

R831

1M

C241

1/50

+

C602

470/16

+

C601

1/50

+

C208

10/16

+

L203

NCH2137

2 1

R228

12K

C229

4.7/50

+

R222

10K

R221

10K

C230

4.7/50

+

R230

12K

C232

4.7/50

+

C231

4.7/50

+

D201

1SS352

D202

1SS352

Q203

RN1411

Q408 uPC1330HA

123

4

CNT

5

GND

6

VCC

789

L201

NMC6079

3

2

176

5

4

8

L202

NMC6079

6

5

483

2

1

7

C102

221

R101

100K

C101

221

R102

100K

C104

471

C103

471

C707

104

C918

2.2/50

+

R914

2.2K

R915

2.2K

R908

470

R909

2.7K

C932

104

R725

22K

Q706

2SD655

R724

22K

Q705

2SD655

R728

0

C911

273

C212

222

C238

331

C237

331

C407

123/100V

C402

101

L403

NLO-2059

3

2

186

5

4

7

R404

100KB

123

R403

100KB

123

R119

50KB

2

13

R117

50KB

2

13

R118

50KB

2

31

R120

50KB

2

31

R772

180(1/2W)

Q101 BA3416BL

13579

11

131517

1816141210

864

2

R805

100K

R802

2KB

2

3 1

Q801

2SB1068

Q804

2SA933S

Q813 2SB1068

R733

2.7K

R734

2.7K

R735

2.7K

R742

4.7K

R738

4.7K

P5021

2

3

C722

104Z

C721

104Z

Q702

KRA107S

D701

1SS352

R748

470

R747

220K

R781100KX10

11

10

987654321

R783

0

R745

4.7K

D704

1SS352

D705

1SS352

R784

0

R830

10K

Q815

2SA1037AK

R828

10K

Q807

2SA1037AK

R786

0

L701

BK1608LM182-T

R237

56K

R238

47K

R240

100K

R239

100K

R245

10K

C236

104

C235

104

P205

321

C401

101

C409

223

D702

UDZS5.6B

D703

UDZS5.6B

R782 100KX10

123456789

10

11

R791

0

D708

1SS352

D707

1SS352

R792

0

R793

0

P705

1

2

3

D709

1SS352

D801

1N4003

2 1

D802

1N4003

2 1

C405 223

R903

3.9K

C914

104

R912

2.2K

R913

2.2K

Q903

78M05

1

I

2

G

3

O

Q901

78M12

1

I

2

G

3

O

R923

10(1/2W)

D907

UDZS18C

D908

1N4003

2 1

D904 1N4003

2 1

D9031N4003

2 1

D902 1N4003

2 1

D9011N4003

2 1

D913

1N40032 1

C915

1/50

+

Q904

2SA933S

C910

2200/16

+

R731

4.7K

R732

4.7K

R744

4.7K

R743

4.7K

R741

4.7K

R739

4.7K

R740

4.7K

R797

10K

R798

0

P701A

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

P102A

8

7

6

5

4

3

2

1

P101A

1

2

3

R746

47K

P801A

123456789

10

L102

NCH2137

2 1

L401

4.7mH

NCH2133

2 1

C413

681

C415

680

C414

681

C416

680

L402

4.7mH