Page 1

BLOCK DIAGRAM

SKW-8230 : POWERED SUBWOOFER

HTP-8230

HTP-8230

Page 2

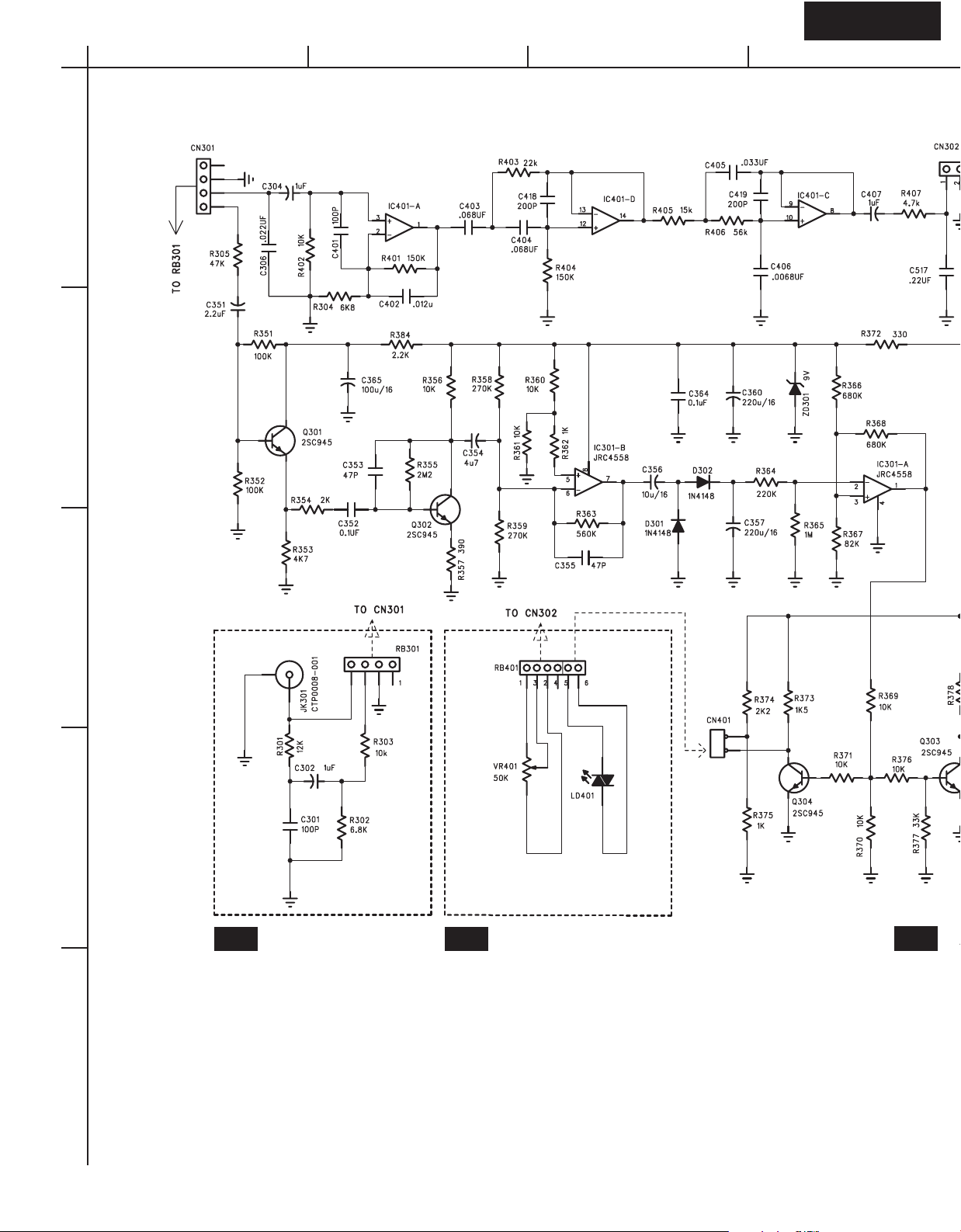

SCHEMATIC DIAGRAM

SKW-8230 : POWERED SUBWOOFER

HTP-8230

A

1

2

3

4

5

BCDEFGH

LINE

INPUT

OUTPUT

LEVEL

AC 120V / 60Hz

INPUT PC BOARD

U02

MAIN PC BOARD

U01

VR / LED PC BOARD

U03

LED

RED : STANDBY

GREEN : ON

Page 3

HTP-8230

SPEAKER

MAIN PC BOARD

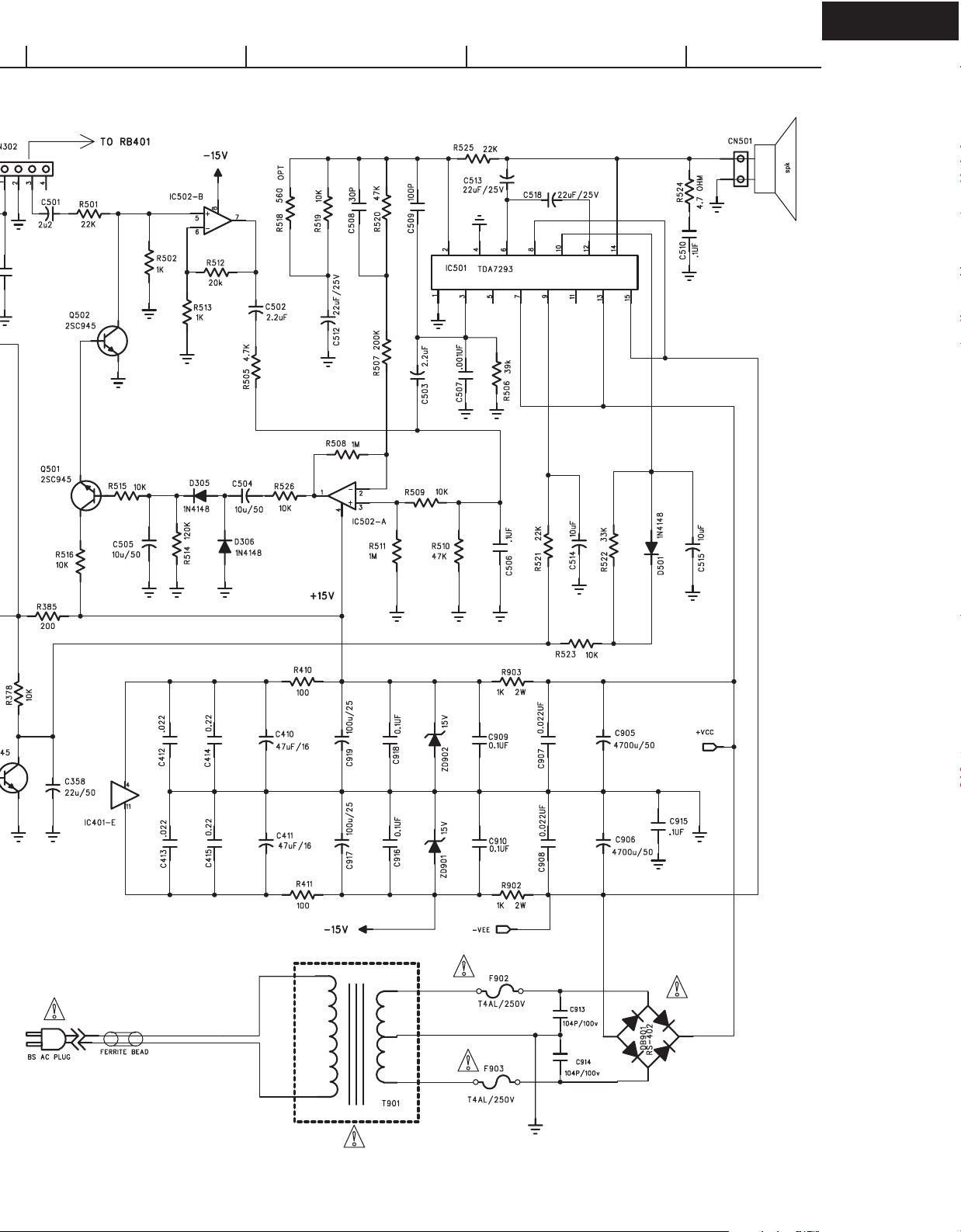

Page 4

HTP-8230

SCHEMATIC DIAGRAM

SKW-8230 : POWERED SUBWOOFER

A

1

2

3

4

5

BCDEFGH

LINE

INPUT

OUTPUT

LEVEL

AC 120V / 60Hz

SPEAKER

INPUT PC BOARD

U02

MAIN PC BOARD

U01

VR / LED PC BOARD

U03

LED

RED : STANDBY

GREEN : ON

Page 5

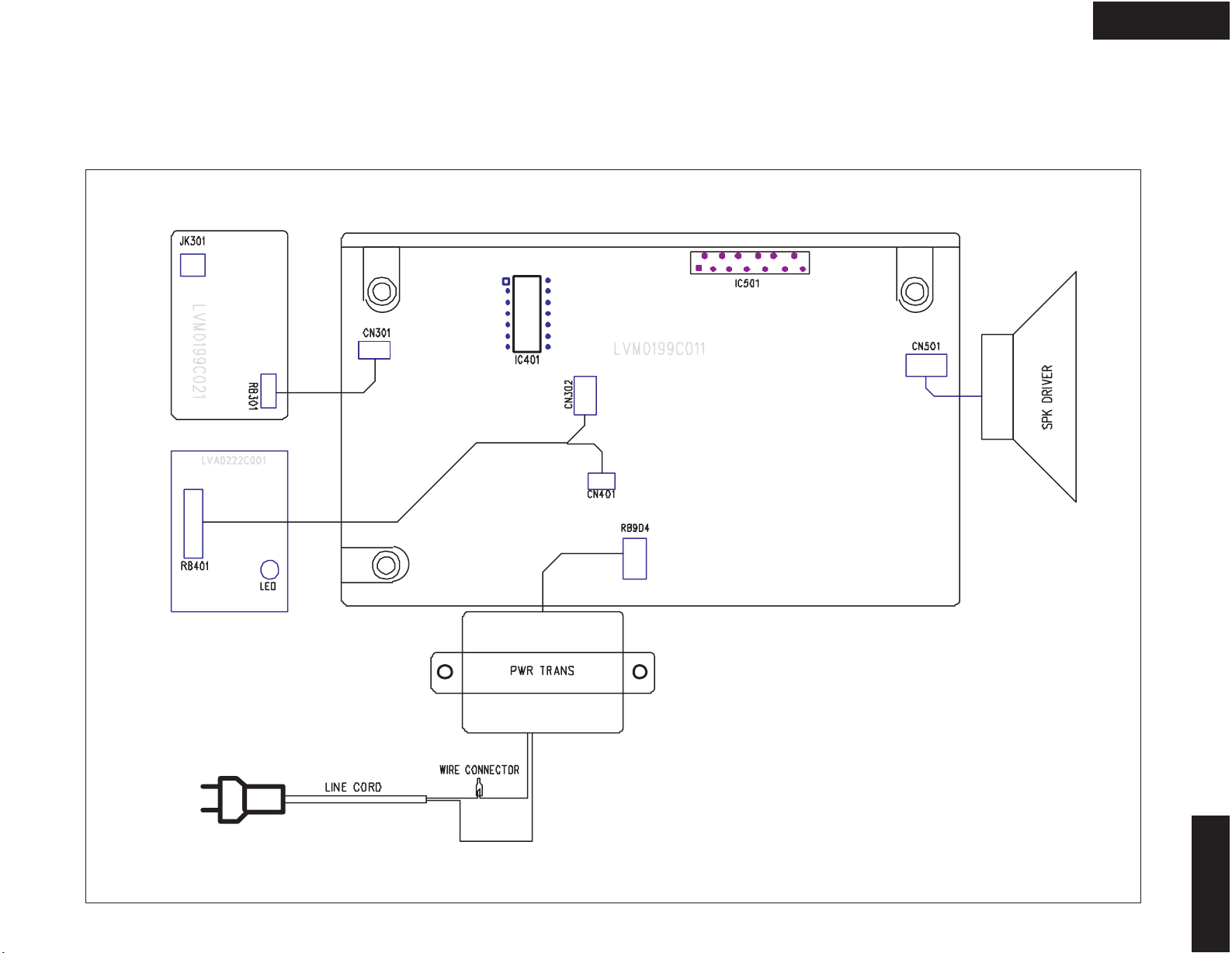

PC BOARD CONNECTION DIAGRAM

SKW-8230 : POWERED SUBWOOFER

INPUT PC BOARD

HTP-8230

MAIN PC BOARD

VR / LED PC BOARD

HTP-8230

Page 6

HTP-8230

A

PRINTED CIRCUIT BOARD VIEW

SKW-8230 : POWERED SUBWOOFER

MAIN PC BOARD

U01

1

2

BCD

3

4

INPUT PC BOARD

U02

5

VR / LED PC BOARD

U03

No PC board view

Look over the actual PC board on hand

Page 7

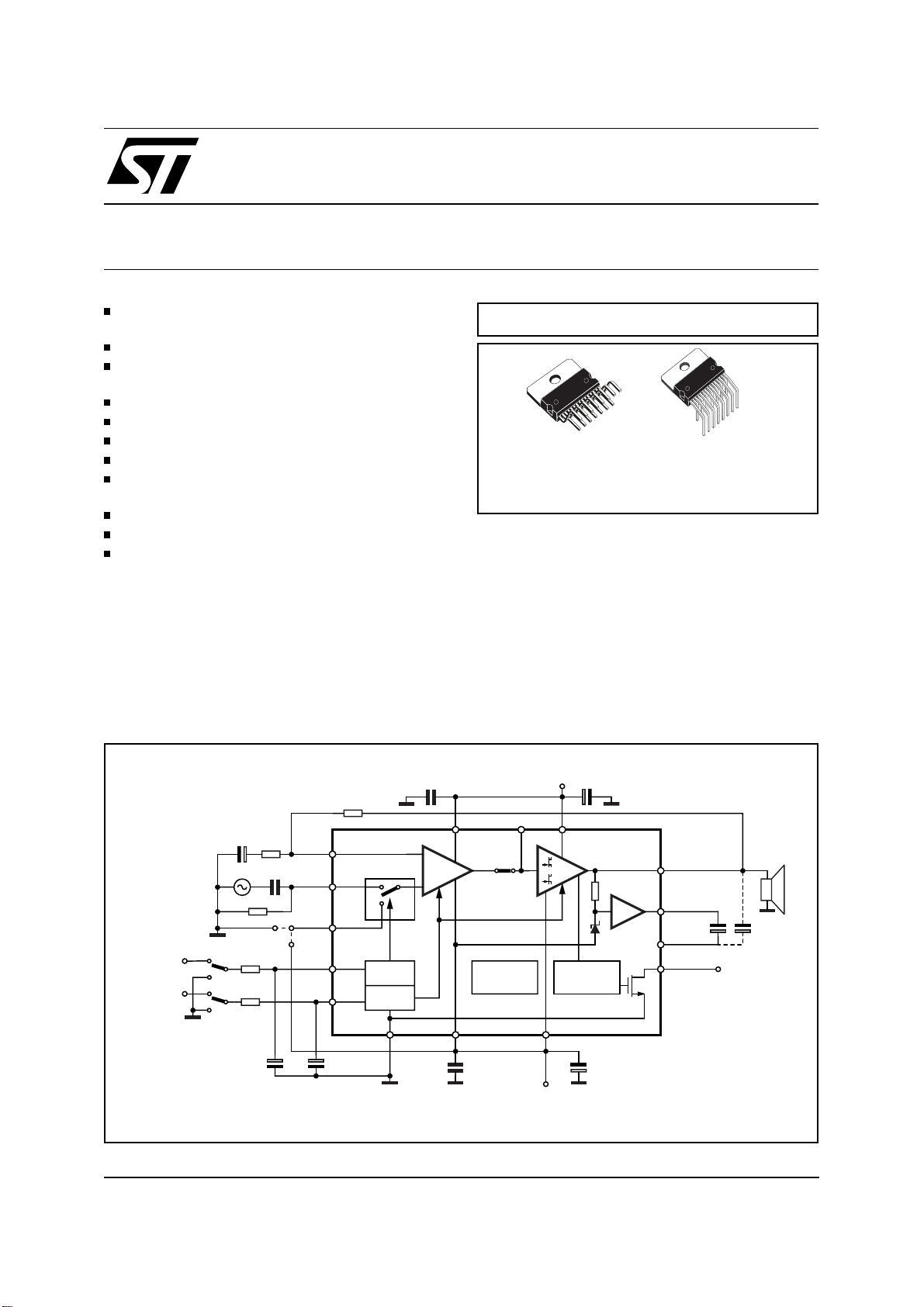

®

TDA7293

120V - 100W DMOS AUDIO AMPLIFIER WITH MUTE/ST-BY

VERY HIG H OPERATI NG VOLTAGE R ANGE

(±50V)

DMOS POWER STAGE

HIGH OUTPUT POWER (100W @ THD =

10%, R

L

= 8Ω, VS = ±40V)

MUTING/STAND- BY FUNC TION S

NO SWITCH ON/OFF NOISE

VERY LOW DISTORTION

VERY LOW NOISE

SHORT CIRCUIT PROTECTED (WITH NO IN-

PUT SIGNAL APPLIED)

THERMAL SHUTDOWN

CLIP DETECTOR

MODULARITY (MORE DEVICES CAN BE

EASILY CONNECTED IN PARALLEL TO

DRIVE VERY LOW IMPEDANCES)

DESCRIPTION

The TDA7293 is a monolithic integrated circuit in

Multiwatt15 package, intended for use as audio

class AB amplifier in Hi-Fi field applications

(Home Stereo, self powered loudspeakers, Top-

Figure 1: Typical Application and Test Circuit

MULTIPOWER BCD TECHNOLOGY

Multiwatt15V Multiwatt15H

ORDERING NUMBERS:

TDA7293V TDA7293HS

class TV). Thanks to the wide voltage range and

to the high out current c apability it is able to supply the highest power into both 4Ω and 8Ω loads.

The built in muting function with turn on delay

simplifies the remote operation avoiding switching

on-off noises.

Parallel mode is made possible by connecting

more device through of pin11. High out put power

can be delivered to very low impedance loads, so

optimizing the thermal dissipation of the system.

VMUTE

VSTBY

January 2003

R3 22K

C2

R2

22µF

680Ω

C1 470nF

R1 22K

R5 10K

R4 22K

C3 10µF C4 10µF

IN- 2

IN+

3

4

SGND

(**)

10

MUTE

9

STBY

(*) see Application note

(**) for SLAVE function

C7 100nF C6 1000µF

BUFFER DRIVER

11

713

-

+

MUTE

STBY

1

STBY-GND

THERMAL

SHUTDOWN

-Vs -PWVs

C9 100nF C8 1000µF

-Vs

+Vs

+PWVs+Vs

S/C

PROTECTION

158

14

12

6

5

D97AU805A

OUT

BOOT

LOADER

C5

22µF

BOOTSTRAP

CLIP DET

(*)

VCLIP

1/15

Page 8

TDA7293

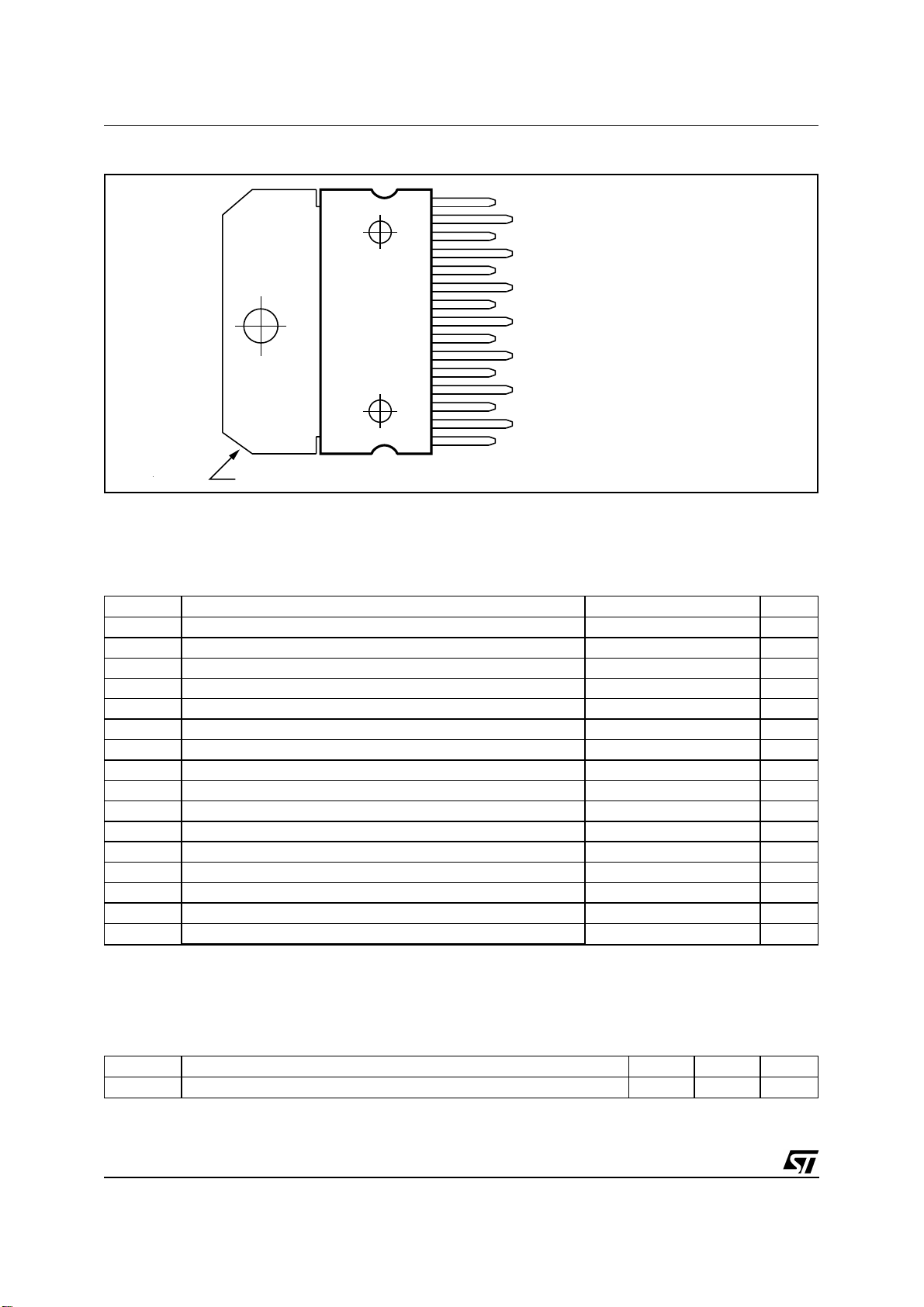

PIN CONNECTION (Top view)

-VS (POWER)

OUT

+V

(POWER)

S

BOOTSTRAP LOADER

BUFFER DRIVER

MUTE

STAND-BY

-V

(SIGNAL)

S

+V

(SIGNAL)

S

BOOTSTRAP

CLIP AND SHORT CIRCUIT DETECTOR

SIGNAL GROUND

NON INVERTING INPUT

INVERTING INPUT

STAND-BY GND

TAB CONNECTED TO PIN 8

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

D97AU806

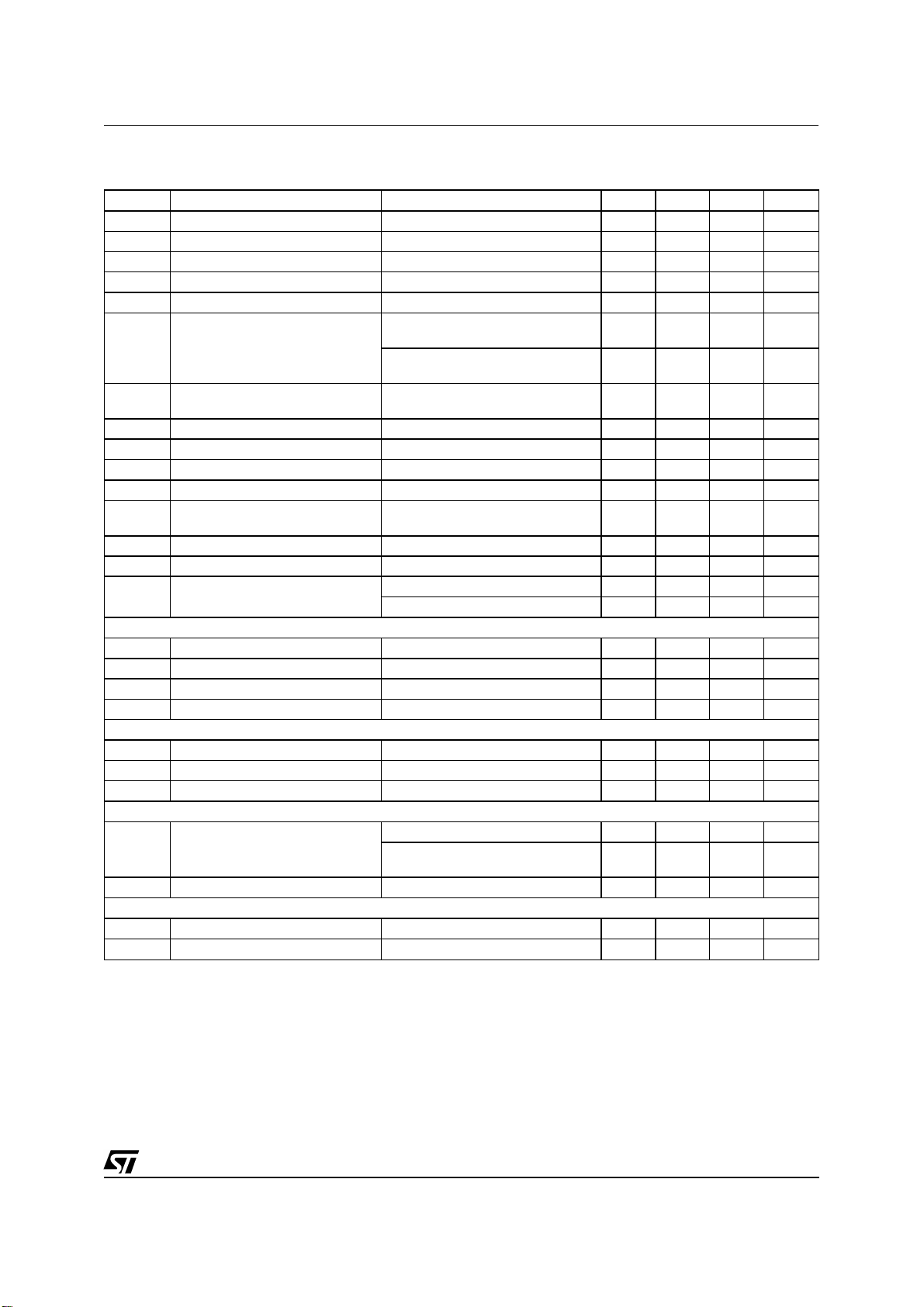

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

S

V

1

V

2

- V

V

2

V

3

V

4

V

5

V

6

V

9

V

10

V

11

V

12

I

O

P

tot

T

op

, T

T

stg

Supply Voltage (No Signal)

V

STAND-BY

GND Voltage Referred to -VS (pin 8) 90 V

Input Voltage (inverting) Referred to -VS 90 V

Maximum Differential Inputs

3

Input Voltage (non inverting) Referred to -VS 90 V

Signal GND Voltage Referred to -VS 90 V

Clip Detector Voltage Referred to -VS 120 V

Bootstrap Voltage Referred to -VS 120 V

Stand-by Voltage Referred to -VS 120 V

Mute Voltage Referred to -VS 120 V

Buffer Voltage Referred to -VS 120 V

Bootstrap Loader Voltage Referred to -VS 100 V

Output Peak Current 10 A

Power Dissipation T

= 70°C50W

case

Operating Ambient Temperature Range 0 to 70

Storage and Junction Temperature 150

j

60 V

±

30 V

±

C

°

C

°

THERMAL DATA

Symbol Description

Thermal Resistance Junction-case 1 1.5

2/15

R

th j-case

Typ

Max Unit

C/W

°

Page 9

TDA7293

ELECTRICAL CHARACTERISTICS (Refer to the Test Circuit V

T

= 25°C, f = 1 kHz; unless otherwise specified).

amb

= ±40V, RL = 8Ω, Rg = 50 Ω;

S

Symbol Parameter Test Condition Min. Typ. Max. Unit

V

I

I

V

I

OS

P

Supply Range

S

Quiescent Current 50 100 mA

q

Input Bias Current 0.3 1

b

Input Offset Voltage -10 10 mV

OS

Input Offset Current 0.2

RMS Continuous Output Power d = 1%:

O

R

= 4

VS = ± 29V,

Ω;

L

d = 10%

= 4Ω ; VS = ±29V

R

L

d Total Harmonic Distortion (**) PO = 5W; f = 1kHz

P

= 0.1 to 50W; f = 20Hz to 15kHz

O

I

SC

Current Limiter Threshold VS ≤ ± 40V 6.5 A

12

±

75 80

90 100

100

0.005

80

50 V

±

0.1

SR Slew Rate 5 10 V/µs

G

G

e

R

SVR Supply Voltage Rejection f = 100Hz; V

T

Open Loop Voltage Gain 80 dB

V

Closed Loop Voltage Gain (1) 29 30 31 dB

V

Total Input Noise A = curve

N

f = 20Hz to 20kHz

Input Resistance 100 k

i

= 0.5Vrms 75 dB

ripple

Thermal Protection DEVICE MUTED 150

S

1

310

DEVICE SHUT DOWN 160

STAND-BY FUNCTION

V

V

ATT

I

q st-by

ST on

ST off

Stand-by on Threshold 1.5 V

Stand-by off Threshold 3.5 V

Stand-by Attenuation 70 90 dB

st-by

Quiescent Current @ Stand-by 0.5 1 mA

MUTE FUNCTION

V

V

ATT

Mon

Moff

Mute on Threshold 1.5 V

Mute off Threshold 3.5 V

Mute AttenuatIon 60 80 dB

mute

(Ref: to pin 1)

(Ref: to pin 1)

CLIP DETECTOR

Duty Duty Cycle ( pin 5) THD = 1% ; RL = 10KΩ to 5V 10 %

THD = 10% ;

30 40 50 %

RL = 10KΩ to 5V

I

CLEAK

SLAVE FUNCTION pin 4

V

Slave

V

Master

Note (1):

Note:

Note (**):

SlaveThreshold 1V

Master Threshold 3 V

Vmin

G

26dB

≥

Pin 11 only for modular connection. Max external load 1MΩ/10 pF, only for test purpose

Tested with optimized Application Board (see fig. 2)

(Ref: to pin 8 -V

PO = 50W 3

)

S

A

µ

A

µ

W

W

%

%

V

µ

V

µ

Ω

C

°

C

°

A

µ

3/15

Page 10

TDA7293

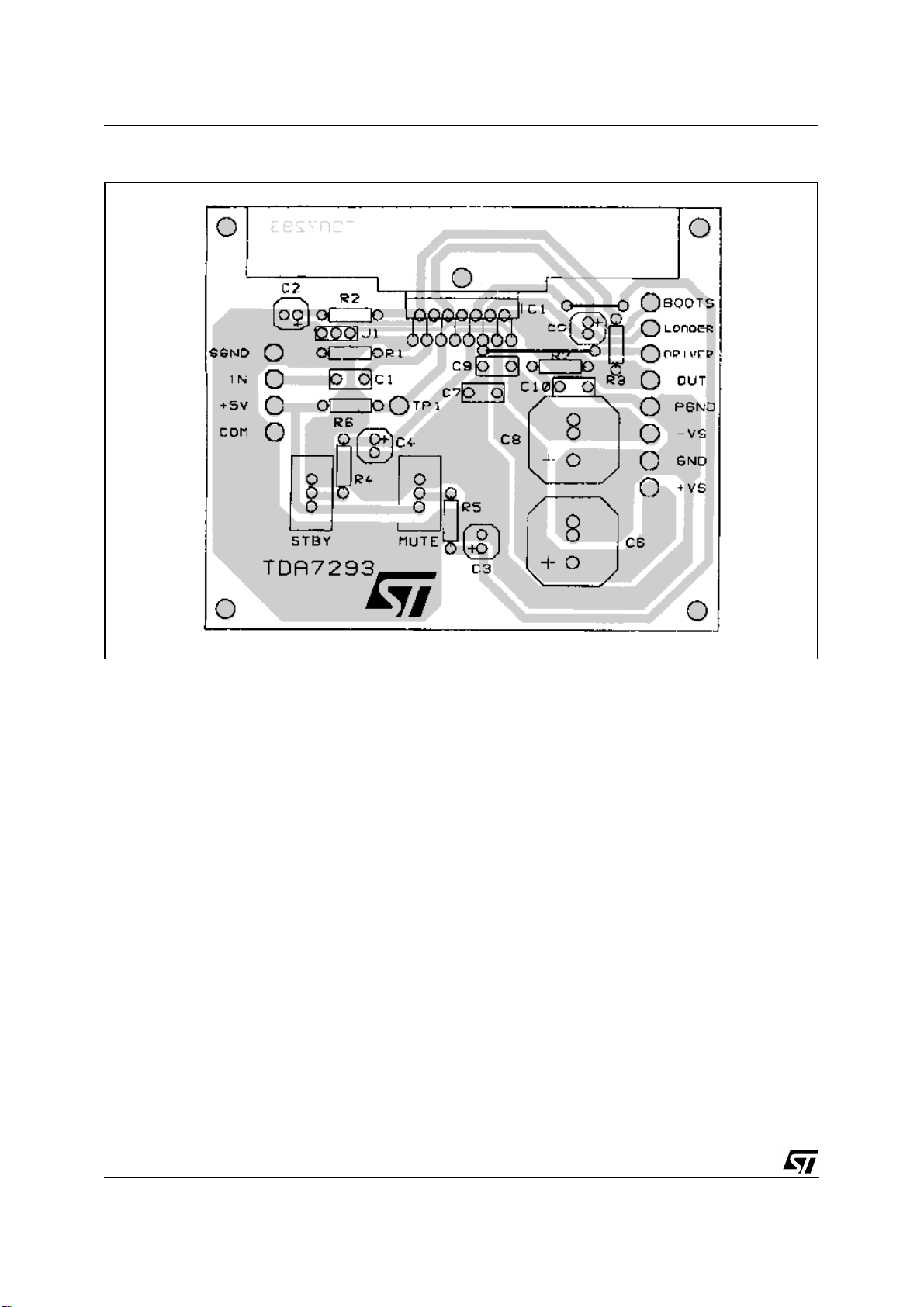

Figure 2: Typical Application P.C. Board and Component Layout (scale 1:1)

4/15

Page 11

TDA7293

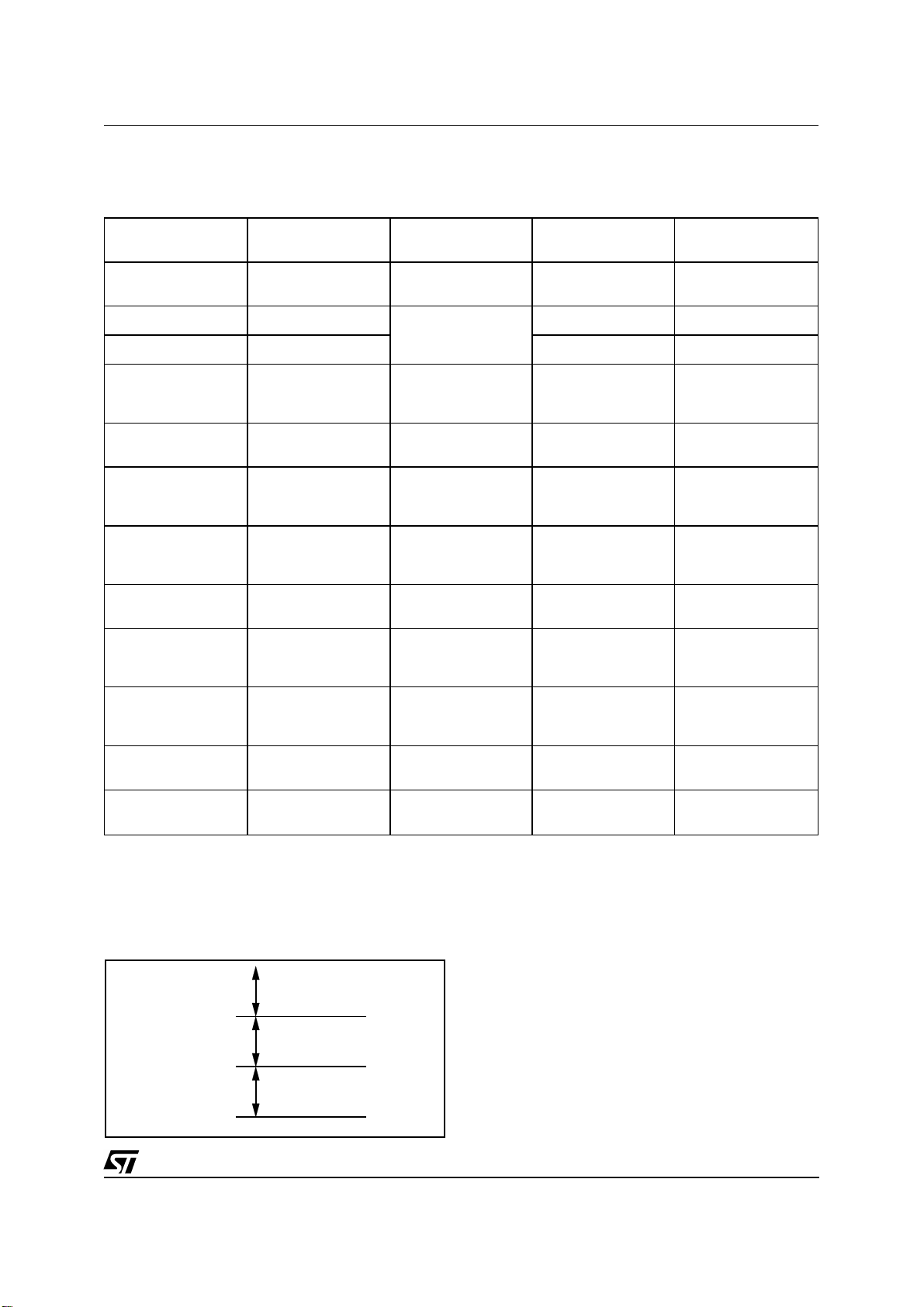

APPLICATION SUGGES TION S (see Test and Application Circuits of the Fig. 1)

The recommended values of t he external components are t hose shown on t he application circuit o f Figure 1. Different values can be used; the following table can help the designer.

COMPONENTS SUGGESTED VALUE PURPOSE

LARGER THAN

SUGGESTED

R1 (*) 22k INPUT RESISTANCE INCREASE INPUT

IMPEDANCE

R2 680

Ω

CLOSED LOOP GAIN

DECREASE OF GAIN INCREASE OF GAIN

SMALLER THAN

SUGGESTED

DECREASE INPUT

IMPEDANCE

SET TO 30dB (**)

R3 (*) 22k INCREASE OF GAIN DECREASE OF GAIN

R4 22k ST-BY TIME

CONSTANT

LARGER ST-BY

ON/OFF TIME

SMALLER ST-BY

ON/OFF TIME;

POP NOISE

R5 10k MUTE TIME

CONSTANT

C1 0.47µF INPUT DC

DECOUPLING

LARGER MUTE

ON/OFF TIME

SMALLER MUTE

ON/OFF TIME

HIGHER LOW

FREQUENCY

CUTOFF

C2 22µF FEEDBACK DC

DECOUPLING

HIGHER LOW

FREQUENCY

CUTOFF

C3 10µF MUTE TIME

CONSTANT

C4 10µF ST-BY TIME

CONSTANT

LARGER MUTE

ON/OFF TIME

LARGER ST-BY

ON/OFF TIME

SMALLER MUTE

ON/OFF TIME

SMALLER ST-BY

ON/OFF TIME;

POP NOISE

C5 22µFXN (***) BOOTSTRAPPING SIGNAL

C6, C8 1000µF SUPPLY VOLTAGE

C7, C9 0.1µF SUPPLY VOLTAGE

(*) R1 = R3 for pop optimization

(**) Closed Loop Gain has to be ≥ 26dB

(***) Multiplay this value for the number of modular part connected

D98AU821

S

)

Slave function: pin 4 (Ref to pin 8 -V

+3V

-V

S

-V

+1V

S

-V

S

MASTER

UNDEFINED

SLAVE

DEGRADATION AT

LOW FREQUENCY

BYPASS

DANGER OF

BYPASS

OSCILLATION

Note:

If in the application, the speakers are connected

via long wires, it is a good rule to add between

the output and GND, a Boucherot Cell, in order to

avoid dangerous spurious oscillations when the

speakers terminal are shorted.

The suggested Boucherot Resistor is 3.9Ω/2W

and the capacitor is 1µF.

5/15

Page 12

TDA7293

INTRODUCTION

In consumer electronics, an increasing demand

has arisen for very high power monolithic audio

amplifiers able to match, with a low cost, the performance obtained from the best discrete designs.

The task of realizing this linear integrated circuit

in conventional bipolar technology is made extremely difficult by the occurence of 2nd breakdown phoenomenon. It limits the safe operating

area (SOA) of the power devices, and, as a consequence, the maximum attainable output power,

especially in presence of highly reactive loads.

Moreover, full exploitation of the SOA translates

into a substantial increase in circuit and layout

complexity due to the need of sophisticated protection circuits.

To overcome these substantial drawbacks, the

use of power MOS devices, which are immune

from secondary breakdown is highly desirable.

The device described has therefore been developed in a mixed bipolar-MOS high voltage technology called BCDII 100/120.

1) Output Stage

The main design task in developping a po wer operational amplifier, independently of the technology used, is that of realization of the output stage.

The solution shown as a principle shematic by

Fig3 represents the DMOS unity - gain output

buffer of the TDA7293.

This large-signal, high-power buffer must be capable of handling extremely high current and voltage levels while maintaining acceptably low harmonic distortion and good behaviour over

frequency response; moreover, an accurate control of quiescent current is required.

A local linearizing feedback, provided by differential amplifier A, is used to fullfil the above requirements, allowing a simple and effective quiescent

current setting.

Proper biasing of the power output transistors

alone is however not enough to guarantee the absence of crossover distortion.

While a linearization of the DC transfer characteristic of the stage is obtained, the dynamic behaviour of the system must be taken into account.

A significant aid in keeping the distortion contributed by the final stage as low as possible is provided by the compensation scheme, which exploits the direct connection of the Miller capacitor

at the amplifier’s output to introduce a local AC

feedback path enclosing the output stage itself.

2) Protections

In designing a power IC, particular attention must

be reserved to the circuits devoted to protection

of the device from short circuit or overload conditions.

Due to the absence of the 2nd breakdown phenomenon, the SOA of the power DMOS tr ansistors is delimited only by a maximum dissipation

curve dependent on the duration of the applied

stimulus.

In order to fully exploit the capabilities of the

power transistors, the protection scheme implemented in this device combines a conventional

SOA protection circuit with a novel local temperature sensing technique which " dynamically" controls the maximum dissipation.

Figure 3: Principle Schematic of a DMOS unity-gain buffer.

6/15

Page 13

Figure 4: Turn ON/OFF Suggested Sequence

+Vs

(V)

+40

-40

-Vs

V

IN

(mV)

V

ST-BY

PIN #9

(V)

5V

TDA7293

V

MUTE

PIN #10

(V)

I

Q

(mA)

V

OUT

(V)

OFF

ST-BY

5V

PLAY

MUTE MUTE

In addition to the overload protection described

above, the device features a thermal shutdown

circuit which initially puts the device into a muting

state (@ Tj = 150

Tj = 160

o

C).

o

C) and then into stand-by (@

Full protection against electrostatic discharges on

every pin is included.

Figure 5: Single Signal ST-BY/MUTE Control

Circuit

MUTE STBY

MUTE/

ST-BY

20K

10K 30K

1N4148

10µF10µF

D93AU014

3) Other Features

The device is provided with both stand-by and

ST-BY OFF

D98AU817

mute functions, independently driven by two

CMOS logic compatible input pins.

The circuits dedicated to the switching on and off

of the amplifier have been carefully optimized to

avoid any kind of uncontrolled audible transient at

the output.

The sequence that we recommend during the

ON/OFF transients is shown by Figure 4.

The application of figure 5 shows the possibility of

using only one command for both st-by and mute

functions. On both the pins, the maximum applicable range corresponds to the oper ating supply

voltage.

APPLICATION INFORMATION

HIGH-EFFICIENCY

Constraints of implementing high power solutions

are the power dissipation and the size of the

power supply. These are both due to the low efficiency of conventional AB class amplifier approaches.

Here below (figure 6) is described a circuit proposal for a high efficiency amplifier which can be

adopted for both HI-FI and CAR-RADIO applications.

7/15

Page 14

TDA7293

The TDA7293 is a monolithic MOS power amplifier which can be operated at 100V supply voltage

(120V with no signal applied) while delivering output currents up to ±6.5 A.

This allows the use of this device as a very high

power amplifier (up to 180W as peak power with

T.H.D.=10 % and Rl = 4 Ohm); the only drawback

is the power dissipation, hardly manageable in

the above power range.

The typical junction-to-case thermal resistance of

the TDA7293 is 1

avoid that, in worst case conditions, the chip temperature exceedes 150

of the heatsink must be 0.038

bient temperature of 50

o

C/W (max= 1.5 oC/W). To

o

C, the thermal resistance

o

o

C).

C/W (@ max am-

As the above value is pratically unreachable; a

high efficiency system is needed in those cases

where the continuous RMS output power is higher

than 50-60 W.

The TDA7293 was designed to work also in

higher efficiency way.

For this reason there are four power supply pins:

two intended for the signal part and two for the

power part.

T1 and T2 are two power transistors that only

operate when the output power reaches a certain

threshold (e.g. 20 W). If the output power increases, these transistors are switched on during

the portion of t he signal where more output voltage swing is needed, thus "bootstrapping" the

power supply pins (#13 and #15).

The current generators formed by T4, T7, zener

diodes Z1, Z2 and resistors R7,R8 define the

minimum drop across the power MOS transistors

of the TDA7293. L1, L2, L3 and the snubbers C9,

R1 and C10, R2 stabilize the loops formed by the

"bootstrap" circuits and the output stage of the

TDA7293.

By considering again a maximum average

output power (music signal) of 20W, in case

of the high efficiency application, the thermal

resistance value needed from the heatsink is

o

C/W (Vs =±50 V and Rl= 8 Ohm).

2.2

All components (TDA7293 and power transistors T1 and T2) can be placed on a 1.5

o

C/W

heatsink, with the power darlingtons electrically

insulated from the heatsink.

Since the total power dissipation is less than that

of a usual class AB amplifier, additional cost savings can be obtained while optimizing the power

supply, even with a high heatsink .

BRIDGE APPLICATION

Another application suggestion is the BRIDGE

configuration, where two TDA7293 are used.

In this application, the value of the load must not

be lower than 8 Ohm for dissipation and current

capability reasons.

A suitable field of application includes HI-FI/TV

subwoofers realizations.

The main advantages offered by this solution are:

- High power performances with limited supply

voltage level.

- Considerably high output power even with high

load values (i.e. 16 Ohm).

With Rl= 8 Ohm, Vs = ±25V the maximum output

power obtainable is 150 W, while with Rl=16

Ohm, Vs = ±40V the maximum Pout is 200 W.

APPLICATION NOTE: (ref. fig. 7)

Modular Application (more Devices in Parallel)

The use of the modular application lets very high

power be delivered to very low impedance loads.

The modular application implies one device to act

as a master and the others as slaves.

The slave power stages are driven by the master

devic e and work in pa r allel all toge t h er , w hi le the i nput and the gain stages of the slave device are disabled, t he figure below shows t he connectio ns required to co nfi g ure tw o dev ic es to w o rk toge the r.

The master chip connections are the same as

the normal single ones.

The outputs can be conne cted together with-

out the need of any ballast resistance.

The slave SGND pin must be tied to the negative supply.

The slave ST-BY and MUTE pins must be connected to the master ST-BY and MUTE pins.

The bootstrap lines must be connected together and the bootstrap capacitor must be increased: for N devices the boostrap capacitor

must be 22µF times N.

The slave IN-pin must be connected to the

negative supply.

THE BOOTSTRAP CAPACITOR

For compatibility purpose with the previous devices of the family, the boostrap capacitor can be

connected both between the bootstrap pin (6) and

the output pin (14) or between the boostrap pin

(6) and the bootstrap loader pin (12).

When the bootcap is connected between pin 6

and 14, the maximum supply voltage in presence

of output signal is limited to 100V, due the bootstrap capacitor overvoltage.

When the bootcap is connected between pins 6

and 12 the maximum supply voltage extend to the

full voltage that the technology can stand: 120V.

This is accomplished by the clamp introduced at

the bootstrap loader pin (12): this pin follows the

output voltage up to 100V and remains clamped

at 100V for higher output voltages. This feature

lets the output voltage swing up to a gate-source

S

voltage from the positive supply (V

-3 to 6V).

8/15

Page 15

Figure 6: High Efficiency Application Circuit

TDA7293

+50V

D6

1N4001

PLAY

ST-BY

D5

1N4148

D1 BYW98100

C12 330nF

INC7

C13 10µF

R13 20K

R14 30K

R15 10K

10µF

D2 BYW98100

R20

20K

R21

20K

+25V

GND

-25V

-50V

C1

1000µF

63V

C2

1000µF

63V

C3

100nF

C4

100nF

C5

1000µF

35V

C6

1000µF

35V

100nF

R22

10K

R23

10K

C8

100nF

C9

330nF

C10

330nF

D7

1N4001

R1

2

R2

2

Figure 6a: PCB and Component Layout of the fig. 6

C14

R12

13K

3

4

TDA7293

9

1

815

10

137

BDX53A

R17 270

L1 1µH

2

14

6

12

L2 1µH

R19 270

BDX54A

T3

BC394

T1

D3 1N4148

R3 680

R16

13K

C15

22µF

D4 1N4148

T2

T6

BC393

C11 22µF

L3 5µH

R18 270

R4

270R5270

T4

BC393

Z1 3.9V

Z2 3.9V

T7

BC394

R9

270

R6

20K

R7

3.3K

R8

3.3K

R10

270

D97AU807C

T5

BC393

1.8nF

1.8nF

T8

BC394

R11

20K

C16

C17

OUT

P

ot

9/15

Page 16

TDA7293

Figure 6b: PCB - Solder Side of the fig. 6.

Figure 7: Modular Application Circuit

SGND

MUTE

STBY

C3 10µF

SGND

MUTE

STBY

IN- 2

IN+

C4 10µF

IN- 2

IN+ 3

R3 22K

3

4

10

9

4

10

9

MASTER

VMUTE

VSTBY

SLAVE

C2

22µF

R5 10K

R4 22K

680Ω

C1 470nF

R1 22K

R2

C7 100nF C6 1000µF

BUFFER

DRIVER

713

-

+

MUTE

STBY

1

STBY-GND

C7 100nF C6 1000µF

-

+

MUTE

STBY

1

STBY-GND

11

THERMAL

SHUTDOWN

-Vs -PWVs

C9 100nF C8 1000µF

-Vs

BUFFER

DRIVER

713

11

THERMAL

SHUTDOWN

-Vs -PWVs

C9 100nF C8 1000µF

-Vs

+Vs

+PWVs+Vs

S/C

PROTECTION

158

+Vs

+PWVs+Vs

S/C

PROTECTION

158

14

12

6

5

14

12

6

5

OUT

BOOT

LOADER

C5

47µF

BOOTSTRAP

CLIP DET

OUT

BOOT

LOADER

BOOTSTRAP

D97AU808D

C10

100nF

R7

2Ω

10/15

Page 17

TDA7293

Figure 8a: Modular Application P.C. Board and Component Layout (scale 1:1) (Component SIDE)

Figure 8b: Modular Application P.C. Board and Component Layout (scale 1:1) (Solder SIDE)

11/15

Page 18

TDA7293

Figure 9: Distortion vs Output Power

T.H.D (%)

10

5

2

1

0.5

0.2

0.1

0.05

0.02

0.01

0.005

0.002

0.001

Vs = +/-29V

Rl = 4 Ohm

f = 1KHz

210051020 50

Pout (W)

f = 20 KHz

Figure 10: Distortion vs Output Power

T.H.D (%)

10

5

2

1

0.5

0.2

0.1

0.05

0.02

0.01

0.005

0.002

0.001

Vs = +/-40V

Rl = 8 Ohm

2 10051020 50

Pou t (W)

f = 20 KHz

f = 1KHz

Figure 11: Distortion vs Frequency

T.H.D. (%)

10

1

0.1

0.01

0.001

00.1110100

VS= +/- 35 V

Rl= 8 Ohm

Pout=100 mW

Po=50 W

Frequen cy (K Hz)

Figure 12: Modular Application Derating Rload

vs Vsupply (ref. fig. 7)

6

5

4

3

2

Forbidden A rea

1

Minimum Allovable Load (ohm)

Pd > 50W at T

0

20 25 30 35 40 45 50

Supply Voltage (+/-Vcc)

case

=70°C

Figure 13: Modular Application Pd vs Vsupply

(ref. fig. 7)

60

Dissipated Power for each

50

device of the modular

application

40

4ohm

30

20

Pdissipated (W)

10

0

20 25 30 35 40 45 50

Supply Voltage (+/-Vcc)

Pd limit at Tcase=70°C

8ohm

Figure 14: Output Power vs. Supply Voltage

Po (W)

120

110

100

90

80

70

60

50

40

30

20

10

0

10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40

Rl=8 Ohm

f= 1 KHz

T.H.D.=10 %

THD=0.5 %

Vs (+/-V)

12/15

Page 19

TDA7293

13/15

Page 20

TDA7293

DIM.

MIN. TYP. MAX. MIN. TYP. MAX.

A 5 0.197

B 2.65 0.104

C 1.6 0.063

E 0.49 0.55 0.019 0.022

F 0.66 0.75 0.026 0.030

G 1.14 1.27 1.4 0.045 0.050 0.055

G1 17.57 17.78 17.91 0.692 0.700 0.705

H1 19.6 0.772

H2 20.2 0.795

L 20.57 0.810

L1 18.03 0.710

L2 2.54 0.100

L3 17.25 17.5 17.75 0.679 0.689 0.699

L4 10.3 10.7 10.9 0.406 0.421 0.429

L5 5.28 0.208

L6 2.38 0.094

L7 2.65 2.9 0.104 0.114

S 1.9 2.6 0.075 0.102

S1 1.9 2.6 0.075 0.102

Dia1 3.65 3.85 0.144 0.152

mm inch

OUTLINE AND

MECHANICAL DATA

Multiwatt15 H

14/15

Page 21

TDA7293

Information furnishe d is beli eved to be accu rate and reliable. However, STMicroelec tronics assumes no res ponsibility for the consequences

of use of such i nformation nor for any i nfringement of patents or ot her rights of third par ties which may result from its use. No license i s

granted by impli cation or otherwis e under any patent or patent righ ts of STMicroelect ronics. Specifica tion mentioned in this publication are

subject to change without notic e. This public ation supers edes and replaces all information prev iously supplied. STMic roelec tronic s products

are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelect roni cs

© 2003 STMicroelectronics – Printed in Italy – All Rights Reserved

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco -

Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.

STMicroelectronics GROUP OF COMPANIES

http://www.st.com

15/15

Page 22

LM124/LM224/LM324/LM2902

Low Power Quad Operational Amplifiers

LM124/LM224/LM324/LM2902 Low Power Quad Operational Amplifiers

August 2000

General Description

The LM124 series consists of four independent, high gain,

internally frequency compensated operational amplifiers

which were designed specifically to operate from a single

power supply over a wide range of voltages. Operation from

split power supplies is also possible and the low power supply current drain is independent of the magnitude of the

power supply voltage.

Application areas include transducer amplifiers, DC gain

blocks and all the conventional op amp circuits which now

can be more easily implementedin single power supply systems. For example, the LM124 series can be directly operated off of the standard +5V power supply voltage which is

used in digital systems and will easily provide the required

interface electronics without requiring the additional

power supplies.

±

15V

Unique Characteristics

n In the linear mode the input common-mode voltage

range includes ground and the output voltage can also

swing to ground, even though operated from only a

single power supply voltage

n The unity gain cross frequency is temperature

compensated

n The input bias current is also temperature compensated

Advantages

n Eliminates need for dual supplies

n Four internally compensated op amps in a single

package

n Allows directly sensing near GND and V

to GND

n Compatible with all forms of logic

n Power drain suitable for battery operation

OUT

also goes

Features

n Internally frequency compensated for unity gain

n Large DC voltage gain 100 dB

n Wide bandwidth (unity gain) 1 MHz

(temperature compensated)

n Wide power supply range:

Single supply 3V to 32V

or dual supplies

n Very low supply current drain (700 µA)—essentially

independent of supply voltage

n Low input biasing current 45 nA

(temperature compensated)

n Low input offset voltage 2 mV

and offset current: 5 nA

n Input common-mode voltage range includes ground

n Differential input voltage range equal to the power

supply voltage

n Large output voltage swing 0V to V

±

1.5V to±16V

+

− 1.5V

Connection Diagram

Dual-In-Line Package

DS009299-1

Top View

Order Number LM124J, LM124AJ, LM124J/883 (Note 2), LM124AJ/883 (Note 1), LM224J,

LM224AJ, LM324J, LM324M, LM324MX, LM324AM, LM324AMX, LM2902M, LM2902MX, LM324N, LM324AN,

LM324MT, LM324MTX or LM2902N LM124AJRQML and LM124AJRQMLV(Note 3)

See NS Package Number J14A, M14A or N14A

Note 1: LM124Aavailable per JM38510/11006

Note 2: LM124 available per JM38510/11005

© 2000 National Semiconductor Corporation DS009299 www.national.com

Page 23

Connection Diagram (Continued)

Note 3: See STD Mil DWG 5962R99504 for Radiation Tolerant Device

LM124/LM224/LM324/LM2902

Order Number LM124AW/883, LM124AWG/883, LM124W/883 or LM124WG/883

LM124AWRQML and LM124AWRQMLV(Note 3)

LM124AWGRQML and LM124AWGRQMLV(Note 3)

Schematic Diagram (Each Amplifier)

DS009299-33

See NS Package Number W14B

See NS Package Number WG14A

www.national.com 2

DS009299-2

Page 24

Absolute Maximum Ratings (Note 12)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

LM124/LM224/LM324 LM2902

Supply Voltage, V

+

Differential Input Voltage 32V 26V

Input Voltage −0.3V to +32V −0.3V to +26V

Input Current

<

(V

−0.3V) (Note 6) 50 mA 50 mA

IN

Power Dissipation (Note 4)

Molded DIP 1130 mW 1130 mW

Cavity DIP 1260 mW 1260 mW

Small Outline Package 800 mW 800 mW

Output Short-Circuit to GND

(One Amplifier) (Note 5)

+

V

≤ 15V and TA= 25˚C Continuous Continuous

Operating Temperature Range −40˚C to +85˚C

LM324/LM324A 0˚C to +70˚C

LM224/LM224A −25˚C to +85˚C

LM124/LM124A −55˚C to +125˚C

Storage Temperature Range −65˚C to +150˚C −65˚C to +150˚C

Lead Temperature (Soldering, 10 seconds) 260˚C 260˚C

Soldering Information

Dual-In-Line Package

Soldering (10 seconds) 260˚C 260˚C

Small Outline Package

Vapor Phase (60 seconds) 215˚C 215˚C

Infrared (15 seconds) 220˚C 220˚C

See AN-450 “Surface Mounting Methods and Their Effect on Product Reliability” for other methods of soldering surface mount

devices.

ESD Tolerance (Note 13) 250V 250V

LM124A/LM224A/LM324A

32V 26V

LM124/LM224/LM324/LM2902

Electrical Characteristics

V+= +5.0V, (Note 7), unless otherwise stated

Parameter Conditions

Input Offset Voltage (Note 8) T

Input Bias Current I

(Note 9) T

Input Offset Current I

Input Common-Mode V

Voltage Range (Note 10) T

Supply Current Over Full Temperature Range

Large Signal V

Voltage Gain (V

Common-Mode DC, V

Rejection Ratio T

IN(+)

IN(+)

T

R

V

V

A

A

+

A

L

+

+

+

O

A

= 25˚C 1 2 1 3 2 3 mV

A

or I

IN(−),VCM

= 25˚C

or I

IN(−),VCM

= 25˚C

= 30V, (LM2902, V+= 26V), 0 V+−1.5 0 V+−1.5 0 V+−1.5 V

= 25˚C

=∞On All Op Amps mA

= 30V (LM2902 V+= 26V) 1.5 3 1.5 3 1.5 3

= 5V 0.7 1.2 0.7 1.2 0.7 1.2

= 15V, RL≥ 2kΩ, 50 100 50 100 25 100 V/mV

= 1V to 11V), TA= 25˚C

CM

= 25˚C

= 0V,

= 0V, 2 10 2 15 5 30 nA

=0VtoV+− 1.5V, 70 85 70 85 65 85 dB

LM124A LM224A LM324A

Min Typ Max Min Typ Max Min Typ Max

20 50 40 80 45 100 nA

www.national.com3

Units

Page 25

Electrical Characteristics (Continued)

V+= +5.0V, (Note 7), unless otherwise stated

Parameter Conditions

Power Supply V

Rejection Ratio (LM2902, V

Amplifier-to-Amplifier f = 1 kHz to 20 kHz, T

+

=5Vto30V

T

= 25˚C

A

+

= 5V to 26V), 65 100 65 100 65 100 dB

= 25˚C −120 −120 −120 dB

A

Coupling (Note 11) (Input Referred)

Output Current Source V

LM124/LM224/LM324/LM2902

Sink V

+

IN

+

= 15V, VO= 2V, TA= 25˚C mA

V

−

IN

+

V

= 15V, VO= 2V, TA= 25˚C

−

V

IN

+

= 15V, VO= 200 mV, TA= 25˚C

V

Short Circuit to Ground (Note 5) V

−

= 1V, V

= 1V, V

= 1V, V

= 0V, 20 40 20 40 20 40

IN

+

= 0V, 10 20 10 20 10 20

IN

+

= 0V, 12 50 12 50 12 50 µA

IN

+

= 15V, TA= 25˚C 40 60 40 60 40 60 mA

Input Offset Voltage (Note 8) 4 4 5 mV

Drift RS=0Ω 7 20 7 20 7 30 µV/˚C

V

OS

Input Offset Current I

Drift RS=0Ω 10 200 10 200 10 300 pA/˚C

I

OS

Input Bias Current I

Input Common-Mode V

IN(+)−IIN(−),VCM

or I

IN(+)

IN(−)

+

= +30V 0 V+−2 0 V+−2 0 V+−2 V

Voltage Range (Note 10) (LM2902, V

+

Large Signal V

Voltage Gain R

Output Voltage V

OH

= +15V (VOSwing = 1V to 11V)

≥ 2kΩ 25 25 15 V/mV

L

V+= 30V RL=2kΩ 26 26 26 V

Swing (LM2902, V

V

Output Current Source V

V+= 5V, RL=10kΩ 520 520 520mV

OL

=2V V

O

Sink V

=0V 303075nA

+

= 26V)

+

= 26V) RL=10kΩ 27 28 27 28 27 28

+

= +1V, 10 20 10 20 10 20

IN

−

= 0V,

V

IN

V+= 15V

−

= +1V, 10 15 5 8 5 8

IN

+

= 0V,

V

IN

V+= 15V

LM124A LM224A LM324A

Min Typ Max Min Typ Max Min Typ Max

40 100 40 100 40 200 nA

Units

mA

Electrical Characteristics

V+= +5.0V, (Note 7), unless otherwise stated

Parameter Conditions

Input Offset Voltage (Note 8) T

Input Bias Current I

(Note 9) T

Input Offset Current I

Input Common-Mode V

Voltage Range (Note 10) T

T

IN(+)

A

IN(+)

A

+

A

Supply Current Over Full Temperature Range

R

L

+

V

+

V

Large Signal V

Voltage Gain (V

+

O

Common-Mode DC, V

Rejection Ratio T

Power Supply V

A

+

Rejection Ratio (LM2902, V

www.national.com 4

= 25˚C 2 5 2 7 2 7 mV

A

or I

IN(−),VCM

= 0V,

= 25˚C

or I

IN(−),VCM

= 0V, 3 30 5 50 5 50 nA

= 25˚C

= 30V, (LM2902, V+= 26V), 0 V+−1.5 0 V+−1.5 0 V+−1.5 V

= 25˚C

=∞On All Op Amps mA

= 30V (LM2902 V+= 26V) 1.5 3 1.5 3 1.5 3

= 5V 0.7 1.2 0.7 1.2 0.7 1.2

= 15V, RL≥ 2kΩ, 50 100 25 100 25 100 V/mV

= 1V to 11V), TA= 25˚C

=0VtoV+− 1.5V, 70 85 65 85 50 70 dB

CM

= 25˚C

=5Vto30V

+

= 5V to 26V), 65 100 65 100 50 100 dB

LM124/LM224 LM324 LM2902

Min Typ Max Min Typ Max Min Typ Max

45 150 45 250 45 250 nA

Units

Page 26

Electrical Characteristics (Continued)

V+= +5.0V, (Note 7), unless otherwise stated

Parameter Conditions

T

= 25˚C

A

Amplifier-to-Amplifier f = 1 kHz to 20 kHz, T

= 25˚C −120 −120 −120 dB

A

Coupling (Note 11) (Input Referred)

+

Output Current Source V

Sink V

= 1V, V

IN

+

= 15V, VO= 2V, TA= 25˚C mA

V

−

= 1V, V

IN

+

= 15V, VO= 2V, TA= 25˚C

V

−

= 1V, V

V

IN

+

V

= 15V, VO= 200 mV, TA= 25˚C

Short Circuit to Ground (Note 5) V

−

= 0V, 20 40 20 40 20 40

IN

+

= 0V, 10 20 10 20 10 20

IN

+

= 0V, 12 50 12 50 12 50 µA

IN

+

= 15V, TA= 25˚C 40 60 40 60 40 60 mA

Input Offset Voltage (Note 8) 7 9 10 mV

Drift RS=0Ω 7 7 7 µV/˚C

V

OS

Input Offset Current I

Drift RS=0Ω 10 10 10 pA/˚C

I

OS

Input Bias Current I

Input Common-Mode V

IN(+)−IIN(−),VCM

or I

IN(+)

IN(−)

+

= +30V 0 V+−2 0 V+−2 0 V+−2 V

Voltage Range (Note 10) (LM2902, V

Large Signal V

Voltage Gain R

Output Voltage V

OH

+

= +15V (VOSwing = 1V to 11V)

≥ 2kΩ 25 15 15 V/mV

L

V+= 30V RL=2kΩ 26 26 22 V

Swing (LM2902, V

V

OL

Output Current Source V

V+= 5V, RL=10kΩ 5 20 5 20 5 100 mV

=2V V

O

Sink V

= 0V 100 150 45 200 nA

+

= 26V)

+

= 26V) RL=10kΩ 27 28 27 28 23 24

+

= +1V, 10 20 10 20 10 20

IN

−

V

= 0V,

IN

V+= 15V

−

= +1V, 5 8 5 8 5 8

IN

+

= 0V,

V

IN

+

V

= 15V

Note 4: Foroperating at high temperatures, the LM324/LM324A/LM2902 must be derated based on a +125˚C maximum junction temperature and a thermal resistance of 88˚C/W which applies for the device soldered in a printed circuit board, operating in a still air ambient. The LM224/LM224A and LM124/LM124A can be derated based on a +150˚C maximum junction temperature. The dissipation is the total of all four amplifiers— use external resistors, where possible, to allow the amplifier to saturate of to reduce the power which is dissipated in the integrated circuit.

+

Note 5: Shortcircuits from the output to V

current is approximately 40 mA independent of the magnitude of V

can cause excessive heating and eventual destruction. When considering short circuits to ground, the maximum output

+

. At values of supply voltage in excess of +15V, continuous short-circuits can exceed the power

dissipation ratings and cause eventual destruction. Destructive dissipation can result from simultaneous shorts on all amplifiers.

Note 6: This input current will only exist when the voltage at any of the input leads is driven negative. It is due to the collector-base junction of the input PNP tran-

sistors becoming forward biased and thereby acting as input diode clamps. In addition to this diode action, there is also lateral NPN parasitic transistor action on the

IC chip. This transistor action can cause the output voltages of the op amps to go to the V

an input is driven negative. This is not destructive and normal output states will re-establish when the input voltage, which was negative, again returns to a value

greater than −0.3V (at 25˚C).

Note 7: Thesespecifications are limited to −55˚C ≤T

≤ +85˚C, the LM324/LM324A temperature specifications are limited to 0˚C ≤ TA≤ +70˚C, and the LM2902 specifications are limited to −40˚C ≤ TA≤ +85˚C.

≤ T

A

Note 8: V

. 1.4V, RS=0Ωwith V+from 5V to 30V; and over the full input common-mode range (0V to V+− 1.5V) for LM2902, V+from 5V to 26V.

O

≤ +125˚C forthe LM124/LM124A. With the LM224/LM224A, all temperature specificationsarelimited to −25˚C

A

Note 9: The direction of the input current is out of the IC due to the PNP input stage. This current is essentially constant, independent of the state of the outputso

no loading change exists on the input lines.

Note 10: The input common-mode voltage of either input signal voltage should not be allowed to go negative by more than 0.3V (at 25˚C). The upper end of the

common-mode voltage range is V

+

.

V

+

− 1.5V (at 25˚C), but either or both inputs can go to +32V without damage (+26V for LM2902), independent of the magnitude of

Note 11: Due to proximity of external components, insure that coupling is not originating via stray capacitance between these external parts. This typically can be

detected as this type of capacitance increases at higher frequencies.

Note 12: Refer to RETS124AX for LM124A military specifications and refer to RETS124X for LM124 military specifications.

Note 13: Human body model, 1.5 kΩ in series with 100 pF.

LM124/LM224 LM324 LM2902

Min Typ Max Min Typ Max Min Typ Max

40 300 40 500 40 500 nA

+

voltage level (or to ground for a large overdrive) for the time duration that

Units

mA

LM124/LM224/LM324/LM2902

www.national.com5

Page 27

Typical Performance Characteristics

Input Voltage Range

LM124/LM224/LM324/LM2902

Supply Current

DS009299-34

Input Current

DS009299-35

Voltage Gain

Open Loop Frequency

Response

DS009299-36

DS009299-37

Common Mode Rejection

Ratio

DS009299-38

DS009299-39

www.national.com 6

Page 28

Typical Performance Characteristics (Continued)

LM124/LM224/LM324/LM2902

Voltage Follower Pulse

Response

Large Signal Frequency

Response

DS009299-40

Voltage Follower Pulse

Response (Small Signal)

DS009299-41

Output Characteristics

Current Sourcing

Output Characteristics

Current Sinking

DS009299-42

DS009299-44

DS009299-43

Current Limiting

DS009299-45

www.national.com7

Page 29

Typical Performance Characteristics (Continued)

Input Current (LM2902 only)

LM124/LM224/LM324/LM2902

DS009299-46

Application Hints

The LM124 series are op amps which operate with only a

single power supply voltage, have true-differential inputs,

and remain in the linear mode with an input common-mode

voltage of 0 V

of power supply voltage with little change in performance

characteristics. At 25˚C amplifier operation is possible down

to a minimum supply voltage of 2.3 V

The pinouts of the package have been designed to simplify

PC board layouts. Inverting inputs are adjacent to outputs for

all of the amplifiers and the outputs have also been placed at

the corners of the package (pins 1, 7, 8, and 14).

Precautions should be taken to insure that the power supply

for the integrated circuit never becomes reversed in polarity

or that the unit is not inadvertently installed backwards in a

test socket as an unlimited current surge through the resulting forward diode within the IC could cause fusing of the internal conductors and result in a destroyed unit.

Large differential input voltages can be easily accommodated and, as input differential voltage protection diodes are

not needed, no large input currents result from large differential input voltages. The differential input voltage may be

larger than V

should be provided to prevent the input voltages from going

negative more than −0.3 V

with a resistor to the IC input terminal can be used.

To reduce the power supply drain, the amplifiers have a

class A output stage for small signal levels which converts to

class B in a large signal mode. This allows the amplifiers to

both source and sink large output currents. Therefore both

NPN and PNP external current boost transistors can be used

to extend the power capability of the basic amplifiers. The

output voltage needs to raise approximately 1 diode drop

above ground to bias the on-chip vertical PNP transistor for

output current sinking applications.

For ac applications, where the load is capacitively coupled to

the output of the amplifier, a resistor should be used, from

the output of the amplifier to ground to increase the class A

bias current and prevent crossover distortion.

. These amplifiers operate over a wide range

DC

.

DC

+

without damaging the device. Protection

(at 25˚C). An input clamp diode

DC

Voltage Gain (LM2902 only)

DS009299-47

Where the load is directly coupled, as in dc applications,

there is no crossover distortion.

Capacitive loads which are applied directly to the output of

the amplifier reduce the loop stability margin. Values of

50 pF can be accommodated using the worst-case

non-inverting unity gain connection. Large closed loop gains

or resistive isolation should be used if larger load capacitance must be driven by the amplifier.

The bias network of the LM124 establishes a drain current

which is independent of the magnitude of the power supply

voltage over the range of from 3 V

to 30 VDC.

DC

Output short circuits either to ground or to the positive power

supply should be of short time duration. Units can be destroyed, not as a result of the short circuit current causing

metal fusing, but rather due to the large increase in IC chip

dissipation which will cause eventual failure due to excessive junction temperatures. Putting direct short-circuits on

more than one amplifier at a time will increase the total IC

power dissipation to destructive levels, if not properly protected with external dissipation limiting resistors in series

with the output leads of the amplifiers. The larger value of

output source current which is available at 25˚C provides a

larger output current capability at elevated temperatures

(see typical performance characteristics) than a standard IC

op amp.

The circuits presented in the section on typical applications

emphasize operation on only a single power supply voltage.

If complementary power supplies are available, all of the

standard op amp circuits can be used. In general, introducing a pseudo-ground (a bias voltage reference of V

allow operation above and below this value in single power

supply systems. Many application circuits are shown which

take advantage of the wide input common-mode voltage

range which includes ground. In most cases, input biasing is

not required and input voltages which range to ground can

easily be accommodated.

+

/2) will

www.national.com 8

Page 30

LM124/LM224/LM324/LM2902

Typical Single-Supply Applications (V

Non-Inverting DC Gain (0V Input = 0V Output)

*

R not needed due to temperature independent I

DC Summing Amplifier

(V

≥ 0VDCand VO≥ VDC)

IN’S

IN

+

= 5.0 VDC)

DS009299-5

Power Amplifier

Where: V0=V1+V2−V3−V

(V1+V2)≥(V3+V4) to keep V

DS009299-7

DS009299-6

4

>

0V

O

DC

V0=0VDCfor VIN=0V

AV=10

DC

www.national.com9

Page 31

Typical Single-Supply Applications (V

+

= 5.0 VDC) (Continued)

LED Driver

LM124/LM224/LM324/LM2902

DS009299-8

fo= 1 kHz

Q=50

= 100 (40 dB)

A

V

“BI-QUAD” RC Active Bandpass Filter

DS009299-9

Fixed Current Sources

Lamp Driver

DS009299-11

DS009299-10

www.national.com 10

Page 32

Typical Single-Supply Applications (V

Current Monitor

DS009299-12

+

= 5.0 VDC) (Continued)

LM124/LM224/LM324/LM2902

Driving TTL

DS009299-13

*

(Increase R1 for ILsmall)

Voltage Follower

Pulse Generator

DS009299-14

DS009299-15

www.national.com11

Page 33

Typical Single-Supply Applications (V

+

= 5.0 VDC) (Continued)

Squarewave Oscillator

LM124/LM224/LM324/LM2902

Pulse Generator

DS009299-16

DS009299-17

High Compliance Current Sink

IO= 1 amp/volt V

(Increase REfor Iosmall)

IN

DS009299-18

www.national.com 12

Page 34

Typical Single-Supply Applications (V

Low Drift Peak Detector

+

= 5.0 VDC) (Continued)

LM124/LM224/LM324/LM2902

Comparator with Hysteresis

DS009299-20

DS009299-19

Ground Referencing a Differential Input Signal

VO=V

R

DS009299-21

www.national.com13

Page 35

Typical Single-Supply Applications (V

Voltage Controlled Oscillator Circuit

LM124/LM224/LM324/LM2902

*

Wide control voltage range: 0 VDC≤ VC≤ 2(V+−1.5 VDC)

Photo Voltaic-Cell Amplifier

+

= 5.0 VDC) (Continued)

DS009299-22

AC Coupled Inverting Amplifier

www.national.com 14

DS009299-23

DS009299-24

Page 36

Typical Single-Supply Applications (V

AC Coupled Non-Inverting Amplifier

+

= 5.0 VDC) (Continued)

LM124/LM224/LM324/LM2902

DS009299-25

fO= 1 kHz

Q=1

=2

A

V

DC Coupled Low-Pass RC Active Filter

DS009299-26

www.national.com15

Page 37

Typical Single-Supply Applications (V

High Input Z, DC Differential Amplifier

LM124/LM224/LM324/LM2902

High Input Z Adjustable-Gain

DC Instrumentation Amplifier

+

= 5.0 VDC) (Continued)

DS009299-27

www.national.com 16

DS009299-28

Page 38

Typical Single-Supply Applications (V

+

= 5.0 VDC) (Continued)

LM124/LM224/LM324/LM2902

Using Symmetrical Amplifiers to

Reduce Input Current (General Concept)

Bridge Current Amplifier

DS009299-30

DS009299-29

fO= 1 kHz

Q=25

Bandpass Active Filter

DS009299-31

www.national.com17

Page 39

Physical Dimensions inches (millimeters) unless otherwise noted

LM124/LM224/LM324/LM2902

Ceramic Dual-In-Line Package (J)

Order Number JL124ABCA, JL124BCA, JL124ASCA, JL124SCA, LM124J,

LM124AJ, LM124AJ/883, LM124J/883, LM224J, LM224AJ or LM324J

NS Package Number J14A

MX S.O. Package (M)

Order Number LM324M, LM324MX, LM324AM, LM324AMX, LM2902M or LM2902MX

NS Package Number M14A

www.national.com 18

Page 40

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

LM124/LM224/LM324/LM2902

Molded Dual-In-Line Package (N)

Order Number LM324N, LM324AN or LM2902N

NS Package Number N14A

Ceramic Flatpak Package

Order Number JL124ABDA, JL124ABZA, JL124ASDA, JL124BDA, JL124BZA,

JL124SDA, LM124AW/883, LM124AWG/883, LM124W/883 or LM124WG/883

NS Package Number W14B

www.national.com19

Page 41

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

14-Pin TSSOP

Order NumberLM324MT or LM324MTX

NS Package Number MTC14

LM124/LM224/LM324/LM2902 Low Power Quad Operational Amplifiers

LIFE SUPPORT POLICY

NATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL

COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or

systems which, (a) are intended for surgical implant

into the body, or (b) support or sustain life, and

whose failure to perform when properly used in

accordance with instructions for use provided in the

2. A critical component is any component of a life

support device or system whose failure to perform

can be reasonably expected to cause the failure of

the life support device or system, or to affect its

safety or effectiveness.

labeling, can be reasonably expected to result in a

significant injury to the user.

National Semiconductor

Corporation

Americas

Tel: 1-800-272-9959

Fax: 1-800-737-7018

Email: support@nsc.com

www.national.com

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

National Semiconductor

Europe

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor

Asia Pacific Customer

Response Group

Tel: 65-2544466

Fax: 65-2504466

Email: ap.support@nsc.com

National Semiconductor

Japan Ltd.

Tel: 81-3-5639-7560

Fax: 81-3-5639-7507

Page 42

T

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

EXPLODED

1/2PAGE

HTP-8230

EXPLODED VIEW PARTS LIS

NOTE : THE COMPONENTS IDENTIFIED BY THE MARK

! ARE CRITICAL FOR RISK OF FIRE AND

ELECTRIC SHOCK. REPLACE ONLY WITH PART

NUMBER SPECIFIED.

REF. NO. PART NAME DESCRIPTION Q'TY PART NO. MARK

SKW-8230 : POWERED SUBWOOFER

SP01 CABINET ASS'Y SKW-8230 1 ANK8S404S-BM10

SP02 PLASTIC FOOT D87.5 x D37.5 x H50 HIPS 4 BPE8000040001

SP03 STAND BOARD F2905-GW 1 ANF860005-BM10

SP04 LOGO PLATE SKW-8230 / ONKYO NAME PLATE 1 BPL800150-0001

SP05 WOOD SCREW 8 x 4 x L75 PAN HEAD (FOR FOOT) 8 NST8550514750

SP06 WOOD SCREW 4STT+20A (FOR AMPLIFIER / SP) 18 837440204

SP08 WOOFER SPEAKER 20cm 4ohm 50W 1 W20178A

A01 REAR PANEL "SKW-8230" SPCC 190 x 120 x T2.0mm 1 GSE400175-2006

A02 AC CORD LINE CORD 2P 1800mm BLK POLARIZE 1 VPA0040120010

A03 BUSHING AC LINE BUSHING 1 DBU001002-0011

A04 POWER TRANSFORMER DC30V, DC2.3A, 120V / 60Hz 100W 1 TTI1120010120

A05 SCREW M4.0 x P0.7 x L25mm (FOR TRANS) 4 HSD1431033250

F902 FUSE 4A / 250V SLOW WALT 1 KSA0204000011

F903 FUSE 4A / 250V SLOW WALT 1 KSA0204000011

U01 MAIN PC BOARD ASS'Y MAIN PC BOARD ASS'Y 1 APE4012115001

<Note>

U01 : MAIN PC BOARD ASS'Y = PCB BRACKET + HEAT SINK + ALL PARTS FOR MAIN PC BOARD

U02 INPUT PC BOARD ASS'Y INPUT PC BOARD ASS'Y 1 APE4012125001

<Note>

U02 : INPUT PC BOARD ASS'Y = INPUT PC BOARD with RCA JACK + CORD ASS'Y

U03 VR / LED PC BOARD ASS'Y VR / LED PC BOARD ASS'Y 1 APE4012135001

<Note>

U03 : VR / LED PC BOARD ASS'Y = VR / LED PC BOARD with VR / LED / CORD ASS'Y etc.

SKF-8230F : FRONT SPEAKERS (L / R)

SP10 COMPLETE UNIT "SKF-8230F (L)" 1 ASL8M404S-BM10

SP11 BACK LABEL (L) without serial numbering 1 YLB810006-FL10

SP12 COMPLETE UNIT "SKF-8230F (R)" 1 ASL8M404S-BM11

SP13 BACK LABEL (R) without serial numbering 1 YLB810006-FR10

SKC-8230C : CENTER SPEAKER

SP14 COMPLETE UNIT "SKC-8230C" 1 ASL8C404S-BM10

SP15 BACK LABEL without serial numbering 1 YLB810006-C010

SKM-8230S : SURROUND SPEAKERS (L / R)

SP16 COMPLETE UNIT "SKM-8230S (L)" 1 ASL8S404S-BM10

SP17 BACK LABEL (L) without serial numbering 1 YLB810006-SL10

SP18 COMPLETE UNIT "SKM-8230S (R)" 1 ASL8S404S-BM11

SP19 BACK LABEL (R) without serial numbering 1 YLB810006-SR10

!

!

!

!

!

Page 43

2/2PAGE

T

HTP-8230

PRINTED CIRCUIT BOARD PARTS LIS

CIRCUIT NO. PART NAME DESCRIPTION Q'TY PART NO. MARK

PWB

PWB

IC501 POWER IC IC 15 PIN TDA7293 1 RHI007293-0001

DB901 DIODE RS402L 4A 100V 1 RHD2040100011

!

Page 44

HTP-8230

ONKYO CORPORATION

Sales & Product Planning Div. : 2-1, Nisshin-cho, Neyagawa-shi, OSAKA 572-8540, JAPAN

Tel: 072-831-8023 Fax: 072-831-8124

ONKYO U.S.A. CORPORATION

18 Park Way, Upper Saddle River, N.J. 07458, U.S.A.

Tel: 201-785-2600 Fax: 201-785-2650 http://www.onkyousa.com

ONKYO EUROPE ELECTRONICS GmbH

Liegnitzerstrasse 6, 82194 Groebenzell, GERMANY

Tel: +49-8142-4401-0 Fax: +49-8142-4401-555 http://www.onkyo.net

ONKYO CHINA LIMITED

Units 2102-2107, Metroplaza Tower I, 223 Hing Fong Road, Kwai Chung,

N.T., HONG KONG Tel: 852-2429-3118 Fax: 852-2428-9039

HOMEPAG

http://www.onkyo.com/

E

Loading...

Loading...